# **Z86D990/Z86D991 OTP and Z86L99X ROM**

## Low-Voltage Microcontrollers with ADC

**Preliminary Product Specification**

PS003807-1002

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

### **ZiLOG Worldwide Headquarters**

532 Race Street San Jose, CA 95126-3432 Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

#### **Document Disclaimer**

© 2002 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

## **Table of Contents**

| Architectural Overview                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features2Counter/Timers2Input/Output and Interrupts2Operating Characteristics3User-Programmable Option Bits3                                                                                    |

| Functional Block Diagram                                                                                                                                                                        |

| Pin Descriptions    5      Pins Configuration    7                                                                                                                                              |

| Operational Description9Central Processing Unit (CPU) Description9Memory (ROM/OTP and RAM)10Clock Circuit Description14Interrupts15Reset Conditions19Power Management22I/O Ports24Peripherals28 |

| Control and Status Registers52Register Summary52Register Error Conditions54Registers (Grouped by Function)55                                                                                    |

| Electrical Characteristics85Absolute Maximum Ratings85Standard Test Conditions85DC Characteristics86Analog-to-Digital Converter Characteristics89AC Characteristics90                           |

| Packaging                                                                                                                                                                                       |

| Design Considerations                                                                                                                                                                           |

| Ordering Information                                                                                                                                                                            |

| Precharacterization Product                                                                                                                                                                     |

## List of Figures

| Figure 1.  | Functional Block Diagram                                    | . 4 |

|------------|-------------------------------------------------------------|-----|

| Figure 2.  | 48-Pin SSOP Pin Assignments                                 | . 5 |

| Figure 3.  | 40-Pin DIP Pin Assignment                                   | . 6 |

| Figure 4.  | 28-Pin SOIC/DIP Pin Assignment—User Mode                    | . 7 |

| Figure 5.  | Program Memory Map                                          | 12  |

| Figure 6.  | Standard Z8 Register File (Working Reg. Groups 0–F, Bank 0) | 13  |

| Figure 7.  | Z8 Expanded Register File Architecture                      | 14  |

| Figure 8.  | Interrupt Block Diagram                                     | 16  |

| Figure 9.  | External Interrupt Sources IRQ0-IRQ2 Block Diagram          | 17  |

| Figure 10. | IRQ Logic                                                   | 18  |

| Figure 11. | Interrupt Request Timing                                    | 18  |

| Figure 12. | General Input/Output Pin                                    | 26  |

| Figure 13. | Analog Comparators                                          | 28  |

| _          | ADC Block Diagram                                           |     |

| Figure 15. | Low-Pass Filter (with 8-MHz Crystal)                        | 30  |

| Figure 16. | Active Glitch/Power Filter                                  | 32  |

| •          | I-V Characteristics for the Current Sink Pad P43            |     |

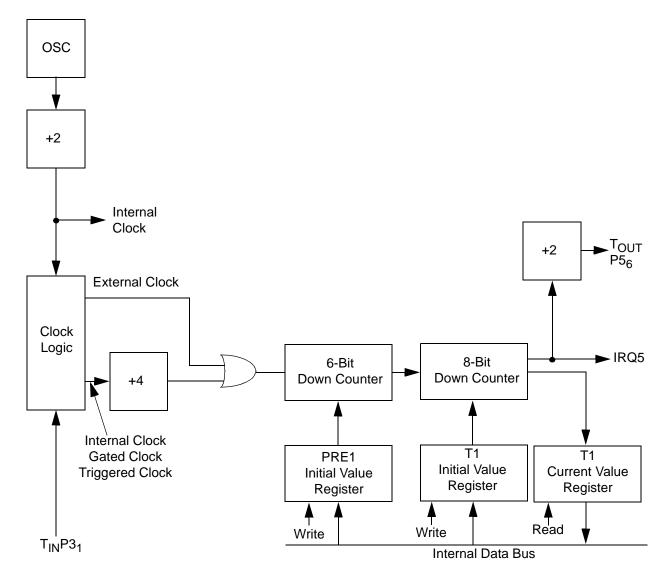

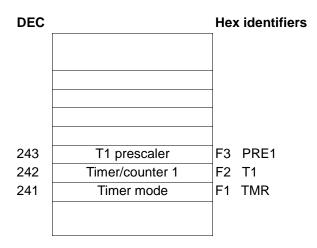

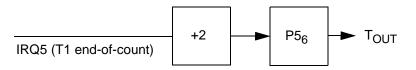

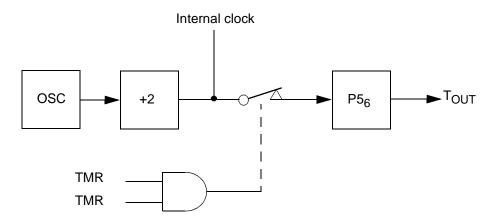

| Figure 18. | T <sub>1</sub> Counter/Timer Block Diagram                  | 35  |

| Figure 19. | Register File                                               | 36  |

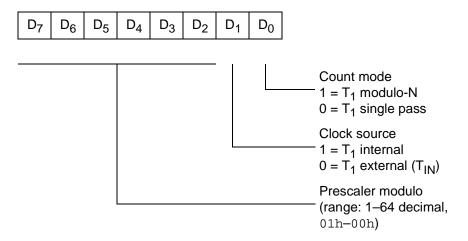

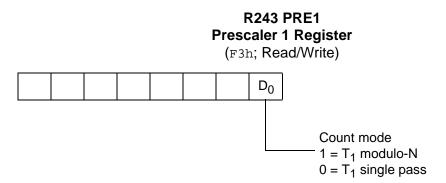

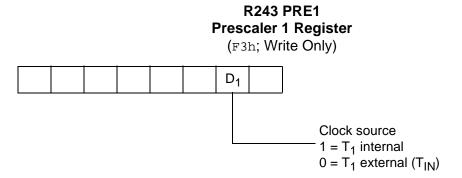

| -          | Prescaler 1 Register                                        |     |

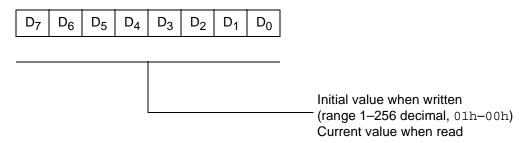

| Figure 21. | Counter/Timer 1 Register                                    | 37  |

| Figure 22. | Timer Mode Register                                         | 37  |

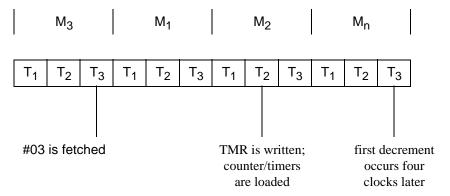

| Figure 23. | Starting the Count                                          | 38  |

| Figure 24. | Counting Modes                                              | 39  |

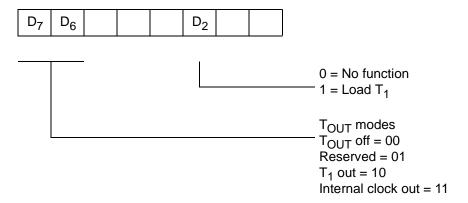

| Figure 25. | Timer Mode Register T <sub>OUT</sub> Operation              | 40  |

| Figure 26. | Counter/Timer Output Using T <sub>OUT</sub>                 | 41  |

| Figure 27. | Internal Clock Output Using T <sub>OUT</sub>                | 41  |

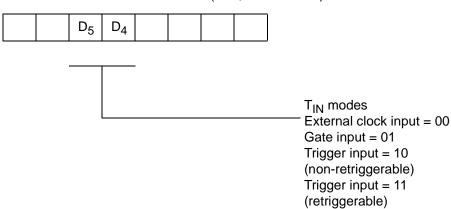

|            | Timer Mode Register T <sub>IN</sub> Operation               |     |

| -          | Prescaler 1 T <sub>IN</sub> Operation                       |     |

|            | External Clock Input Mode                                   |     |

| _          | Gated Clock Input Mode                                      |     |

| -          | Triggered Clock Mode                                        |     |

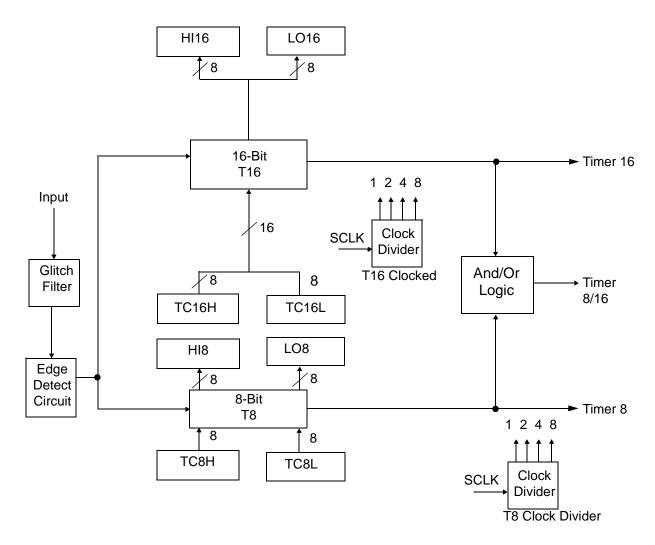

| Figure 33. | Counter/Timer Architecture                                  | 46  |

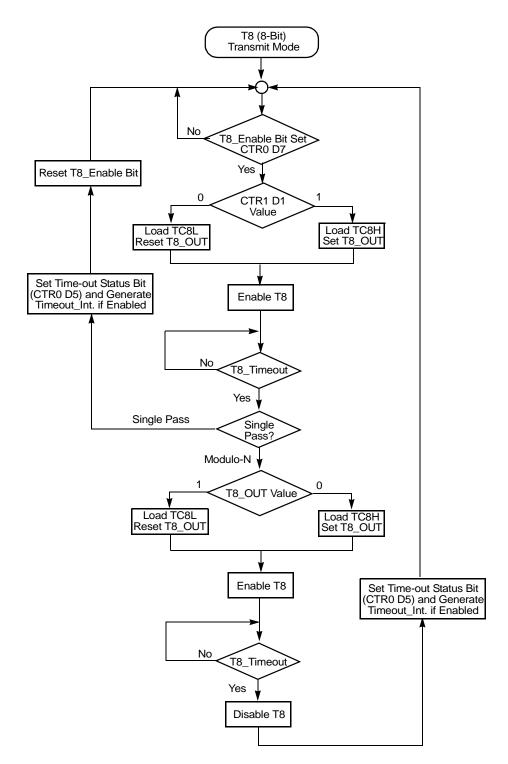

| Figure 34. | Transmit Mode Flowchart                                     | 48  |

## Z86D990/Z86D991 OTP and Z86L99X ROM Low-Voltage Microcontrollers with ADC

| Figure 35. | Demodulation Mode Flowchart | 50 |

|------------|-----------------------------|----|

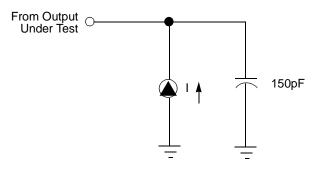

| Figure 36. | Test Load Diagram           | 86 |

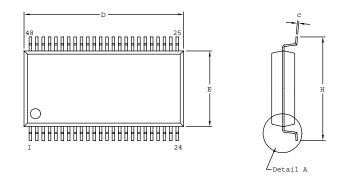

| Figure 37. | 48-Pin SSOP                 | 91 |

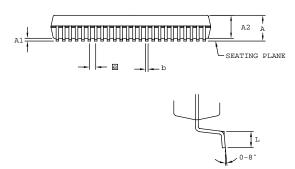

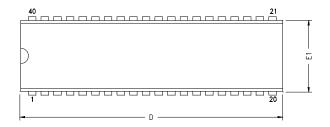

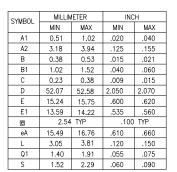

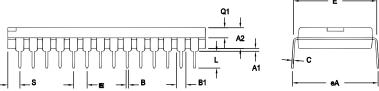

| Figure 38. | 40-Pin PDIP                 | 92 |

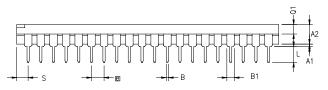

| Figure 39. | 28-Pin PDIP                 | 92 |

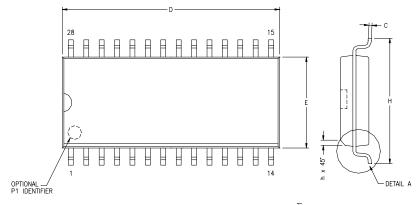

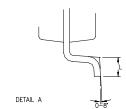

| Figure 40  | 28-Pin SOIC                 | 93 |

## Z86D990/Z86D991 OTP and Z86L99X ROM Low-Voltage Microcontrollers with ADC

## List of Tables

| Table 1.  | Z86L99/Z86D99 Feature Comparison                             | 1    |

|-----------|--------------------------------------------------------------|------|

| Table 2.  | Pin Descriptions                                             | 7    |

| Table 3.  | Interrupt Types, Sources, and Vectors                        | . 15 |

| Table 4.  | Interrupt Edge Select for External Interrupts                | . 17 |

| Table 5.  | Control and Status Register Reset Conditions                 | . 20 |

| Table 6.  | Clock Status in Operating Modes                              | . 22 |

| Table 7.  | Special Port Pin Functions                                   | . 27 |

| Table 8.  | Active Glitch/Filter Specifications (Preliminary)            | . 32 |

| Table 9.  | Current Sink Pad P43 Specifications (Preliminary)            | . 33 |

| Table 10. | I/O Port Registers (Group 0, Bank 0, Registers 0–F)          | . 52 |

| Table 11. | Timer Control Registers (Group 0, Bank D, Registers 0–F)     | . 53 |

| Table 12. |                                                              |      |

|           | Registers 0–F)                                               | . 53 |

| Table 13. | SMR and Port Mode Registers (Group 0, Bank F, Registers 0–F) | 54   |

| Table 14. |                                                              |      |

| Table 15. | -                                                            |      |

| Table 16. | RP Register [Group/Bank F0h, Register D (R253)]              |      |

| Table 17. | SP Register [Group/Bank F0h, Register F (R255)]              |      |

| Table 18. | LB Register (Group/Bank 0Dh, Register C)                     |      |

| Table 19. | ADCCTRL Register (Group/Bank 0Fh, Register 8)                |      |

| Table 20. | ADCDATA Register (Group/Bank 00h, Register 7)                |      |

| Table 21. | IMR (Group/Bank 0Fh, Register B)                             | . 63 |

| Table 22. | IPR (Group/Bank 0Fh, Register 9)                             | . 64 |

| Table 23. | IRQ (Group/Bank 0Fh, Register A)                             |      |

| Table 24. | P456CON Register (Group/Bank 0Fh, Register 0)                | . 67 |

| Table 25. | P3M Register [Group/Bank F0h, Register 7 (R247)]             | . 68 |

| Table 26. | P2 Register [Group/Bank 00h, Register 2 (R2)]                | . 68 |

| Table 27. | P2M Register [Group/Bank F0h, Register 6 (R246)]             | . 68 |

| Table 28. | P4 Register [Group/Bank 00h, Register 4 (R4)]                | . 69 |

| Table 29. | P4M Register (Group/Bank 0Fh, Register 2)                    | . 69 |

| Table 30. | P5 Register [Group/Bank 00h, Register 5 (R5)]                | . 70 |

| Table 31. | P5M Register (Group/Bank 0Fh, Register 4)                    | . 70 |

| Table 32. | P6 Register [Group/Bank 00h, Register 6 (R6)]                | . 71 |

## Z86D990/Z86D991 OTP and Z86L99X ROM Low-Voltage Microcontrollers with ADC

**⊿**∣ vii

| rable 33. | P6M Register (Group/Bank 0Fn, Register 6)                         | 71 |

|-----------|-------------------------------------------------------------------|----|

| Table 34. | T1 Register [Group/Bank F0h, Register 2 (R242)]                   | 72 |

| Table 35. | TMR Register [Group/Bank F0h, Register 1 (R241)]                  | 72 |

| Table 36. | PRE1 Register [Group/Bank F0h, Register 3 (R243)]                 | 73 |

| Table 37. | CTR1 Register (In Transmit Mode) (Group/Bank 0Dh, Register 1)     | 74 |

| Table 38. | CTR1 Register (in Demodulation Mode) (Group/Bank 0Dh, Register 1) | 75 |

| Table 39. | CTR3 Register (Group/Bank 0Dh, Register 3)                        | 76 |

| Table 40. | CTR0 Register (Group/Bank 0Dh, Register 0)                        | 77 |

| Table 41. | HI8 Register (Group/Bank 0Dh, Register B)                         | 78 |

| Table 42. | LO8 Register (Group/Bank 0Dh, Register A)                         | 78 |

| Table 43. | TC8H Register (Group/Bank 0Dh, Register 5)                        | 79 |

| Table 44. | TC8L Register (Group/Bank 0Dh, Register 4)                        | 79 |

| Table 45. | CTR2 Register (Group/Bank 0Dh, Register 2)                        | 80 |

| Table 46. | HI16 Register (Group/Bank 0Dh, Register 9)                        | 81 |

| Table 47. | LO16 Register (Group/Bank 0Dh, Register 8)                        | 81 |

| Table 48. | TC16H Register (Group/Bank 0Dh, Register 7)                       | 82 |

| Table 49. | TC16L Register (Group/Bank 0Dh, Register 6)                       | 82 |

| Table 50. | SMR Register (Group/Bank 0Fh, Register B)                         | 83 |

| Table 51. | P2SMR Register (Group/Bank 0Fh, Register 1)                       | 84 |

| Table 52. | P5SMR Register (Group/Bank 0Fh, Register 5)                       | 84 |

| Table 53. | Absolute Maximum Ratings                                          | 85 |

| Table 54. | DC Characteristics for the Z86D99X (OTP Only)                     | 87 |

| Table 55. | DC Characteristics for the Z86L99X (Mask Only)                    | 88 |

| Table 56. | Analog-to-Digital Converter Characteristics                       | 89 |

| Table 57. | AC Characteristics                                                | 90 |

## **Architectural Overview**

The Z86D99 is a low-voltage general-purpose one-time programmable (OTP) Z8<sup>®</sup> microcontroller with an integrated four-channel 8-bit sigma delta analog-to-digital converter. The Z86L99 is the read-only memory (ROM) version of this controller.

The Z86D99/Z86L99 family is designed to be used in a wide variety of embedded control applications including battery chargers, home appliances, infrared (IR) remote controls, security systems, and wireless keyboards.

It has three counter/timers, a general-purpose 8-bit counter/timer with a 6-bit prescaler and an 8-bit/16-bit counter/timer pair that can be used individually for general-purpose timing or as a pair to automate the generation and reception of complex pulses or signals. Unique features of the Z86D99/Z86L99 family of products include 489 bytes of general-purpose random-access memory (RAM), 256 bytes of which are mapped into the program memory space and can be used to store data variables or as executable RAM, a low-battery detection flag, and a controlled current output pin, which is a regulated current source that sinks a predefined current (I<sub>CCO</sub>). Table 1 highlights the basic product features of these microcontrollers.

Table 1. Z86L99/Z86D99 Feature Comparison

|         | Pins  | I/O | Memory<br>(Bytes) | Operating<br>Voltage (V) | ADC       | Timers | Watch-Dog<br>Timer |

|---------|-------|-----|-------------------|--------------------------|-----------|--------|--------------------|

| Z86D990 | 40/48 | 32  | 32K OTP           | 3.0-5.5                  | 4 channel | 3      | Yes                |

| Z86D991 | 28    | 24  | 32K OTP           | 3.0-5.5                  | _         | 3      | Yes                |

| Z86L990 | 40/48 | 32  | 16K ROM           | 2.3-5.5                  | 4 channel | 3      | Yes                |

| Z86L991 | 28    | 24  | 16K ROM           | 2.3-5.5                  | _         | 3      | Yes                |

| Z86L996 | 28    | 24  | 4K ROM            | 2.3-5.5                  | _         | 3      | Yes                |

| Z86L997 | 28    | 24  | 8K ROM            | 2.3-5.5                  | _         | 3      | Yes                |

The Z8 microcontroller core offers more flexibility and performance than accumulator-based microcontrollers. All 256 general-purpose registers, including dedicated input/output (I/O) port registers, can be used as accumulators. This unique register-to-register architecture avoids accumulator bottlenecks for high code efficiency. The registers can be used as address pointers for indirect addressing, as index registers, or for implementing an on-chip stack.

The Z8 has a sophisticated interrupt structure and automatically saves the program counter and status flags on the stack for fast context-switching. Speed of execution and smooth programming are also supported by a "working register area" with short 4-bit register addresses.

The Z8 instruction set, consisting of 43 basic instructions, is optimized for high-code density and reduced execution time. It is similar in form to the ZiLOG Z80 instruction set. The eight instruction types and six addressing modes together with the ability to operate on bits, 4-bit nibbles or binary coded decimal (BCD) digits, 8-bit bytes, and 16-bit words, make for a code-efficient, flexible microcontroller.

## **Features**

- Four-channel, 8-bit sigma delta analog-to-digital (A/D) converter with external voltage references (not available in the 28-pin configuration)

- Two independent analog comparators

- Controlled current output

- 489 bytes of RAM

- 233 bytes of general-purpose register-based RAM

- 256 bytes of RAM mapped into the program memory space that can be used as data RAM or executable RAM

- 32 Kbytes of OTP memory (Z86D99X)

- 16 Kbytes of ROM (Z86L99X)

#### Counter/Timers

- Special architecture to automate generation and reception of complex pulses or signals:

- Programmable 8-bit counter/timer (T8) with two 8-bit capture registers and two 8-bit load registers

- Programmable 16-bit counter/timer (T16) with one 16-bit capture register pair and one 16-bit load register pair

- Programmable input glitch filter for pulse reception

- One general-purpose 8-bit counter/timer (T1) with 6-bit prescaler

## Input/Output and Interrupts

- Thirty-two I/Os, twenty-nine of which are bidirectional I/Os with programmable resistive pull-up transistors (24 I/Os are available in the 28-pin configuration)

- Sixteen I/Os are selectable as stop-mode recovery sources

- Six interrupt vectors with nine interrupt sources

- Three external sources

- Two comparator interrupts

- Three timer interrupts

- One low-battery detector flag

## **Operating Characteristics**

- 8-MHz operation

- 3.0 V to 5.5 V operating voltage (Z86D990/Z86D991)

- 2.3 V to 5.5 V operating voltage (Z86L990/Z86L991)

- Low power consumption with three standby modes:

- Stop

- Halt

- Low Voltage Standby

- Low-battery detection flag

- Low-voltage protection circuit (also known as V<sub>BO</sub>, or voltage brownout, circuit)

- Watch-dog timer and power-on reset circuits

## **User-Programmable Option Bits**

- Clock source—RC/other (LC, resonator, or crystal)

- Watch-dog timer permanently enable

- 32-kHz crystal

- Port 20–27 pull-up resistive transistor

- Port 40–42 pull-up resistive transistor

- Port 44–47 pull-up resistive transistor

- Port 50–51 pull-up resistive transistor

- Port 54–57 pull-up resistive transistor

- Port 60–63 pull-up resistive transistor (not available in Z86D991/Z86L991)

- Port 64–67 pull-up resistive transistor (not available in Z86D991/Z86L991)

- P43 high impedance in STOP mode (available in OTP only)

Force P43 to output a 1 in the open-drain configuration

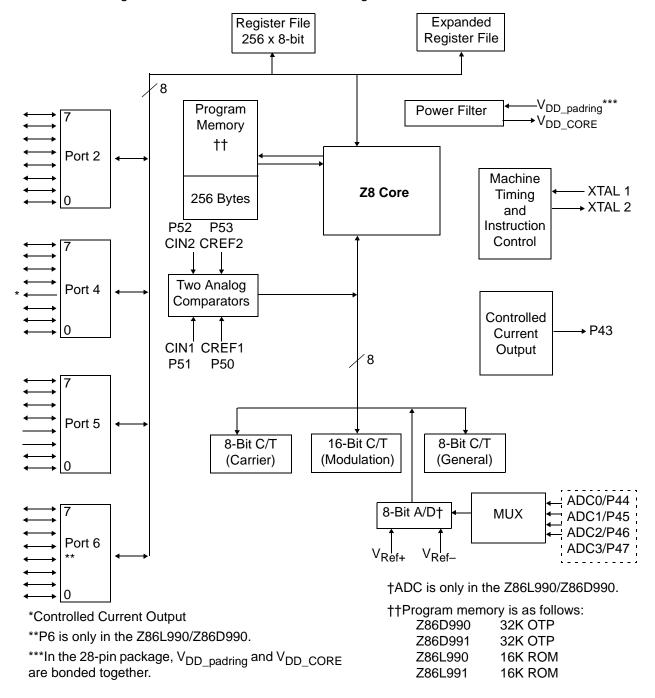

## **Functional Block Diagram**

Figure 1 shows the functional block diagram for the microcontrollers.

Figure 1. Functional Block Diagram

## **Pin Descriptions**

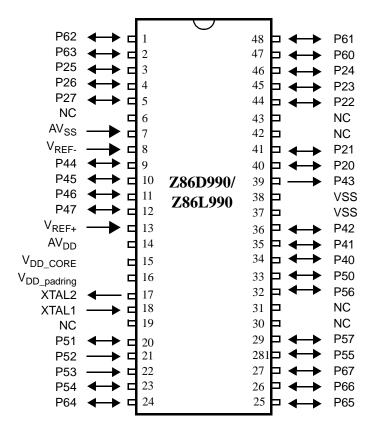

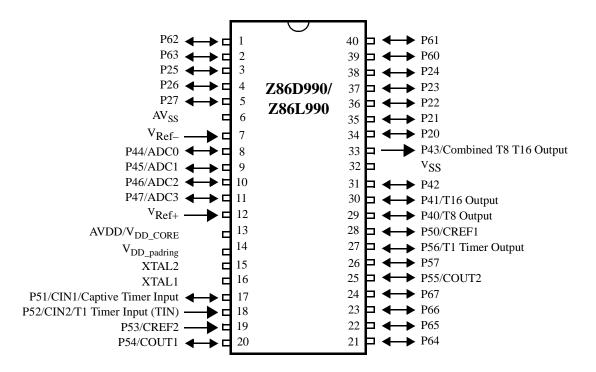

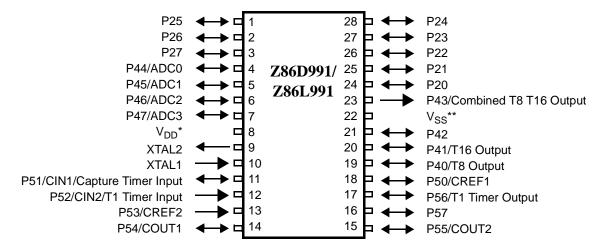

Figure 2 through Figure 4 show the pin names and locations.

### **Notes:**

- 1. Both V<sub>SS</sub> pins must be connected to ground.

- 2. NC is no connection to the die.

- 3.  $AV_{DD}$  must be connected to  $V_{DD}$  CORE and a 10- $\mu F$  capacitor for good A/D conversion.

- 4. Power must be connected to V<sub>DD\_padring</sub>. Current passes to V<sub>DD\_CORE</sub> through the internal power filter.

Figure 2. 48-Pin SSOP Pin Assignments

#### **Notes:**

- 1.  $AV_{DD}$  must be connected to  $V_{DD}$  CORE and a 10- $\mu F$  capacitor for good A/D conversion.

- 2. Power must be connected to  $V_{DD\_padring}$ . Current passes to  $V_{DD\_CORE}$  through the internal power filter.

Figure 3. 40-Pin DIP Pin Assignment

### **Notes:**

- 1. P43 is a controlled current output.

- 2. P54, P55, P56, and P57 are high drive outputs.

\*

$$V_{DD} = V_{DD\_CORE} + V_{DD\_padring} + AV_{DD}$$

Figure 4. 28-Pin SOIC/DIP Pin Assignment—User Mode

## **Pins Configuration**

Table 2 describes the pins.

**Table 2. Pin Descriptions**

|        | Pin #           |            |            |     |                         |

|--------|-----------------|------------|------------|-----|-------------------------|

| Symbol | 28<br>PDIP/SOIC | 40<br>PDIP | 48<br>SSOP |     | Description             |

| P20    | 24              | 34         | 40         | I/O | Port 2 Bit 0            |

| P21    | 25              | 35         | 41         | I/O | Port 2 Bit 1            |

| P22    | 26              | 36         | 44         | I/O | Port 2 Bit 2            |

| P23    | 27              | 37         | 45         | I/O | Port 2 Bit 3            |

| P24    | 28              | 38         | 46         | I/O | Port 2 Bit 4            |

| P25    | 1               | 3          | 3          | I/O | Port 2 Bit 5            |

| P26    | 2               | 4          | 4          | I/O | Port 2 Bit 6            |

| P27    | 3               | 5          | 5          | I/O | Port 2 Bit 7            |

| P40    | 19              | 29         | 34         | I/O | Port 4 Bit 0, T8 Output |

Table 2. Pin Descriptions (Continued)

|                         | Pin #           |            |            |                            |                                                        |  |

|-------------------------|-----------------|------------|------------|----------------------------|--------------------------------------------------------|--|

| Symbol                  | 28<br>PDIP/SOIC | 40<br>PDIP | 48<br>SSOP |                            | Description                                            |  |

| P41                     | 20              | 30         | 35         | I/O                        | Port 4 Bit 1, T16 Output                               |  |

| P42                     | 21              | 31         | 36         | I/O                        | Port 4 Bit 2                                           |  |

| P43                     | 23              | 33         | 39         | Output                     | T8/T16 Output, Controlled current output               |  |

| P44                     | 4               | 8          | 9          | I/O                        | Port 4 Bit 4, A/D Channel 0*                           |  |

| P45                     | 5               | 9          | 10         | I/O                        | Port 4 Bit 5, A/D Channel 1*                           |  |

| P46                     | 6               | 10         | 11         | I/O                        | Port 4 Bit 6, A/D Channel 2*                           |  |

| P47                     | 7               | 11         | 12         | I/O                        | Port 4 Bit 7, A/D Channel 3*                           |  |

| P50, CREF1              | 18              | 28         | 33         | I/O                        | Port 5 Bit 0, Comparator 1 reference                   |  |

| P51, CIN1               | 11              | 17         | 20         | I/O                        | Port 5 Bit 1, Capture timer input, IRQ <sub>2</sub>    |  |

| P52, CIN2               | 12              | 18         | 21         | Input                      | Port 5 Bit 2, Timer 1 timer input, IRQ <sub>0</sub>    |  |

| P53, CREF2              | 13              | 19         | 22         | Input                      | Port 5 Bit 3, Comparator 2 reference, IRQ <sub>1</sub> |  |

| P54                     | 14              | 20         | 23         | I/O                        | Port 5 Bit 4, High drive output                        |  |

| P55                     | 15              | 25         | 28         | I/O                        | Port 5 Bit 5, High drive output                        |  |

| P56                     | 17              | 27         | 32         | I/O                        | Port 5 Bit 6, Timer 1 output, High drive output        |  |

| P57                     | 16              | 26         | 29         | I/O                        | Port 5 Bit 7, High drive output                        |  |

| P60                     |                 | 39         | 47         | I/O                        | Port 6 Bit 0                                           |  |

| P61                     |                 | 40         | 48         | I/O                        | Port 6 Bit 1                                           |  |

| P62                     |                 | 1          | 1          | I/O                        | Port 6 Bit 2                                           |  |

| P63                     |                 | 2          | 2          | I/O                        | Port 6 Bit 3                                           |  |

| P64                     |                 | 21         | 24         | I/O                        | Port 6 Bit 4                                           |  |

| P65                     |                 | 22         | 25         | I/O                        | Port 6 Bit 5                                           |  |

| P66                     |                 | 23         | 26         | I/O                        | Port 6 Bit 6                                           |  |

| P67                     |                 | 24         | 27         | I/O                        | Port 6 Bit 7                                           |  |

| XTAL1                   | 10              | 16         | 18         | Input                      | Crystal, Oscillator clock                              |  |

| XTAL2                   | 9               | 15         | 17         | Output                     | Crystal, Oscillator clock                              |  |

| $AV_DD$                 |                 | 13         | 14         |                            | Analog power supply                                    |  |

| V <sub>DD_CORE</sub>    |                 | 13         | 15         |                            | Z8 core power supply                                   |  |

| AV <sub>SS</sub>        |                 | 6          | 7          |                            | Analog ground                                          |  |

| $V_{Ref-}$              |                 | 7          | 8          | Input                      | A/D converter lower reference                          |  |

| V <sub>Ref+</sub>       |                 | 12         | 13         | Input                      | A/D converter upper reference                          |  |

| V <sub>DD_padring</sub> | 8**             | 14         | 16         |                            | Power supply (pad ring)                                |  |

| V <sub>SS</sub>         | 22**            | 32         | 37, 38     |                            | Ground                                                 |  |

| Notes:                  | *A/D conve      | rter is n  | ot availat | ole in the $\overline{28}$ | pin configuration.                                     |  |

<sup>\*</sup>A/D converter is not available in the 28-pin configuration.

<sup>\*\*</sup>In the 28-pin configuration, all three (core, pad ring, and analog) powers are tied together.

## **Operational Description**

## **Central Processing Unit (CPU) Description**

The Z8 architecture is characterized by a flexible I/O scheme, an efficient register and address space structure and a number of ancillary features for cost-sensitive, high-volume embedded control applications. ROM-based products are geared for high-volume production (where the software is stable) and one-time programmable equivalents for prototyping as well as volume production where time to market or code flexibility is critical.

## **Architecture Type**

The Z8 register-oriented architecture centers around an internal register file composed of 256 consecutive bytes, known as the standard register file. The standard register file consists of 4 I/O port registers (R2, R4, R5, and R6), 12 control and status registers, 233 general-purpose registers, and 7 registers reserved for future expansion. In addition to the standard register file, the Z86D99/Z86L99 family uses 21 control and status registers located in the Z8 expanded register file. Any general-purpose register can be used as an accumulator and address pointer or an index, data, or stack register.

All active registers can be referenced or modified by any instruction that accesses an 8-bit register, without the requirement for special instructions. Registers accessed as 16 bits are treated as even-odd register pairs. In this case, the data's most significant byte (MSB) is stored in the even-numbered register, while the least significant byte (LSB) goes into the next higher odd-numbered register.

The Z8 CPU has an instruction set designed for the large register file. The instruction set provides a full compliment of 8-bit arithmetic and logical operations. BCD operations are supported using a decimal adjustment of binary values, and 16-bit quantities for addresses and counters can be incremented and decremented. Bit manipulation and Rotate and Shift instructions complete the data-manipulation capabilities of the Z8 CPU. No special I/O instructions are necessary because the I/O is mapped into the register file.

## **CPU Control Registers**

The standard Z8 control registers govern the operation of the CPU. Any instruction which references the register file can access these control registers. The following are available control registers:

- Register Pointer (RP)

- Stack Pointer (SP)

- Program Control Flags (FLAGS)

- Interrupt Control (IPR, IMR, and IRQ)

- Stop Mode Recovery (SMR, P2SMR, and P5SMR)

- Low-Battery Detect (LB) Flag

The Z8 uses a 16-bit Program Counter (PC) to determine the sequence of current program instructions. The PC is not an addressable register.

Peripheral registers are used to transfer data, configure the operating mode, and control the operation of the on-chip peripherals. Any instruction that references the register file can access the peripheral registers. The following are peripheral control registers:

- Analog/Digital Converter (ADCCTRL and ADCDATA)

- T1 Timer/Counter (TMR, T1, and PRE1)

- T8 Timer/Counter (CTR0, HI8, LO8, TC8H, and TC8L)

- T16 Timer/Counter (CTR2, HI16, LO16, TC16H, and TC16L)

- T8/T16 Control Registers (CTR1and CTR3)

In addition, the four port registers are considered to be peripheral registers. The following are port control registers:

- Port Configuration Registers (P456CON and P3M)

- Port 2 Control and Mode Registers (P2 and P2M)

- Port 4 Control and Mode Registers (P4 and P4M)

- Port 5 Control and Mode Registers (P5 and P5M)

- Port 6 Control and Mode Registers (P6 and P6M)

The functions and applications of the control and peripheral registers are explained in "Control and Status Registers" on page 52.

## Memory (ROM/OTP and RAM)

There are four basic address spaces available to support a wide range of configurations:

- Program memory (on-chip)

- Standard register file

- Expanded register file

- Executable RAM

The Z8 standard register file totals up to 256 consecutive bytes organized as 16 groups of 16 eight-bit registers. These registers consist of I/O port registers,

general-purpose RAM registers, and control and status registers. Every RAM register acts like an accumulator, speeding instruction execution and maximizing coding efficiency. Working register groups allow fast context switching.

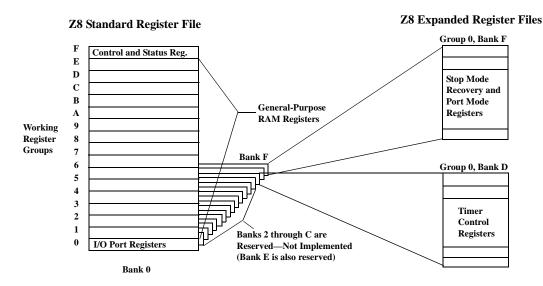

The standard register file of the Z8 (known as Bank 0) has been expanded to form 16 expanded register file (ERF) banks. The expanded register file allows for additional system control registers and for the mapping of additional peripheral devices into the register area. Each ERF bank can potentially consist of up to 256 registers (the same amount as in the standard register file) that can then be divided into 16 working register groups. Currently, only Group 0 of ERF Banks F and D (OFh and ODh) has been implemented.

In addition to the standard program memory and the RAM register files, the Z86D99/Z86L99 family also has 256 bytes of executable RAM that has been mapped into the upper 256 bytes of the program memory address space (FF00h-FFFFh). Data can be written to the executable RAM by using the LDC instruction.

### **Program Memory Structure**

The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts (IRQ<sub>0</sub> through IRQ<sub>5</sub>.) Address 12 (0ch) up to 32,767 (7FFFh) consists of on-chip one-time programmable memory. The Z86L99X only has the 4K/8K/16K ROM size.

After any reset operation (power-on reset, watch-dog timer time out, and stop mode recovery), program execution resumes with the initial instruction fetch from location 000ch. After a reset, the first routine executed must be one that initializes the control registers to the required system configuration.

A unique feature of the Z86D99/Z86L99 family is the presence of 256 bytes of onchip executable RAM. This random-access memory is in addition to the standard Z8 register file memory available on all Z8 microcontrollers. As illustrated in Figure 5, the executable RAM is mapped into the upper 256 bytes of the 64K program memory address space (FF00h-FFFFh). Data can be written to the executable RAM by using the LDC instruction.

Memory locations between 8000h and FEFFh have not been implemented on the Z86D99X microcontrollers.

The Z86D99/Z86L99 family does not have the capability of accessing external memory.

| Location (nex | 9                                                                    |

|---------------|----------------------------------------------------------------------|

| FFFF          |                                                                      |

|               | 256 bytes                                                            |

|               | Executable RAM                                                       |

| FF00          |                                                                      |

|               | Not Implemented                                                      |

| 3FFF/7FFF     |                                                                      |

| (ROM)/(OTP)   | PROGRAM                                                              |

|               | MEMORY                                                               |

|               |                                                                      |

| 000C          | Location of the first byte of the initial instruction executed after |

|               | RESET                                                                |

| 000B          | IRQ <sub>5</sub> (lower byte)                                        |

| 000A          | IRQ <sub>5</sub> (upper byte)                                        |

| 0009          | IRQ <sub>4</sub> (lower byte)                                        |

| 8000          | IRQ <sub>4</sub> (upper byte)                                        |

| 0007          | IRQ <sub>3</sub> (lower byte)                                        |

| 0006          | IRQ <sub>3</sub> (upper byte)                                        |

| 0005          | IRQ <sub>2</sub> (lower byte)                                        |

| 0004          | IRQ <sub>2</sub> (upper byte)                                        |

Figure 5. Program Memory Map

0003

0002

0001

0000

Location (Hex)

### Z8 Standard Register File (Bank 0)

Bank 0 of the Z8 expanded register file architecture is known as the standard register file of the Z8. As shown in Figure 6, the Z8 standard register file consists of 16 groups of sixteen 8-bit registers known as Working Register (WR) groups. Working Register Group F contains various control and status registers. The lower half of Working Register Group 0 consists of I/O port registers (R0 to R7), the upper eight registers are available for use as general-purpose RAM registers. Working Register Group 1 through Group E of the standard register file are available to be used as general-purpose RAM registers. The user can use 233 bytes of general-purpose RAM registers in the standard Z8 register file (Bank 0).

IRQ<sub>1</sub> (lower byte)

IRQ<sub>1</sub> (upper byte)

IRQ<sub>0</sub> (lower byte)

IRQ<sub>0</sub> (upper byte)

| Grp/Bnk | Reg      | Working Register Group Function |

|---------|----------|---------------------------------|

| (F0h)   | r0 to 15 | Control and Status Registers    |

| (E0h)   | r0 to 15 | General-purpose RAM registers   |

| (D0h)   | r0 to 15 | General-purpose RAM registers   |

| (C0h)   | r0 to 15 | General-purpose RAM registers   |

| (B0h)   | r0 to 15 | General-purpose RAM registers   |

| (A0h)   | r0 to 15 | General-purpose RAM registers   |

| (90h)   | r0 to 15 | General-purpose RAM registers   |

| (80h)   | r0 to 15 | General-purpose RAM registers   |

| (70h)   | r0 to 15 | General-purpose RAM registers   |

| (60h)   | r0 to 15 | General-purpose RAM registers   |

| (50h)   | r0 to 15 | General-purpose RAM registers   |

| (40h)   | r0 to 15 | General-purpose RAM registers   |

| (30h)   | r0 to 15 | General-purpose RAM registers   |

| (20h)   | r0 to 15 | General-purpose RAM registers   |

| (10h)   | r0 to 15 | General-purpose RAM registers   |

|         | r8 to 15 | General-purpose RAM registers   |

| (00h)   | r0 to 7  | I/O Port Registers              |

Figure 6. Standard Z8 Register File (Working Reg. Groups 0–F, Bank 0)

## **Z8 Expanded Register File**

In addition to the Standard Z8 Register File (Bank 0), Expanded Register File Banks F and D of Working Register Group 0 have been implemented on the Z86D99/Z86L99. Figure 7 illustrates the Z8 Expanded Register File architecture. These two expanded register file banks of Working Register Group 0 provide a total of 32 additional RAM control and status registers. The Z86D99/Z86L99 family has implemented 21 of the 32 available registers.

Figure 7. Z8 Expanded Register File Architecture

## **Clock Circuit Description**

The Z8 derives its timing from on-board clock circuitry connected to pins XTAL1 and XTAL2. The clock circuitry consists of an oscillator, a divide-by-two shaping circuit, and a clock buffer. The oscillator's input is XTAL1, and the oscillator's output is XTAL2. The clock can be driven by a crystal, a ceramic resonator, LC clock, RC, or an external clock source.

#### **Clock Control**

The Z8 offers software control of the internal system clock using programming register bits in the SMR register. This register selects the clock divide value and determines the mode of STOP Mode Recovery.

The default setting is external clock divide-by-two. When bits 1 and 0 of the SMR register are set to 0, the System Clock (SCLK) and Timer Clock (TCLK) are equal to the external clock frequency divided by two.

When bit 1 of the SMR register is set to 1, then SCLK and TCLK equal the external clock frequency. Refer to Table 53 on page 85 for the maximum clock frequency.

A divide-by-16 prescaler of SCLK and TCLK allows the user to selectively reduce device power consumption during normal processor execution (under SCLK control) and/or HALT mode, where TCLK sources counter/timers and interrupt logic. Combining the divide-by-two circuitry with the divide-by-16 prescaler allows the external clock to be divided by 32.

## Interrupts

The Z86D99/Z86L99 family allows up to six different interrupts, three external and three internal, from nine possible sources. The six interrupts are assigned as follows:

- Three edge-triggered external interrupts (P51, P52, and P53), two of which are shared with the two analog comparators

- One internal interrupt assigned to the T8 Timer

- One internal interrupt assigned to the T16 Timer

- One internal interrupt shared between the Low-Battery Detect flag and the T1 Timer

Table 3 presents the interrupt types, the interrupt sources, and the location of the specific interrupt vectors.

Table 3. Interrupt Types, Sources, and Vectors

|                  |                                                                                                                                                                      | Vector   |                                                                                                                                                        |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name             | Source                                                                                                                                                               | Location | Comments                                                                                                                                               |  |  |  |

| IRQ <sub>0</sub> | P52 (F/R), Comparator 2                                                                                                                                              | 0,1      | External interrupt (P52) is triggered by either rising or falling edge; internal interrupt generated by Comparator 2 is mapped into IRQ <sub>0</sub>   |  |  |  |

| IRQ <sub>1</sub> | P53 (F)                                                                                                                                                              | 2,3      | External interrupt (P53) is triggered by a falling edge                                                                                                |  |  |  |

| IRQ <sub>2</sub> | P51 (R/F), Comparator 1                                                                                                                                              | 4,5      | External interrupt (P51) is triggered by either a rising or falling edge; internal interrupt generated by Comparator 1 is mapped into IRQ <sub>2</sub> |  |  |  |

| IRQ <sub>3</sub> | T16 Timer                                                                                                                                                            | 6,7      | Internal interrupt                                                                                                                                     |  |  |  |

| IRQ <sub>4</sub> | T8 Timer                                                                                                                                                             | 8,9      | Internal interrupt                                                                                                                                     |  |  |  |

| IRQ <sub>5</sub> | LVD, T1 Timer                                                                                                                                                        | 10,11    | Internal interrupt, LVD flag is multiplexed with T1 Timer End-of-Count interrupt                                                                       |  |  |  |

| Notes:           | F = Falling-edge triggered; R = Rising-edge triggered. When LVD is enabled, IRQ5 is triggered only by low-voltage detection. Timer 1 does not generate an interrupt. |          |                                                                                                                                                        |  |  |  |

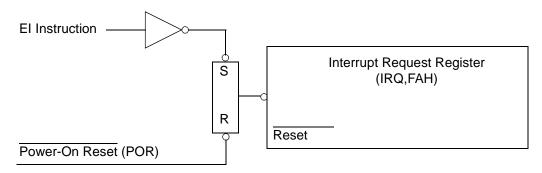

These interrupts can be masked and their priorities set by using the Interrupt Mask Register (IMR) and Interrupt Priority Register (IPR) (Figure 8.) When more than one interrupt is pending, priorities are resolved by a priority encoder, controlled by the IPR.

Figure 8. Interrupt Block Diagram

Interrupt requests are stored in the Interrupt Request Register (IRQ), which can also be used for polling. When an interrupt request is granted, the Z8 enters an "interrupt machine cycle" that globally disables all other interrupts, saves the program counter (the address of the next instruction to be executed) and status flags, and finally branches to the vector location for the interrupt granted. It is only at this point that control passes to the interrupt service routine for the specific interrupt.

All six interrupts can be globally disabled by resetting the master Interrupt Enable (bit 7 of the IMR) with a Disable Interrupts (DI) instruction. Interrupts are globally enabled by setting the same bit with an Enable Interrupts (EI) instruction.

Descriptions of three interrupt control registers—the Interrupt Request Register, the Interrupt Mask Register, and the Interrupt Priority Register—are provided in "Register Summary" on page 52. The Z8 family supports both vectored and polled interrupt handling.

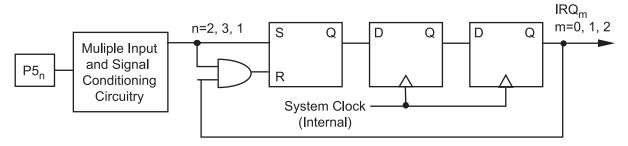

## **External Interrupt Sources**

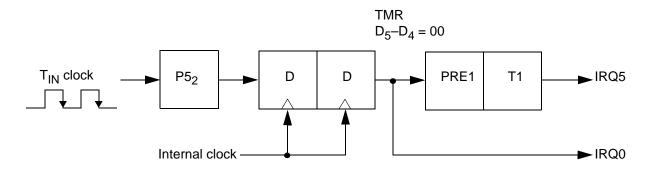

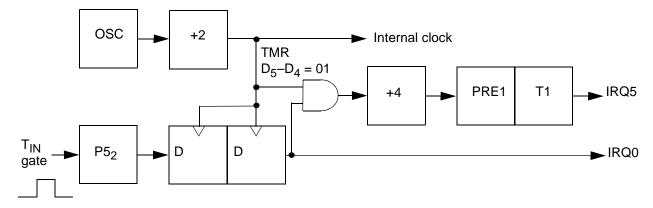

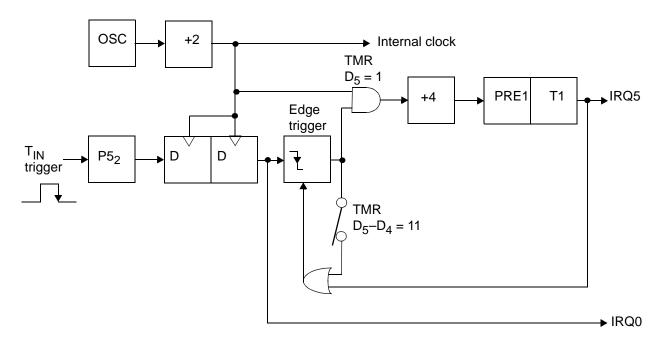

External sources involve interrupt request lines P51, P52, and P53 (IRQ $_2$ , IRQ $_0$ , and IRQ $_1$ , respectively.) IRQ $_0$ , IRQ $_1$ , and IRQ $_2$  are generated by a transition on the corresponding port pin. As shown in Figure 9, when the appropriate port pin (P51, P52, or P53) transitions, the first flip-flop is set. The next two flip-flops synchronize the request to the internal clock and delay it by two internal clock periods. The output of the most recent flip-flop (IRQ $_0$ , IRQ $_1$ , or IRQ $_2$ ) sets the corresponding Interrupt Request Register bit.

Figure 9. External Interrupt Sources IRQ<sub>0</sub>-IRQ<sub>2</sub> Block Diagram

The programming bits for the Interrupt Edge Select function are located in the IRQ register, bits 6 and 7. The configuration of these bits and the resulting interrupt edge is shown in Table 4.

Table 4. Interrupt Edge Select for External Interrupts

| Interrupt Requ | uest Register | Interru        | pt Edge                |

|----------------|---------------|----------------|------------------------|

| Bit 7          | Bit 7 Bit 6   |                | IRQ <sub>0</sub> (P52) |

| 0              | 0             | Falling        | Falling                |

| 0              | 1             | Falling        | Rising                 |

| 1              | 0             | Rising         | Falling                |

| 1              | 1             | Rising/Falling | Rising/Falling         |

**Note:** Although interrupts are edge triggered, minimum interrupt request Low and High times must be observed for proper operation. See "Electrical Characteristics" on page 85 for exact timing requirements (T<sub>W</sub>IL, T<sub>W</sub>IH) on external interrupt requests.

#### **Internal Interrupt Sources**

Internal sources are ORed with the external sources, so that either an internal or external source can trigger the interrupt.

### **Interrupt Request Register Logic and Timing**

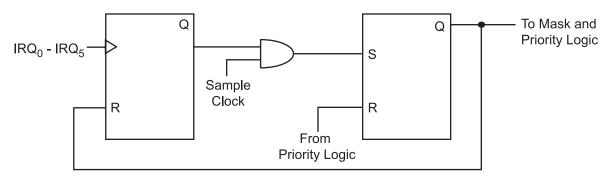

Figure 10 shows the logic diagram for the Interrupt Request Register. The leading edge of an interrupt request sets the first flip-flop. It remains set until the interrupt requests are sampled.

Figure 10. IRQ Logic

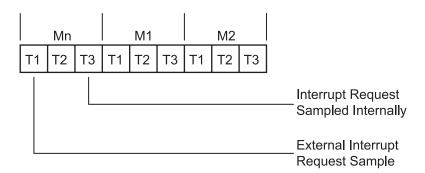

Internal interrupt requests are sampled during the most recent clock cycle before an Op Code fetch (see Figure 11.) External interrupt requests are sampled two internal clocks earlier than internal interrupt requests because of the synchronizing flip-flops shown in Figure 9.

Figure 11. Interrupt Request Timing

At sample time, the interrupt request is transferred to the second flip-flop shown in Figure 10, which drives the interrupt mask and priority logic. When an interrupt cycle occurs, this flip-flop is reset only for the highest priority level that is enabled.

The user has direct access to the second flip-flop by reading and writing to the IRQ. The IRQ is read by specifying it as the source register of an instruction, and the IRQ is written by specifying it as the destination register.

### Interrupt Initialization

After RESET, all interrupts are disabled and must be re-initialized before vectored or polled interrupt processing can begin. The Interrupt Priority Register, Interrupt Mask Register, and Interrupt Request Register must be initialized, in that order, to

start the interrupt process. However, the IPR does not have to be initialized for polled processing.

Interrupts must be globally enabled using the EI instruction. Setting bit 7 of the IMR is not sufficient. Subsequent to this EI instruction, interrupts can be enabled either by IMR manipulation or by use of the EI instruction, with equivalent effects.

Additionally, interrupts must be disabled by executing a DI instruction before the IPRs or IMRs can be modified. Interrupts can then be enabled by executing an EI instruction.

#### **IRQ Software Interrupt Generation**

IRQ can be used to generate software interrupts by specifying IRQ as the destination of any instruction referencing the Z8 Standard Register File. These Software Interrupts (SWIs) are controlled in the same manner as hardware-generated requests (the IPR and the IMR control the priority and enabling of each SWI level).

To generate a SWI, the request bit in the IRQ is set as follows:

where the immediate data, *NUMBER*, has a 1 in the bit position corresponding to the appropriate level of the SWI.

For example, for an SWI on IRQ5, *NUMBER* has a 1 in bit 5. With this instruction, if the interrupt system is globally enabled, IRQ5 is enabled, and there are no higher priority pending requests, control is transferred to the service routine pointed to by the IRQ5 vector.

### **Reset Conditions**

A system reset overrides all other operating conditions and puts the Z8 into a known state. The control and status registers are reset to their default conditions after a power-on reset (POR) or a Watch-Dog Timer (WDT) time-out while in RUN mode. The control and status registers are not reset to their default conditions after Stop Mode Recovery (SMR) while in HALT or STOP mode.

General-purpose registers are undefined after the device is powered up. Resetting the Z8 does not affect the contents of the general-purpose registers. The registers keep their most recent value after any reset, as long as the reset occurs in the specified  $V_{CC}$  operating range. Registers do not keep their most recent state from a  $V_{LV}$  reset, if  $V_{CC}$  drops below  $V_{RAM}$  (see Table 54 on page 87).

Following a reset (see Table 5), the first routine executed must be one that initializes the control registers to the required system configuration.

Table 5. Control and Status Register Reset Conditions

|                        | Address | 5     |        |                    |     | Res | set V | alue |    |     |    |    |   |

|------------------------|---------|-------|--------|--------------------|-----|-----|-------|------|----|-----|----|----|---|

| Register Function      | Grp/Bnk | Reg   | jister | Symbol             | R/W | 7   | 6     | 5    | 4  | 3   | 2  | 1  | 0 |

| Register Pointer       | F0h     | r13 ( | (R253) | RP                 | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| Stack Pointer          | F0h     | r15 ( | (R255) | SP                 | R/W | Χ   | Χ     | Χ    | Χ  | Χ   | Χ  | Χ  | Χ |

| Program Control Flags  | F0h     | r12 ( | (R252) | Flags              | R/W | Χ   | Χ     | Χ    | Χ  | Χ   | Χ  | Χ  | Χ |

| Low Battery Detect     | 0Dh     | r12   |        | LB                 | R/W | 1   | 1     | 1    | 1  | 1   | Χ  | 0  | 0 |

| ADC Control            | 0Fh     | r8    |        | ADCCTRL            | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| ADC Data               | 00h     | r7 (  | (R7)   | ADCDATA            | R   | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| Interrupt Mask         | F0h     | r11 ( | (R251) | IMR                | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| Interrupt Priority     | F0h     | r9 (  | (R249) | IPR                | W   | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| Interrupt Request      | F0h     | r10 ( | (R250) | IRQ                | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| Port Configuration (A) | 0Fh     | r0    |        | P456CON            | R/W | 0   | 0     | 0    | 0  | 0   | 1  | 1  | 1 |

| Port Configuration (B) | F0h     | r7 (  | (R247) | P3M                | W   | 1   | 1     | 1    | 1  | 1   | 1  | 1  | 1 |

| Port 2 Data            | 00h     | r2 (  | (R2)   | P2                 | R/W | Χ   | Χ     | Χ    | Χ  | Χ   | Χ  | Χ  | Χ |

| Port 2 Mode            | F0h     | r6 (  | (R246) | P2M                | W   | 1   | 1     | 1    | 1  | 1   | 1  | 1  | 1 |

| Port 4 Data            | 00h     | r4 (  | (R4)   | P4                 | R/W | Χ   | Χ     | Χ    | Χ  | Χ   | Χ  | Χ  | X |

| Port 4 Mode            | 0Fh     | r2    |        | P4M                | R/W | 1   | 1     | 1    | 1  | 1** | 1  | 1  | 1 |

| Port 5 Data            | 00h     | r5 (  | (R5)   | P5                 | R/W | Χ   | Χ     | Χ    | Χ  | Χ   | Χ  | Χ  | Χ |

| Port 5 Mode            | 0Fh     | r4    |        | P5M                | R/W | 1   | 1     | 1    | 1  | 1   | 1  | 1  | 1 |

| Port 6 Data            | 00h     | r6 (  | (R6)   | P6                 | R/W | Χ   | Χ     | Χ    | Χ  | Χ   | Χ  | Χ  | Χ |

| Port 6 Mode            | 0Fh     | r6    |        | P6M                | R/W | 1   | 1     | 1    | 1  | 1   | 1  | 1  | 1 |

| T1 Timer Data          | F0h     | r2 (  | (R242) | T1                 | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T1 Timer Mode          | F0h     | r1 (  | (R241) | TMR                | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 1  | 1 |

| T1 Timer Prescale      | F0h     | r3 (  | (R243) | PRE1               | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T8/T16 Control (A)     | 0Dh     | r1    |        | CTR1               | R/W | 0   | 0     | 0*   | 0* | 0   | 0  | 0  | 0 |

| T8/T16 Control (B)     | 0Dh     | r3    |        | CTR3               | R/W | 0   | 0     | 0*   | Χ  | Χ   | Χ  | Χ  | Χ |

| T8 Timer Control       | 0Dh     | r0    |        | CTR0               | R/W | 0   | 0     | 0*   | 0* | 0*  | 0* | 0* | 0 |

| T8 High Capture        | 0Dh     | r11   |        | HI8 <sup>†</sup>   | RW  | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T8 Low Capture         | 0Dh     | r10   |        | LO8 <sup>†</sup>   | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T8 High Load           | 0Dh     | r5    |        | TC8H <sup>†</sup>  | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T8 Low Load            | 0Dh     | r4    |        | TC8L <sup>†</sup>  | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T16 Timer Control      | 0Dh     | r2    |        | CTR2               | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T16 High Capture       | 0Dh     | r9    |        | HI16 <sup>†</sup>  | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T16 Low Capture        | 0Dh     | r8    |        | LO16 <sup>†</sup>  | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T16 High Load          | 0Dh     | r7    |        | TC16H <sup>†</sup> | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

| T16 Low Load           | 0Dh     | r6    |        | TC16L <sup>†</sup> | R/W | 0   | 0     | 0    | 0  | 0   | 0  | 0  | 0 |

Table 5. Control and Status Register Reset Conditions (Continued)

|                    | Address                                        | Address                                                                                                                                                                                                                                                                                                                                                          |        |     | Reset Value |   |   |   |   |   |   |   |

|--------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|---|---|---|---|---|---|---|

| Register Function  | Grp/Bnl                                        | k Register                                                                                                                                                                                                                                                                                                                                                       | Symbol | R/W | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Stop Mode Recovery | 0Fh                                            | r11                                                                                                                                                                                                                                                                                                                                                              | SMR    | R/W | 0           | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| Port 2 SMR Source  | 0Fh                                            | r1                                                                                                                                                                                                                                                                                                                                                               | P2SMR  | R/W | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Port 5 SMR Source  | 0Fh                                            | r5                                                                                                                                                                                                                                                                                                                                                               | P5SMR  | R/W | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Notes:             | *This bit<br>X means<br>**In OTF<br>initialize | †This register is not reset following Stop Mode Recovery (SMR). *This bit is not reset following SMR.  X means this bit is undefined at POR and is not reset following SMR.  **In OTP, the default for P43 is open-drain output at power up; you need to initialize the P43 data. In the mask part, the P43 output is disabled until it is configured as output. |        |     |             |   |   |   |   |   |   |   |

#### **Power-On Reset**

A POR (cold start) always resets the Z8 control and status registers to their default conditions. A POR sets bit 7 of the Stop Mode Recovery register to 0 to indicate that a cold start has occurred.

A timer circuit clocked by a dedicated on-board RC oscillator is used for the Power-On Reset Timer (TPOR) function. The POR time is specified as  $T_{POR}$ .  $T_{POR}$  time allows  $V_{CC}$  and the oscillator circuit to stabilize before instruction execution begins.

The POR delay timer circuit is a one-shot timer triggered by one of three conditions:

- Power Fail to Power OK status including recovery from Low Voltage (V<sub>LV)</sub> Standby mode

- STOP-Mode Recovery (when bit 5 of the SMR register = 1)

- WDT time-out

Under normal operating conditions, a stop mode recovery event always triggers the POR delay timer. This delay is necessary to allow the external oscillator time to stabilize. When using an RC or LC oscillator (with a low Q factor), the shorter wake-up time means the delay can be eliminated.

Bit 5 of the SMR register selects whether the POR timer delay is used after Stop-Mode Recovery or is bypassed. If bit 5 = 1, then the POR timer delay is used. If bit 5 = 0, then the POR timer delay is bypassed. In this case, the SMR source must be held in the recovery state for 5 TpC to pass the Reset signal internally.

## Watch-Dog Timer (WDT)

The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. When operating in the RUN modes, a WDT reset is functionally

equivalent to a hardware POR reset. If the mask option of the permanently enabled watch-dog timer is selected, it runs when power up. If the option is not selected, the WDT is initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction.

The WDT instruction does not affect the Zero (Z), Sign (S), and Overflow (V) flags. Permanently enabled WDTs are always enabled, and the WDT instruction is used to refresh it. The WDT cannot be disabled after it has been initially enabled. The WDT is off during both HALT and STOP modes.

The WDT circuit is driven by an on-board RC oscillator. The time-out period for the WDT is fixed to a typical value (see Table 57 on page 90).

## **Power Management**

In addition to the standard RUN mode, the Z8 supports three power-down modes to minimize device current consumption. The following three modes are supported:

- HALT

- STOP

- Low-Voltage Standby

Table 6 shows the status of the internal CPU clock (SCLK), the internal Timer clock (TCLK), the external oscillator, and the Watch-Dog Timer during the RUN mode and three low-power modes.

Table 6. Clock Status in Operating Modes

| Operating Mode                                     | SCLK | TCLK | External OSC | WDT* |  |  |

|----------------------------------------------------|------|------|--------------|------|--|--|

| RUN                                                | On   | On   | On           | On   |  |  |

| HALT                                               | Off  | On   | On           | Off  |  |  |

| STOP                                               | Off  | Off  | Off          | Off  |  |  |

| Low-Voltage Standby                                | Off  | Off  | Off          | Off  |  |  |

| Note: * When WDT is enabled by the mask option bit |      |      |              |      |  |  |

### **Using the Power-Down Modes**

In order to enter HALT or STOP mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. You can flush the

instruction pipeline by executing a NOP (Op Code = FFh) immediately before the appropriate sleep instruction. For example:

| Mnemonic | Comment              | Op Code |  |  |

|----------|----------------------|---------|--|--|

| NOP      | ; clear the pipeline | FFh     |  |  |

| STOP     | ; enter STOP mode    | 6Fh     |  |  |

or

| Mnemonic | Comment              | Op Code |  |  |  |

|----------|----------------------|---------|--|--|--|

| NOP      | ; clear the pipeline | FFh     |  |  |  |

| HALT     | ; enter HALT mode    | 7Fh     |  |  |  |

#### **HALT**

HALT mode suspends instruction execution and turns off the internal CPU clock (SCLK). The on-chip oscillator circuit remains active, so the internal Timer clock (TCLK) continues to run and is applied to the counter/timers and interrupt logic.

An interrupt request, either internally or externally generated, must be executed (enabled) to exit HALT mode. After the interrupt service routine, the program continues from the instruction immediately following the HALT.

The HALT mode can also be exited by a POR. In this case, the program execution restarts at the reset address 000Ch.

#### **STOP**

STOP mode provides the lowest possible device standby current. This instruction turns off both the internal CPU clock (SCLK) and internal Timer clock (TCLK) and reduces the standby current to the minimum.

The STOP mode is terminated by a POR or SMR source. Terminating the STOP mode causes the processor to restart the application program at address <code>000Ch</code>.

**Note:** When the STOP instruction is executed, the microcontroller goes into the STOP mode despite any state/change of the state of the port. The ports

STOP mode despite any state/change of the state of the port. The ports need to be checked immediately before the NOP and STOP instructions to ensure the right input logic before waiting for the change of the ports.

#### **Stop Mode Recovery Sources**

Exiting STOP mode using an SMR source is greatly simplified in the Z86D99/Z86L99 family. The Z86D99/Z86L99 family of products allows 16 individual I/O

pins (Ports 2 and 5) to be used as stop-mode recovery sources. The STOP mode is exited when one of these SMR sources is toggled. A transition from either low to high or high to low on any pin of Port 2 or Port 5 if the pin is identified as an SMR source will effect an SMR.

There are three registers that control STOP mode recovery:

- Stop Mode Recovery

- Port 2 Stop Mode Recovery (P2SMR)

- Port 5 Stop Mode Recovery (P5SMR)

The functions and applications of these registers are explained in "Stop-Mode Recovery Control Registers" on page 82.

## **Low-Voltage Standby**

An on-chip voltage comparator checks that the  $V_{CC}$  level is at the required level for correct operation of the Z8. When  $V_{CC}$  falls below the low-voltage trip voltage  $(V_{LV})$ , reset is globally driven, and then the device is put in a low-current standby mode with the external oscillator stopped. If the  $V_{CC}$  remains above  $V_{RAM}$ , the RAM content is preserved.

When the power level rises above the  $V_{LV}$  level, the device performs a POR and functions normally.

The minimum operating voltage varies with temperature and operating frequency, while  $V_{LV}$  varies with temperature only.

### I/O Ports

The Z86D99/Z86L99 family has up to 32 lines dedicated to input and output in the 40-pin configuration. These lines are grouped into four 8-bit ports known as Port 2, Port 4, Port 5, and Port 6. All four ports are bit programmable as either inputs or outputs with the exception of P52, P53, and P43. P52 and P53 are input only as they are used in OTP programming. P43 is the controlled current output and is therefore output only.

All ports have push-pull CMOS outputs. In addition, the push-pull outputs can be turned off for open-drain operation using the P456CON register.

Internal resistive pull-up transistors are available as a user-defined OTP/mask option on all ports. For Ports 4, 5, and 6, the pull-ups are nibble selectable. For Port 2, the pull-up option applies to all eight I/O lines.

**)**

**Note:** Internal pull-ups are disabled on any given pin or group of port pins when those pins are programmed as outputs.

## **Mode Registers**

Each port has an associated Mode Register that determines the port's functions and allows dynamic change in port functions during program execution. Port and Mode Registers are mapped into the Standard Register File. Because of their close association, Port and Mode Registers are treated like any other general-purpose register. There are no special instructions for port manipulation. Any instruction that addresses a register can address the ports. Data can be directly accessed in the Port Register, with no extra moves.

## **Input and Output Registers**

Each of the four ports (Ports 2, 4, 5, and 6) has an input register, an output register, and associated buffer and control logic. Because there are separate input and output registers associated with each port, writing bits defined as inputs store the data in the output register. This data cannot be read as long as the bits are defined as inputs. However, if the bits are reconfigured as output, the data stored in the output register is reflected on the output pins and can then be read. This mechanism allows the user to initialize the outputs before driving their loads.

Because port inputs are asynchronous to the Z8 internal clock, a READ operation could occur during an input transition. In this case, the logic level might be uncertain (somewhere between a logic 1 and 0).

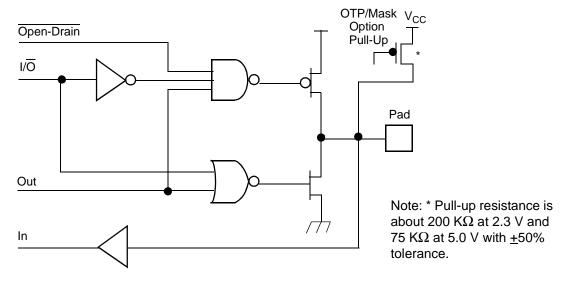

#### **General Port I/O**

The eight I/O lines of each port (except P43, P52, and P53) can be configured under software control to be either input or output, independently. Bits programmed as outputs can be globally programmed as either push-pull or opendrain. See Figure 12.

Figure 12. General Input/Output Pin

### **Read/Write Operations**

The ports are accessed as general-purpose registers. Port registers are written by specifying the port register as an instruction's destination register. Writing to a port causes data to be stored in the output register of the port, and reflected externally on any bit configured as an output.

Ports are read by specifying the port register as the source register of an instruction. When an output bit is read, data on the external pin is returned. Under normal loading conditions, returning data on the external pin is equivalent to reading the output register. However, if a bit is defined as an open-drain output, the data returned is the value forced on the output pin by the external system. This value might not be the same as the data in the output register. Reading input bits also returns data on the external pins.

## **Special Functions**

Table 7 defines the special functions of Ports 4 and 5.

Table 7. Special Port Pin Functions

| Function                             | Pin | Signal            | Configuration Register |

|--------------------------------------|-----|-------------------|------------------------|

| Analog Comparator Inputs             | P51 | CIN1              | P456CON                |

|                                      | P52 | CIN2              | P456CON                |

| Analog Comparator                    | P50 | CREF1             |                        |

| References                           | P53 | CREF2             |                        |

| Analog Comparator Outputs            | P54 | COUT1             |                        |

|                                      | P55 | COUT2             |                        |

| ADC Channels                         | P44 | ADC0              | ADCCTRL                |

|                                      | P45 | ADC1              | ADCCTRL                |

|                                      | P46 | ADC2              | ADCCTRL                |

|                                      | P47 | ADC3              | ADCCTRL                |

| External Interrupts                  | P52 | IRQ <sub>0</sub>  | IMR and IRQ            |

|                                      | P53 | IRQ <sub>1</sub>  | IMR and IRQ            |

|                                      | P51 | IRQ <sub>2</sub>  | IMR and IRQ            |

| T <sub>IN</sub> External Clock Input | P52 | T <sub>IN</sub>   | TMR and PRE1           |

| Capture Timer Input                  | P51 | Demodulator_Input | CTR1                   |

| T1 Timer Output                      | P56 | T1OUT             | TMR                    |

| T8 Output                            | P40 | P40_Out           | CTR0                   |

| T16 Output                           | P41 | P41_Out           | CTR2                   |

| Combined T8/T16 Output               | P43 | P43_Out           | CTR1                   |

| Controlled Current Output            |     |                   |                        |

| ZiLOG Test Mode                      | P41 | DSn Enable        | P456CON                |

|                                      | P42 | ASn Enable        | P456CON                |

## **Peripherals**

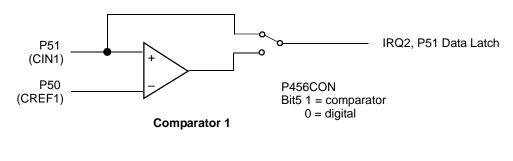

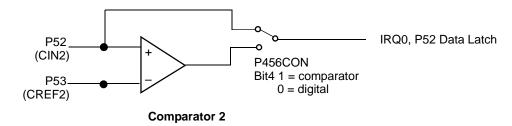

## **Analog Comparators**

The Z86D99/Z86L99 family includes two independent on-chip general-purpose analog comparators as shown in Figure 13. The comparators are multiplexed with a digital input signal by the P456CON register. They can also be used to generate interrupts IRQ0 and IRQ2. The comparators are turned off in STOP mode.

Figure 13. Analog Comparators

## **Analog/Digital Converter (ADC)**

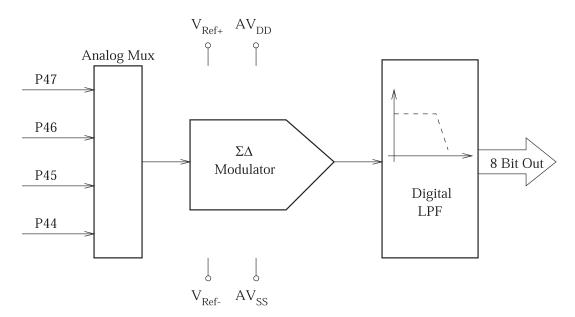

The Z86D99/Z86L99 family incorporates an 8-bit ADC that uses a sigma delta architecture (Figure 14) comprised of a modulator and a digital filter. The input is selected (bit 3,2 from ADCCTRL) with an analog mux from 4 (P47–P44) pins that can be configured as analog inputs (bit 7–4 from ADCCTRL).

**Note:** Whenever an input pin has an analog value, the digital input buffer has to be disabled in order to reduce the current through the device.

Figure 14. ADC Block Diagram

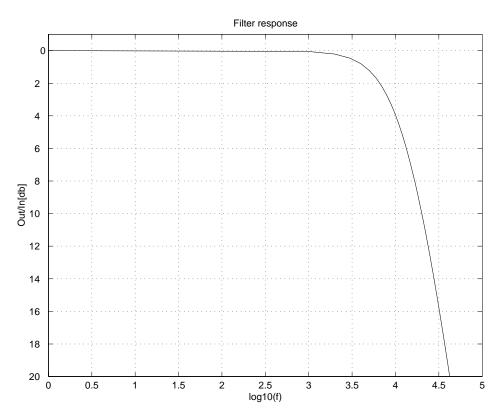

The low-pass filter transfer function is presented in Figure 15 with the -3-dB frequency given by the formula:

$$f_{3db} = 0.0021 \cdot f_{ADC}$$

where  $f_{\mbox{\scriptsize ADC}}$  is the sampling frequency of the modulator.

Figure 15. Low-Pass Filter (with 8-MHz Crystal)

The sampling frequency of the modulator  $f_{ADC}$  can be selected between  $f_{SCLK}$  and  $f_{SCLK}/2$  (bit1 from ADCCTRL). Reducing the clock frequency lowers the power dissipated in the ADC block.

The ADC can be enabled or disabled. When enabled, the  $\Sigma\Delta$  converter tracks the input voltage. When switching between the channels (step response), the required time to reach the final value is given by the time constant of the low-pass filter:

$$T_{delay} = \frac{2}{f_{3db}} = \frac{2}{0.0021 f_{ADC}} = \frac{952}{f_{ADC}}$$

When available, the reference for the ADC is set externally with the  $V_{ref+}$  and  $V_{ref-}$  pins. The output code represents the following ratio:

$$D_{out} = \frac{V_{in} - V_{Ref-}}{V_{Ref-} - V_{Ref-}} \times 256$$

Though the ADC functions for smaller input voltage range (V<sub>Ref+</sub>–V<sub>Ref-</sub>), the noise and offsets remain constant over the specified electrical range. The errors of the converter increase due to small input signals.

For fast access to the output of the ADC, the current data is available in the ADC result register (r8, bank00).

To reduce the interference between the digital part and the analog part, separate  $AV_{SS}$  and  $AV_{DD}$  pins are available on the packages where the ADC can be used.

**Note:** In the smaller packages, which do not support the ADC, the user must keep the converter *not active* in order to not have power dissipated in the ADC block. By default, ADC is off.

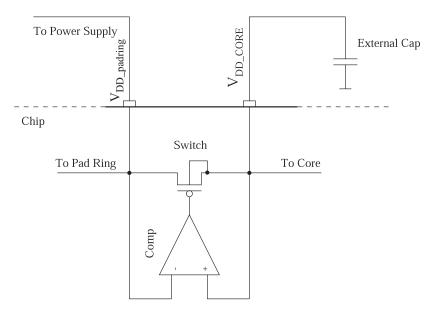

#### **Active Glitch Filter**

The Z86D99/Z86L99 family incorporates an active power/glitch filter that can be used to improve the quality of the power supply when the device is operating in noisy environments. The chips use three separate power buses:

- pad ring power bus (all the output drivers plus the crystal/RC oscillator) called

V<sub>DD\_padring</sub>

- core power bus (all digital circuitry) called V<sub>DD\_CORE</sub>

- analog power bus (all analog circuitry) called AV<sub>DD</sub>

Depending on the pin availability, one or more of the power buses are connected together.

The active power filter can be used in the packages that have the  $V_{DD}$  separate. Figure 16 shows the internal schematic.

Figure 16. Active Glitch/Power Filter

When the internal power/glitch filter is not used, both  $V_{DD\_padring}$  and  $V_{DD\_CORE}$  must be connected together externally to the power supply.

When the internal circuitry is used, the  $V_{DD\_padring}$  has to be connected to the power supply and the  $V_{DD\_CORE}$  has to be connected to an external energy storage capacitor (1–10  $\mu$ F range). The core is connected only to this capacitor during power supply glitches.

Table 8 describes the active glitch/filter specifications.

Table 8. Active Glitch/Filter Specifications (Preliminary)

| Parameter             | Max    | Min    | Condition   |

|-----------------------|--------|--------|-------------|

| Diff. stage gain      |        | 75 dB  |             |

| Diff. stage bandwidth | า      | 15 MHz |             |

| Rise time             | 255 ns |        | 50 mV pulse |

| Fall time             | 214 ns |        | 50 mV pulse |

| R <sub>dson</sub>     | 10 Ω   |        |             |

On the wafer level, all three power buses are available. Depending on the number of pins of the package, one or more power buses are connected together.

The active glitch/power filter effectively increases the noise immunity for batteryoperated designs where the controller is driving high current loads (for example, IR LED).

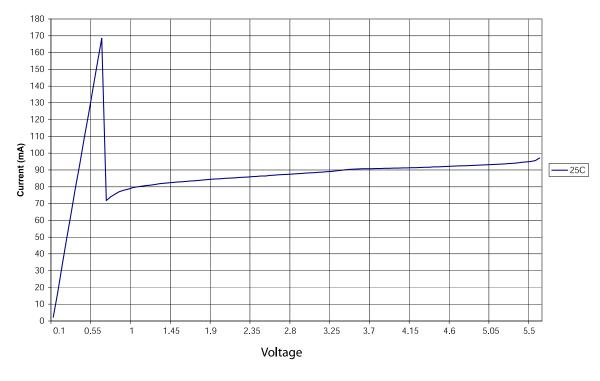

## **Controlled Current Output**

P43 is an open-drain output-only pin on the Z86D990/D991, but it can be configured as output or Tristate High Impedance on the Z86L990/L991. To function properly, Bit 3 of P4M must be set to zero to configure the pin as an open-drain output. For the Z86L990/L991 after reset, P43 defaults to Tristate High Impedance while the Z86D990/D991 P43 is always configured as output. The data at Port 4 must be initialized as it is undefined at power-on reset.

The current output is a controlled current source that is controlled by the output of the value of P43 (see Table 9). P43 *cannot* be configured as input, and if P43 is read, P43 always returns the state of the output value (1 for no sink and 0 for sink).

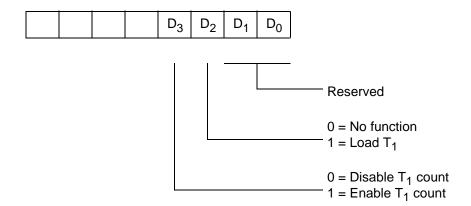

P43 uses internal current reference and will draw current if it outputs a low logic even without external connection. This applies to both Run mode and Stop mode.