# Z80S183/Z80L183

# **GENERAL-PURPOSE INTEGRATED MICROPROCESSOR**

PRODUCT SPECIFICATION

PS000503-1100

#### **DOCUMENT CONVENTIONS**

#### **DOCUMENT ASSUMPTIONS AND CONVENTIONS**

The following assumptions and conventions have been adopted to provide clarity and ease of use:

#### • Use of the Words Set and Clear

The words *set* and *clear* imply that a register bit or a condition has the value of *logical* 1 and *logical* 0 respectively. When the terms set and clear are followed by a number, often in parentheses, the word *logical* may not be included, but it is implied.

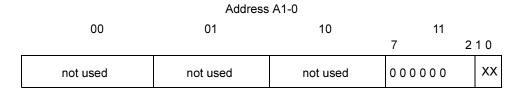

# • Notation for Bits and Similar Registers

A field of bits within a register are designated as: Register (n..n). For example: PWM\_CR (31..20). A field of bits within a bus are designated as: Bus<sub>n..n</sub>. For example: PCntl<sub>7..4</sub>. A range of similar (whole) registers is designated as: Register*n*..Register*n*. For example: OPBCS5..OPBCS0.

#### Use of the Terms LSB and MSB

In this document, the terms LSB and MSB mean least significant bit and most significant bit respectively.

#### Courier Font

Commands, code lines and fragments, register and other mnemonics, values, equations, and various executable items are distinguished from general text by the use of the Courier font. This convention is not used within tables. Where the use of the font is not possible, as in the Index, the name of the entity is capitalized. For example: The STP bit in the CNTR register must be 1.

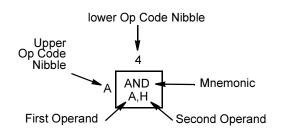

### Hexadecimal Values Designated by H

Hexadecimal values are designated by an upper-case letter H as well as the use of Courier font. For example: STAT is set to F8H.

## • Use of All Upper-Case Letters

The use of all upper-case letters designates the names of states and commands. For example: The receiver can force the SCL line to Low for force the transmitter into a WAIT state. The bus is considered BUSY after the Start condition. A START command triggers the processing of the initialization sequence.

# Use of Initial Upper-Case Letters

Initial upper-case letters designate settings, modes, and conditions in general text. For example: The Slave receiver leaves the data line High. In Transmit mode, the byte is sent most significant bit first. The Master can generate a Stop condition to abort the transfer.

PS000503-1100 iii

#### Z80S183/Z80L183 PRODUCT SPECIFICATION

Register Access Abbreviations

Register access is designation by the following abbreviations:

| Designation | Description                  |

|-------------|------------------------------|

| R           | Read Only                    |

| R/W         | Read/Write                   |

| W           | Write Only                   |

| _           | Unspecified or indeterminate |

Use of Fewer Bits Than in a Register Field

When a register field is comprised of multiple bits, a value for the field may be stated as a single number. For example: The reset value for an 8-bit field may be described as 0 when the register contains 8 bits that each have the value 0.

#### PRECHARACTERIZATION PRODUCT

The product represented by this document is newly introduced and ZiLOG has not completed the full characterization of the product. The document states what ZiLOG knows about this product at this time, but additional features or non-conformance with some aspects of the document may be found, either by ZiLOG or its customers in the course of further application and characterization work. In addition, ZiLOG cautions that delivery may be uncertain at times, due to start-up yield issues.

## COPYRIGHT AND DISCLAIMER

©2000 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

ZiLOG, Inc. 910 East Hamilton Avenue, Suite 110 Campbell, CA 95008 Telephone (408) 558-8500 FAX 408 558-8300

Internet: HTTP://www.ZILOG.COM

iv PS000503-1100

# **Architectural Overview**

The Z80S183/Z80L183 is a general-purpose integrated microprocessor. It includes the Z180 processor, 32 bits of general purpose I/O, an Analog-to-Digital converter with eight multiplexed inputs, a Programmable Output Generator, a Digital-to-Analog converter, a Watch-Dog Timer, two ASCI channels, two timers, a CSI/O channel, a Real Time Clock, 2KB of on-chip RAM, and 1KByte of on-chip ROM. It is packaged in a 100-pin VQFP.

The Z80S183/Z80L183 includes the following features:

- Code-compatible with Z80 & Z180

- On-chip wait state generator

- Two enhanced UART channels (ASCIs)

- Two 16-bit counters

- Three interrupt request inputs, two with optional edge-triggering

- Real time clock

- Two on-chip oscillators

- DC-to-33 MHz operating frequency @ 5.0V

- DC-to-20 MHz operating frequency @ 3.3V

- Clock divide by 2X or 1X

- Fully static CMOS design with low-power STANDBY mode

- 2 KB of on-chip RAM

- 1 KB of on-chip ROM

- Eight 10-bit A/D channels

- One 10-bit D/A

- 32 bits of general-purpose I/O

- Low-power PLL oscillator

- Programmable Output Generator (POG)

- Watch-Dog Timer (WDT)

- Clocked Serial I/O Interface (CSI/O)

- ZiLOG Debug Interface (ZDI)

- Power-down logic

- ASCI Tx complete output

PS000503-1100 Architectural Overview

- Economical 100-pin VQFP

- Interrupts on ports A and D

# **Block Diagram and Overview**

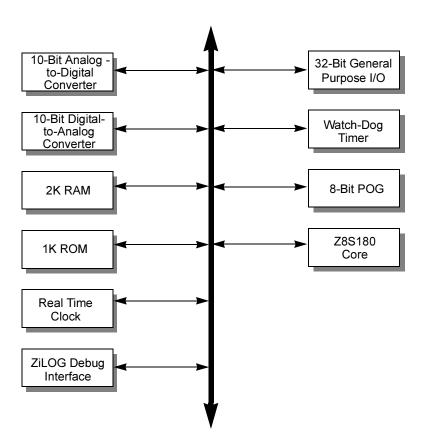

Figure 1 illustrates the block diagram for the Z80S183/Z80L183. In addition to a Z8S180-compatible processor, it includes the following modules:

- 32 Bits of General Purpose I/O.

- Four 8-bit ports are selectively multiplexed with on-chip peripheral functions (ASCIs, CSI/O, PRT, POG), and are individually programmable as inputs or outputs. Each I/O pin can source and sink 15mA.

- Programmable Output Generator.

- An engine that is independent of the processor, that can drive programmable waveforms onto 8 digital outputs, as well as initiating A/D and D/A conversions.

- Two ASCI Channels.

- Asynchronous serial channels with baud rate generators, modem control, and status.

- Two 16-bit Timers.

- Down-counters with interrupt capability.

- CSI/O.

- Clocked serial I/O can be used for serial memory or peripheral interface.

- Watch-Dog Timer.

- This circuit helps detect code runaway and helps minimize its negative effects.

A range of time-out values is available. The RESET pin can be forced Low at the terminal count of the Watch-Dog Timer.

- Eight Channel Analog-To-Digital Converter.

- A 10-bit converter with eight multiplexed inputs.

- Digital to Analog Converter.

- 10-bit resolution.

- 2KB of On-Chip RAM.

- Used for stack and other read/write operations.

PS000503-1100 Architectural Overview

Figure 1. Z80S183/Z80L183 Block Diagram

PS000503-1100 Architectural Overview

ZiLOG

# **Pin Descriptions**

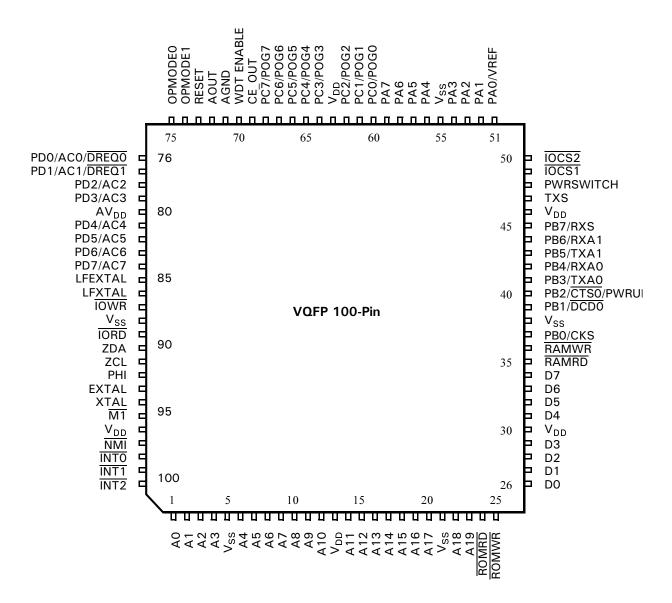

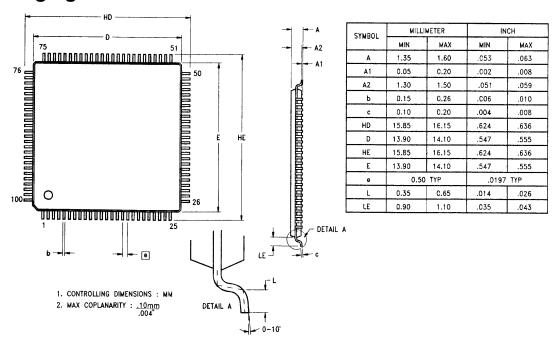

Figure 2 illustrates the Z80S183/Z80L183 pinout. Table 2 describes the processor and device pins. Table 2 describes the Asynchronous Serial Communications Interface (ASCI) and Clocked Serial I/O (CSI/O) pins. Table 3 describes the Port and Programmable Output Generator (POG) pins. Table 4 describes the analog pins.

Figure 2. Z80S183/Z80L183 Pin Description

Table 1. Processor and Device Pin Descriptions

| Symbol  | Pin#                             | Function                  | Туре                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|----------------------------------|---------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

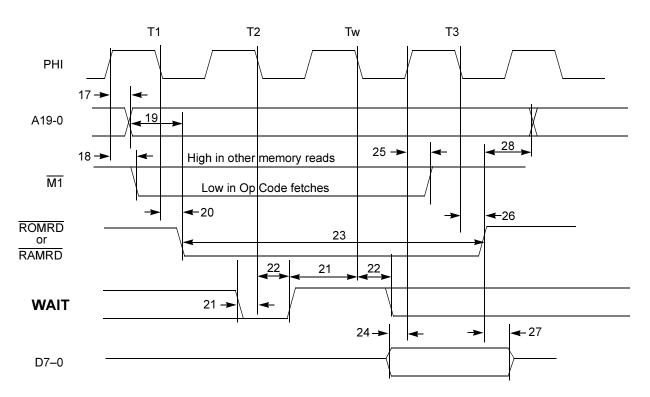

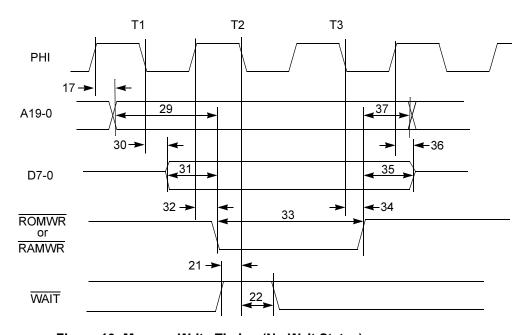

| A19-0   | 1–4,<br>6–12,<br>14–20,<br>22–23 | Address Bus               | Bidirectional,<br>3-state                   | These lines select a location in memory or I/O space to be read or written. The Z80S183/Z80L183 does not drive these lines during Reset nor external bus acknowledge cycles. Drive is optional during LOW-POWER modes.                                                                                                                                                                                                                                                                                                                                                               |

| CE_OUT  | 69                               | Chip Enable<br>Out        | Open drain output                           | An open-drain output, with no internal pull-up. Can be used to enable an external RAM, as described in "Using the Power Control Register" on page 33.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D7-0    | 26–29,<br>31–34                  | Data Bus                  | Bidirectional,<br>3-state                   | These lines transfer information to and from I/O and memory devices. The Z80S183/Z80L183 drives these lines only during write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

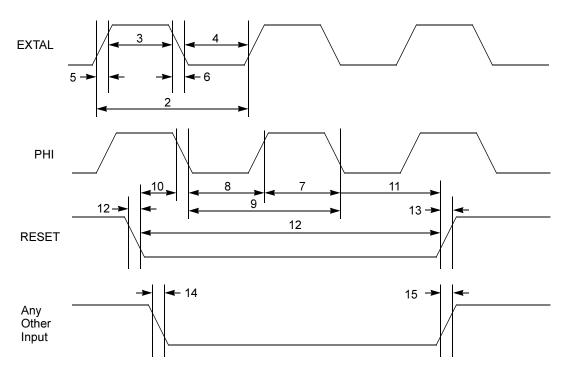

| EXTAL   | 93                               | Oscillator or<br>Clock In | Input                                       | This pin can be connected to a crystal or to an external clock. When a crystal is used, this signal is not a logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INTO    | 98                               | Interrupt<br>Request 0    | Input, active<br>Low                        | This signal can be driven Low in an open-drain fashion by external I/O devices. The processor responds to this request at the end of the current instruction cycle if it is enabled, and the NMI and BUSREQ signals are inactive. This pin can only be used in Z80/180 Mode 1, in which the processor acknowledges this request by interrupting to location 0038H.                                                                                                                                                                                                                   |

| INT1-2  | 99, 100                          | Interrupt<br>Requests 1–2 | Inputs, active<br>Low or edge-<br>triggered | These signals are generated by external devices. The processor acknowledges a request on one of these lines at the end of the current instruction cycle, so long as the NMI, BUSREQ, and INTO signals are inactive. The processor acknowledges one of these requests with an internal cycle, in which a fixed vector corresponding to one of the pins is used to select an interrupt service routine. These pins may be programmed for active Low level, rising or falling edge interrupts. The state of the external INT1 and INT2 pins can be read in the Interrupt Edge Register. |

| IOCS1-2 | 49, 50                           | I/O Chip<br>Selects 1–2   | Outputs, active<br>Low                      | When Bit 2 of the System Control register (SCR) is 1, IOCS1 goes Low for accesses to I/O addresses 0080–87H, and IOCS2 goes Low for accesses to 0088–8FH.                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 1. Processor and Device Pin Descriptions (Continued)

| Symbol    | Pin#  | Function                              | Туре                           | Description                                                                                                                                                                                                                                                                                           |

|-----------|-------|---------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IORD      | 89    | I/O Read                              | Output, active<br>Low, 3-state | IORD Low indicates that the Z80S183/Z80L183 is reading data from a location in I/O space. The addressed I/O device uses this signal to gate data onto the processor data bus. The Z80S183/Z80L183 does not drive this line during Reset, nor during bus acknowledge cycles.                           |

| IOWR      | 87    | I/O Write                             | Output, active<br>Low, 3-state | IOWR indicates that Bits D7–0 hold valid data to be stored at the addressed I/O location. The Z80S183/Z80L183 does not drive this line during Reset, nor during bus acknowledge cycles.                                                                                                               |

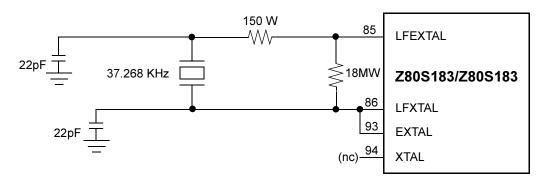

| LFExtal   | 85    | Low-<br>Frequency<br>Crystal or Clock | Input                          | A low-frequency crystal or line frequency input can be connected to this pin, for use by the real time clock. A low-frequency crystal can be also used with the FLL for a system clock.                                                                                                               |

| LFXTAL    | 86    | Low Frequency<br>Crystal              | Output                         | A low-frequency crystal can be connected to this pin, for use by the Real Time Clock or as the system clock.                                                                                                                                                                                          |

| M1        | 95    | Machine<br>Cycle 1                    | Output, active<br>Low          | Together with ROMRD or RAMRD, M1 Low indicates that the current cycle is the fetch cycle of an instruction execution.                                                                                                                                                                                 |

| NMI       | 97    | Nonmaskable<br>Interrupt              | Input, falling-<br>edge active | NMI has a higher priority than INTO and is always recognized at the end of an instruction, regardless of the state of the interrupt enable flip-flops. This signal forces processor execution to location 0066H. This input includes a Schmitt trigger to allow RC rise times.                        |

| OPMODE0-1 | 74–75 | Operating<br>Mode Select<br>1, 0      | Inputs                         | These pins select the basic operating mode of the Z80S183/Z80L183. A rising edge on OPMODE1 makes the Z80S183/Z80L183 generate a Power On Reset (POR), and subsequently enter Boot mode.  OPMODE1 OPMODE0 Operating Mode  L L Normal  L H Reserved  H L Internal ROM enabled  H H BUSREQ is generated |

| PHI       | 92    | System Clock                          | Output                         | This output is the Z80S183/Z80L183's master clock, and is provided for use by external logic. The frequency of this clock may be equal to or half of the crystal or input clock frequency, depending on an internal register bit.                                                                     |

Table 1. Processor and Device Pin Descriptions (Continued)

| Symbol    | Pin# | Function     | Туре                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|------|--------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRSWITCH | 48   | Power Switch | Output                         | This pin is a positive logic output controlled by Bit 5 of the Power Control register. Bit 5 resets to 0, so this pin goes Low at any Reset, including one initiated by a rising edge on PWRUP or OPMOD1. See "Using the Power Control Register" on page 33.                                                                                                                                                                                             |

| PWRUP     | 40   | Power Up     | Input                          | When Bit 6 is 1 in the Power Control Register, a rising edge on PB2/CTS0/PWRUP resets the part, as described in "Using the Power Control Register" on page 33.                                                                                                                                                                                                                                                                                           |

| RAMRD     | 35   | RAM Read     | Output, active<br>Low, 3-state | RAMRD Low indicates that the processor reads data from a memory location in the address range of external RAM. The Z80S183/Z80L183 does not drive this line during Reset, nor during bus acknowledgment.                                                                                                                                                                                                                                                 |

| RAMWR     | 36   | RAM write    | Output, active<br>Low, 3-state | RAMWR Low indicates D7–D0 hold data to be stored at a memory location in the address range of external RAM. The Z80S183/Z80L183 does not drive this line during Reset, nor during bus acknowledgement.                                                                                                                                                                                                                                                   |

| RESET     | 73   | Master Reset | Input/Output,<br>active Low    | This signal initializes the Z80S183/Z80L183 and other devices in the system. This input must be Low for a minimum of six system clock cycles, and is held Low until the clock is stable. RESET can be programmed as an output, allowing Z80S183/Z80L183 to reset external devices. The Power On Reset and Watch-Dog Timer (if enabled) blocks perform a global reset by forcing RESET Low. This input includes a Schmitt trigger to allow RC rise times. |

| ROMRD     | 24   | ROM Read     | Output, active<br>Low, 3-state | ROMRD Low indicates that the processor wants to read data from a memory location in the address range of external ROM/Flash. The Z80S183/Z80L183 does not drive this line during reset, nor during bus acknowledge cycles.                                                                                                                                                                                                                               |

| ROMWR     | 25   | ROM Write    | Output, active<br>Low, 3-state | ROMWR Low indicates that D7–0 hold a byte to be stored at the addressed memory location in the address range of external Flash memory. The Z80S183/Z80L183 does not drive this line during Reset, nor during bus acknowledge cycles.                                                                                                                                                                                                                     |

Table 1. Processor and Device Pin Descriptions (Continued)

| Symbol          | Pin#                     | Function                  | Туре                        | Description                                                                                                                                                                                                                                                                                           |

|-----------------|--------------------------|---------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$        | 13, 30,<br>46, 63,<br>96 | Power Supply              |                             | These pins carry power to the device. They must be tied to the same voltage externally.                                                                                                                                                                                                               |

| V <sub>SS</sub> | 5, 21,<br>38, 55,<br>88  | Ground                    |                             | These pins are the ground references for the device. They must be tied to the same voltage externally.                                                                                                                                                                                                |

| WDT Enable      | 70                       | Watch-Dog<br>Timer Enable | Input                       | When this pin is High, the Watch-Dog Timer cannot be disabled by software nor by Reset. When this pin is Low at power-up, these three events occur:  A Power On Reset disables the Watch-Dog Timer.  A WDT Reset does not change the status of the WDT.  Software can enable or disable it as needed. |

| XTAL            | 94                       | Crystal                   | Input/Output                | Crystal oscillator connection. This pin is left open if an external clock is used instead of a crystal. This pin does not carry a logic level. (See "DC Characteristics" on page 183.)                                                                                                                |

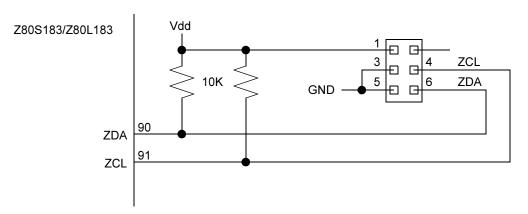

| ZCL             | 91                       | ZDI Clock                 | Input                       | The clock for the ZiLOG Debugging Interface. This input includes a Scmitt trigger.                                                                                                                                                                                                                    |

| ZDA             | 90                       | ZDI Data                  | Input/output,<br>open drain | Data for the ZiLOG Debugging Interface. This input includes a Schmitt trigger.                                                                                                                                                                                                                        |

Table 2. UART and CSI/O Pin Descriptions

| Symbol | Pin#   | Function                 | Туре                 | Description                                 |

|--------|--------|--------------------------|----------------------|---------------------------------------------|

| CTS0   | 40     | Clear To Send<br>0       | Input, active<br>Low | Transmit control signal for ASCI channel 0. |

| DCD0   | 39     | Data Carrier<br>Detect 0 | Input, active<br>Low | Receive control signal for ASCI channel 0.  |

| RXA0-1 | 42, 44 | Receive Data 0, 1        | Inputs               | ASCI Receive data.                          |

| RXS    | 45     | CSI/O Receive<br>Data    | Input                | Receive data for the CSI/O channel.         |

| TXA0-1 | 41, 43 | Transmit Data 0, 1       | Outputs              | ASCI Transmit data.                         |

| TXS    | 47     | CSI/O Transmit<br>Data   | Output               | Transmit data from the CSI/O channel.       |

Table 3. Port and POG Pin Descriptions

| Symbol | Pin#            | Function | Туре          | Description                                                                                                                                                                                                                                      |

|--------|-----------------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA7-0  | 51–54,<br>56–59 | Port A   | Input/outputs | These pins can be configured as inputs or outputs, with or without level-sensitive, active Low interrupt request capability, on a bit-by-bit basis.                                                                                              |

| PB7-0  | 37,<br>39–45    | Port B   | Input/outputs | These pins can be configured as port inputs or outputs, or ASCI or CSI/O signals, on a bit-by-bit basis.                                                                                                                                         |

| PC7-0  | 60–62,<br>64–68 | Port C   | Input/outputs | These pins can be configured as port inputs or outputs, or Programmable Output Generator outputs, on a bit-by-bit basis. Also, PC0 can be used as a 50 or 60 Hz time base for the real time Clock.                                               |

| PD7-0  | 76–79,<br>81–84 | Port D   | Input/outputs | These pins can be configured as inputs or outputs, with or without level-sensitive, active Low interrupt request capability, or as inputs to the A/D converter, on a bit-by-bit basis. PD0 and PD1 can also act as DREQ0 and DREQ1 respectively. |

Table 4. Analog Pin Descriptions

| Symbol           | Pin# | Function                        | Туре   | Description                                              |

|------------------|------|---------------------------------|--------|----------------------------------------------------------|

| AC7-0            |      | Analog<br>Channels              | Inputs | Inputs to the Analog to Digital converter.               |

| AGND             | 71   | Analog Ground                   |        | Reference ground for the analog circuitry.               |

| AOUT             | 72   | Analog Output                   | Output | The output of the Digital to Analog converter.           |

| AV <sub>DD</sub> | 80   | Analog Power                    |        | Power for the analog circuitry.                          |

| VREF             | 51   | External<br>Analog<br>Reference | Input  | External analog reference voltage, multiplexed with PA0. |

# **Operational Description**

This section describes, using text, tables, and figures, how the various parts of the Z80S183/Z80L183 operate. This description is presented from the processor outward to the peripherals. In the latter parts of this section, refer to the corresponding section of "I/O Registers" on page 80 that presents the Z80S183/Z80L183's I/O registers. Cross-reference links are included in both sections to aid these references.

# **Processor Description**

The Z80S183/Z80L183 is an 8-bit microprocessor that performs certain 16-bit operations. In both data sizes, the processor includes an accumulator. Register A is the accumulator for 8-bit operations, and the HL register pair is the accumulator for 16-bit operations.

# **Processor Program Registers**

In addition to register A, there are six more 8-bit registers named B, C, D, E, H, and L that can also be operated on as 16-bit register pairs BC, DE, and HL. Flag register F completes the basic register bank.

Two of these basic register banks are included in all Z80 and Z180 processors. High-speed exchange between these banks can be used by a program internally, or one bank can be allocated to the mainline program and the other to interrupt service routines.

Finally, two Index registers IX and IY allow 'base and displacement' addressing in memory. IX and IY are not included in the register banks on the Z80 and Z180; there is only one copy of each.

# **Memory Management Unit (MMU)**

To the 16-bit, 64 KB memory addressing capability of the Z80, all Z180 processors add a Memory Management Unit (MMU) that expands the addressing capability to 20 bits (1 MB). With the MMU, the 64 KB logical addressing space can be divided into one to three areas of programmable size and location in the 1-MB physical memory space.

#### I/O Space

A separate I/O space includes on-chip and off-chip peripheral devices. On the Z80, I/O space included 8-bit addresses and 256 bytes. All Z180 processors feature an expanded I/O space with 16-bit addresses and 64 KB. The Z80S183/ Z80L183 includes an extensive set of on-chip peripherals in I/O space that can be augmented by external peripherals.

# **Processor Control Registers**

In addition to the data-oriented registers described above, the Z80S183/Z80L183 processor includes several other control registers. Unlike the registers in I/O space, which are described in Section 4, these control registers have no addresses, but are used implicitly in certain processor operations.

## Program Counter (PC)

This 16-bit register tracks program execution by the processor that automatically increments PC while fetching instructions. The processor stores PC on the stack when it executes a CALL or RST instruction, or an interrupt or TRAP occurs. The processor loads PC with a new value when it executes a JUMP, CALL, RST, or RET instruction, and when an interrupt, Trap, or Reset occurs. PC resets to 0000.

#### Stack Pointer (SP)

The processor decrements this 16-bit register by 2, and stores a 16-bit value in memory at this updated address, when it executes a PUSH, CALL, or RST instruction, and when an interrupt or Trap occurs. The processor fetches a 16-bit value from memory at the address in SP, and then increments SP by 2, when it executes a POP, RET, RETI, or RETN instruction. Software can store the value in SP in memory, load SP from memory or another register, or load it with a constant/immediate value. Further, software can add or subtract the value in SP to or from another register, and can increment or decrement SP. Finally, software can exchange the 16-bit value in memory, to which SP currently points, with the contents of a 16-bit register. SP resets to 0000B.

# Flags (F)

The processor includes two Flag registers each containing six bits, named Zero (Z), Carry (CF), Sign (S), Parity or Overflow (P/V), Half-Carry (HC), and Add/Subtract (N). Certain flags are automatically updated as part of executing certain instructions. Subsequent instructions can then use the flags, either as an operand (ADC, SBC, DAA), or to determine whether to perform a JUMP, CALL, or RET operation. The flags can be saved on the stack with a PUSH instruction, or restored from the stack with a POP instruction. The two sets of flag registers are paired with the two (A) accumulators; the current pair is toggled by the EX AF, AF' instruction.

#### Interrupt High Address (I)

The contents of this register are used as the eight high-order address bits, when the processor fetches the address of an interrupt service routine from memory, for an interrupt from the INTI or INT2 pin, or from an on-chip peripheral. The I register points to a table of interrupt service routine addresses that starts at a 256-byte boundary in the 64 KB logical address space. The I register resets to 0, and can be read or written by the dedicated instructions LD A, I and LD I, A.

# R Counter (R)

On the Z8018x family processors, this register contains a count of executed fetch cycles. R resets to 0, and can be read or written by the dedicated instructions LD A, R and LD R, A.

# Observing Read Data from On-Chip Devices

Bit 7 of the Output Control Register (OCR, illustrated on page 89) determines whether the Z80S183/Z80L183 drives data from on-chip ROM, RAM, and I/O registers, onto the D7–D0 pins for debugging and monitoring purposes. When this bit is 0, as it is after a reset, the D7–D0 pins remain in high-impedance state during read cycles from on-chip devices, saving power.

When software sets this bit to 1 during device initialization, the Z80S183/Z80L183 drives read data from on-chip devices onto D7–D0, allowing it to be captured by debugging instruments such as logic analyzers.

## **Illegal Instruction Traps**

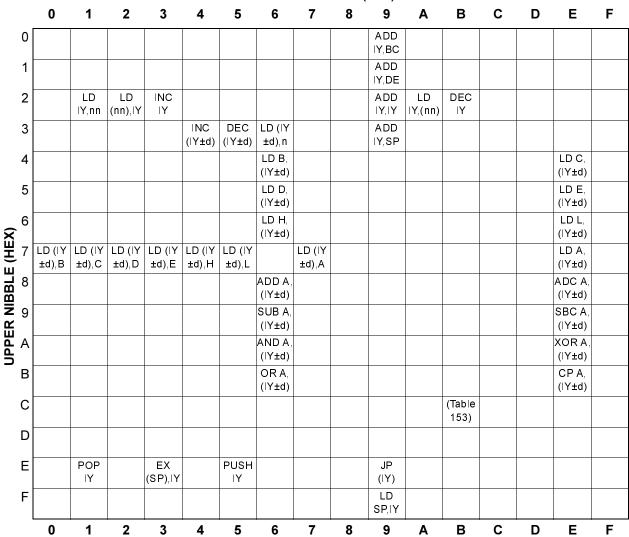

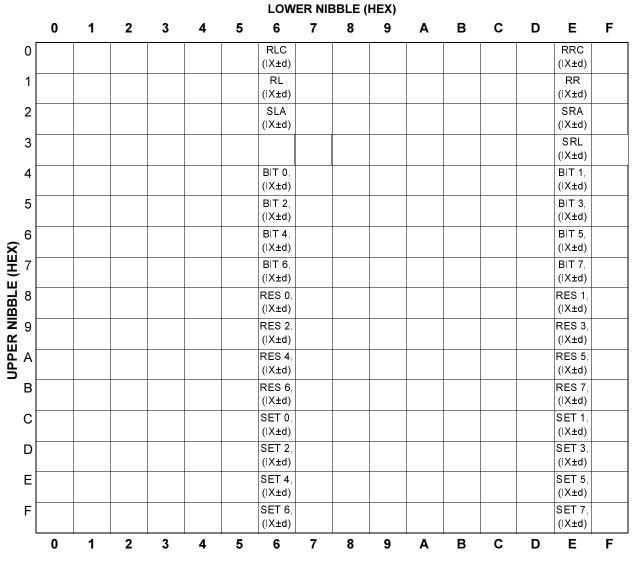

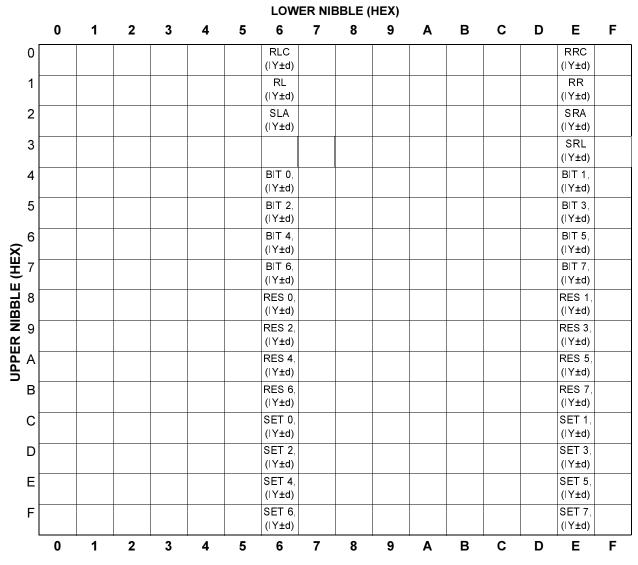

Like most processors, the defined instruction set for the Z8018x family does not fully cover all possible sequences of binary values. The Op Code maps, in the section, "Op Code Map" on page 175, include numerous blank cells. These cells represent Op Code sequences for which no operation is defined, and are commonly called *illegal* instructions.

When a Z80S183/Z80L183 or other Z8018x processor fetches one of these sequences, it performs a Trap sequence as follows:

- 1. The Trap bit is set to 1 when an undefined Op Code is fetched.

- The UFO bit (ITC Bit 6) toggles to indicate the starting address of the undefined Op Code in the event that the instruction is two or three bytes long. This action is necessary because the Trap may occur on either the second or third byte of Op Code.

- When the UFO bit is set to 0 when a Trap interrupt occurs, the first undefined Op Code must be interrupted as the stacked PC-1. When UFO is 1, the first undefined Op Code address is stacked PC-2.

- The processor decrements the Stack Pointer (SP) by 2 and stores the 16-bit logical address from PC, in memory at the new SP address. This address points to the last byte of the illegal Op Code sequence.

- 4. The processor then clears PC and resumes execution at logical address 0000.

#### Trap Handling

The code at logical address 0000B can optionally store the value of SP in memory, and then set SP to an area of memory dedicated to its private stack.

13

In all cases, the trap-handling routine stores as many registers among AF, BC, DE, HL, IX, and IY as it may use, by pushing them onto the stack. A general-purpose routine stores all of these registers, those in the alternate set, the value of I, and the state of the Interrupt Enable flag.

Next, the Trap-handling code distinguishes among the four events that can bring execution to address 0000B:

- A Reset

- A Trap

- An RST 0 instruction

- A program error, such as a JUMP to a null pointer

The code detects a Trap by reading the Interrupt/Trap Control register (ITC) and checking Bit 7 (Trap). When Bit 7 is 1, a Trap has occurred, and the code handles it as follows:

- 1. Clears the Trap bit by writing a o to Bit 7 of the ITC

- 2. Fetches the PC value stored on the stack

- 3. Examines Bit 6 of the ITC (UFO).

- 4. Decrements the PC value by 1, if the UFO bit is 0; otherwise, decrements it by 2, so that it points to the start of the illegal instruction.

The next action of the trap handling routine depends on the application and its stage of development.

Extending the Instruction Set

Core software can use illegal instructions as extensions to the Z8018x instruction set. To accomplish this, the trap handler must fetch and examine each illegal instruction. When an illegal instruction is an extension, the trap handler performs the extended operation that the instruction indicates. It then advances the stacked PC value over the instruction, restores the saved register values, and returns to the next instruction.

Error Message vs. Restart

Except for these extended instructions, the trap handling software can perform either of the following actions:

- Output an error message and wait for someone to examine the situation and restart the application

- Attempt to restart the application immediately

The former course is more common in the debugging/development stages of an application, while the latter may be more appropriate in the production/deploy-

ment stage. In the latter case, software may log the event for future readout, using an external storage medium or just in memory.

# **Device and Version ID Registers**

Three registers (described on page 85), allow software to determine if it is operating on a Z80S183/Z80L183, as well as the device version. These registers are a mandatory feature of the ZDI interface that is described in "ZiLOG Debug Interface" on page 198, and are also available in I/O space.

I/O addresses 003BH and 003CH read as 01 and 00 respectively, indicating that the Z80S183/Z80L183 is one of the first devices to incorporate a ZDI interface. I/O address 003DH reads as 00 for revision AB, 01 for revision BA, and will feature higher values on future revisions.

# Interrupts

ZiLOG Z80 and Z180 processors have a rich legacy of sophisticated interrupt capabilities. Because of the lack of an I/O Request signal on the Z80S183/Z80L183, its interrupt subsystem is substantially simpler and easier to describe than those of other 8018x devices.

The following topics, which are significant for other 8018x processors, do not apply to the Z80S183/Z80L183:

- INTO Mode 0 and 2 interrupts

- Interrupt acknowledge cycles

- Interrupt daisy chains

- Interrupt Pending and Interrupt Under Service bits

- RETT instructions

## Interrupt Resources in the Z80S183/Z80L183

IEF1 and IEF2

These bits are internal to the processor and are only affected and manipulated by certain specific events:

- A Reset clears IEF1 and IEF2

- An EI instruction sets IEF1 and IEF2

- A DI instruction clears IEF1 and IEF2

- An NMI sequence copies IEF1 to IEF2, then clears IEF1

- A maskable interrupt clears IEF1 and IEF2

- An LD A, I or LD A, R instruction copies IEF2 to the P/V flag

- An RETN instruction copies IEF2 to IEF1

When IEF1 is 1, RESET and BUSREQ condition on the OPMODE pins are both High, and no falling edge has occurred on NMT, the Z80S183/Z80L183 checks for maskable interrupt requests from external pins and on-chip peripherals, as it completes each instruction, or each instruction iteration for HALT, the block I/O instructions, block move instructions, and block scan instructions.

## The I Register

The Z80S183/Z80L183 uses the contents of this register as A15–8 of the logical address for fetching interrupt service routine addresses from memory, in response to interrupt requests on INTI and INT2, and from internal peripherals.

See "Interrupt Registers" that starts on page 92 for other registers associated with interrupts.

# The IL Register

The Z80S183/Z80L183 uses bits 7-5 of this register as A7–5 of the logical address for fetching interrupt service routine addresses from memory, in response to interrupt requests on INTI and INT2, and from internal peripherals.

The Interrupt/Trap Control Register (ITC)

Bits 2-0 of the ITC are individual Enable bits for the <u>INT2</u>, <u>INT1</u>, and <u>INT0</u> pins, respectively. They reset to <code>001B</code>, so that requests on <u>INT0</u> can be enabled by an <code>EI</code> instruction after Reset.

Interrupt Edge Register (IER)

By reading this register, software detects the current state of the INT2 and INT1 pins, and whether an edge has been detected on each. Other bits in the IER select whether each of these pins is low-level sensitive, or rising- and/or falling-edge sensitive.

# Nonmaskable Interrupt (NMI)

The Z80S183/Z80L183 latches falling edges on the NMI pin. A falling edge clears the DME bit in the DMA Status register (DSTAT), disabling the on-chip DMA channels. Only a Low on RESET or ON BUSREQ takes precedence over NMI. Unless RESET or BUSREQ is Low, the Z80S183/Z80L183 checks for a falling edge on NMI as it completes each instruction (each instruction iteration of HALT, the block I/O instructions, block move instructions, and block scan instructions), and performs an NMI sequence if a falling edge has occurred.

BUSREQ is a conditional state of the OPMODE0 and OPMODE1 pins.

An NMI sequence includes 4 steps:

- 1. The processor copies the state of the IEF1 bit to IEF2.

- 2. It clears IEF1 to prevent maskable interrupts.

- 3. It decrements SP by 2, and stores the logical address in the PC in memory at the new address in SP. For most interrupts, this value is the address of the instruction the processor would have executed next, had no interrupt occurred. When the processor was stopped by HALT or SLP, this value is the address of the next instruction. In the event of an incomplete block transfer, block scan, or block I/O instruction, this value is the address of the instruction.

- 4. The processor loads 0066H into PC, and resumes execution from that logical address.

# NMI Handling

NMI routines fall into two categories, based on whether the external hardware that drives NMI is capable of producing another falling edge on the pin, before the NMI service routine has completed its execution and returned to the interrupted process. The case when the NMI is not capable of producing another falling edge is called *Single Edge Guaranteed*. The case when the NMI *can* produce another falling edge is called *Repeated Edge Possible*. Debug monitors, which may display the state of the interrupt process, fall into the Repeated Edge category.

#### Single Edge Guaranteed

An NMI routine in this category is similar to other interrupt service routines. This routine has the option of storing the contents of SP in memory and loading SP with the address of a memory area that is dedicated for the stack. In any case, this routine stores as many of the registers as it may use during its execution.

## Repeated Edge Possible

An NMI routine in this category starts with a PUSH AF instruction, then LOAD A from a dedicated location in memory that indicates whether the interrupted process is the NMI routine. When this location indicates that the process is the NMI routine, it immediately performs a POP AF and then a RETN instruction, to return to its former execution.

When the *in NMI* location is cleared, software sets it to 1. Then, if the NMI routine performs either of the following:

- Places a DI instruction in a Save The Registers routine that it shares with other means of entry

- Displays the I register or the interrupt-enable state of the interrupted process, and allows a user/programmer to change these (in essence, a debug monitor)

it performs LD A, I and PUSH AF instructions. This stores the I register at the address in SP plus one, and the interrupt enabled state (IEF2) in the P/V flag and in Bit 2 of the memory location pointed to by SP.

When the NMI routine uses a common *Save The Registers* subroutine that it shares with other entry points, the save subroutine can perform a DI instruction to prevent interruption by maskable interrupts.

The NMI routine has the option to store the SP value in a dedicated location in memory, and load SP with the address of a dedicated NMI stack area.

In any case, the NMI routine must PUSH as many other registers as it uses. A debug monitor typically performs PUSH operations on all registers in both banks, so that it can display them.

# Reenabling The DMA Channels

In an NMI service routine in an application that uses the DMA channels, software next reads the DSTAT register and reenables any DMA operation that was in progress, as described in the section "NMI and DME" on page 47.

# Exiting The NMI Routine

On completion of its processing, an NMI routine restores the saved registers. When the routine used its own stack area, it then restores the SP value of the interrupted process. When the routine sets an in NMI memory location on the way in, it clears this location to 0.

NMI routines that did not save the I register and IEF2 state at the start, can conclude with POP AF and RETN instructions. RETN copies the state of IEF2 back into IEF1, restoring the interrupt enable state of the interrupted process.

NMI routines that saved I and IEF2 at the start, conclude with a POP AF for the saved I register and IEF2 bit. Then an LD I,A, followed by a JP V to a POP AF, EI, RET sequence. The JP is followed by LD I,A, POP AF, and RET instructions.

#### INTO Mode 1

The Z80S183/Z80L183 can only handle interrupts requested on the INTO pin in Mode 1. All Z80S183/Z80L183 applications that enable interrupts and do not tie INTO High, must include an IM 1 instruction before the first EI instruction.

The Z80S183/Z80L183 performs an INTO interrupt sequence at the end of an instruction (each instruction iteration for HALT, the block I/O instructions, block move instructions, and block scan instructions), if all of the following are true:

- INTO is Low

- Bit 0 of the Interrupt/Trap Control register is 1 to enable INTO

- The IEF1 bit is set to 1 to enable interrupts in general

- RESET and BUSREQ are both High, and a negative edge on NMI has not been detected.

- Note: BUSREQ is a conditional state of the OPMODE0 and OPMODE1 pins.

When all of these conditions occur simultaneously, the Z80S183/Z80L183 responds as follows:

- 1. It clears IEF1 and IEF2 to prevent further interrupts.

- 2. It decrements SP by 2, and stores the contents of PC in memory at the new address in SP. This value is typically the address of the instruction the processor would have executed next, if no interrupt had occurred. When the processor is stopped by HALT or SLP, this value is the address of the next instruction. In the event of an incomplete block transfer, block scan, or block I/O instruction, this value is the address of the instruction.

- 3. It loads 0038H into PC, and resumes execution from that logical address.

# Interrupt Handling

Any Interrupt Service Routine (ISR) has the initial option of saving the contents of SP in memory, and loading SP with the address of a memory area that is dedicated to its stack. Most interrupt service routines do not use this option.

An INTO ISR must save the contents of the registers it uses, using PUSH and/or EX AF, AF' and EXX instructions.

When the application includes a mechanism for allowing nested interrupts, the ISR can begin as specified by that mechanism, leading to an IE instruction that allows the ISR to be interrupted by other interrupts. Most applications do not allow for nested interrupts.

The ISR next reads status registers from each device that can request an interrupt on INTO, to identify the cause of the interrupt. The ISR must process each interrupting device according to this status, and the device and application requirements.

Many ISRs read data from interrupting device(s), or write data to interrupting device(s). In addition, the ISRs can write registers in these devices, to modify its mode, status, or operation.

When interrupt processing is complete, if nested interrupts were allowed, the ISR ends as specified by the nesting mechanism. When nested interrupts were not allowed, the ISR restores the saved registers and concludes with EI and RET instructions.

The Z80 and Z80180 instruction sets include an RETI instruction that is used for servicing Z80 peripherals. Since the Z80S183/Z80L183 includes no such peripherals, nor does it allow them to be connected externally, there is no reason to conclude a Z80S183/Z80L183 ISR with an RETI. RET is both shorter and faster than RETI, and fills the same function.

# INT1 and INT2

The Z80S183/Z80L183 performs an <u>INTI</u> or <u>INT2</u> interrupt sequence at the end of an instruction (each instruction iteration for <u>HALT</u>, the block I/O instructions, block move instructions, and block scan instructions), if all of the following are true:

- INTI and/or INT2 meets the condition specified for it in the Interrupt Edge Control register (low level, rising edge, falling edge),

- Bit 2 or 1 of the Interrupt/Trap Control register (ITC) is 1 to enable this pin

(if both pins are enabled and both pins meet the specified condition, INTI

takes precedence over INT2),

- IEF1 is 1, to enable interrupts in general,

- INTO is High or Bit 0 of the ITC is 0,

- RESET and BUSREQ are High, and

- A negative edge on MMI has not been detected.

- Note: BUSREQ is a conditional state of the OPMODE0 and OPMODE1 pins.

When all of these conditions occur simultaneously, the Z80S183/Z80L183 responds as follows:

- 1. It clears IEF1 and IEF2 to prevent further interrupts.

- 2. It decrements SP by 2, and stores the contents of PC in memory at the new address in SP. Typically, this value is the address of the instruction the processor would have executed next, if no interrupt had occurred. When the processor was stopped by HALT or SLP, this value is the address of the next instruction. In the event of an incomplete block transfer, block scan, or block I/O instruction, this value is the address of the instruction.

- 3. Next, the processor forms a logical memory address using the contents of the I register as A15–8, Bits 7–5 of the IL register as A7–5, and 0 as A4–0 for TNTT or 2 in A4–0 for TNTT

4. Finally, the processor fetches a 16-bit logical address from memory at that logical address, loads it into PC, and resumes instruction execution from

# INT1-2 Handling

there.

All of the considerations noted for INTO ISRs in "Interrupt Handling" on page 18, also apply to ISRs for INTI and INT2. One additional step is required when the pin is edge-triggered: read the INT2-1 Interrupt Edge Register (IECR), and write the value (including 1 in Bit 5 or 4) back to the IECR to clear the edge-detection logic.

# On-Chip Interrupts

The Z80S183/Z80L183 performs an interrupt sequence for an on-chip device at the end of an instruction (each instruction iteration for HALT, the block I/O instructions, block move instructions, and block scan instructions), if all of the following are true:

- An interrupting condition has occurred in the device

- That condition is interrupt-enabled in the device's registers

- IEF1 is 1, to enable interrupts in general

- No higher-priority internal device is requesting an interrupt (see Table 5 below for the relative priorities of internal devices)

- Neither <u>INT1</u> nor <u>INT2</u> is interrupting

- INTO is High or Bit 0 of the ITC is 0

- RESET and BUSREQ are both High

- A negative edge on MMI has not been detected.

**Note:** BUSREQ is a conditional state of the OPMODE0 and OPMODE1 pins.

When all of these conditions occur simultaneously, the Z80S183/Z80L183 responds as follows:

- 1. It clears IEF1 and IEF2 to prevent further interrupts.

- 2. It decrements SP by 2, and stores the contents of PC in memory at the new address in SP. Typically, this value is the address of the instruction the processor would have executed next, if no interrupt had occurred. When the processor was stopped by a HALT or SLP instruction, this value is the address of the next instruction. For an incomplete block transfer, block scan, or block I/O instruction, this value is the address of the instruction.

- 3. Next, the processor forms a logical memory address using the contents of the I register as A15–8, Bits 7–5 of the IL register as A7–5, and the value corresponding to the interrupting device as A4–0.

- 4. Finally, the processor fetches a 16-bit logical address from memory at that logical address, loads it into PC, and resumes instruction execution from there.

# **On-Chip Interrupt Handling**

The only difference between handling an on-chip interrupt, and the considerations noted for INTO ISRs in "Interrupt Handling" on page 18, is that the ISR for an on-chip device never needs to differentiate among several devices connected to an INT pin, only among interrupt sources within the device.

Table 5. Interrupt Offsets and Priorities

| Device                              | Priority | A4–0 Offset |

|-------------------------------------|----------|-------------|

| INT1 pin                            | highest  | 0           |

| INT2 pin                            |          | 2           |

| PRT0                                |          | 4           |

| PRT1                                |          | 6           |

| DMA0                                |          | 8           |

| DMA1                                |          | 10 = 0AH    |

| CSI/O                               |          | 12 = 0CH    |

| ASCI0                               |          | 14 = 0EH    |

| ASCI1                               |          | 16 = 10H    |

| Programmable Output Generator (POG) |          | 18 = 12H    |

| Port A                              |          | 20 = 14H    |

| Port D                              |          | 22 = 16H    |

| A/D Converter                       |          | 24 = 18H    |

| Real Time Clock (RTC)               |          | 26 = 1AH    |

| Reserved                            |          | 28 = 1CH    |

| ZiLOG Debug Interface (ZDI)         | lowest   | 30 = 1EH    |

NOTE: Devices are ordered identically with respect to interrupt priority and offset value

# Memory

Z8018x family processors include a 64 KB logical memory space in which software operates, and a 1 MB physical memory address space in which on-chip and external memory reside. The Memory Management Unit (MMU) translates 16-bit logical addresses to 20-bit physical addresses dynamically, as part of each memory access.

# **Memory Structure**

On the Z80S183/Z80L183, memory is divided into four categories:

- 1 KB of on-chip ROM

- 2 KB of on-chip RAM

- External ROM or Flash memory using on-chip decoding

- External RAM using on-chip decoding

Table 30 on page 91 describes the System Configuration Register (SCR) that includes bits that enable or disable each of these four memory categories. Software designers must be cautious when programming this register, to not disable the memory in which the current code sequence resides.

On-chip ROM can be enabled or disabled at Reset time, by the state of the OPMODE1-0 pins. These pins control the initial state of the on-chip ROM Enable bit in the SCR. When on-chip ROM is enabled, it occupies physical addresses

The last 256 bytes of on-chip RAM are always accessible to the Programmable Output Generator (POG) module. When processor access to on-chip RAM is enabled, another bit in the SCR controls whether A19–16 are included in address decoding for on-chip RAM.

The on-chip address decoder for external ROM or Flash memory decodes from physical address 00000 through a programmable upper limit. When external ROM is enabled, memory accesses at addresses below the upper limit, drive the ROMRD or ROMWR pin Low. (Among the capabilities of the ROMWR pin are programming of Flash memories.)

The on-chip address decoder for external RAM decodes between programmable lower and upper limits. When external RAM is enabled, memory accesses at addresses between these two limits, drive the RAMRD or RAMWR pin Low.

When software programs the Memory Chip Select Logic and System Configuration Register so that some addresses do not match either the ROM or RAM chip selection, accesses to these addresses do not appear on the external bus. Avoid this possibility by programming the active chip selects to cover the entire memory address space.

Instructions can specify a memory address in several ways. Z80S183/Z80L183 addressing modes include:

# Relative Addressing

JR and DJNZ instructions include a signed 8-bit displacement that specifies a range of addresses –126 to +129 from the Op Code, to which program control can be transferred.

# **Direct Addressing**

In this mode, instructions include a 16-bit logical address.

# Register Indirect Addressing

In this mode, the address is taken from one of the register pairs BC, DE, or HL.

#### Indexed Addressing

In this mode, instructions include an 8-bit signed displacement from the address in an index register IX or IY.

Other contexts in which memory is accessed include instruction fetching, interrupts, and DMA operations.

#### **Memory Management Unit (MMU)**

The MMU translates the 16-bit addresses used by software, called *logical* addresses, into 20-bit *physical* addresses, as part of all memory accesses performed by the processor. The MMU has no effect on accesses performed by the DMA channels that include 20-bit address registers. It also has no effect on addresses in I/O space that always have A19–16 o.

The MMU resets to a state in which it has no effect on addresses in processor cycles, passing A15–0 through without change and keeping A19–16 o. When an application needs 64 KB of memory or less, it ignores the MMU.

Even when the MMU has been programmed to perform active address transactions, it passes A11  $_{\odot}$  from the logical to the physical address. The MMU manages memory in 4 KB blocks.

The section titled "MMU Registers" on page 94, describes the registers associated with the MMU.

#### **MMU** Operation

The MMU compares Bits 15–12 of each logical address to two 4-bit fields in its Common/Base Address Register (CBAR), in an unsigned manner.

When Bits 15–12 of a logical address are less than the value in Bits 3–0 of the CBAR, the MMU considers the address to be in Common Area 0. For these

24

addresses, it passes Bits 15–12 to the A15-12 pins unchanged, and sets pins A19–16 to  $_{0}$ .

When Bits 15–12 of a logical address are greater than or equal to the value in Bits 3–0 of the CBAR, but are less than the value in Bits 7–4 of the CBAR, the MMU considers the address to be in the Bank Area. For such addresses, it adds the value in its 8-bit Bank Base Register (BBR) to Bits 15–12 of the logical address, and outputs the 8-bit sum on pins A19–12.

When Bits 15–12 of a logical address are greater than or equal to the value in Bits 7–4 of the CBAR, the MMU considers the address to be in Common Area 1. For such addresses, it adds the value in its 8-bit Common Base Register (CBR) to Bits 15–12 of the logical address, and outputs the 8-bit sum on A19–12.

The value in Bits 7–4 of the CBAR must never be less than the value in Bits 3–0 of the CBAR.

#### **MMU** Configurations

In the general case, the MMU divides the 64 KB logical memory space into three parts, with Common Area 0 located at the start of the

1 MB physical address space, and the Bank Area and Common Area 1 relocatable to other parts of the physical address space. These three parts are under control of the Bank Base Register and Common Base Register, respectively.

Certain combinations of values in the CBAR result in the logical address space being divided into fewer active areas:

- When the CBAR contains 0, all logical addresses fall into Common Area 1, and are relocated to a contiguous 64 KB area starting at the address in the CBR times 4096.

- When CBAR3-0 are 0 but CBAR7-4 are non-zero, the Bank Area and Common Area 1 are active. Logical addresses less than (CBAR7-4) \*4096 are relocated by the Bank Base Register, while other addresses are related by the Common Base Register.

- When CBAR7-4 and CBAR3-0 are equal and not 0, Common Area 0 and Common Area 1 are active. Logical addresses less than (CBAR3-0) \*4096 are not relocated, and map to the start of physical memory. Other addresses are relocated by the Common Base Register.

#### The MMU After Reset

Because the CBAR resets to 11110000B, logical addresses 0000–EFFFH are in the Bank Area and F000–FFFFH are in Common Area 1 after Reset. But since the BBR and CBR both reset to 0, the MMU passes all logical addresses through without change, with A19–16 all 0.

# **On-Chip ROM**

Bit 7 in the System Configuration Register (page 91) controls whether physical addresses 00000-003FFH access on-chip ROM or external memory. A 1 in this bit enables on-chip ROM. At reset, this bit is set to 1 if the OPMOD1 pin is High and the OPMOD2 pin is Low. Otherwise, this bit is cleared to 0.

# **On-Chip RAM**

Bits 6–5 in the System Configuration Register control processor access to on-chip RAM. When Bit 6 is 0, on-chip RAM is disabled. When Bits 6–5 are 10, on-chip RAM does not decode Bits 19–16 of physical addresses, and responds to all physical addresses with A15–11 all 1: xF800 through xFFFFH. When Bits 6–5 are 11B, on-chip RAM responds to physical addresses with A19–11 all 1: addresses FF800–FFFFFH.

The Programmable Output Generator (POG) can always read the last 256 bytes of on-chip RAM, regardless of Bits 6–5 in the SCR.

# **External ROM/Flash Decoding**

Bit 4 of the System Configuration Register enables or disables an on-chip address decoder for external ROM or Flash memory. When this bit is 1, memory accesses at physical addresses less than the upper limit programmed in the ROM Boundary Register (ROMBR, page 97), drive the ROMRD or ROMWR pin Low. (The ROMWR pin can be used to program Flash memories.)

When SCR Bit 4 is 1,  $\overline{\text{ROMRD}}$  or  $\overline{\text{ROMWR}}$  goes Low for addresses with A19–12 less than or equal to the contents of ROMBR, that is, for addresses less than (ROMBR+1)\*4096.

# **External RAM Decoding**

Bit 3 of the System Configuration Register (page 91) enables or disables an onchip address decoder for external RAM. When this bit is 1, memory accesses at physical addresses between the lower limit programmed in the RAM Lower Bound Register (RAMLBR), and the upper limit programmed in the RAM Upper Bound Register (RAMUBR), drive the RAMRD or RAMWR pin Low. These registers are described on page 98.

When SCR Bit 3 is 1, RAMRD or RAMWR goes Low for addresses with A19–12 greater than or equal to the contents of RAMLBR, and less than or equal to the contents of RAMUBR, that is, for addresses A in the range

(RAMLBR)\*4096 < A < (RAMUBR+1)\*4096

#### **Wait State Generators**

The Z80S183/Z80L183 includes two registers that control automatic insertion of Wait States into memory and I/O accesses.

The DMA/Wait Control register (DCNTL) is shown on page 121, and is present on all 8018x family members. DCNTL is one of the DMA registers, but the Wait States that it controls apply to processor cycles as well as to those generated by the DMA channels.

Bits 7–6 select the number of wait states for all memory accesses.

Bits 5–4 select the number of wait states for I/O accesses other than those to 180 registers. The Z80S183/Z80L183 interprets both fields as a binary number of wait states:

| Bit 5 | Bit 4 | Wait State    |

|-------|-------|---------------|

| 0     | 0     | 0 Wait States |

| 0     | 1     | 1 Wait State  |

| 1     | 0     | 2 Wait States |

| 1     | 1     | 3 Wait States |

The Wait State Generator Control register (WSGCR) is described on page 96, and is unique to the Z80S183/Z80L183.

Bits 7–6 control the number of Wait States for memory accesses in the  $\overline{ROMRD}/ROMWR$  address range.

Bits 5–4 control the number of Wait States for memory accesses in the RAMRD/RAMWR address range.

Bits 3–2 control the number of Wait States for other memory accesses, but these cycles do not appear on the external bus.

The Z80S183/Z80L183 interprets these fields as follows:

| Bit 3 | Bit 2 | Wait State    |

|-------|-------|---------------|

| 0     | 0     | 0 Wait States |

| 0     | 1     | 1 Wait State  |

| 1     | 0     | 2 Wait States |

| 1     | 1     | 4 Wait States |

#### No DRAM Refresh

ZiLOG's Z80 and Z8018x families have traditionally included dynamic RAM refresh logic. This logic is identical on all Z8018x devices including the Z80S183/Z80L183, but the Z80S183/Z80L183 does not have a RFSH pin with which to signal refresh cycles, nor a Refresh Control Register.

# Input/Output

The Z80S183/Z80L183 includes an I/O space that is distinct from memory space. I/O space is accessed by means of IN and OUT instructions rather than LD, PUSH, POP, and other instructions that access memory space. The MMU passes addresses in I/O space through without change; such addresses always have A19–16 all  $_{0}$ .

#### I/O Instructions

The original Z80 featured a 256-byte I/O space. The following instructions are specific to the Z80's 256-byte I/O space, and should not be used on the Z80S183/Z80L183 except to access external I/O devices that do not decode A15–8:

```

OUT (port), A

IND

INDR

INI

INIR

OTDR

OTIR

OUTD

OUTI

```

The following instructions ensure that A15–8 are all 0, and can be used to access the Z80S183/Z80L183's on-chip I/O registers, as well as external devices that decode A15–8 as all 0:

```

INO r, (port)

OUTO (port), r

OTDM

OTDMR

OTIM

OTIMR

```

The following instructions drive A15–0 from the BC register pair, and can be used to access the full 64 Kbyte I/O space:

```

IN r, (C)

OUT (C), r

```

PS000503-1100

The following instruction can access the entire 64 Kbyte I/O space, by pre-loading the MS 8 bits of the address into A. (This step is unnecessary for external devices that do not decode A15-8.)

# Relocating the 80180 Registers

The section, "Registers Summary" on page 80, describes how the Z80S183/ Z80L183's I/O registers are divided into 80180-registers and Z80S183/Z80L183specific registers. The latter registers are always located in the range 0040-007FH. After a reset, the 80180 Registers are located in the range 0000-003FH, but bits 7-6 of the I/O Control Register (page 88) allow software to relocate the 80180 Registers to higher addresses:

| IOCR 7-6 | 180 Register Addresses   |

|----------|--------------------------|

| 00       | 0000-003FH               |

| 01       | Reserved, do not program |

| 10       | 0080-00BFH               |

| 11       | 00C0-00FFH               |

Relocating the 180 registers is included to ease porting of Z80 applications to the Z8018x family.

**Caution:** Use this facility with caution because certain tools may assume that the 80180 Registers are located in the 0000-003FH range. Those tools need to be reconfigured (reassembled, recompiled) to allow for relocated 180 Registers.

## Write Enable/Lock for Critical Registers

Some registers are protected from inadvertent modification by software. Writing a OBH to the Watch-Dog Timer Command Register (WDTCR, page 124) sets Bit 0 of the Watch-Dog Timer Master register to 1 (WDTMR, page 123) and enables writing to these registers. Writing any other value to WDTCR clears Bit 0 of the WDTMR to 0 and prevents writing to these registers.

The Write Enable state has no effect on reading the registers protected by this mechanism that include.

- System Configuration register (SCR, page 91)

- Power Control register (PCR, page 90)

29

- Port A-D Data Direction registers (DDRA-D, pages 100–108)

- All Real Time Clock registers (pages 131–137)

## I/O Chip Selects

When Bit 2 in the System Control Register (SCR) is 1, the Z80S183/Z80L183 drives the  $\overline{\texttt{IOCSI}}$  pin for accesses to I/O addresses 0080-87H, and drives the  $\overline{\texttt{IOCS2}}$  pin Low for accesses to 0088-8FH. When SCR Bit 2 is 0,  $\overline{\texttt{IOCSI}}$  and  $\overline{\texttt{IOCS2}}$  remain High at all times.

#### I/O Waits

Bits 5–4 of the DMA/Wait Control Register can be used to insert Wait States into I/O cycles with the Z80S183/Z80L183-specific registers at addresses 0040–007FH, and into I/O cycles with external devices. This field is interpreted as a binary number of wait states:

| Bit 5 | Bit 4 | Wait State    |

|-------|-------|---------------|

| 0     | 0     | 0 Wait States |

| 0     | 1     | 1 Wait State  |

| 1     | 0     | 2 Wait States |

| 1     | 1     | 3 Wait States |

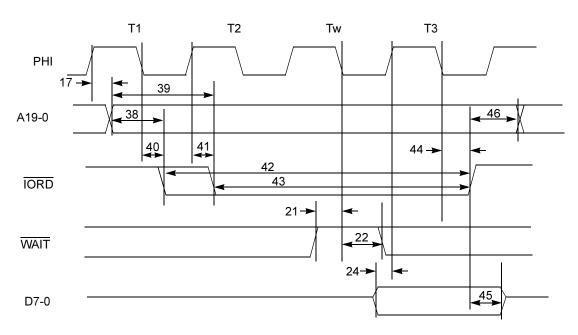

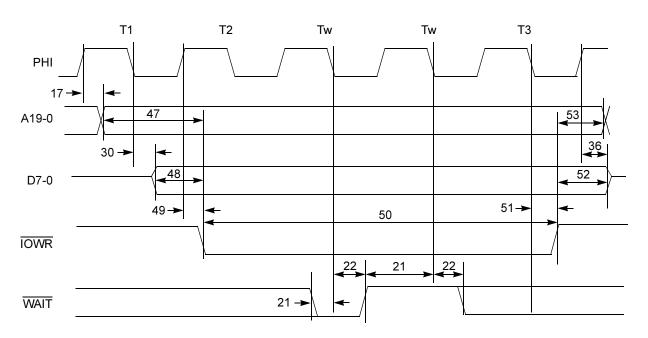

# **IORD** Timing

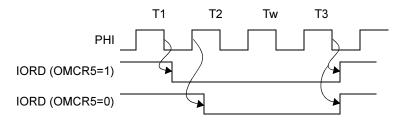

Bit 5 in the Operating Mode Control Register (OMCR, shown on page 87) controls the timing of the  $\mathtt{IORD}$  signal when software reads from an external I/O device. When this bit is 1, as it is after a reset, the Z80S183/Z80L183 drives  $\mathtt{IORD}$  Low from the falling edge of PHI in the T1 clock cycle. When this bit is 0, it drives  $\mathtt{IORD}$  Low one-half clock cycle later, from the rising edge of PHI at the start of T2. Both cases are illustrated in Figure 3.

On other Z8018x family members, Bits 7 and 6 in the OMCR control how the M1 signal affects Z80 peripheral devices.

Because the Z80S183/Z80L183 does not have an IORQ pin, it cannot be used with Z80 peripherals, and OMCR Bits 7–6 do not matter.

Figure 3. IORD Timing

# **Clock Circuits**

The Z80S183/Z80L183 can be clocked in any of three ways:

- By an external TTL- or CMOS-level clock on the EXTAL pin

- By a crystal connected to its XTAL and EXTAL pins

- By a low-frequency crystal (typically 32.768 KHz) connected to its LFXTAL and LFEXTAL pins

An external clock signal must be free of overshoot or ringing, must make continuous, monotonic, and rapid transitions in both directions, and must meet the minimum High and Low times specified in "AC Characteristics" on page 188.

### **Clock Selection**

Bits 1–0 of the System Configuration Register, which is shown on page 91, select the source of the main device clock (PHI) between the XTAL/EXTAL pins and the LFXTAL/LFEXTAL pins, and in the latter case, a multiplier for the clock:

| SCR 1-0 | PHI source                |  |

|---------|---------------------------|--|

| 00      | XTAL/EXTAL                |  |

| 01      | LFXTAL/LFEXTAL            |  |

| 10      | LFXTAL/LFEXTAL times 1004 |  |

| 11      | LFXTAL/LFEXTAL times 502  |  |

31

Because these bits reset to 00, an application that requires LFXTAL and LFEXTAL must start up using XTAL and EXTAL. The circuit in Figure 6 includes a connection that satisfies this need.

#### Divide-by-2 vs. Direct Option

Regardless of the source of PHI, Bit 7 of the CPU Control Register (CCR, described on page 84) controls whether the Z80S183/Z80L183 uses the signal selected by Bits 1–0 of the SCR directly as PHI, or whether it divides the signal by 2 to obtain PHI.

When CCR Bit 7 is 0, as it is after a reset, the part divides the selected signal by 2. This mode insulates the part against an asymmetric waveform on the selected signal. When CCR Bit 7 is 1, the Z80S183/Z80L183 uses the selected signal directly. In this case, if an external clock is connected to EXTAL, the clock must meet the minimum High and Low times specified in "AC Characteristics" on page 188.

#### **Circuits**

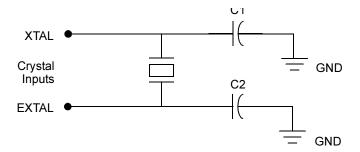

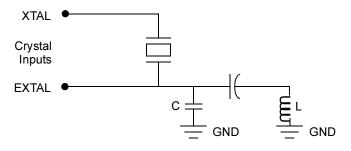

When using a crystal connected to XTAL and EXTAL, locate the crystal as close as possible to the pins. This placement minimizes the trace lengths between the crystal, the pins, and the two capacitors shown in Figure 4, which illustrates the connection of a fundamental mode crystal up to and including 20 MHz. C1 and C2 are 20–30 pF, with 22 pF a typical value.

Figure 4. Fundamental Mode Crystal Circuit ≤ 20 MHz

For frequencies above 20 MHz, use a third-overtone crystal and include an LC tank circuit to filter the fundamental frequency, as shown in Figure 5. Again, it is essential to minimize trace lengths by locating all of the components as close as possible to the XTAL and EXTAL pins.

Figure 5. Third-Overtone Crystal > 20 MHz

A low-frequency crystal can be connected between the LFXTAL and LFEXTAL pins without any other components (see Figure 6). When the LF crystal is used as the clock source for the Real Time Clock, it must be exactly 32.768 KHz.

Figure 6. Low-Frequency Crystal Circuit

## **Crystal Specifications**

The following specifications apply to fundamental mode crystals up to 20 MHz:

- Fundamental, parallel type (AT cut recommended)

- Load capacitance: C<sub>L</sub> = C1 = C2 = 20–30 pF (22 pF typical)

- Equivalent Resistance R<sub>S</sub> ≤ 60 ohms

- $C_{IN} = C_{OUT} = 15-22 pF$

# **Reduced Oscillator Drive Option**

Bit 6 in the Clock Control Register, described on page 83, controls the gain of the XTAL/EXTAL oscillator. When Bit 6 is 0, as it is after a reset, a crystal connected to XTAL and EXTAL is driven strongly, to guarantee that oscillation always starts. This drive is suitable for traditional crystals packaged in HC–49-type packages, but

may be too powerful for crystals packaged for miniaturized applications such as PCMCIA.

To reduce the gain of the oscillator, write a 1 to Bit 6 of the Clock Control Register. This action reduces the drive to about 25% of normal mode, and reduces the maximum oscillator frequency from 33 to 20 MHz.

#### **Reset Conditions**

The effects of Reset on each of the registers in I/O space is described in Tables 18–131 in the section describing "I/O Registers" on page 80. Among processor registers, the following registers and state bits are cleared to 0: PC, SP, I, IEF1, IEF2, R, and F. The following are not changed by Reset: A, B, C, D, E, H, L, IX, and IY.

The Z80S183/Z80L183 resets itself on power-up. When power is applied, the device detects power rising. When the oscillator starts, the Power On Reset circuitry holds the Z80S183/Z80L183 in reset for 2<sup>16</sup> clock cycles, driving RESET Low to provide a reset to external peripherals. This Power On Reset sequence also occurs in response to a rising edge on OPMOD1 pin. When Bit 6 of the Power Control Register (PCR) is 1, a reset is generated in response to a rising edge on PB2/CTS0/PWRUP.

Another possible source of Reset is the Watch-Dog Timer (WDT). See "Watch-Dog Timer" on page 48, for more information on the WDT.

# **Power Management**

The Z80S183/Z80L183's low-power modes are controlled by the Standby and Idle/Quick bits in the CPU Control Register (page 84), the IOSTOP bit in the I/O Control Register (page 88), and execution of SLP and HALT instructions.

The section titled "LOW-POWER Modes" on page 34 describes the low-power modes.

# **Using the Power Control Register**

The Power Control Register (PCR, page 90) is unique to the Z80S183/Z80L183, and offers additional power control options to the board designer and programmer.

CE OUT

This pin can be connected to the CE or CS pin(s) of external RAM, and to an external pullup resistor. The Z80S183/Z80L183 drives this pin Low when Bit 7 of the Power Control Register is 1. Software sets this bit before trying to access external RAM. When PCR Bit 7 is 0, the Z80S183/Z80L183 does not drive CE\_OUT, and

the external resistor pulls it High, which helps safeguard the RAM against modification. Software clears PCR Bit 7 to 0 before entering a LOW-POWER mode.

The RAM and the external pullup can be powered from a supply that is active when the Z80S183/Z80L183 is not powered, for example, from standby power or from a battery.

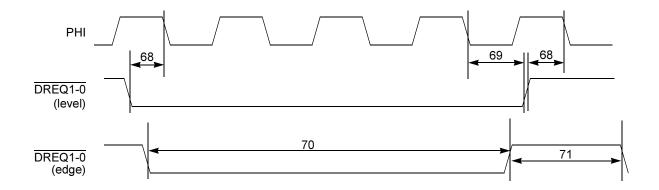

#### PB2/CTS0/PWRUP