PRODUCT BRIEF

# SIX-CHANNEL DOLBY DIGITAL SURROUND PROCESSOR

### **FEATURES**

- Multi-Function

- Decode of six-channel Dolby AC-3 Digital Surround Sound

- Two-channel AC-3 to four-channel Dolby Pro Logic

- Two-channel PCM to four-channel Dolby Pro Logic

- One- or two-channel PCM to two-channel mono or stereo

- Pink noise generator function for testing of all channels

- Programmable center and surround channel delays

- Added power of the programmable ZR38001 core processor for custom product features

- Low-Cost Solution

- Programmable internal I/O clock generators

- Internal oscillator with x2 PLL for use with 33 MHz crystal

- No host microcontroller required

- Simple bit-serial SPI compatible interface for host if used

- Single external memory for digital delay can be byte-wide

- Wait-state generation for low-cost external memory

- 128-pin Plastic Quad Flat Pack (PQFP) packaging

- Flexible System Component

- Internal ROM contains all decoder algorithms

- Control by commands from host microprocessor or the user designed core processor program

- User designed program in external boot-strap ROM, internal masked ROM or down-loaded from host

- User designed program adds product distinctions to industry standard decoder functions

- Flexible Audio Input/Output

- Master or slave I/O with programmable internal clocks

- 16-, 18- or 20-bit word sizes

- Formats: I<sup>2</sup>S, EIAJ, non-delayed data or frameless

- Protocols: AC-3/IEC 958 (S/PDIF) or unformatted

- Sample rates: 44.1 kHz, 48 kHz or 32 kHz

- Software and Hardware PC Development Environment

- On-chip ICE support

- Assembler/Linker

- Software simulator with Microsoft Windows user interface

- PC AT bus hardware development board for real-time algorithm execution and debugging

## **APPLICATIONS**

- The complete solution for Dolby multi-channel decoding for:

- CD and Digital Audio Tape consumer electronics

- Television set-top boxes

- Multimedia computing

- Virtual Reality

- Professional digital audio

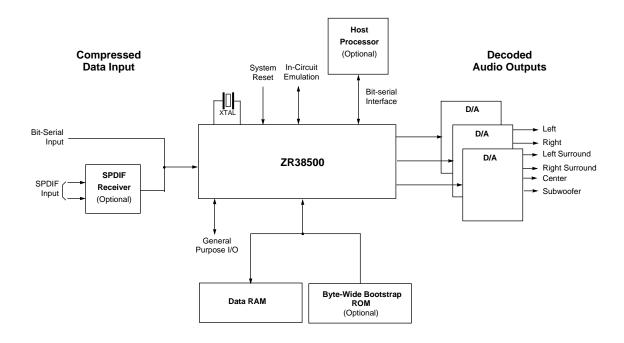

Figure 1. ZR38500 Configuration Diagram

## **GENERAL DESCRIPTION**

The Zoran ZR38001 is the first programmable digital signal processor capable of real-time single-chip decoding of the Dolby Laboratories AC-3 5.1-channel digital surround sound algorithm. The ZR38500 is a derivative design with AC-3 and a selection of Dolby algorithms pre-programmed in internal ROM. Useful in a number of different configurations, it provides even lower cost system solutions than a ZR38001 yet retains the programmability.

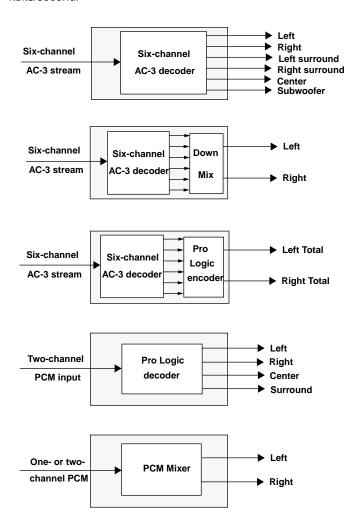

From a compressed digital audio stream (in a variety of formats), the ZR38500 generates all of the signals for virtually all serial audio D/A converters to produce the decoded analog outputs. The available decoding functions, illustrated in Figure 2, are:

- Compressed six-channel Dolby AC-3 to the six decoded channels. Loudspeaker configuration, center and surround delay and dynamic range are all selectable

- Compressed two-channel AC-3 to the four decoded channels of Dolby Pro Logic. Surround delay and loudspeaker configuration are selectable

- Two-channel PCM to the four generated channels of Dolby Pro Logic. Surround delay and loudspeaker configuration are selectable

- One- or two-channel PCM with stereo or mono loudspeaker configuration and mixing selectable.

- An additional function is pink noise generation for system testing on any selected channel.

These functions can be used on their own in a very cost-effective way, but an additional power of the ZR38500 is that they may be embedded in user written code with other functions that execute on the core processor. An additional internal mask-programmable ROM of 1.5 Kwords and/or 1 Kwords of RAM are available for these coded functions.

The ZR38500 is as flexible in its hardware configuration as in its functional operation. Figure 1 shows the possibilities. The basic configuration is the ZR38500 with its clock crystal, a byte-wide RAM for I/O buffering and delay memory, the desired input connection and the appropriate number of output D/A converters.

This basic configuration is all that is required when using a custom mask-programmed version. The user written program in ROM executes the desired functions with the selected parameters after being reset by the system. Control and interaction with the system can take place through the four single-bit user-defined general-purpose I/O ports.

The basic configuration's operation can be achieved without the delay of custom mask-programming by using the optional external byte-wide bootstrap ROM shown. The user code in the ROM is down-loaded after reset and executed from the internal program/data RAM.

If there is a host microprocessor in the system, only the basic configuration need be used. A connection is made with the host

through an inexpensive bit-serial peripheral interface (SPI compatible). User code may be then be down-loaded from the host or the decoder functions and their parameters may be selected through a simple command structure with the ZR38500.

The ZR38500 is also useful in many different digital audio applications because of the flexibility of its input/output ports. Three sample rates of 48, 44.1 and 32 kHz are supported with the processor being selectable as either slave or master for input and outputs separately. Programmable dividers are used when master I/O clocking is derived from the ZR38500's crystal clock. This master clock is output for system use or the input divider can be used with an external clock. Word size can be 16, 18 or 20 bits with single or multiple word frames. Formats can be I<sup>2</sup>S with word select or frame synchronization, EIAJ with LSB justification or ones with non-delayed data among others.

Special protocols supported are the AC-3 data stream in IEC 958 (S/PDIF) format and the continuous or frameless types used in telecommunications. The maximum input data rate is 640 kbits/second.

Figure 2. ZR38500 Decoding Functions.

#### Trademarks:

All brand, product, and company names are trademarks or registered trademarks of their respective companies.