# **Z90356** and **Z90351**

# 64KWord Television Controller with Expanded OSD Features

#### PB000101-TVC1199

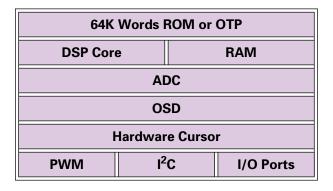

#### **Product Block Diagram**

#### **General Description**

The Z90356 and Z90351 are the ROM and OTP versions of a Digital Signal Processor (DSP)-based TV controller that provide a highly-integrated solution for TV design. With 64 KWords of ROM and 1KWord of RAM, the Z90356 provides high processing power.

This DSP architecture supports expanded On-Screen Display (OSD) features including hardware cursor control, independent left and right shadows, and semi-transparency. In addition, the Z90356 has both fixed and programmable color palettes.

Closed captioning and program blocking provide additional versatility for the TV manufacturer. Relocatable CGROM supports unlimited character sets. The Z90356 is an ideal choice for mid-to-high end TV products for both PAL and NTSC standards.

The Z9035x family consists of three basic devices:

- The Z90356 masked ROM

- The Z90351 One-Time-Programmable device

- The Z90359 In-Circuit Emulation (ICE) chip

In addition, ZiLOG provides a complete development suite for TV product development, which includes emulator, evaluation kit, C-Compiler, Application Programmer Interface (API), ZiLOG Developer Studio (ZDS) software, and font editor. These tools help TV developers work efficiently and effectively with quick time to market.

#### **On-Screen Display Features**

- 16x16, 16x18, and 16x20 pixel matrices

- 2X and 3X character stretch with smoothing

- Unlimited characters with programmable display attributes

- 8 Fixed palettes plus 8 programmable color palettes

- Hardware cursor control

- Independent left/right shadows with color control, shadows on transparent and non-transparent backgrounds

- Semi-transparency support

#### **TV Control Features**

- Six Channel, 4-bit Analog-to-Digital Converter (ADC) which supports:

- Automatic frequency tuning (AFT)

- Analog keypad entry

- Audio level input adjustment

- Vertical Blank Interval (VBI) decoding

- Six Pulse Width Modulators (PWM) to control video, audio, and tuners

- Master/Slave I<sup>2</sup>C bus interface

- Twenty-five programmable I/Os

- On-chip Horizontal Synchronization (H<sub>SYNC</sub>) and Vertical Synchronization (V<sub>SYNC</sub>) generation circuits

- On-chip Infrared (IR) capture register

#### **Controller Features**

- 16-bit Single-cycle instruction execution

- Phase Lock Loop (PLL), controlled by a 32KHz external crystal

- 64KWord ROM or OTP with re-locatable Character Generation ROM

- 1KWord of RAM

- 52-pin SDIP package

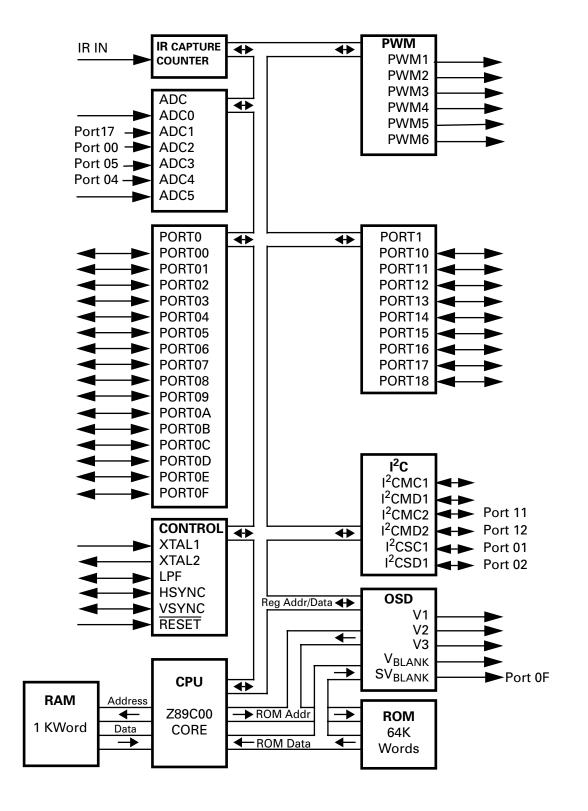

#### Block Diagram of Z90356 and Z90351

2

## **Pin-Outs and Pin Direction**

| Port16/SCLK   1   52   Port15/B1     IRIN   2   51   Port14/B0     Port0C   3   50   Port13/G1     Port0B   4   49   Port18/G0     Port0A   5   48   Port08/R1 | <b>A A A A A A A A A</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| IRIN □ 51 □ Port14/B0   Port0C □ 3 50 □ Port13/G1   Port0B □ 4 49 □ Port18/G0                                                                                  |                          |

| Port0C     □ 3     50     □ Port13/G1       Port0B     □ 4     49     □ Port18/G0                                                                              |                          |

| ← Port0B □ 4 49 □ Port18/G0 <                                                                                                                                  |                          |

|                                                                                                                                                                |                          |

|                                                                                                                                                                |                          |

| Port09 □ 6 47 □ Port10/R0                                                                                                                                      |                          |

| ← Port0D □ 7 46 □ PWM6 →                                                                                                                                       |                          |

| ← Port07/CSYNC □ 8 45 □ PWM5                                                                                                                                   |                          |

| Port06/CNTR □ 9 Z90356 44 □ PWM4                                                                                                                               |                          |

| → Port03 □ 10 Or 43 □ PWM3                                                                                                                                     |                          |

| Port01/I2CSC □ 11 Z90351 42 □ PWM2 →                                                                                                                           |                          |

| ← Port02/I2CSD □ 12 41 □ PWM1 →                                                                                                                                |                          |

|                                                                                                                                                                |                          |

|                                                                                                                                                                |                          |

| → AGND □ 15 38 □ GND →                                                                                                                                         |                          |

| → ADC5 □ 16 37 □ XTAL2 →                                                                                                                                       |                          |

| ← → Port04/ADC4 □ 17 36 □ XTAL1 ←                                                                                                                              |                          |

| Port05/ADC3 🗖 18 35 🗖 RESET 🛶                                                                                                                                  |                          |

| ← Port00/ADC2 □ 19 34 □ I2CMC1 <                                                                                                                               |                          |

| Port17/ADC1 □ 20 33 □ I2CMD1 <                                                                                                                                 |                          |

| AGND 21 32 Port0E                                                                                                                                              |                          |

| → AV <sub>CC</sub> □ 22 31 □ Port11/I2CMC2 →                                                                                                                   |                          |

| Port0F/SVBLANK □ 23 30 □ Port12/I2CMD2 <                                                                                                                       |                          |

| V3/B □ 24 29 □ VSYNC <                                                                                                                                         |                          |

| ✓ V2/G □ 25 28 □ HSYNC                                                                                                                                         |                          |

| ✓ V1/R □ 26 27 □ VBLANK →                                                                                                                                      |                          |

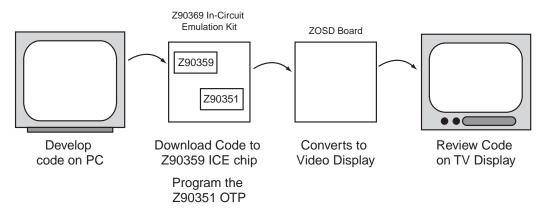

#### **Development Tools & Support**

Available in One-Time Programmable (OTP) and MASK ROM Versions, the Z90356 and Z90351 fulfill Prototype and Production Requirements. The Z90356 uses ICEbox<sup>TM</sup> (In-Circuit Emulator) tools (Z9036900ZEM) to make Programming and Debugging easy and convenient.

ZiLOG Developer Studio (ZDS) provides automatic code generation and program management.

For code development, ZiLOG offers its proven Application Programmer Interface (API) for OSD. API deals directly with proper sequencing and timing when interfacing with hardware, shielding the user application program from tedious and error prone details.

The Z9034600ZCO, an OSD evaluation board (ZOSD) is used to synchronize the emulator with a video display. Refer to the diagram below for a suggested code development environment. ZiLOG also offers the Z9034600TSC Protopak to verify code on a television.

#### **Related Products**

| Z9037x | Dual Scan TV controller for Progressive Scan                                   |

|--------|--------------------------------------------------------------------------------|

| Z9035x | Advanced TV controller with 64 KWords of ROM, Programmable Palette, and Cursor |

| Z9036x | Advanced TV controller with 32 KWords of ROM                                   |

| Z86129 | Closed Caption Decoder (CCD)                                                   |

| Z86229 | Closed Caption Decoder (CCD) with Second I <sup>2</sup> C Address Select       |

| Z86131 | Auto Time Set                                                                  |

| Z86130 | Smart V-Chip                                                                   |

| Z86230 | Smart V-Chip with Second I <sup>2</sup> C Address Select                       |

|        |                                                                                |

4

#### **Electrical Features Summary**

- 40 mA Maximum Supply Current

- 4.50 V to 5.50 V Operating Range

#### Z9035X Device Selection

| Device | Application               | ROM<br>(Words) | RAM<br>(Words) | Pkg            | I <sup>2</sup> C | IR<br>Capture | ADC  | Bit I/O<br>(max) | PWM<br>(8-bit) |

|--------|---------------------------|----------------|----------------|----------------|------------------|---------------|------|------------------|----------------|

| Z90356 | TV Receiver<br>Controller | 64K            | 1K             | 52-Pin<br>SDIP | Yes              | Yes           | 6 Ch | 25               | 6              |

| Z90351 | TV Receiver<br>Controller | 64K<br>OTP     | 1K             | 52-Pin<br>SDIP | Yes              | Yes           | 6 Ch | 25               | 6              |

### **Ordering Information**

| Part                                                         | PSI                | Description                    |  |  |  |  |

|--------------------------------------------------------------|--------------------|--------------------------------|--|--|--|--|

| Z90351                                                       | Z9035112PSC        | OTP TV Controller              |  |  |  |  |

| Z90356                                                       | Z9035612PSC Rxxxx* | Masked ROM TV Controller       |  |  |  |  |

| Emulation Kit                                                | Z9036900ZEM        | Emulator/ Programmer           |  |  |  |  |

| Protopak                                                     | Z9034900TSC        | Protopak for code verification |  |  |  |  |

| Evaluation BoardZ9034600ZCOOSD Evaluation Board              |                    |                                |  |  |  |  |

| * xxxx is a unique ROM number assigned to each customer code |                    |                                |  |  |  |  |

#### **Document Disclaimer**

© 1999 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.