# MPEG-1 SYSTEM and VIDEO DECODER

# **Features**

- Single chip MPEG-1 System and Video Decoder, conforming to the MPEG-1 standard (ISO 11172-1,2)

- Highly integrated device:

- Parses the MPEG-1 system bitstream and performs real-time decoding of video bitstreams at SIF resolution, (352x240 pixels at 30 fps or 352x288 pixels at 25 fps)

- Synchronizes the MPEG-1 audio and video data

- Includes the circuitry required for minimal-glue interfacing to host buses, and supports DMA or programmed I/O data transfer, 8 or 16 bits wide

- High quality of decoded video:

- Accepts up to 5Mbits/second MPEG-1 system bitstream

- Accepts up to 3Mbits/second MPEG-1 video bitstream

- Flexible video output formats:

- Supports NTSC and PAL video timing standards

- Provides progressive SIF-size or interlaced CCIR-size output

- Provides several video output formats with optional pixel interpolation and field repetition: 24-bit RGB, 16-bit RGB (5,5,5 or 5,6,5), 16-bit YUV 4:2:2, 12-bit YUV 4:1:1

- Full support for stand-alone CD-ROM MPEG-1 applications:

- Optional on chip sync generation

- Provides outputs compatible with industry-standard digital video encoders

- On-chip support for synchronization of audio and video:

- Decodes audio and video time stamps from the MPEG-1 multiplexed system bitstream

- Provides programmable compensation for the total delays of the audio and video reconstruction chains

- Maintains synchronization during freeze, single step and slow motion playback of video

- Two serial output ports provide audio and private bitstreams to external decoders

- Includes special display modes and operating features:

- Freeze, single step and random access

- Slow motion, with slowdown factors of 2 to 7

- Decodes special high-resolution still-image sequences (352x480 NTSC, 352x576 PAL)

- Performs frame rate conversion from all common MPEG picture rates to standard NTSC or PAL display frame rates, including 3/2 pulldown as a special case

- Interfaces directly to DRAM:

- Requires 4Mbits of 80ns or faster DRAM

- Supports two configurations, 256Kx16 or 4x256Kx4

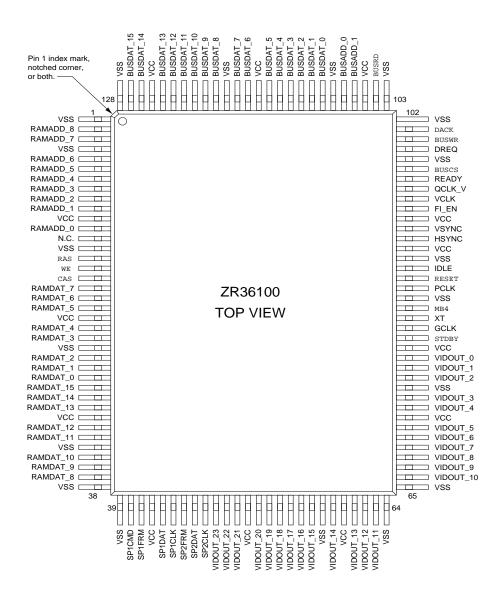

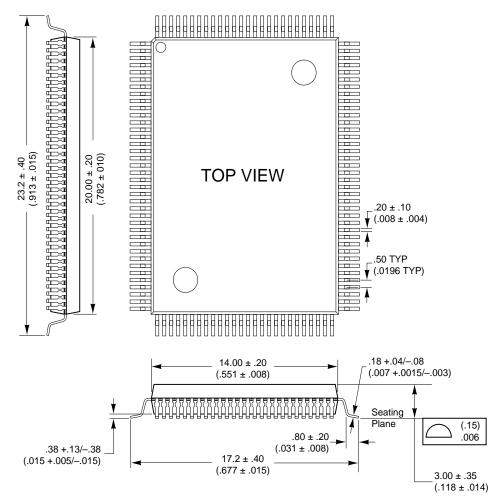

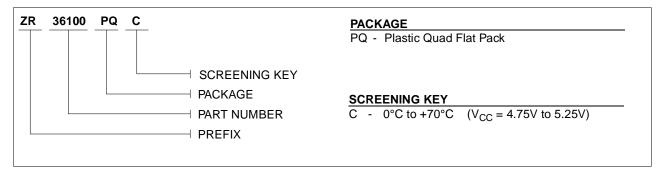

- Occupies minimal PCB area:

- Available in a 128 pin small-outline PQFP

# **Applications**

- Entertainment and games

- Interactive training/education tools

- Video kiosks and karaoke systems

- Movie players

- Video-enhanced presentations

- Multimedia books and reference materials

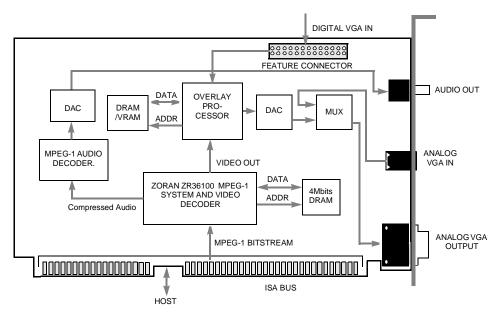

Figure 1. Block Diagram of a Typical MPEG-1 Playback Card

# INTRODUCTION

Zoran's ZR36100 MPEG 1 System and Video Decoder is targeted to the needs of developers of cost-sensitive MPEG 1 full-motion video playback products, both personal computer add-in cards and stand-alone consumer Video CD players.

In addition to being a full-motion MPEG 1 video decoder, the ZR36100 is an MPEG 1 system-layer decoder and audio-video synchronizer. In this capacity, it demultiplexes the MPEG system bitstream, extracts the time stamps from the individual video and audio bitstreams, buffers both the compressed audio and video data, and provides the audio data to the input of an external audio decoder, all while maintaining full synchronization of audio and video, and compensating for any differences in processing delay of the audio and video decoders. Support from a host controller is minimal, confined mainly to initialization of the ZR36100 for decoding of the desired MPEG bitstream. During the decoding itself, the host controller is only required to feed the bitstream to the decoder while monitoring its status, and optionally giving it on-line commands to enter one of the special decoding modes, but is not required to perform any parsing of the bitstream.

A block diagram of a personal computer MPEG add-in board employing the ZR36100 is shown in Figure 1. This application typifies the interconnection of components in an MPEG decoding system featuring the ZR36100. In this example, the host controller for the ZR36100 is the personal computer's CPU, which initializes the decoder and transfers the bitstream to it. If the host system has a DMA controller, this can be used for the bitstream data transfer, thus reducing the load on the CPU to a minimum.

The decoded video, including appropriate sync signals, is sent to a display control circuit, in this case the overlay processor, where it is scaled to fit a window in the computer's graphics display and provided to the DAC with appropriate timing derived from the graphics card's syncs and pixel clock. The output of the DAC is multiplexed with the analog output of the graphics card to create the effect of MPEG video in a graphics window. Alternatively, the video output of the ZR36100 can be connected directly to a video encoder whose composite video output is suitable for display on a television monitor.

The MPEG audio stream, extracted from the multiplexed bitstream and correctly synchronized with the displayed video by the ZR36100, is passed in bit-serial form to the audio decoder. The analog audio can be connected directly to an audio amplifier and speakers, or to the auxiliary input of the computer's sound system.

# FUNCTIONAL DESCRIPTION

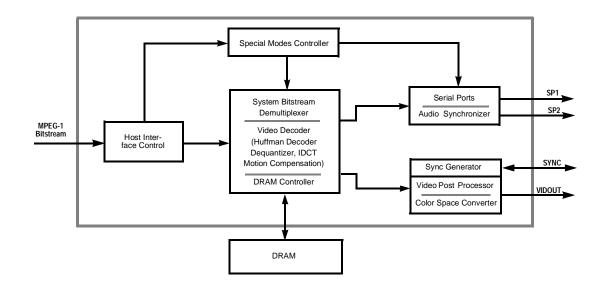

Figure 2 is a simplified block diagram of the ZR36100, showing the major functional blocks and their interfaces to the host controller, video display, audio decoder and external DRAM.

# **Host Interface**

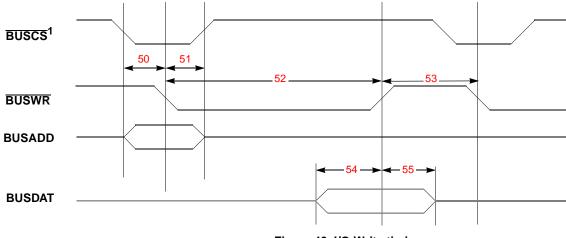

The MPEG bitstream is transferred to the ZR36100 through its host bus, a parallel interface typically connected to a host microprocessor. The host interface is also used for initialization of the device prior to starting the MPEG decoding, for on-line commands from the host to start decoding and while decoding is in progress, and for status readout during the initialization and decoding phases.

The host interface has a flexible configuration that allows it to be connected with minimal glue logic to a variety of bus types. It has a 16-bit data bus and two address lines. The byte order on the 16-bit bus is selectable, to conform with either the Intel or Motorola conventions. The bus can also be configured to operate with a width of 8 bits. Two handshake modes are supported for the bitstream transfer, a programmed I/O mode in which the bitstream port is addressed directly by the host CPU, and a mode suitable for DMA. Initialization, on-line commands and status readout always use the programmed I/O mode of access.

## System Bitstream Demultiplexing

The System Bitstream Demultiplexer separates the MPEG-1 stream into its elementary streams - the video and audio streams and an optional private data stream. These elementary streams are stored in buffers in the DRAM: one buffer for the video stream data and two buffers for any combination of audio or private data. In addition to MPEG system bitstreams, the system bitstream demultiplexer can be configured to deal with input from the host interface consisting of an MPEG video-only or audio-only elementary bitstream. In these cases, it clearly does not have to perform any demultiplexing, but only stores the incoming data in the DRAM buffer.

The video and audio (or private) elementary streams are extracted concurrently from the buffers in DRAM by the Video Decoder and Audio Synchronizer, respectively.

#### Video Decoding

The Video Decoder computes the motion vectors, and the Huffman-decoded transform coefficients subsequently undergo dequantization, rescaling, inverse discrete cosine transformation, and motion compensation. Reconstructed pictures are buffered as needed in the DRAM, to be read out later in the correct display order, which is in general not the same as the order of the encoded pictures in the bitstream, because of the presence of B-pictures which require bidirectional prediction.

#### **Video Post Processing**

The reconstructed pictures are stored in DRAM in the native progressive SIF 4:2:0 format of MPEG-1, in which each 2 x 2 array of luminance samples is associated with one chrominance sample pair. Before being output through the video interface, they are post-processed by the Video Post Processor and, optionally, the Color Space Convertor, to produce video in one of a number of commonly used pixel representations and one of two raster size options.

The video format (size and representation) options are:

- Progressive SIF-size, with 16-bit YUV 2:1:1 (2:1:1 is the same pixel format as 4:2:2, but for a SIF-size picture), 24-bit RGB, 16-bit RGB (5,6,5), or 15-bit RGB (5,5,5) pixels

- Interlaced CCIR-size, with 16-bit YUV 4:2:2, 12-bit YUV 4:1:1, 24-bit RGB, 16-bit RGB (5,6,5), or 15-bit RGB (5,5,5) pixels

The term "CCIR-size" is used here to denote a video frame whose vertical and horizontal dimensions are each twice that of the original MPEG picture. Typically but not necessarily, the pixel clock frequency and number of pixel clocks per line are as specified in CCIR601. The term is used interchangably for square-pixel or other similar (non-CCIR601) formats.

When interlaced CCIR-size output is selected, the SIF-size pictures are doubled in size horizontally, and (except when performing frame rate conversion, see below) the same picture is output in both fields. Conversion from the native 4:2:0 pixel format to any of the supported representations entails reconstruction of missing rows of chrominance samples; this is done by duplication of the existing rows. In all cases for which missing samples must be reconstructed to double the size horizontally, this can optionally be done by duplication or by interpolation using a two-tap filter. This includes reconstruction of chrominance samples for the RGB representation, which is always 4:4:4, and reconstruction of chrominance and luminance for the doubling to CCIR-size fields.

# Video Timing and Sync Generation

The video sync signals have two functions in the ZR36100: the horizontal and vertical sync signals provide the timing for the postprocessed video output; the vertical sync signal also determines the rate at which the pictures are decoded from the bitstream.

# ZR36100

The sync signals can be configured as inputs, in which case they are driven by an external sync generator. More commonly, the ZR36100's internal sync generator is used as the master sync generator, and the sync signals are configured as outputs. The sync generator is highly programmable, and is capable of generating the standard interlaced NTSC and PAL raster formats, as well as a wide variety of other interlaced and progressive formats.

The ZR36100 supports cropping of the decoded picture, so that the active displayed region can optionally be smaller than the decoded picture. With the exception of some necessary restrictions, the active region can be positioned anywhere within the display raster defined by the vertical and horizontal sync signals. The display region outside the active region, except for the horizontal and vertical blanking regions, is filled with a user-specified background color.

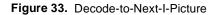

Video decoding in the ZR36100 is tightly synchronized to the vertical sync signal. That is, it decodes pictures from the video stream, and thus consumes the video stream (and consequently the whole MPEG system bitstream), at a rate which bears a fixed relationship to the video frame rate. Nominally, this picture decoding rate is the same as the video frame rate. When, however, the video interface is configured for interlaced CCIR-size output, the ZR36100 is also capable of performing conversions from commonly used picture rates to the standard PAL and NTSC frame rates. A simple example of rate conversion supported is 3/2 pulldown, in which a 23.976 pictures/sec video bitstream is decoded, and output at the NTSC rate of 29.97 frames/sec, by displaying each decoded picture during two or three fields in an alternating sequence. This achieves the required ratio of four decoded pictures for every five output frames.

One consequence of the tight coupling of the bitstream consumption rate to the vertical sync rate is that, if the bitstream is provided to the ZR36100 at a constant rate over which it has no control, the master video clock of the ZR36100 should be locked to the bitstream clock to ensure continuous operation without glitches. On the other hand, in a computer environment, where the bitstream can be provided on request, there is no such requirement to lock the clocks.

# **Serial Ports**

The audio or private data from each of the buffers in the DRAM is assigned to one of the two serial output ports. The data is read out of the buffer and output from the serial port at a constant user-programmed rate, which, in the case of an audio stream, is equal to the audio bit rate. The audio decoder connected to the serial port must be able to accept and decode the serial stream at the rate provided by the ZR36100. Since the ZR36100 decodes the video, and consumes the system bitstream, at a rate which is determined by the vertical sync frequency, this usually means that the audio decoder's output sampling clock frequency must be locked to the ZR36100's video clock frequency.

Synchronization of audio and video is achieved by timing the start of audio bitstream output from the serial port, relative to the start of video decoding. The starting time is computed from the time stamps embedded in the MPEG system bitstream. Thereafter, synchronization is maintained automatically by virtue of the constant rates of video decoding and audio bitstream output.

# **Microcoded Architecture**

The ZR36100 comprises a number of hard-wired functional units operating in conjunction with, and under control of, a programmable microcoded unit. Microcode for all the modes and options contained in this data sheet is provided by Zoran. Users are also advised to consult the ZR36100 microcode release notes for information on new features that are added from time to time.

To initialize the ZR36100 for decoding, the host system must load the microcode, and also a 128-byte array of set-up parameters that configure the hard-wired functional units and microcode.

# **On-line Commands and Special Playback Modes**

Once it is initialized, the behavior of the ZR36100 is controlled by the host by means of on-line commands. The commands supported are for the basic playback functions of starting, pausing, continuing and ending decoding, and also the following special playback modes:

- Single step: step to the next picture and pause

- Decode to first I picture: decode and display until the next I picture is displayed, then pause

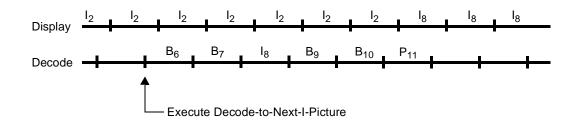

- Decode to next I picture: freeze the displayed picture and continue decoding until the next I picture, then display it and pause

- Slow motion: decode and display with a slowdown factor of 2 to 7

- Random access: start or restart decoding at a random location in the bitstream

The ZR36100 can also be configured (by the appropriate set-up parameters) for decoding of specially-encoded high-resolution stillimage sequences. These sequences have each still image encoded as a pair of consecutive pictures, of up to the maximum (SIF) picture size supported for normal bitstreams, which can be interlaced in the conventional way to produce an image with double the vertical resolution of standard SIF. The video post-processor and output interface are configured for interlaced CCIR-size operation. The image is doubled horizontally as for a normal MPEG sequence, but the two fields of the display contain the two separate pictures comprising the image. Advancing to the next image is the same as a single step of a normal MPEG sequence.

Figure 2. Simplified Block Diagram

# SIGNAL DESCRIPTION

| Name          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC (5V)      | S    | 5 volt power supply inputs.                                                                                                                                                                                                                                                                                                                                                                                                              |

| VSS (0V)      | S    | Power supply ground inputs.                                                                                                                                                                                                                                                                                                                                                                                                              |

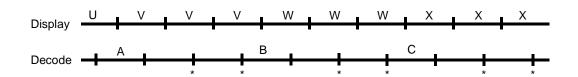

| GCLK          | I    | General Clock input. Used by the internal PLL to generate the ZR36100's internal processing clock (PCLK). When MB4 is low, the PLL multiples GCLK by 4, and the allowed frequency range of GCLK is 13.5MHz to 14.75MHz. When MB4 is high, the PLL multiples GCLK by 9/2, and the allowed frequency range of GCLK is 12.0MHz to 13.1MHz.                                                                                                  |

|               |      | In most applications, the VCLK and GCLK pins can be tied together.                                                                                                                                                                                                                                                                                                                                                                       |

|               |      | If the internal crystal oscillator is used, with a crystal connected between GCLK and XT, a 20pF capacitor must be connected between GCLK and VSS.                                                                                                                                                                                                                                                                                       |

| ХТ            | 0    | Crystal oscillator output. Instead of using an external clock generator connected to GCLK, a parallel resonant crystal of the required frequency may be connected between GCLK and XT for clock generation. If a crystal is not used, this pin should be left unconnected. If a crystal is used, a 20pF capacitor must be connected between XT and VSS.                                                                                  |

| MB4           | I    | Input signal used to select the multiplication ratio of the PLL. Low selects a ratio of 4 and high selects a ratio of 9/2.                                                                                                                                                                                                                                                                                                               |

| PCLK          | 0    | Output signal used to monitor the ZR36100's internal processing clock. Used for test purposes only.                                                                                                                                                                                                                                                                                                                                      |

| RESET         | I    | Active low reset input. Reset operation is described in the Reset and Standby Power section of this document.                                                                                                                                                                                                                                                                                                                            |

| STDBY         | I    | Active low input that drives the chip to the Standby state, forcing all output signals to float. In Standby the chip consumes a minimal amount of power. For operating restirictions when STDBY is activated, see the <i>Reset and Standby Power</i> section of this document.                                                                                                                                                           |

|               |      | <i>Note</i> : If RESET is activated together with STDBY, the power consumption is higher than the Standby power, as long as RESET is active.                                                                                                                                                                                                                                                                                             |

| IDLE          | 0    | An active high output signal, activated by the ZR36100 with activation of RESET or after the decoding of a sequence has ended. The ZR36100 deactivates the IDLE signal after receiving the <b>GO</b> on-line command.                                                                                                                                                                                                                    |

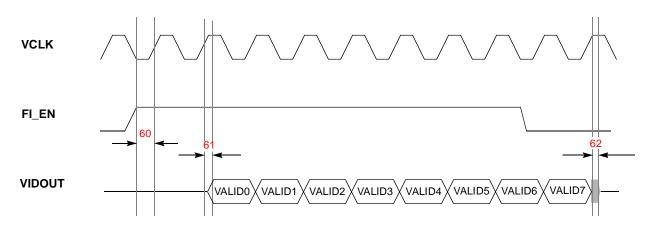

| VIDOUT (23:0) | 0    | 24-bit output bus used to output the video data. The data has one of several sizes and formats with different color space, width, and sub-sampling configurations.                                                                                                                                                                                                                                                                       |

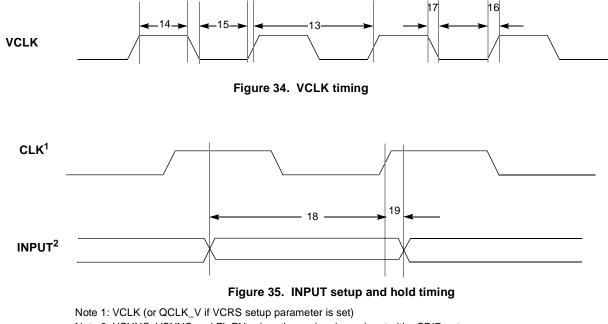

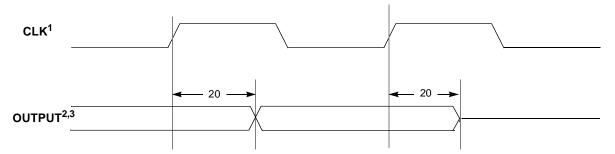

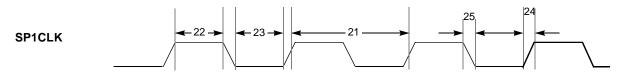

| VCLK          | I    | Video clock input. Synchronizes the VIDOUT bus and video sync signals (HSYNC, VSYNC, FI_EN). VCLK is the pixel clock when the video output mode is Interlaced CCIR-size and also in the special Enabled video output mode. VCLK can optionally be configured to be the pixel clock when the video output mode is Progressive SIF-size. When a serial port clock is configured as an output, it is derived by integer division from VCLK. |

| QCLK_V        | 0    | In the normal video output modes, this is an output clock signal derived by dividing VCLK by 4. QCLK_V can optionally be configured to be the pixel clock when the video output mode is Progressive SIF-size.                                                                                                                                                                                                                            |

|               |      | In the special Enabled video output mode, this is an active high signal indicating that the video output FIFO contains at least 8 valid pixels.                                                                                                                                                                                                                                                                                          |

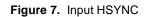

| HSYNC         | I/O  | A signal indicating the beginning of a line on the VIDOUT bus. HSYNC can be configured to be active high or active low, short or long, input or output.                                                                                                                                                                                                                                                                                  |

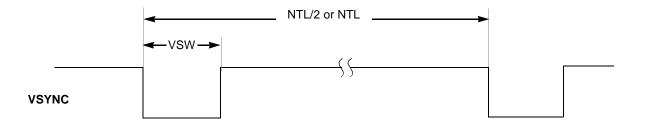

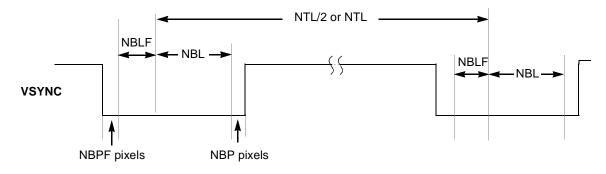

| VSYNC         | I/O  | A signal indicating the beginning of a field or frame on the VIDOUT bus. VSYNC can be configured to be active high or active low, short or long, input or output.                                                                                                                                                                                                                                                                        |

| FI_EN         | I/O  | This signal can be programmed for one of three functions.                                                                                                                                                                                                                                                                                                                                                                                |

|               |      | It can be an input or output signal that indicates the field (Field I or Field II, see note 1) being output. This signal is relevant only for interlaced video output.                                                                                                                                                                                                                                                                   |

|               |      | It can be an output, active low, composite blanking signal.                                                                                                                                                                                                                                                                                                                                                                              |

|               |      | In the Enabled video output mode, this signal is an input, used as an enable signal for the video output.                                                                                                                                                                                                                                                                                                                                |

| BUSDAT (15:0) | В    | 16-bit host interface bus. The MPEG bitstream, set-up parameters, microcode and on-line commands are all transferred to the ZR36100 over this bus. Status is read back to the host using bits 7 and 3:0. Lines 15:8, and 6:4 are input only (they float and are pulled down when read). Lines 7 and 3:0 are bidirectional.                                                                                                               |

| Name          | Туре | Description                                                                                                                                                                                                |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSADD (1:0)  | I    | 2-bit input host address bus.                                                                                                                                                                              |

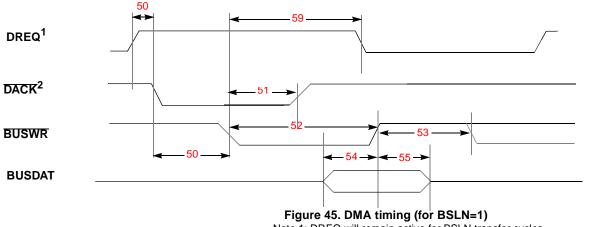

| DREQ          | 0    | Active high output control signal requesting data transfer from the host in DMA mode.                                                                                                                      |

| DACK          | I    | Active low input control signal acknowledging the request of data transfer from the host in DMA mode.                                                                                                      |

| BUSWR         | I    | Host interface write strobe.                                                                                                                                                                               |

| BUSRD         | I    | Host interface read strobe.                                                                                                                                                                                |

| BUSCS         | I    | Host interface chip select.                                                                                                                                                                                |

| READY         | 0    | Active high output host bus control signal permitting data transfer from the host in I/O mode.                                                                                                             |

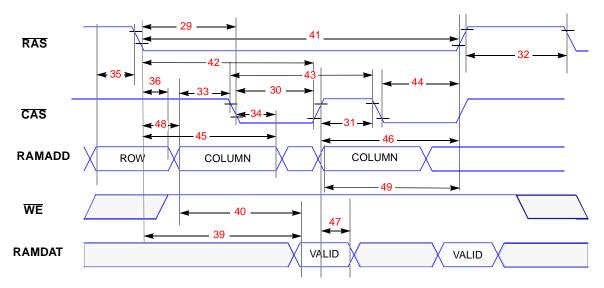

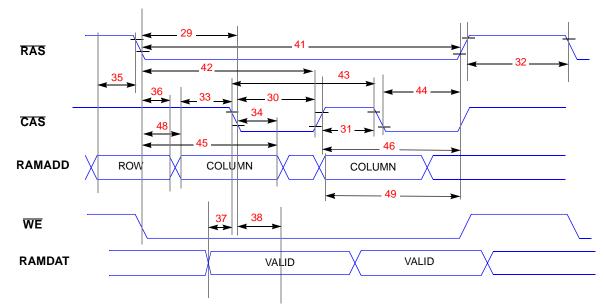

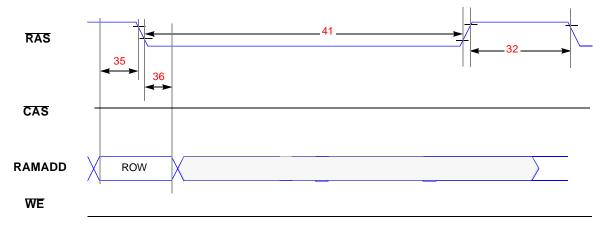

| RAMDAT (15:0) | В    | 16-bit bidirectional bus used to transfer data between the ZR36100 and the external DRAM.                                                                                                                  |

| RAMADD (8:0)  | 0    | 9-bit output bus used by the ZR36100 for addressing the external DRAM.                                                                                                                                     |

| RAS           | 0    | Active low output control signal used by the ZR36100 to specify the DRAM row address and enable the transfer of data between the ZR36100 and the DRAM.                                                     |

| CAS           | 0    | Active low output control signal used by the ZR36100 to specify the DRAM column address and initiate the transfer of data between the ZR36100 and the DRAM.                                                |

| WE            | 0    | Active low output control signal used by the ZR36100 to specify whether the transfer of data between the ZR36100 and the external DRAM buffer is a write operation (WE low) or a read operation (WE high). |

| SP1DAT        | 0    | Output signal for serial port 1 data. Serial port 1 data can be assigned to an audio stream, or one of the two private bitstreams.                                                                         |

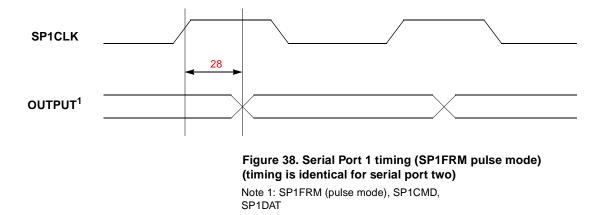

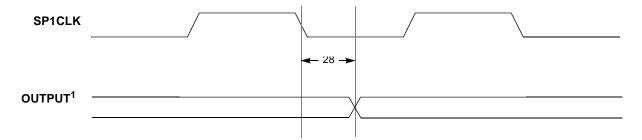

| SP1CLK        | I/O  | Serial port 1 clock. Can be programmed to be either an input or an output.                                                                                                                                 |

| SP1FRM        | 0    | Output frame synchronization signal for data output from serial port 1.                                                                                                                                    |

| SP1CMD        | 0    | Output signal used by the ZR36100 to send commands to the receiver of serial port 1 data.                                                                                                                  |

| SP2DAT        | 0    | Output signal for serial port 2 data. Serial port 2 data can be assigned to an audio stream, or one of the two private bitstreams.                                                                         |

| SP2CLK        | I/O  | Serial port 2 clock. Can be programmed to be either an input or an output.                                                                                                                                 |

| SP2FRM        | 0    | Output frame synchronization signal for data output from serial port 2.                                                                                                                                    |

Key to signal types: S - power supply; I - input only; O - output only; B - bi-directional bus; I/O - configurable as input or output.

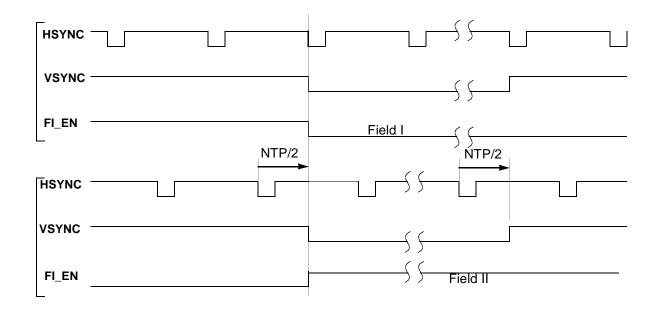

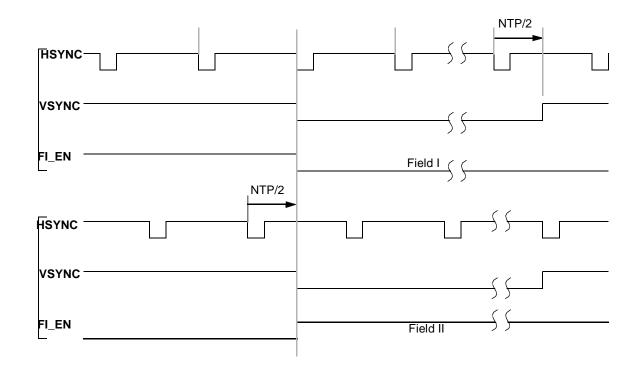

*Note 1*: When referring to the fields of an interlaced frame, Field I is defined to be the field that starts at the beginning of a line, while Field II is defined to be the field that starts at the middle of a line.

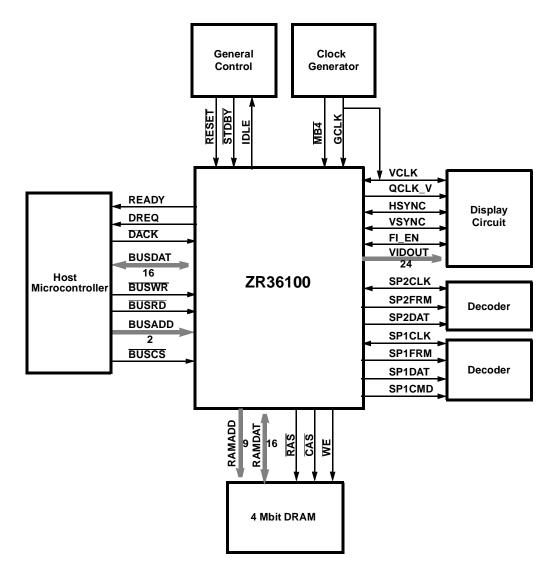

# TYPICAL CIRCUIT DIAGRAM

Figure 3 is a generic schematic showing the connections of the ZR36100 to a host microcontroller, video display circuit, decoders of serial port data, DRAM, clock generator, and general system control circuits.

Figure 3. Generic ZR36100 Schematic Diagram

An actual implentation could differ from this in a number of typical ways:

- Only one serial port is typically used, connected to an audio decoder.

- The video sync signals, HSYNC and VSYNC, are either outputs or inputs, depending on whether the ZR36100's internal or an external sync generator is used. Depending on the video interface mode, a subset of the 24 bits of the VIDOUT bus may be used, and QCLK\_V may be unused.

- DREQ and DACK are only used if the bitstream is transferred by the host in DMA mode.

- 8 bits of the BUSDAT bus are unused if the host interface is operated in its 8-bit configuration.

- The READY and IDLE signals may be unused since their states are available to the host via a status register.

- VSYNC is typically provided as an interrupt to the host controller, to maintain synchronization of the host software with the decoding of the MPEG bitstream.

# SUPPORTED BITSTREAMS

The ZR36100 can be configured to accept the MPEG bitstream in one of three forms:

- System bitstream, with multiplexed video and/or audio and/or private bitstream packets, as defined in ISO 11172-1,2,3

- Video-only bitstream, that is, containing only the elementary video bitstream data, as defined in ISO 11172-2

- Audio-only bitstream, that is, containing only audio bitstream data

The bitstream must be byte-aligned as supplied by the host. For the bitstream to be decoded properly, it must obey the following restrictions.

### System (multiplexed) bitstream

The ZR36100 decodes any legal MPEG-1 system bitstream which conforms to the ISO 11172-1 standard and obeys the following restrictions.

#### System Header

- 1. rate\_bound Less than or equal to 13107 (in 50 bytes/sec units, equivalent to 5Mbits/sec).

- 2. STD\_buffer\_size\_bound -

- Less than or equal to 32 if STD\_buffer\_size\_scale is 0 and the preceding stream\_id is "1011 1000". This is equivalent to 4Kbytes bound on the size of the input buffer for each audio or private-1 bitstream.

- Less than or equal to 46 if STD\_buffer\_size\_scale is 1 and the preceding stream\_id is "1011 1001". The above is equivalent to 46Kbytes input buffer for the video bitstream.

#### Pack Header

3. mux\_rate - Less than or equal to 13107 (in 50bytes/sec units, equivalent to 5 Mbits/sec).

#### Packet Header

- 4. STD\_buffer\_size -

- Less than or equal to 32 if STD\_buffer\_scale is 0 and the preceding stream\_id is "110x xxxx" (They always go together in the packet header). This is equivalent to 4Kbytes input buffer for the audio or private-1 bitstream.

- Less than or equal to 46 if STD\_buffer\_scale is set and the preceding stream\_id is "1110 xxxx" (They always go together in the packet header). This is equivalent to 46Kbytes input buffer for the video bitstream.

- 5. The packet rate must be less than or equal to 300 per second.

- 6. Requirements for audio-video synchronization:

- The difference between the initial SCR and the initial video PTS, and between the initial SCR and each of the initial PTSs (presentation time stamps) of the streams assigned to the serial ports, must be less than 65536.

The concepts "initial SCR," "initial video DTS" and "initial PTS" are defined in the Playback Operation section.

#### Video bitstream (video-only, or the elementary video stream multiplexed in a system bitstream)

The ZR36100 decodes any legal MPEG-1 video bitstream which conforms to the ISO 11172-2 standard and obeys the following restrictions.

#### Sequence Header

- 1. horizontal\_size Less than or equal to 352. Minimum value is 32. With certain restrictions, horizontal\_size values of 368 and 384, found in some CD-I sequences, are also supported. Details are contained in the ZR36100 microcode release notes.

- vertical\_size Less than or equal to 288 if the picture\_rate is 25 (PAL). Less than or equal to 240 if the picture\_rate is 29.97 (NTSC). Minimum value is 32.

- picture\_rate The picture rate codes supported are: 0001 (23.976 pps), 0010 (24 pps), 0011 (25 pps), 0100 (29.97 pps), 0101 (30 pps).

- 4. bit\_rate Less than or equal to 7865 in 400 bits/sec units, equivalent to 3 Mbits/sec.

- 5. vbv\_buffer\_size Less than or equal to 20 in 16Kbits units, equivalent to 40Kbytes.

#### Picture Header

6. picture\_coding\_type - Not equal to 4, i.e. no sequences with D-pictures.

# Audio bitstream multiplexed in a system bitstream

The ZR36100 passes through its serial port, to the audio decoder device, any audio bitstream which obeys the following restrictions: The bitrate\_index, layer and sampling\_frequency parameters of all frames must have the same values as in the first frame. Free bit rate, that is, bitrate\_index=0, is not allowed.

# Audio-only bitstream

The ZR36100 passes through its serial port, to the audio decoder device, any audio bitstream which obeys the following restrictions: The bit rate must be constant, and less than or equal to 448 kbits/sec.

## Private1 bitstream (multiplexed in a system bitstream)

The ZR36100 passes through its serial port any legal MPEG-1 private1 bitstream which conforms to the ISO 11172-1 standard and obeys the following restrictions.

7. Constant bit rate, which is less than or equal to the maximum bit rate allowed for audio bitstreams in ISO 11172-3.

# SET-UP PARAMETERS

The set-up parameters of the ZR36100 consist of 128 bytes of data, divided up as follows:

- 7 single-byte parameters, six of which are further divided into single-bit or multi-bit sub-fields, configure the decoding system and interfaces

- 22 parameters (38 bytes) control the display (syncs and video output)

- 8 parameters (19 bytes) control timing and delays

- 2 parameters (4 bytes) control frame rate conversion

- 3 parameters (3 bytes) control video and audio stream selection

- 57 additional bytes, here designated as reserved. Some of these may be assigned to new functions implemented in the microcode and not described in this data sheet; the most current parameter assignments are specified in the ZR36100 microcode release notes. If unused, the reserved bytes must be loaded with the value zero.

The complete 128-byte array must always be loaded whenever a change to any parameter is required, for example when a sequence has ended and a new sequence with different MPEG parameters must be decoded.

Some of the parameter fields have default values, which are preset to a given value during a cold reset (cold reset is defined in the *Reset and Standby Power* section). The only parameters that have default values are those needed to specify signal directions for bidirectional lines to avoid contention, and to define the initial configuration of the host interface.

Some of the parameters and bit fields, designated "fixed parameter", or "fixed bit," may not be changed without a cold reset. These parameters pertain generally to the overall system configuration. All parameters with default values are also defined to be "fixed" in this sense.

The set-up parameters are listed in Table 1.

# Table 1. Set-up parameters

| Byte No.<br>(Hex) | Symbol      | Brief description                             |

|-------------------|-------------|-----------------------------------------------|

| 00                | BUSMODE     | Host bus mode                                 |

| 01                | BUSOFF      | Request off timing (in DMA mode)              |

| 02                | SYSMODE     | Decoding system mode                          |

| 03                | VIDMODE     | Video output mode                             |

| 04                | SYNMODE     | Video synchronization mode                    |

| 05                | SP1MODE     | Serial port 1 mode                            |

| 06                | SP2MODE     | Serial port 2 mode                            |

| 07                |             | Reserved                                      |

| 08                | NAP (m.s.)  | Number of active pixels per line              |

| 09                | NAP (l.s.)  | Number of active pixels per line              |

| 0A                | NOP (m.s.)  | Number of offset pixels per line              |

| 0B                | NOP (I.s.)  | Number of offset pixels per line              |

| 0C                | NTP (m.s.)  | Number of total pixels per line               |

| 0D                | NTP (I.s.)  | Number of total pixels per line               |

| 0E                | NBP (m.s.)  | Number of blank pixels per line               |

| 0F                | NBP (l.s.)  | Number of blank pixels per line               |

| 10                | NBPF (m.s.) | Number of front blank pixels per line         |

| 11                | NBPF (I.s.) | Number of front blank pixels per line         |

| 12                | NDP (m.s.)  | Number of delay pixels per line               |

| 13                | NDP (l.s.)  | Number of delay pixels per line               |

| 14                | NAL (m.s.)  | Number of active lines per picture            |

| 15                | NAL (I.s.)  | Number of active lines per picture            |

| 16                | NOL (m.s.)  | Number of offset lines per picture            |

| 17                | NOL (l.s.)  | Number of offset lines per picture            |

| 18                | NTL (m.s.)  | Number of total lines per frame               |

| 19                | NTL (I.s.)  | Number of total lines per frame               |

| 1A                | NBL (m.s.)  | Number of blank lines per field [frame]       |

| 1B                | NBL (l.s.)  | Number of blank lines per field [frame]       |

| 1C                | NBLF (m.s.) | Number of front blank lines per field [frame] |

| 1D                | NBLF (I.s.) | Number of front blank lines per field [frame] |

| 1E                | NDL (m.s.)  | Number of delay lines per field [frame]       |

| 1F                | NDL (I.s.)  | Number of delay lines per field [frame]       |

| 20                | HSW         | Width of horizontal sync signal (in pixels)   |

# ZORAN

# Table 1. Set-up parameters (continued)

| Byte No.<br>(Hex) | Symbol       | Brief description                         |

|-------------------|--------------|-------------------------------------------|

| 21                | VSW          | Width of vertical sync signal (in lines)  |

| 22                | BGRV         | R or V component of the background color  |

| 23                | BGGY         | G or Y component of the background color  |

| 24                | BGBU         | B or U component of the background color  |

| 25                | FIL          | Value output on bits 23:16 of VIDOUT      |

| 26                | CRV (m.s.)   | V to R color space conversion coefficient |

| 27                | CRV (I.s.)   | V to R color space conversion coefficient |

| 28                | CBU (m.s.)   | U to B color space conversion coefficient |

| 29                | CBU (I.s.)   | U to B color space conversion coefficient |

| 2A                | CGV (m.s.)   | V to G color space conversion coefficient |

| 2B                | CGV (I.s.)   | V to G color space conversion coefficient |

| 2C                | CGU (m.s.)   | U to G color space conversion coefficient |

| 2D                | CGU (I.s.)   | U to G color space conversion coefficient |

| 2E                | SP1BR (m.s.) | Serial port 1 bit rate ratio              |

| 2F                | SP1BR        | Serial port 1 bit rate ratio              |

| 30                | SP1BR (I.s.) | Serial port 1 bit rate ratio              |

| 31                | SP2BR (m.s.) | Serial port 2 bit rate ratio              |

| 32                | SP2BR        | Serial port 2 bit rate ratio              |

| 33                | SP2BR (I.s)  | Serial port 2 bit rate ratio              |

| 34                | SP1CD (m.s.) | Divisor of VCLK for SP1CLK                |

| 35                | SP1CD (I.s.) | Divisor of VCLK for SP1CLK                |

| 36                | SP2CD (m.s.) | Divisor of VCLK for SP2CLK                |

| 37                | SP2CD (I.s.) | Divisor of VCLK for SP2CLK                |

| 38                | SP1DL (m.s.) | Serial port 1 delay                       |

| 39                | SP1DL (I.s.) | Serial port 1 delay                       |

| ЗA                | SP2DL (m.s.) | Serial port 2 delay                       |

| 3B                | SP2DL (I.s.) | Serial port 2 delay                       |

| 3C                | VOD (m.s.)   | Video output delay                        |

| 3D                | VOD (I.s.)   | Video output delay                        |

| 3E                | VCLK (m.s.)  | VCLK rate (Hz)                            |

| 3F                | VCLK         | VCLK rate (Hz)                            |

| 40                | VCLK (I.s.)  | VCLK rate (Hz)                            |

| 41                | Reserved     |                                           |

| 42                | Reserved     | -                                         |

#### Table 1. Set-up parameters (continued)

| Byte No.<br>(Hex) | Symbol   | Brief description                       |

|-------------------|----------|-----------------------------------------|

| 43                | R (m.s.) | Parameter used in frame rate conversion |

| 44                | R (l.s.) | Parameter used in frame rate conversion |

| 45                | M (m.s.) | Parameter used in frame rate conversion |

| 46                | M (I.s.) | Parameter used in frame rate conversion |

| 47                | SELMODE  | Stream selection mode                   |

| 48                | VSID     | Video stream_id                         |

| 49                | ASID     | Audio stream_id                         |

| 50 - 7F           | Reserved |                                         |

Key: I.s. indicates the least significant byte, m.s. indicates the most significant byte of a multi-byte parameter.

# **Configuration Parameters**

## BUSMODE

This byte configures the host interface. It contains the following sub-fields.

■ BSWD (bit 7) - host bus width.

This bit defines the active width of the host bus, either 8 bits or 16 bits.

- 0 The host bus width is 8 bits

- 1 The host bus width is 16 bits

Default is 0, 8 bits bus width.

■ BSOR (bit 6) - Order of bytes on the host bus.

This bit defines the byte order of the data on the host bus, when the active width of the host bus is 16 bits. It defines which byte of the host data bus contains the earlier byte of the bitstream, the lower-numbered byte of the set-up parameters or microcode, or the MSB (most significant byte) of an on-line command. When the active width is 8 bits, the data are always on bits 7:0 and BSOR must be 0.

0 -"Motorola" style. Bits 15:8 of the host bus contain the earlier byte, lower-numbered byte or MSB.

1 - "Intel" style. Bits 7:0 of the host bus contain the earlier byte, lower-numbered byte or MSB.

Default is 0. When BSWD is 0 (8-bit bus width), BSOR is not applicable and must be 0.

■ BSTM (bit 5) - bitstream transfer mode.

BSTM specifies whether the MPEG-1 bitstream is transferred using programmed I/O or DMA. Microcode, set-up parameters, online commands and status reads always use programmed I/O.

0 - programmed I/O

1 - DMA

Default is 0, programmed I/O.

■ BSLN (bits 4:0) - burst length.

This is part of the mechanism that regulates the MPEG bitstream data transfer over the host bus interface. The same mechanism is used also during loading of the set-up parameters.

In programmed I/O transfer and set-up parameter loading, this bit field specifies the maximum number of write cycles that the host can perform after checking READY, before it must again check READY.

In DMA transfer mode, this field specifies the maximum number of DMA write cycles for which the DREQ signal will remain active before being de-activated.

For 8-bit host bus width, the allowed range for BSLN is 2 to 30, even numbers only. For 16-bit host bus width, the allowed range for BSLN is 1 to 15.

Default value is 16.

# ZR36100

# BUSOFF

This parameter is used to regulate the utilization of the host bus in DMA transfer mode. It is an unsigned integer which, when multiplied by 16, defines the minimum time, in PCLK periods, for which the ZR36100 will refrain from requesting the host bus, that is, not activate DREQ, after deactivating DREQ. Minimum value is 1 (16 PCLK periods). Must be zero in programmed I/O transfer mode.

# SYSMODE

This byte configures the decoding system. It contains the following sub-fields.

■ CODE (bit 7) - Bitstream type.

This bit is not currently used. However, for compatibility with existing implementations of host software, it is recommended to set it as follows:

- 1 For a video-only bitstream.

- 0 For any other bitstream (system or audio-only)

- VIDS (bit 6) Frame rate conversion control.

Used in conjunction with the R and M parameters, as described below under Frame Rate Conversion Parameters. This parameter must be fixed.

■ VIDB (bit 5) - Video interface mode.

This bit configures the video interface for the special Enabled mode, described in the Video Interface section.

0 - Normal video interface mode.

1 - Enabled video interface mode.

- This parameter must be fixed.

- VSTL (bit 4) High-resolution still images decoding mode.

This bit configures the ZR36100 for decoding the special high-resolution still images.

- 0 Bitstream is normal moving-picture MPEG or audio-only.

- 1 Bitstream contains special high-resolution still images.

- Reserved (bits 3-1) Must be 0.

- LPIC (bit 0) Display after sequence end.

This bit defines what is displayed on the video output bus after the ZR36100 decodes a sequence\_end\_code in the bitstream, and the last picture of the sequence has been displayed.

- 0 The background color is displayed after the last picture.

- 1 The last decoded picture is displayed indefinitely.

When VIDB is 1 (for Enabled video interface mode), LPIC is not relevant and must be 0.

# VIDMODE

This byte configures the video post-processor and output interface. See Tables 10 and 11 in the *Video Interface* section for the allowed combinations of VIDMODE's sub-fields.

■ VSIZ (bit 7) - Video output size and scan mode selection.

This bit defines the video output (display) scan mode and size option: either interlaced CCIR-size, or progressive SIF-size.

0 - Video output is interlaced CCIR-size.

1 - Video output is progressive SIF-size.

This parameter must be fixed.

If the Enabled video interface mode is used, VSIZ must be 1. If the special still-images mode is used, VSIZ must be 0.

VINT (bit 6) -Video horizontal interpolation.

This bit defines whether the reconstruction of the U and V samples from the native MPEG SIF picture format, and/or the horizontal size doubling, are done by replication or by linear interpolation.

0 - Interpolation.

- 1 Replication.

- VCLR (bit 5) Video output color space selection.

This bit defines the color space of the video output: either YUV or RGB.

- 0 Video output color space is YUV

- 1 Video output color space is RGB

If the Enabled video interface mode is used, VCLR must be 0.

VIWD (bits 4,3) - Video output color depth.

For RGB color space, these bits define the color depth (in bits) of the video output.

- 00 RGB width is 24 bits

- 01 RGB width is 16 bits (5,6,5)

- 10 RGB width is 15 bits (5,5,5)

11 - Reserved

When the output color space is YUV, VIWD must be 00.

VSMP (bit 2) - Video output component sub-sampling structure.

This bit specifies 4:1:1 or 4:2:2 video output sub-sampling for interlaced CCIR-size video output, when YUV color space is selected.

0 -YUV format is 4:2:2

1 -YUV format is 4:1:1

This parameter must be fixed.

If the video output mode is not interlaced CCIR-size, or if the output color space is RGB, VSMP must be 0.

■ VBUV (bit 1) - Video output with biased U and V.

This bit defines whether the U and V video outputs for YUV color space are un-biased (i.e. in the range 0 to 255) or biased (i.e. in the range -128 to 127). The values for the biased case are the values of the unbiased case with 128 subtracted.

0 - U and V are un-biased

1 - U and V are biased

If the output color space is RGB, VBUV must be 0.

■ VBLN (bit 0) - Composite blanking output signal.

This bit defines whether the FI\_EN signal, when output, is field index indicator or a composite blanking signal.

0 - FI\_EN is field index

1 - FI\_EN is composite blanking

This parameter must be fixed.

If the sync signals are defined to be inputs, or if the Enabled video interface mode is used, VBLN must be 0.

# SYNMODE

This byte configures the video synchronization signals. It contains the following sub-fields. Note: Bits 2 to 6 must be set properly even when the SYNC signals are input.

■ SDIR (bit 7) - Video sync signals direction.

This bit determines whether the video sync signals (VSYNC, HSYNC, FI\_EN) are input or output (i.e. generated by the ZR36100).

0 - Sync signals are input

1 - Sync signals are output

When the Enabled video interface mode is used (VIDB = 1), SDIR must be 1. In this mode, VSYNC and HSYNC are outputs, and FI\_EN is an input even though SDIR = 1.

Default is 0 (the sync signals are input).

■ HSHL (bit 6) - HSYNC signal level.

This bit defines whether the HSYNC signal is active high or active low.

0 - HSYNC is active low

1 - HSYNC is active high

This parameter must be fixed.

■ VSHL (bit 5) - VSYNC signal level.

This bit defines whether the VSYNC signal is active high or active low.

0 - VSYNC is active low

1 - VSYNC is active high

This parameter must be fixed.

■ FIHL (bit 4) - FI\_EN signal level.

This bit defines whether the FI\_EN, when used as a field index signal, is high or low during field I. During field II the level is the complement of the level during field I.

0 - FI\_EN is low during field I.

1 - FI\_EN is high during field I.

This parameter must be fixed. If VIDB=1 or VBLN=1, FIHL must be 0.

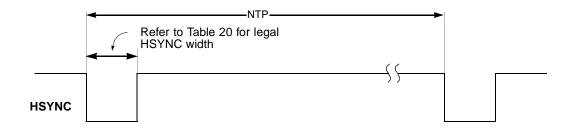

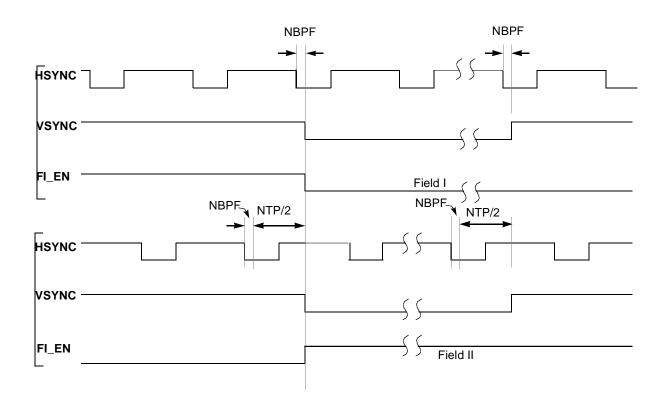

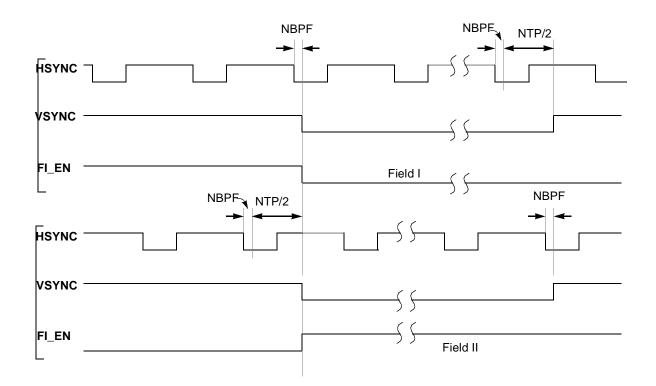

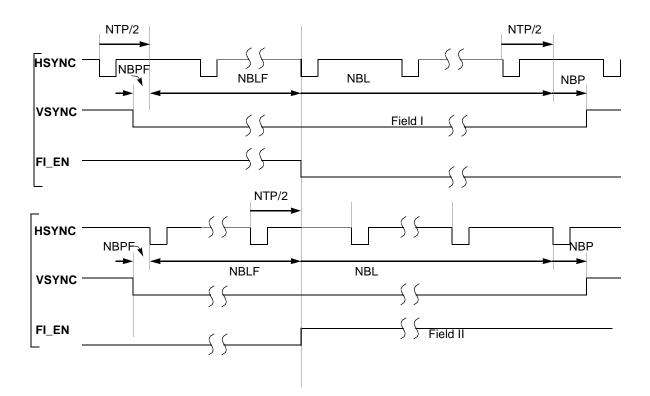

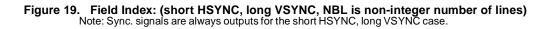

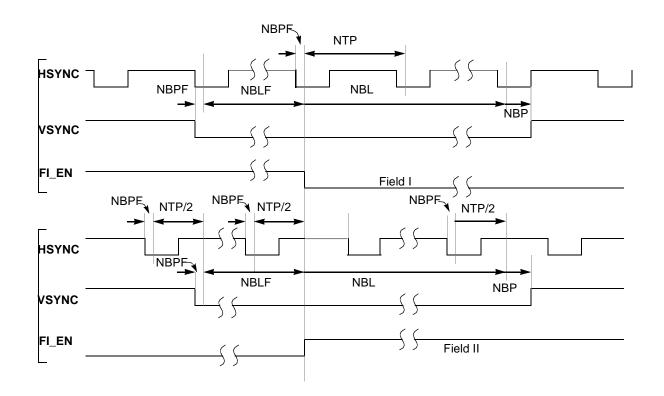

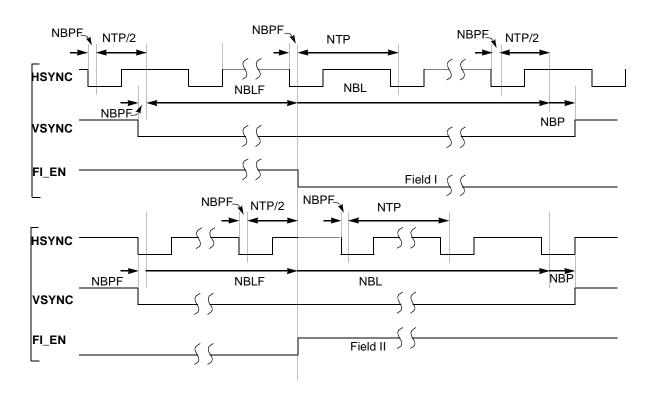

■ HSLN (bit 3) - HSYNC signal length selection.

This bit defines the length of the HSYNC signal: Either short (Sync) or long (Blanking). The length of HSYNC is HSW pixels when short, or NBP+NBPF pixels when long (HSW, NBP and NBPF are defined below).

0 - HSYNC is short (Sync pulse)

1 - HSYNC is long (Blanking pulse)

This parameter must be fixed.

If the Enabled video interface mode is used, HSLN must be 1.

■ VSLN (bit 2) - VSYNC signal length.

This bit defines the length of the VSYNC signal: Either short (Sync) or long (Blanking). The length of VSYNC is VSW\*NTP pixels when short, or (NBL+NBLF)\*NTP+NBP+NBPF pixels when long (VSW, NTP, NBL, NBLF, NBP and NBPF are defined below).

0 - VSYNC is short (Sync pulse)

1 - VSYNC is long (Blanking pulse)

This parameter must be fixed.

If the Enabled video interface mode is used, VSLN must be 1.

■ VFAC (bit 1) - First field active video output.

This bit defines whether (for interlaced CCIR-size output) the first field of an active video frame is field I or field II. Note: If the NBL set-up parameter (see below) specifies an integer number of lines (as required for NTSC), field I is the top field and field II is the bottom field. If the NBL set-up parameter specifies a non-integer number of lines (as required for PAL), field I is the bottom field and field II is the bottom field.

- 0 Field I is the first field

- 1 Field II is the first field

This parameter must be fixed.

If the video output mode is not interlaced CCIR-size, VFAC must be 0.

VCRS (bit 0) - Video clock frequency range.

This bit defines whether, for progressive SIF-size output, VCLK or QCLK\_V (1/4 the frequency of VCLK) is used as the pixel clock. See Table 5 in the *Video Interface* section.

0 -VCLK is the pixel clock.

1 - QCLK\_V is the pixel clock.

This parameter must be fixed.

If the video output mode is interlaced CCIR-size, VCRS must be 0. If the Enabled video interface mode is used, VCRS must be 1.

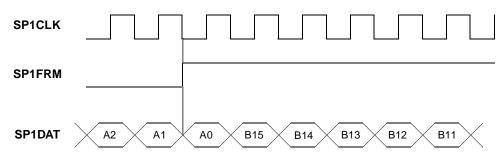

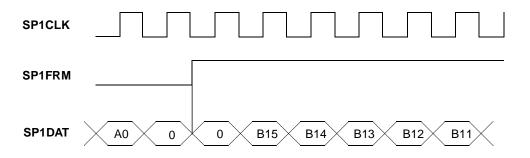

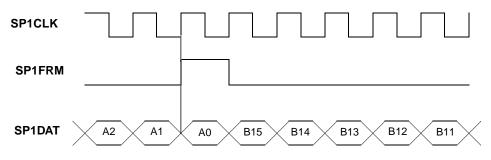

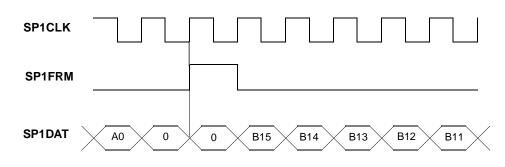

# SP1MODE, SP2MODE

The SP1MODE parameter configures serial port 1. SP2MODE (with sub-fields S2FT, S2CD, S2BS and S2AC) has exactly the same function for serial port 2. Only SP1MODE is described below. For restrictions on selection of these parameters, see the *Serial Ports Interface* section.

- Reserved (bits 7,6) Must be 0.

- S1FT (bit 5) SP1FRM signal type.

This bit defines whether the SP1FRM signal type is pulse or transition. The signal types are specified in the Serial Ports Interface section.

0 - SP1FRM signal is pulse type

1 - SP1FRM signal is transition type

This parameter must be fixed.

If the serial port is not active, (S1AC=0), S1FT must be 0.

■ S1CD (bit 4) - SP1CLK signal direction.

This bit defines whether the SP1CLK clock signal is an input or an output.

0 - SP1CLK clock signal is an input

1 - SP1CLK clock signal is an output

Default is 0, input clock.

If the serial port is not active, (S1AC=0), S1CD must be 0.

S1BS (bit 3-1) - Serial port 1 stream selection.

This field selects the source of the data assigned to serial port 1.

- 000 Serial port 1 is assigned the first audio stream encountered

- 001 Serial port 1 is assigned the second audio stream encountered

- 010 Serial port 1 is assigned the private-1 bitstream

- 011 Reserved

- 100 Serial port 1 is assigned the private-2 bitstream

- 101 Reserved

- 110 Reserved

- 111 None

The SELMODE and ASID parameters permit selection of a specific audio stream, from an MPEG system stream containing two or more audio streams. These parameters override S1BS. This feature is described below under Stream Selection Parameters. Note that the same stream can not be output on both serial ports. That is, S1BS and S2BS may not have the same value except 111.

If the serial port is not active, (S1AC=0), S1BS must be 111.

■ S1AC (bit 0) - Serial port 1 active selection.

This bit specifies whether serial port 1 is active or not.

- 0 Inactive

- 1 Active

When a video-only bitstream is decoded, both serial ports must be inactive (S1AC = S2AC = 0). Whenever a serial port is unused, it must be configured to be inactive.

## **Display Control Parameters**

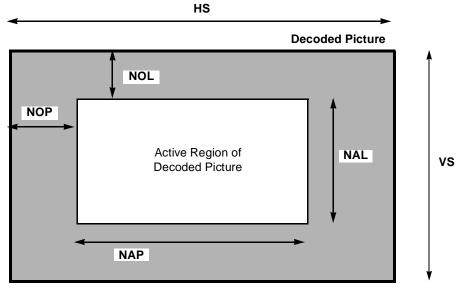

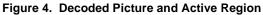

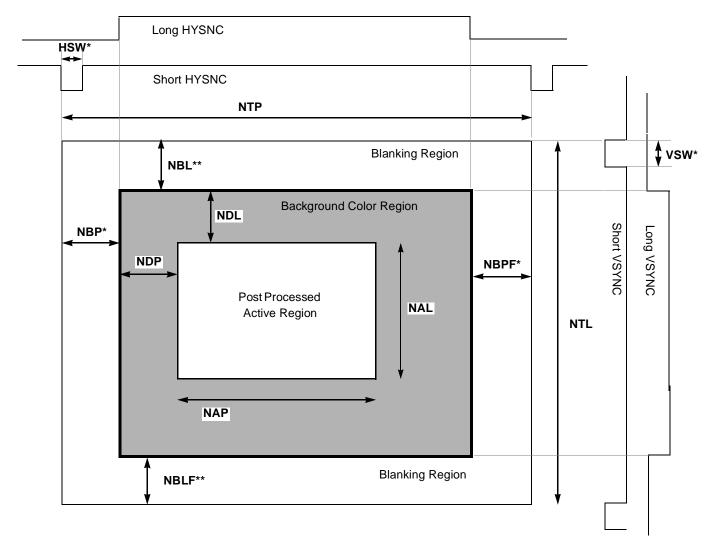

The first four display parameters define the "active region" of the decoded picture, the portion of the picture that is actually displayed. Refer to Figure 4 and Table 18 in the *Video Interface* section.

#### NAP

Defines the width in pixels of the active region of the decoded picture.

#### NAL

Defines the height in lines of the active region of the decoded picture.

#### NOP

Defines the offset in pixels of the active region from the left side of the decoded picture.

NOL

Defines the offset in lines of the active region from the top of the decoded picture.

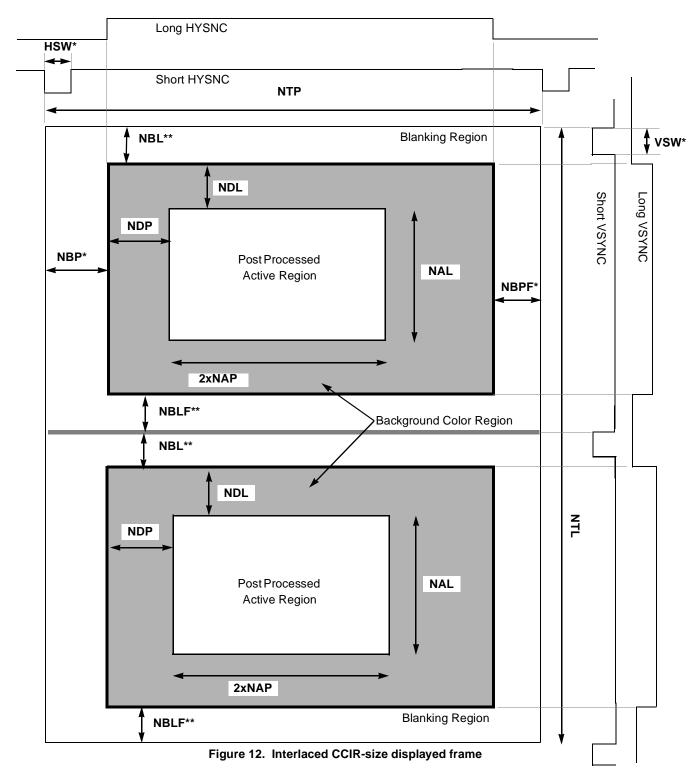

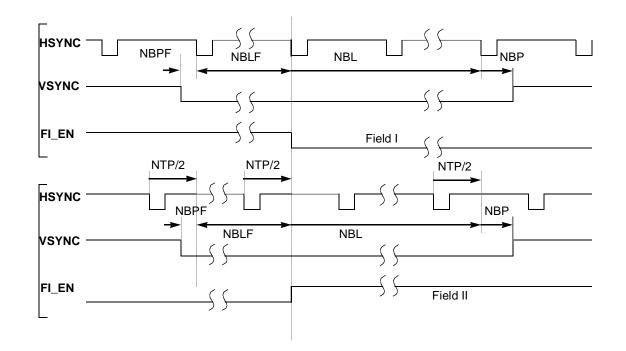

The following eight parameters specify the positioning of the active and background video in the display, relative to the raster defined by the sync signals. These parameters have different interpretations for the two display sizes and formats: interlaced CCIR-size or progressive SIF-size, as illustrated in Figures 12 and 13. For the restrictions on the values of these parameters, see Tables 19, 20 and 21 in the *Video Interface* section.

Note: Unless otherwise indicated, the values of these parameters must be set properly even when the sync signals are input.

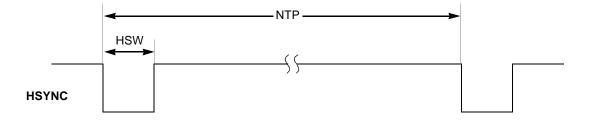

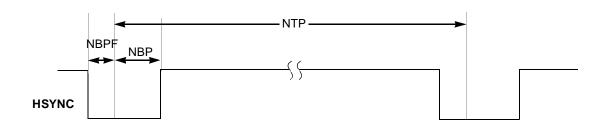

#### NTP

Defines the number of pixels per displayed line, (i.e. the number of VCLK or QCLK\_V periods, depending on the video output format; see the discussion of the pixel clock in the *Video Interface* section) between the leading edges of two consecutive HSYNC pulses. These 2 bytes are treated as a 16-bit unsigned integer.

This parameter must be fixed.

# NTL

Defines the number of lines per frame, i.e. the number of HSYNC activations between the leading edges of consecutive VSYNC pulses (for progressive SIF-size output) or alternate VSYNC pulses (for interlaced CCIR-size output). These 2 bytes are treated as a 16-bit unsigned integer.

This parameter must be fixed.

#### NBP

Specifies the blanking region (number of blank pixels) at the beginning of each line. These 2 bytes are treated as a 16-bit unsigned integer. Not applicable for long input HSYNC, and must be set to 0 in this case. For long input HSYNC, the blanking region at the beginning of each line ends with the deactivation of HSYNC. Also, for long output HSYNC, NBP+NBPF specifies the width of the HSYNC pulse.

This parameter must be fixed.

#### NBL

Specifies the blanking region (number of blank lines) at the beginning of each field or frame. These 2 bytes are treated as a 16bit unsigned fraction, with 15 integer bits and 1 bit after the binary point (that is, NBL specifies the number of blank lines with a resolution of one-half line). Not applicable for long input VSYNC, and must be set to 0 in this case. For long input VSYNC, the blanking region at the beginning of each field or frame ends with the deactivation of VSYNC. Also, for long output VSYNC, NBL+NBLF lines plus NBP+NBPF pixels specifies the width of the VSYNC pulse.

This parameter must be fixed.

#### NBPF

Specifies the blanking region (number of blank pixels) at the end of each line. These 2 bytes are treated as a 16-bit unsigned integer. Not applicable and must be 0 for long input HSYNC. Also, for long output HSYNC, NBP+NBPF specifies the width of the HSYNC pulse.

This parameter must be fixed.

#### NBLF

Specifies the blanking region (number of blank lines) at the end of each field or frame. These 2 bytes are treated as a 16-bit unsigned fraction, with 15 integer bits and 1 bit after the binary point (that is, NBLF specifies the number of blank lines with a resolution of one-half line). Not applicable and must be 0 for long input VSYNC. Also, for long output VSYNC, NBL+NBLF lines plus NBP+NBPF pixels specifies the width of the VSYNC pulse.

This parameter must be fixed.

#### NDP

Defines the number of background pixels on each line prior to (that is, to the left of) the active region. The 2 bytes of NDP are treated as a 16-bit unsigned integer.

#### NDL

Defines the number of background lines prior to (that is, above) the active region per field or frame. These 2 bytes are treated as a 16-bit unsigned integer.

The next two parameters specify the width of the video sync signals when they are output and short. Restrictions on the values of these parameters can be found in Table 20 in the *Video Interface* section. See also Figures 5 and 8.

#### HSW

Specifies the width of the horizontal sync signal (HSYNC), in pixels, when it is a short output. This byte is treated as an unsigned integer.

This parameter must be fixed.

#### VSW

Specifies the width of the vertical sync signal (VSYNC), in lines, when it is a short output. This byte is treated as an 8-bit unsigned fraction with 7 integer bits and 1 bit after the binary point.

This parameter must be fixed.

The next four parameters define background color, and the value of the upper byte of the video bus for 16-bit, 15-bit and 12-bit video output (see Tables 12, 13, 15 and 16). The background color values are not modified by the color space conversion (parameter VCLR), or the biasing of U and V (VBUV), so they must be specified in the output color space, and with the desired bias if applicable. They are, however, post processed according to the settings of VSMP and VIWD when applicable.

#### BGRV

The value of the R component of the background color if VCLR = 1, or the value of the V component of the background color, if

VCLR =0.

## BGGY

The value of the G component of the background color if VCLR = 1, or the value of the Y component of the background color, if VCLR = 0.

# BGBU

The value of the B component of the background color if VCLR = 1, or the value of the U component of the background color, if VCLR = 0.

#### FIL

The value output on bits [23:16] of the VIDOUT bus when one of the YUV or 16-bit RGB formats is used.

The following four parameters define the color space conversion coefficients. The conversion formulas are specified in the Video Interface section.

#### CRV

Defines the value of the V to R color space conversion coefficient. These two bytes are treated as a 16-bit two's complement fraction with 6 integer bits and 10 fractional bits.

Minimum value is 0. Maximum value is (2-1/1024). Note: CCIR 601 value is 1.402.

#### CBU

Defines the value of the U to B color conversion coefficient. These two bytes are treated as a 16-bit two's complement fraction with 6 integer bits and 10 fractional bits.

Minimum value is 0. Maximum value is (2-1/1024). Note: CCIR 601 value is 1.772.

#### CGV

Defines the value of the V to G color conversion coefficient. These two bytes are treated as a 16-bit two's complement fraction with 6 integer bits and 10 fractional bits.

Minimum value is -1. Maximum value is 0. Note: CCIR 601 value is -0.714.

# CGU

Defines the value of the U to G color conversion coefficient. These two bytes are treated as a 16-bit two's complement fraction with 6 integer bits and 10 fractional bits.

Minimum value is -1. Maximum value is 0. CCIR 601 value is -0.344.

Note: If the output color space is YUV (VCLR=0), the values of the conversion coefficients must be zero.

# **Timing Parameters**

The following parameters define the timing of the serial ports, presentation delays of the video and serial port data, and the frequency of VCLK.

#### SP1CD, SP2CD

The integer divisors of VLCK, used to specify the frequency of SP1CLK and SP2CLK respectively, when they are outputs.

The resulting serial port clock rates should be equal to or above the bit rates of the streams specified for the serial ports. These are 2-byte parameters, treated as 16-bit unsigned integers. Minimum value is 4. Maximum value is 1023 (the most significant 6 bits must always be zero). If a serial port is inactive (S1AC=0 or S2AC=0), or the serial clock is an input (S1CD=0 or S2CD=0), the corresponding divisor value must be 0.

#### SP1BR, SP2BR

These parameters specify the ratios of bit rate to clock rate for serial ports 1 and 2 respectively. The ZR36100 maintains average bit rates as defined by these two parameters if the clock rates, generated by using SP1CD or SP2CD (or the external clocks), are equal to or higher than the bit rates specified for the serial ports.

These are 3-byte parameters treated as 24-bit unsigned fractions with 5 integer bits and 19 fractional bits. Minimum value is 1/64.

ZR36100

Maximum value is 1.0 (i.e., the most significant 4 bits must be zero). If a serial port is inactive, the corresponding value of SP1BR or SP2BR must be zero.

These parameters must be chosen so that the actual serial port bit rate is equal (to within the available precision) to the desired bit rate, which is usually equal to the bit rate of the audio stream assigned to the serial port. For example, if ABR is the bit rate of the audio stream assigned to serial port 2,  $F_{VCLK}$  is the frequency of VCLK, and the serial port clock is configured to be an output so that its frequency is  $F_{VCLK}$  / SP2CD,

SP2BR = (ABR \* SP2CD) / F<sub>VCLK</sub>

### SP1DL, SP2DL

These parameters specify the delays in the audio decoders (or other processors) connected to serial port 1 and serial port 2. The delay is defined as the time between the reception of the first bit of the code of a presentation unit and the output of the first sample of this presentation unit to the user. The ZR36100 compensates for this delay when timing the output of the serial port, to maintain synchronization with the video relative to the perception of the user.

These two-byte parameters (treated as 16-bit unsigned integers) measure the delay in units of 90KHz clock. The value of the parameter must be zero when its serial port is inactive.

These parameters must be fixed.

#### VOD

This parameter specifies the delay in a possible display processor connected to the video output, between reception of the first sample of a presentation unit into that device and the output of the first sample of this presentation unit to the user. The ZR36100 compensates for this delay when timing the output of the serial ports, to maintain synchronization with the video relative to the perception of the user. The value of the parameter must be zero when neither serial port is active.

This 2-byte parameter (treated as a 16-bit unsigned integer) measures the delay in units of 90 KHz clock.

This parameter must be fixed.

#### VCLK

This parameter must be set to the nominal frequency of the video input clock (VCLK). VCLK is 3-byte parameter treated as a 24bit unsigned integer, representing the frequency of the VCLK input signal in units of Hertz.

The VCLK parameter is used in the transformation of the time stamps and delay information from a 90KHz clock to a clock derived from VCLK.

This parameter must be fixed.

# Frame Rate Conversion Parameters

Frame rate conversion is supported only when the video interface configuration is interlaced CCIR-size (when the VSIZ bit of VIDMODE is 0; see also the *Video Interface* section). Thanks to the frame rate conversion feature, the ZR36100 can produce NTSC-compatible (29.97 frames/sec) or PAL-compatible (25 frames/sec) video display, when the bitstream picture rate is any of the follow-ing: 23.976, 24, 25, 29.97, 30.

The parameters R and M, together with the VIDS bit of SYSMODE, are used to control the frame rate conversion, and should be set to the values shown in Table 2 (the values are given in decimal representation).

| Diamlass France       |           | Bitstream Picture Rate |      |      |       |      |  |

|-----------------------|-----------|------------------------|------|------|-------|------|--|

| Display Frame<br>Rate | Parameter | 23.976                 | 24   | 25   | 29.97 | 30   |  |

| 29.97 (NTSC)          | R         | 0                      | 1001 | 24   | 0     | 1001 |  |

|                       | М         | 0                      | 1001 | 1001 | 0     | 1001 |  |

|                       | VIDS      | 0                      | 0    | 0    | 1     | 1    |  |

| 25 (PAL)              | R         | 6                      | 6    | 0    | 6     | 6    |  |

|                       | М         | 1200                   | 6    | 0    | 1200  | 6    |  |

|                       | VIDS      | 0                      | 0    | 1    | 1     | 1    |  |

#### **Table 2. Frame Rate Conversion Parameters**

Notes:

- 1. When performing PAL to NTSC conversion, that is, when the bitstream picture height is greater than 240 lines and the display frame rate is 29.97, the frequency of GCLK must be 13.5 MHz and the MB4 pin must be at a logic high.

- When frame rate conversion is used, the video interface must be configured for interlaced CCIR-size mode (VSIZ = 0 in the VIDMODE parameter).

- 3. Only the timing of decoding and display of pictures is affected by the frame rate conversion. The pixel aspect ratio is not changed, that is, the aspect ratio at the video output is the same as that of the pictures in the bitstream. Thus, when pictures with vertical size of 240 are displayed with PAL (625 line) output, the picture does not fill the display vertically. If vertical scaling is required, it must be done by the display device. Similarly, when pictures with vertical size of 288 are displayed with NTSC (525 line) output, the active region of the displayed picture must be cropped vertically.

# **Stream Selection Parameters**

When playing back an MPEG system bitstream that contains multiple video and/or multiple audio streams, the video stream to be decoded and/or the audio stream to be output on a serial port can be selected by specifying their stream\_id numbers, by means of the following set-up parameters.

#### SELMODE

When bit 0 of SELMODE is 1, the video stream specified by VSID (see below) is selected for decoding. When bit 0 of SELMODE is 0, the first video stream encountered is decoded.

When bit 1 of SELMODE is 1, the audio stream specified by ASID (see below) is selected for output from the active serial port. When bit 1 of SELMODE is 0, the audio stream is selected as specified by the SP1BS or SP2BS fields of the SP1MODE or SP2MODE parameters, respectively.

#### VSID

The video stream\_id. The valid range of values for VSID is 0xE0 to 0xEF.

#### ASID

The audio stream\_id. The valid range of values for ASID is 0xC0 to 0xDF. Audio stream selection by means of ASID is supported only when there is only one active serial port This page intentionally left blank

# **ON-LINE COMMANDS**

Once it has been initialized, by the procedure described in the *Initialization* section, subsequent behavior of the ZR36100 is controlled by the host by means of on-line commands. On-line commands are written into the ZR36100 via an I/O port reserved for this purpose, as described in the *Host Interface* section.

An on-line command always consists of two bytes, of which the most significant is always zero. Note that when the host interface operates in 16-bit mode (BSWD=1), the byte order of the command must match the setting of the BSOR set-up parameter. Also note that when the host interface operates in 8-bit mode (BSWD=0), the command must be written with no intervening bitstream data transfers between the two bytes of the command. This restriction must be observed in both modes of bitstream transfer, DMA and programmed I/O.

Table 3 lists the supported on-line commands, with the least significant byte of the code for each command. All least significant byte values not listed in the table are reserved, and may be assigned functions in future releases of microcode. The most current assignments are documented in the ZR36100 microcode release notes.

| Command Name              | Least Significant Byte Value |

|---------------------------|------------------------------|

| Go                        | 0000 0000                    |

| Freeze                    | 0001 0000                    |

| Decode to First I-Picture | 0010 0000                    |

| Single Step               | 0011 0000                    |

| Decode to Next I-Picture  | 0100 0000                    |

| Slow Motion               | 0101 0sss                    |

| End Decoding              | 1000 000d                    |

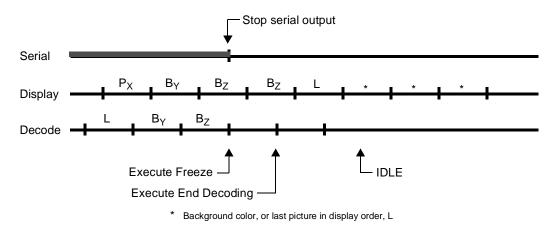

| Continue                  | 1001 0000                    |

## Table 3. On-line commands

The ZR36100 maintains an internal 4-slot queue for on-line commands from the host. If the host writes to the on-line command port while the queue is full, the access is ignored and the command is lost. The status register (described in the *Host Interface* section) contains a bit (bit 7) that indicates to the host whether the queue is full or not. The host may enter commands at intervals of not less than 150 GCLK periods, if there is space in the queue.

The commands are executed from the queue, in the sequence they were received. Once per frame, the queue is checked and if it contains a command, the command is retrieved and executed.

The following is a concise description of the behavior in response to each of the on-line commands. More detailed information can be found in the *Playback Operation* section.

#### Go

Commands the ZR36100 to start consuming and decoding the bitstream. The Go command is allowed only when the decoder is idle (as indicated by the IDLE signal or status register bit), and is the only command allowed when the decoder is idle.

The Go command is a special case with respect to the on-line command queue, since it is executed immediately when received, and effectively does not occupy a slot in the queue.

#### Freeze

When the ZR36100 executes the Freeze on-line command, it pauses video decoding and serial port output, and displays the current picture indefinitely (that is, until another command is executed).

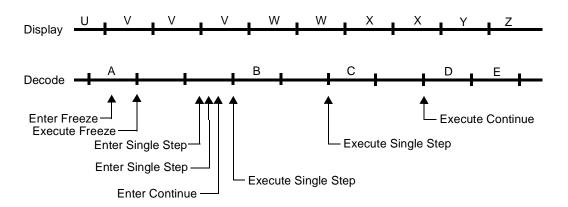

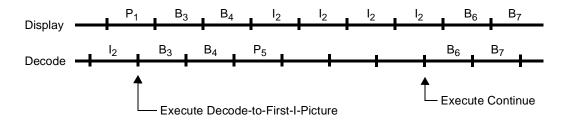

#### **Decode to First I-Picture**

When it executes this command, the ZR36100 continues until the next I-picture. That is, it continues normal decoding and display until it begins to display an I-picture. Then, when it has completed decoding of the picture that was being decoded when display of the I-picture started, it pauses as for the Freeze command, and displays the I-picture indefinitely.

### Single Step

When it executes this command, the ZR36100 steps to the next picture. That is, it resumes decoding, decodes and displays one picture, then pauses, and displays the new picture indefinitely.

#### **Decode to Next I-Picture**

When it executes this command, the ZR36100 steps to the next I-picture. That is, it resumes decoding, but without changing the picture being displayed, until display of the next I-Picture is scheduled to begin. Then, when it has completed decoding of the picture that was being decoded at this time, it pauses, and displays the new I-picture indefinitely.

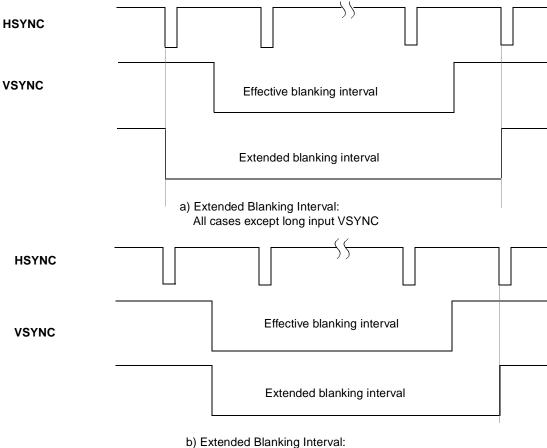

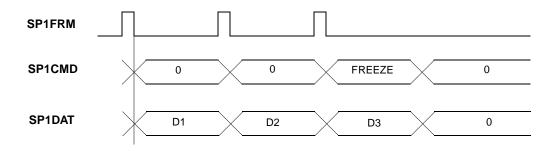

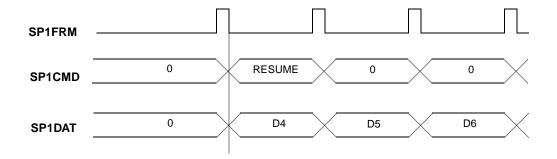

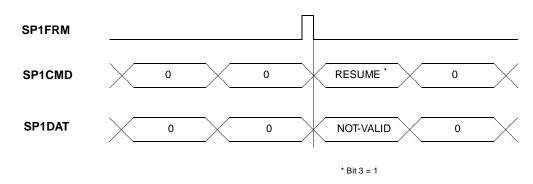

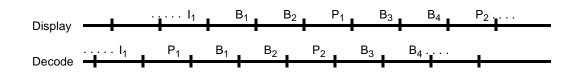

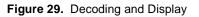

### **Slow Motion**