# YAMAHA L 5 I

# **YSF210B**

# OSF22

22-bit Oversampling Digital Filter

#### OUTLINE

The YSF210B (OSF22) is a high grade digital filter capable of 22-bit, 8-times oversampling in two channels. Like the YM3434 and YM3433B, this LSI is provided with a synchronous mode in which it operates by the 384fs system synchronous clock and an asynchronous mode in which it operates by the system clock independent of the input serial clock if with 432fs or more so that it can be used in various applications.

#### ■ FEATURES

- 8-times oversampling in two channels (exclusively for 2DAC)

- Input selectable from 16/18/20/22 bits and output from 18/20/22 bits.

- Noise shaping available at 18/20 bits output.

- Linear phase FIR type filters (225-order, 41-order and 21-order ones) connected in three vertical stages.

- 22-bit floating point multiplication and addition by the 23 × 22-bit multiplier (with a built-in overflow limiter).

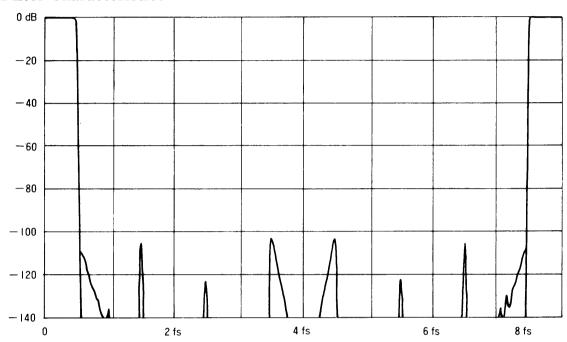

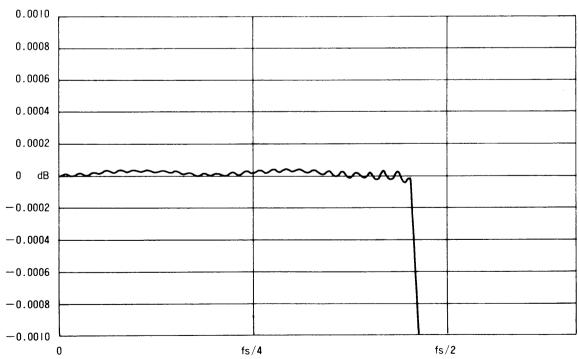

- Filter characteristics

Stop band attenuation: -100dB or more  $(0.5465fs \sim 7.4535fs)$

Pass band ripple : Within  $\pm 0.00005 dB (0 \sim 0.4535 fs)$

- For the system clock, 384fs in synchronous mode or over 432fs in asynchronous mode selectable.

- The input bit clock rates: 32fs, 48fs, 64fs, 80fs, 96fs, 112fs, 128fs, 144fs, 160fs, 176fs and 192fs.

- Sampling frequencies: 32KHz, 44.1KHz and 48KHz.

- 5V power supply, Si-gate CMOS process.

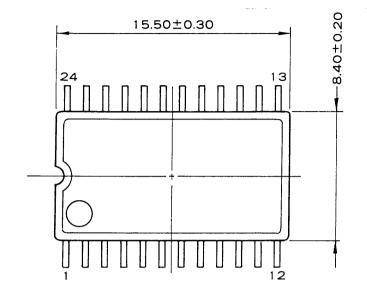

- 24-pin SOP.

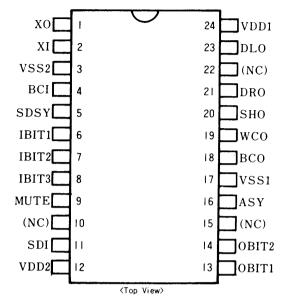

#### ■ PIN CONFIGURATION

24-pin SOP.

#### ■ PIN DESCRIPTION

| No. | Pin Name | I/O | Function                                                            |

|-----|----------|-----|---------------------------------------------------------------------|

| 1   | XO       | О   | Crystal oscillator connecting terminal                              |

| 2   | XI       | I   | Crystal oscillator connecting terminal or external clock input      |

| 3   | VSS2     | _   | Ground                                                              |

| 4   | BCI      | I   | Input data bit clock                                                |

| 5   | SDSY     | I   | Input data LR clock                                                 |

| 6   | IBIT1    | I+  | Input bit length select 1                                           |

| 7   | IBIT2    | I+  | Input bit length select 2                                           |

| 8   | IBIT3    | I+  | Input bit length select 3                                           |

| 9   | MUTE     | I   | Mute terminal ('H'; mute)                                           |

| 10  | (NC)     |     |                                                                     |

| 11  | SDI      | I   | Input data serial data                                              |

| 12  | VDD2     |     | +5V power supply                                                    |

| 13  | OBIT1    | I+  | Output bit length select 1                                          |

| 14  | OBIT2    | I+  | Output bit length select 2                                          |

| 15  | (NC)     |     |                                                                     |

| 16  | ASY      | I+  | System clock select ('H'; Asynchronous mode, 'L'; Synchronous mode) |

| 17  | VSS1     | _   | Ground                                                              |

| 18  | BCO      | О   | Output data bit clock                                               |

| 19  | WCO      | О   | Output data word clock                                              |

| 20  | SHO      | О   | Output data Lch, Rch degricher signal                               |

| 21  | DRO      | О   | Output data Rch serial data                                         |

| 22  | (NC)     |     |                                                                     |

| 23  | DLO      | О   | Output data Lch serial data                                         |

| 24  | VDD1     |     | +5V power supply                                                    |

Note) I+; Input terminal with a pull-up resistor

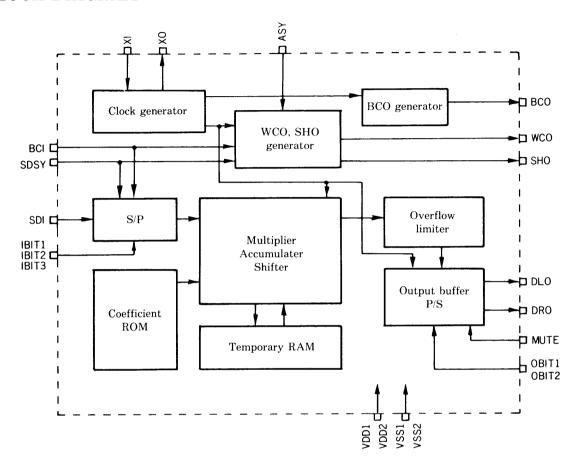

#### ■ BLOCK DIAGRAM

#### ■ FUNCTION DESCRIPTION

• The filter operation process section is operated by the XI clock.

Multiplication and addition are started at the XI timing immediately after a change of SDSY and the results are stored in the output buffer.

At the end of the operation process, the internal condition enters the "wait" mode and remains in that mode till the SDSY changes next time. When in the synchronous mode, the XI clock requires 384fs synchronized with the input clock.

When in the asynchronous mode, for 1 cycle of SDSY, the XI clock requires 432fs or more which affects the waiting time only.

- The characteristics of the 8-times oversampling digital filter are obtained by connecting linear phase type FIR filters (225-order, 41-order and 21-order) at three vertical stages. The built-in multiplier has a built-in overflow limiter and uses the floating point operation system of the data 23 × coefficient 22 bits.

- The operation result is in 23 bits and when 22-bit output is used, it is rounded to 22 bits. When 20 or 18-bit output is used, 1-order noise shaping is performed in rounding to either bit so as to minimize rounding error in the band-width up to fs.

## ■ FILTER CHARACTERISTICS (THEORETICAL VALUES)

#### 1. Filter Characteristics

#### 2. Pass Band Characteristics

#### ■ INPUT/OUTPUT TIMING

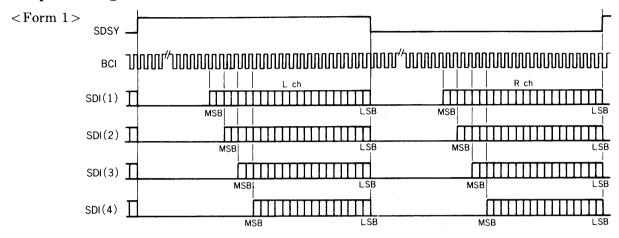

#### 1. Input timing

• The input bit length is selected by using IBIT1, IBIT2 and IBIT3 terminals.

| IBIT1 | IBIT2 | IBIT3 | Format                   | Input bit length |

|-------|-------|-------|--------------------------|------------------|

| Н     | Н     | Н     | < Form 1 > SDI(1)        | 22               |

| L     | Н     | Н     | <form 1="">SDI(2)</form> | 20               |

| Н     | L     | Н     | <form 1="">SDI(3)</form> | 18               |

| L     | L     | Н     | <form 1="">SDI(4)</form> | 16               |

| Н     | Н     | L     | < Form 2>                | 22               |

| L     | Н     | L     | <form 3=""></form>       | 22               |

| Н     | L     | L     | Forbidden                | _                |

| L     | L     | L     | Forbidden                | <del></del>      |

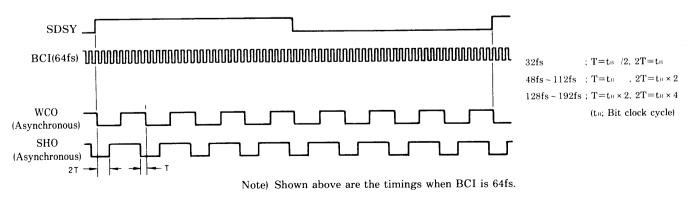

- A synchronous relation must be required among SDSY, BCI and SDI.

- The input bit clock rate should be one of the following. (32fs, 48fs, 64fs, 80fs, 96fs, 112fs, 128fs, 144fs, 160fs, 176fs and 192fs)

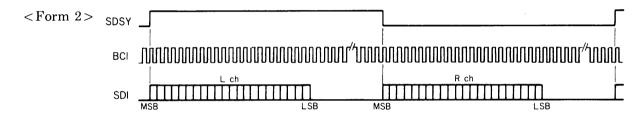

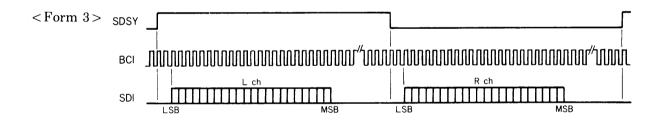

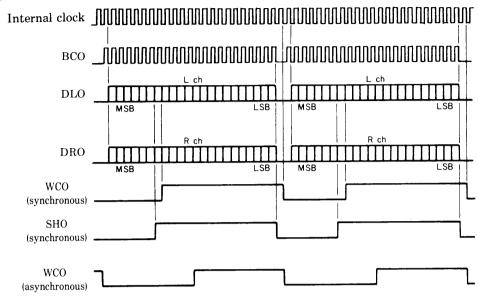

#### 2. Output Timing

Note) Shown above are 22-bit output timings when synchronous 384fs is inputted.

• The output bit length is selected by using OBIT1 and OBIT2 terminals.

| OBIT1 | OBIT2 | Output bit length |

|-------|-------|-------------------|

| Н     | Н     | 22                |

| L     | Н     | 20                |

| Н     | L     | 18                |

| L     | L     | Forbidden         |

- The BCO is the rate obtained by dividing the XI clock into two. The BCO clock Number, DLO and DRO data bit length vary according to the setting of the output bit length.

- When in the synchronous mode (ASY='L'), WCO and SHO are synchronized with BCO, WCO varies according to the output data bit length and falls at 1 clock after the LSB data is output. SHO varies at 1 clock before WCO.

- When in asynchronous mode (ASY='H'), WCO and SHO are synchronized with the input BCI clock. These clocks are generated by counting the Number of the BCI clock in 1 cycle of SDSY. WCO fall only while BCO is at a stop. Though SHO is generated from WCO, T and 2T intervals are determined by the input clock rate as shown below.

#### ■ ELECTRICAL CHARACTERISTICS

#### 1. Absolute Maximum Ratings

| Parameter             | Symbol | Rating                       | Unit |

|-----------------------|--------|------------------------------|------|

| Power supply voltage  | VDD    | -0.3~7.0                     | V    |

| Input voltage         | Vı     | $-0.3 \sim V_{\rm DD} + 0.5$ | V    |

| Operating temperature | Тор    | $-10 \sim 75$                | °C   |

| Storage temperature   | Tstg   | $-50 \sim 125$               | °C   |

#### 2. Recommended Operation Conditions

| Parameter             | Symbol | Min. | Typ.    | Max. | Unit |

|-----------------------|--------|------|---------|------|------|

| Power supply voltage  | VDD    | 4.75 | 5.00    | 5.25 | V    |

| Operating temperature | Тор    | 0    | 25      | 70   | °C   |

| Clock frequency       | fxı    | 11   | 16.9344 | 22   | MHz  |

#### 3. DC Characteristics (Conditions; Ta=0 to 70°C, VDD=5.0±0.25V)

| Parameter                 | Symbol                        | Condition                       | Min. | Typ. | Max. | Unit    |

|---------------------------|-------------------------------|---------------------------------|------|------|------|---------|

| Power consumption         | W                             | VDD=5.0V                        |      |      | 300  | mW      |

|                           |                               | fx1=16.9344MHz                  |      |      |      |         |

| Input voltage H level (1) | V <sub>I</sub> H <sub>1</sub> | XI terminal                     | 3.5  |      |      | V       |

| Input voltage H level (2) | VIH2                          | Other input than<br>XI terminal | 2.7  |      |      | V       |

| Input voltage L level     | VIL                           |                                 |      |      | 0.8  | V       |

| Input leakage current     | ILK                           | *1                              | -10  |      | 10   | $\mu$ A |

| Output voltage H level    | Vон                           | IOH=50μA                        | 4.0  |      |      | V       |

| Output voltage L level    | Vol                           | IoL=1mA                         |      |      | 0.4  | V       |

<sup>\*1)</sup> Except for the input terminal with pull-up resistor

#### 4. AC Characteristics (Conditions; $Ta=0 \sim 70^{\circ}C$ , $VDD=5.0 \pm 0.25V$ )

| Parameter           | Symbol | Min. | Тур. | Max. | Unit |

|---------------------|--------|------|------|------|------|

| XI clock duty       | Rxı    | 40   | 50   | 60   | %    |

| BCI clock frequency | fBC    | 1.0  |      | 9.3  | MHz  |

| duty                | RBC    | 40   | 50   | 60   | %    |

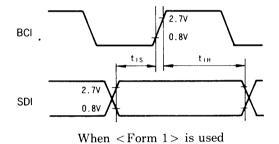

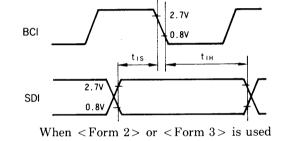

| SDI setup time      | tis    | 50   |      |      | ns   |

| SDI hold time       | tıн    | 20   |      |      | ns   |

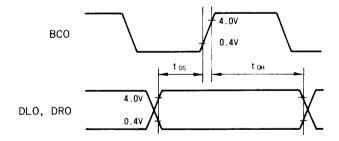

| DLO, DRO setup time | tos    | 15   |      |      | ns   |

| DLO, DRO hold time  | tон    | 15   |      |      | ns   |

#### • Input timing

#### • Output timing

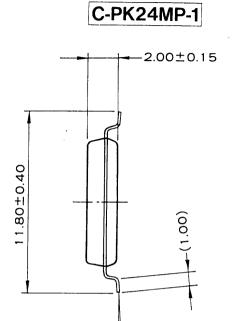

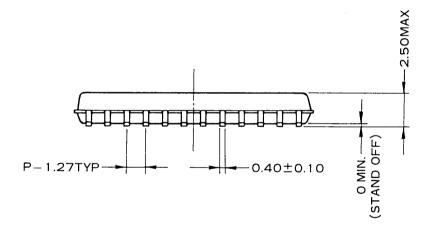

## ■ EXTERNAL DIMENSIONS

$0 - 10^{\circ}$

端子厚さ:0.15±0.10 (LEAD THICKNESS)

> カッコ内の寸法値は参考値とする モールド外形寸法はバリを含まない 単位(UNIT):mm

The figure in the parenthesis ( ) should be used as a reference. Plastic body dimensions do not include burr of resin. UNIT: mm

#### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT. COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS, YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

The specifications of this product are subject to improvement changes without prior notice.

| AGENCY |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

#### YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

203, Matsunokijima, Toyooka-mura, Head Office

Iwata-gun, Shizuoka-ken, 438-0192

Tel. +81-539-62-4918 Fax. +81-539-62-5054

2-17-11, Takanawa, Minato-ku, ■ Tokyo Office

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office Namba Tsujimoto Nissei Bldg. 4F

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

■ U.S.A. Office YAMAHA Systems Technology

100 Century Center Court, San Jose,

CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791