# YAMAHA L 5 I

# YMZ263B

# Multimedia Audio & Game Interface Controller (MMA)

#### OVERVIEW

The YMZ263B (MMA) was developed to meet the multimedia needs of personal computers. We have successfully packaged in a single chip features like PCM/ADPCM record and playback, MIDI communications, and a general purpose game port. It is now possible to create a compact, personal computer based sound system by combining the YMZ263B (MMA) with the YM3812 (OPL2) and the YMF262 (OPL3).

#### **■ FEATURES**

#### (1) PCM/ADPCM section

- Selectable PCM/ADPCM modes.

- Two built-in recording and playback channels.

- Each channel can select among sampling frequencies:

In ADPCM mode, 22.05 kHz, 11.025 kHz, 7.35 kHz, and 5.5125 kHz.

In PCM mode, 44.1 kHz, 22.05 kHz, 11.025 kHz and 7.35 kHz.

- PCM has 8-bit or 12-bit resolution, ADPCM compresses 12-bit data into 4 bits.

- Built-in 12-bit floating A/D and D/A converters for record and playback.

- 2-channel and double over-sampling A/D conversion.

- 4-channel and double over-sampling D/A conversion.

- For voice data I/O with the CPU, channel 1 and channel 2 both provide built-in 128-byte FIFO buffers. Selectable CPU (polling/interrupt) mode and DMA mode.

#### (2) MIDI section

- UART for sending and receiving data that meets MIDI standards.

- Separate built-in 16-byte FIFO buffers for sending and for receiving.

#### (3) Game Port section

• Eight input ports for interfacing joysticks, etc.

#### (4) Miscellaneous

- Three built-in timers.

- Built-in address decoder.

- 5V battery, silicon gate CMOS process.

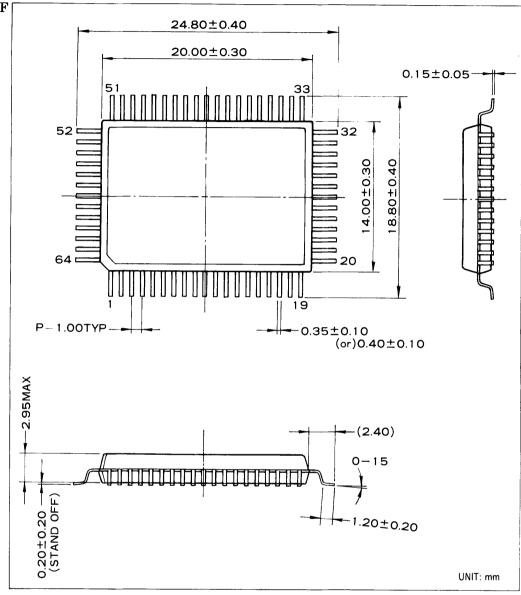

- 64 pin QFP package.

YAMAHA CORPORATION-

YMZ263B CATALOG CATALOG No.: LSI-4MZ2632

1992. 08

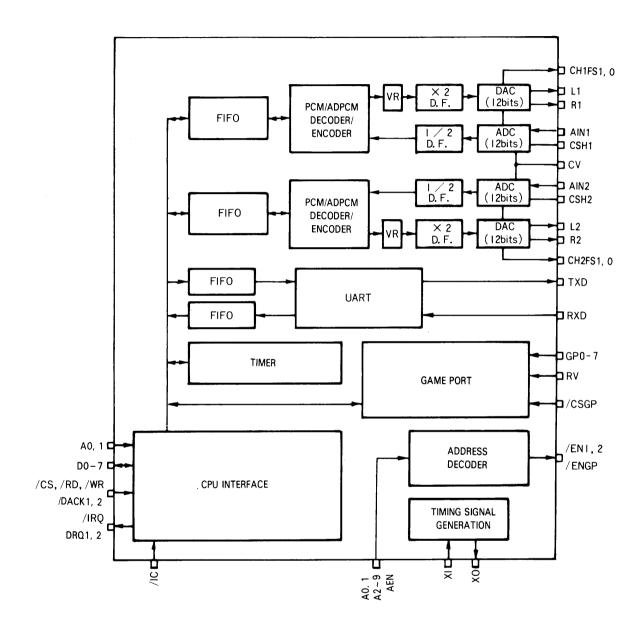

# ■ BLOCK DIAGRAM

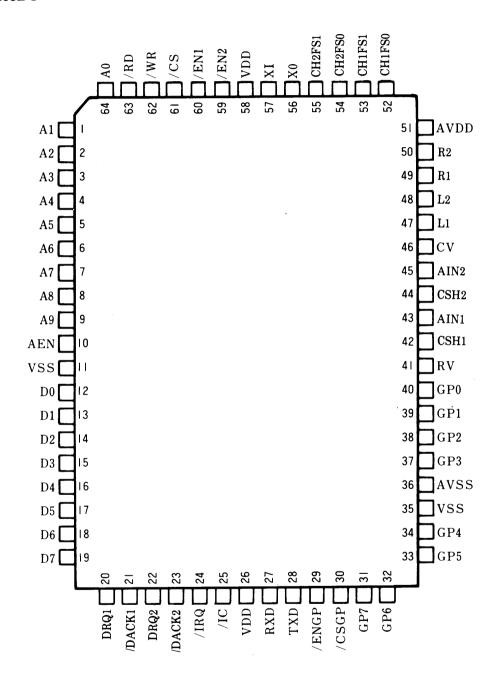

# ■ PIN OUT DIAGRAM

• YMZ263B-F

<64QFP Top View>

# ■ PIN CONFIGURATION

| No. | Name   | I/O | Function                                                     |

|-----|--------|-----|--------------------------------------------------------------|

| 1   | A1     | I   | CPU interface Address bus                                    |

| 2   | A2     | I   | Address bus                                                  |

| 3   | A3     | I   | Address bus                                                  |

| 4   | A4     | I   | Address bus                                                  |

| 5   | A5     | I   | Address bus                                                  |

| 6   | A6     | I   | Address bus                                                  |

| 7   | A7     | I   | Address bus                                                  |

| 8   | A8     | I   | Address bus                                                  |

| 9   | A9     | I   | Address bus                                                  |

| 10  | AEN    | I   | Address enable                                               |

| 11  | VSS    | _   | Ground (digital)                                             |

| 12  | D0     | I/O | CPU interface Data bus                                       |

| 13  | D1     | I/O | Data bus                                                     |

| 14  | D2     | I/O | Data bus                                                     |

| 15  | D3     | I/O | Data bus                                                     |

| 16  | D4     | I/O | Data bus                                                     |

| 17  | D5     | I/O | Data bus                                                     |

| 18  | D6     | I/O | Data bus                                                     |

| 19  | D7     | I/O | Data bus                                                     |

| 20  | DRQ1   | О   | DMA request signal 1                                         |

| 21  | /DACK1 | I   | DMA acknowledge signal 1                                     |

| 22  | DRQ2   | О   | DMA request signal 2                                         |

| 23  | /DACK2 | I   | DMA acknowledge signal 2                                     |

| 24  | /IRQ   | OD  | Interrupt signal                                             |

| 25  | /IC    | I+  | Initial clear input                                          |

| 26  | VDD    | _   | +5V power supply (digital)                                   |

| 27  | RXD    | I   | MIDI UART Data input                                         |

| 28  | TXD    | О   | MIDI UART Data output                                        |

| 29  | /ENGP  | 0   | Address decoder output for game port (201H)                  |

| 30  | /CSGP  | I+  | Game port Chip select                                        |

| 31  | GP7    | I+  | Input port                                                   |

| 32  | GP6    | I+  | Input port                                                   |

| 33  | GP5    | I+  | Input port                                                   |

| 34  | GP4    | I+  | Input port                                                   |

| 35  | VSS    | _   | Ground (digital)                                             |

| 36  | AVSS   | -A  | Ground (analog)                                              |

| 37  | GP3    | IA* | Game port Input port                                         |

| 38  | GP2    | IA* | Input port                                                   |

| 39  | GP1    | IA* | Input port                                                   |

| 40  | GP0    | IA* | Input port                                                   |

| 41  | RV     | IA  | Voltage input pin for game port                              |

| 42  | CSH1   | -A  | PCM/ADPCM channel 1 ADC sample hold capacitor connection pin |

| 43  | AIN1   | IA  | ADC input pin                                                |

| 44  | CSH2   | -A  | PCM/ADPCM channel 2 ADC sample hold capacitor connection pin |

| 45  | AIN2   | IA  | ADC input pin                                                |

| 46  | CV     | -A  | ADC center voltage pin                                       |

| 47  | L1     | OA  | PCM/ADPCM Channel 1 (left) DAC output pin                    |

| 48  | L2     | OA  | PCM/ADPCM Channel 2 (left) DAC output pin                    |

| 49  | R1     | OA  | PCM/ADPCM Channel 1 (right) DAC output pin                   |

| 50  | R2     | OA  | PCM/ADPCM Channel 2 (right) DAC output pin                   |

| No. | Name   | I/O | Function                                                             |

|-----|--------|-----|----------------------------------------------------------------------|

| 51  | AVDD   | -A  | +5V power supply (analog)                                            |

| 52  | CH1FS0 | 0   | PCM/ADPCM Channel 1 Sampling frequency information output 0          |

| 53  | CH1FS1 | 0   | Sampling frequency information output 1                              |

| 54  | CH2FS0 | О   | PCM/ADPCM Channel 2 Sampling frequency information output 0          |

| 55  | CH2FS1 | 0   | Sampling frequency information output 1                              |

| 56  | xo     | 0   | Quartz oscillator connection pin                                     |

| 57  | XI     | I   | Quartz oscillator connection pin or master clock input (16.9344 MHz) |

| 58  | VDD    | _   | +5V power supply (digital)                                           |

| 59  | /EN2   | 0   | Address decoder output 2 (388H~38BH)                                 |

| 60  | /EN1   | 0   | 1 (38CH ~ 38FH)                                                      |

| 61  | /CS    | I+  | CPU interface Chip select                                            |

| 62  | /WR    | I   | Write enable                                                         |

| 63  | /RD    | I   | Read enable                                                          |

| 64  | A0     | I   | Address bus                                                          |

Notes: I/O notation:

A: Analog pin

OD:

Open drain output pin

I+:

Input pin with built-in pull-up resistor

IA\*

short-circuited to AVSS.

#### FUNCTIONS

#### 1. Clock XI, XO

Pins XI and XO make up the quartz oscillator circuit. The oscillation frequency is 16.9344 MHz. An external clock may be connected to the XI input pin.

#### 2. CPU Interface A0, A1, D0 $\sim$ 7, /CS, /RD, /WR, /IRQ

An 8 bit parallel interface is used to control the components of this LSI. Data bus controls, such as register data Read/Write and Status Read, are performed using the /CS, /RD, /WR, A0, and A1 signals. The combination of these signals determines the mode:

| /CS | /RD | /WR | A0 | A1  | CPU access mode    |

|-----|-----|-----|----|-----|--------------------|

| Н   | ×   | ×   | ×  | ×   | Inactive mode      |

| L   | Н   | L   | L  | ×   | Address Write mode |

| L   | Н   | L   | Н  | L/H | Data Write mode    |

| L   | L   | Н   | L  | L   | Status Read mode   |

| L   | L   | Н   | н  | L/H | Data Read mode     |

Note: × means "Don't care"

#### (a) Inactive mode

When /CS is "H", the data bus D0~D7 is in a high impedance state.

#### (b) Address Write mode

Use this mode to specify the address for read/write operations. Address data should be loaded on the data bus.

#### (c) Data Write mode

Use this mode to write data to the address specified in Address Write mode. The data on the data bus will be written to the specified register.

#### (d) Status Read mode

Use this mode to read the status. The status information will be output on the data bus.

#### (e) Data Read mode

Use this mode to read data from the address specified in Address Write mode. The data from the register will be output on the data bus.

When an interrupt signal is generated by any section of this LSI, the /IRQ pin is set to "L" and the CPU is notified.

Note) YMZ263B requires the following wait time before next operation of data/address writing or before that of data/address reading.

WAIT TIME .... Over 8 cycles (Master clock)

#### 3. FIFO Buffer DRQ1, DRQ2, /DACK1, /DACK2

Data input/output between the PCM/ADPCM section and the CPU is carried out through 128 byte FIFO buffers for each channel. This can be connected with the DMA controller for DMA transfer in the DMA mode.

# 4. PCM/ADPCM CH1FS0, CH1FS1, CH2FS0, CH2FS1, L1, R1, L2, R2, AIN1, CSH1, AIN2, CSH2, CV

PCM/ADPCM decoder output is performed in several steps. First, the digital volume controls in both channel 1 and channel 2 adjust the output level. Double over-sampling processing is performed on this output. D/A conversion is performed at twice the specified sampling frequency. Finally, the voltage output is sent to the L1, R1, L2 and R2 pins. (Over-sampling processing is not performed in the 44.1 kHz PCM mode.)

The analog signals input from AIN1 and AIN2 are processed as follows: The signal is A/D converted at twice the specified sampling frequency. One half under-sampling processing is performed on this signal. Finally, the input is fed into the PCM/ADPCM encoder. For A/D conversion, a sample hold capacitor is attached externally to the CSH1 and CSH2 pins. The CV pin is a center voltage pin for the A/D converter. (Under-sampling processing is not performed in the 44.1 kHz PCM mode.)

PCM/ADPCM sampling frequency information for each channel 1 and channel 2 is output for external LPF switching through CH1FS0, CH1FS1, CH2FS0, and CH2FS1.

| PCM        | ADP         | СМ       | CH1FS1, CH2FS1 | CH1FS0, CH2FS0 |

|------------|-------------|----------|----------------|----------------|

| 44.1 kHz   | _           | -        | L              | L              |

| 22.05 kHz  | 22.05       | kHz      | L              | Н              |

| 11.025 kHz | 11.025      | kHz      | Н              | L              |

| 7.35 kHz   | 7.35 or 5.5 | 5125 kHz | Н              | Н              |

#### 5. MIDI TXD, RXD

Output data is buffered in a 16-byte FIFO buffer, and then synchronized output is transmitted by the UART through the TXD pin. Synchronized input from the RXD pin is received by the UART and buffered in a 16-byte FIFO buffer.

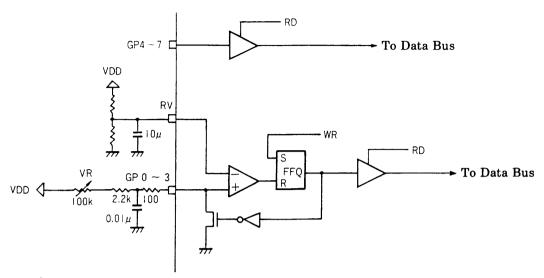

#### 6. Game Port /CSGP, GP0~7, RV

Pins GP4 ~ 7 are used for a general purpose input port. When/GSGP='L' and /RD='L', the data from pins GP4 ~ 7 is output on D4 ~ 7 of the data bus. Pins GP0 ~ 3 can be read from the data bus, and are compared with the RV voltage internally so that these pins can be used for a joystick connection. If the pin voltage is lower than the RV voltage, "1" is assigned. Apply the voltage to be compared on the RV pin. (The voltage to be compared:  $0.63*VDD \sim 0.70*VDD$ )

Note that pins  $GP0 \sim 3$  are connected internally to the AVSS pin. When /CSGP= "L" and /WR= "L", Pins  $GP0 \sim 3$  are cut off from the AVSS pin, and comparison with the RV voltage is started. Thus, by adding a constant, "1" period width of the data to be read varies with respect to the resistance value.

(Example of Pins GP0~7 Input Equivalent Circuit and External Circuit)

# 7. Address Decoder AEN, A0~9, /EN1, /EN2, /ENGP

In order to minimize external connections, an address decoder with fixed parameters is built in. /EN1, /EN2, and /ENGP are decorder output for YMZ263B (except GAME PORT), sound generator the YMF262 and the like, and GAME PORT.

/EN1, /EN2, and /ENGP will become "L" when decoder output address is valid.

AEN is the chip select for the address decoder. If AEN="H", then/EN1, /EN2, and /ENGP will not become "L" regardless of the values of  $A0 \sim 9$ .

#### 8. Initial Clear /IC

Initial clear must be performed at LSI power-up.

# **■ REGISTERS**

# 1. Register Map

| СН     |     |            | CH        | IANN      | EL 1       | (A1=      | 'L')      |      |            |     |     | СН       | IANN     | EL 2        | (A1=      | 'H ')     | , . |            |

|--------|-----|------------|-----------|-----------|------------|-----------|-----------|------|------------|-----|-----|----------|----------|-------------|-----------|-----------|-----|------------|

| ADDR   | R/W | D7         | D6        | D5        | D4         | D3        | D2        | D1   | D0         | R/W | D7  | D6       | D5       | D4          | D3        | D2        | D1  | D0         |

| \$ 0 0 | R/W |            |           |           |            |           |           |      | SELT       | _   |     | 1        |          |             | 3         |           |     |            |

| \$ 0 1 | _   |            |           |           | LSI 7      | rest      |           |      | <b>.</b>   | _   |     |          |          |             |           |           |     |            |

| \$ 0 2 | W   |            |           | T         | IMER       | 0 (L      | .)        |      |            | _   |     |          |          |             |           | ,         |     |            |

| \$ 0 3 | W   |            |           | T         | IMER       | 0 (H      | ()        |      |            | _   |     |          |          |             |           |           |     |            |

| \$ 0 4 | W   |            | ,         | BASI      | E COU      | JNTE      | R (L      | .)   |            | _   |     |          |          |             |           | ,         |     |            |

| \$ 0 5 | W   |            | TIMI      | ER 1      |            | BAS       | E CO      | UNTE | R(H)       | _   |     |          |          |             |           |           |     |            |

| \$06   | R/W |            |           | Т         | IMEF       | R 2 ()    | L)        | -    | -          | _   |     |          | /        |             |           |           |     |            |

| \$ 0 7 | R/W |            |           | Т         | IMEF       | R 2 (1    | H)        |      |            |     |     |          |          |             |           |           |     |            |

| \$ 0 8 | w   | *1         | T2<br>MSK | T1<br>MSK | T0<br>MSK  | ST<br>BC  | ST2       | ST1  | ST0        |     |     |          |          |             |           |           |     |            |

|        |     | ADP        |           |           |            |           |           | PLY  | ADP        |     | ADP |          |          |             |           |           | PLY | ADP        |

| \$09   | W   | RST        | R         | L         | FS1        | FS0       | PCM       | REC  | ST         | W   | RST | R        | L        | FS1         | FS0       | PCM       | REC | ST         |

| \$ 0 A | W   |            |           | VOL       | JME (      | CONT      | ROL       | i    | l          | w   |     | l        | VOL      | U <b>ME</b> | CONT      | rol       |     |            |

| \$ 0 B | R/W |            |           | -         | PCM        | DAT       | A         |      |            | R/W |     |          |          | PCM         | DAT       | A         |     |            |

| \$ 0 C | w   | DMA<br>MOD |           | FMT<br>0  | SEL<br>F2  | SEL<br>F1 | SEL<br>F0 |      | DMA<br>ENB |     |     | FMT<br>1 | FMT<br>0 | SEL<br>F2   | SEL<br>F1 | SEL<br>F0 | 1   | DMA<br>ENB |

| \$ 0 D | w   |            |           | (         | MSK<br>MOV |           |           |      |            | 1   |     |          |          |             |           |           |     |            |

| \$ 0 E | R/W |            |           | l         | MIDI       | DATA      | ١         |      |            | _   |     |          |          |             |           |           |     |            |

Note: Sections with diagonal lines are "Don't care",

All of the register values are set to "0" except for SELT, ADPRST, MDI TRSRST, MDI RCVRST by initial clear.

<sup>\*1:</sup> Be sure to set to '0'.

# 2. Description of Registers

Use pin A1 to select channel 1 or channel 2 of the PCM/ADPCM. Use Data Read mode to read the R/W registers that can be read.

| Address   | Name              | Function                                                                                                     |

|-----------|-------------------|--------------------------------------------------------------------------------------------------------------|

| \$00      | SELT              | Selects 2's complement or offset binary.                                                                     |

| \$01      | LSI TEST          | This register is used for testing the LSI.                                                                   |

| \$02~03   | TIMER0            | TIMER0 is a 16-bit programmable down counter.                                                                |

| \$04 ~ 05 | BASE COUNTER      | BASE COUNTER is a 12-bit programmable counter that supplies clock functions for TIMER1 and TIMER2.           |

| \$05      | TIMER1            | TIMER1 is a 4-bit programmable down counter that is controlled by the base counter clock.                    |

| \$06~07   | TIMER2            | TIMER2 is a 16-bit programmable down counter that is controlled by the base counter clock.                   |

| \$08      | T0MSK,T1MSK,T2MSK | Masks the interrupt signal generated by the corresponding timer.                                             |

| \$08      | ST0,ST1,ST2,STBC  | Control the start and stop of TIMER0, TIMER1, TIMER2 and BASE COUNTER.                                       |

| \$09      | ADPRST            | Resets PCM/ADPCM.                                                                                            |

| \$09      | L,R               | Enables output from the corresponding channel.                                                               |

| \$09      | FS0,FS1           | Selects PCM/ADPCM sampling frequency.                                                                        |

| \$09      | PCM               | Selects PCM mode or ADPCM mode.                                                                              |

| \$09      | PLY/REC           | Selects recording or playback.                                                                               |

| \$09      | ADPST             | Controls the start and stop of recording and playback.                                                       |

| \$0A      | VOLUME CONTROL    | Sets the output attenuation value.                                                                           |

| \$0B      | PCM DATA          | This register is used for writing data into the FIFO buffer and reading data from the FIFO buffer.           |

| \$0C      | DMAMOD            | Sets the mode for transfer of data between channel1 and channel2 using one channel of the controller.        |

| \$0C      | FMT0,FMT1         | Specifies the PCM data format.                                                                               |

| \$0C      | SELF0,SELF1,SELF2 | Specifies the 128-byte FIF0 data valume point for interrupt signal generation.                               |

| \$0C      | MSKFIF            | Masks the interrupt signal generated by FIFO.                                                                |

| \$0C      | DMAENB            | Selects DMA mode or CPU mode.                                                                                |

| \$0D      | MSKPOV            | Masks interrupt signals due to overrun errors during PCM/ADPCM recording.                                    |

| \$0D      | MSKMOV            | Masks interrupt signals due to overrun error during MIDI receiving.                                          |

| \$0D      | MDITRSRST         | Reset the MIDI transmit circuit.                                                                             |

| \$0D      | MSKTRQ            | Masks interrupt signals for the MIDI transmit FIFO.                                                          |

| \$0D      | MDIRCVRST         | Resets the MIDI receive circuit.                                                                             |

| \$0D      | MSKRRQ            | Masks interrupt signals for the MIDI receive FIFO.                                                           |

| \$0E      | MIDI DATA         | This register is used for writing data into the MIDI FIFO buffer and reading data from the MIDI FIFO buffer. |

#### 3. Status Bits

| Bit    | D7 | D6         | D5 | D4 | D3  | D2  | D1  | D0  |

|--------|----|------------|----|----|-----|-----|-----|-----|

|        |    |            |    |    |     |     | FIF | FIF |

| Status | ov | <b>T</b> 2 | Т1 | ТО | TRQ | RRQ | 2   | 1   |

#### 4. Description of Status

When any block generates an interrupt signal, the bit of the corresponding status register becomes "1", and at the same time /IRQ becomes "L" and the CPU is notified.

| Name      | Function                                                                                   |

|-----------|--------------------------------------------------------------------------------------------|

| 0V        | Becomes "1" when a MIDI receive overrun error or a PCM/ADPCM record overrun error occurs.  |

| T0,T1,T2  | Becomes "1" when the specified time elapses in the corresponding timer.                    |

| TRQ       | Becomes "1" when the MIDI transmit FIFO buffer is empty.                                   |

| RRQ       | Becomes "1" when the MIDI receive FIFO buffer has data in it.                              |

| FIF1,FIF2 | Becomes "1" after the PCM/ADPCM FIFO passes the point that was specified in SELF2, F1, F0. |

# ■ ELECTRICAL CHARACTERISTICS

#### 1. Absolute Maximum Ratings

| Item                  | Symbol | Rating                   | Unit |

|-----------------------|--------|--------------------------|------|

| Power supply voltage  | VDD    | -0.3~7.0                 | v    |

| Input voltage         | VI     | $-0.3 \sim V_{DD} + 0.5$ | V    |

| Operating temperature | Top    | 0~70                     | °C   |

| Storage temperature   | Tstg   | -50~125                  | °C   |

#### 2. Recommended Operating Conditions

| Item                  | Symbol                              | Minimum | Typical | Maximum | Unit |

|-----------------------|-------------------------------------|---------|---------|---------|------|

| Power supply voltage  | $\mathbf{V}_{\mathbf{D}\mathbf{D}}$ | 4.75    | 5.00    | 5.25    | V    |

| Operating temperature | $T_{op}$                            | 0       | 25      | 70      | °C   |

#### 3. DC Characteristics (Conditions; $Ta=0 \sim 70^{\circ}C$ , $VDD=5.0 \pm 0.25 V$ )

| Item                      | Symbol | Conditions            | Min.     | Typ. | Max.    | Unit    |

|---------------------------|--------|-----------------------|----------|------|---------|---------|

| Power consumption         | PD     | VDD=5.0V              |          |      | 200     | mW      |

|                           |        | fm=16.9344MHz         |          |      |         |         |

| Input highlevel voltage 1 | VIH1   | *1                    | 2.2      |      |         | V       |

| Input lowlevel voltage 1  | VIL1   | *1                    |          |      | 0.8     | V       |

| Input highlevel voltage 2 | VIH2   | *2                    | 3.5      |      |         | V       |

| Input lowlevel voltage 2  | VIL2   | *2                    |          |      | 1.0     | V       |

| Input leakage current     | Ili    | $V_I = 0 \sim 5V, *3$ | -10      |      | 10      | $\mu A$ |

| Input capacity            | Cı     |                       |          |      | 10      | pF      |

| Output highlevel voltage  | Vон    | $IOH = -80\mu A$      | VDD -1.0 |      |         | V       |

| Output lowlevel voltage   | Vol    | IoL=2.0mA             |          |      | Vss+0.4 | v       |

| Output capacity           | Co     |                       |          |      | 10      | pF      |

| Output leakage current    | ILO    | $V_I = 0 \sim 5V, *4$ | -10      |      | 10      | μΑ      |

| Pull up registance        | Ru     |                       | 80       |      | 400     | kΩ      |

Note) \*1: Applied to /WR, /RD, /CS, A0~A9, AEN, D0~D7, RXD, /CSGD, GP4~GP7, /DACK1, /DACK2 (when used as input pins)

<sup>\*2:</sup> Applied to XI, /IC

<sup>\*3:</sup> Applied to /WR, /RD, A0  $\sim$  A7, AEN, D0  $\sim$  D7, RXD, /CSGP, GP4  $\sim$  GP7 (When used as input pins)

<sup>\*4:</sup> When D0~D7 are in high impedance

#### 4. AC Characteristics (Conditions; $Ta=0 \sim 70^{\circ}C$ , $VDD=5.0 \pm 0.25 \text{ V}$ )

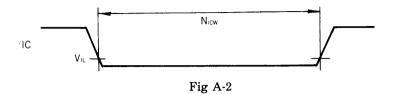

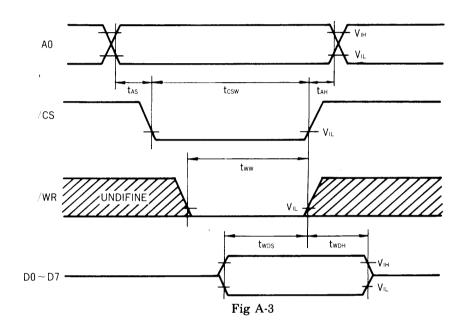

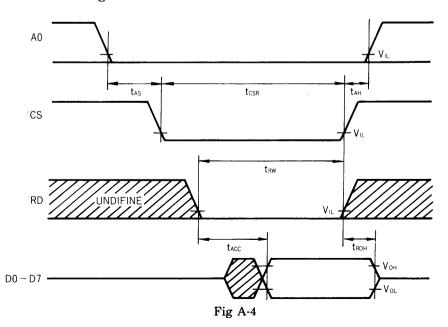

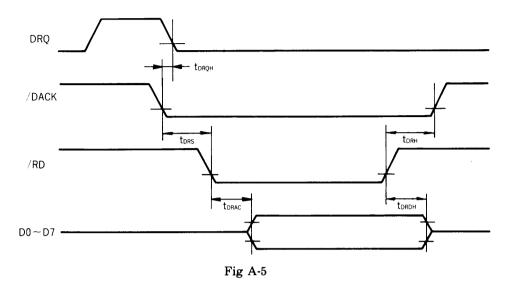

| Item                      | Symbol       | Figure     | Min. | Тур.    | Max. | Unit     |

|---------------------------|--------------|------------|------|---------|------|----------|

| Master clock frequency    | fм           | Fig A-1    |      | 16.9344 |      | MHz      |

| Master clock duty         | D            |            | 45   | 50      | 55   | %        |

| Reset pulse width         | Nicw         | Fig A-2    | 80   |         |      | cycle *1 |

| Address setup time        | tas          | Fig A-3, 4 | 10   |         |      | ns       |

| Address hold time         | tah          | Fig A-3, 4 | 10   |         |      | ns       |

| Chip select write width   | tcsw         | Fig A-3    | 50   |         |      | ns       |

| Chip select read width    | tcsr         | Fig A-4    | 100  |         |      | ns       |

| Write pulse width         | tww          | Fig A-3    | 50   |         |      | ns       |

| Write data setup time     | twds         | Fig A-3    | 10   |         |      | ns       |

| Write data hold time      | twdh         | Fig A-3    | 20   |         |      | ns       |

| Read pulse width          | trw          | Fig A-4    | 100  |         |      | ns       |

| Read data access time     | tacc         | Fig A-4    |      |         | 100  | ns       |

| Read data hold time       | <b>t</b> rdh | Fig A-4    | 10   |         |      | ns       |

| DRQ hold time             | tdrqh        | Fig A-5    |      |         | 50   | ns       |

| DMA read setup time       | tdrs         | Fig A-5    | 50   |         |      | ns       |

| DMA read hold time        | tdrh         | Fig A-5    | 20   |         |      | ns       |

| DMA read data access time | tdrac        | Fig A-5    |      |         | 100  | ns       |

| DMA read data hold time   | tdrdh        | Fig A-5    | 10   |         |      | ns       |

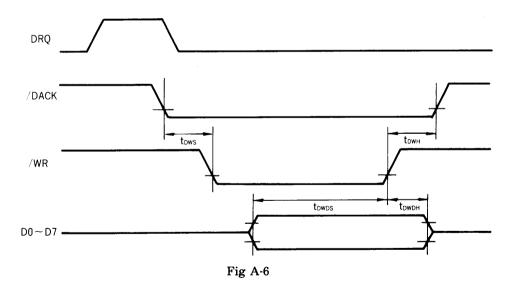

| DMA write setup time      | tows         | Fig A-6    | 50   |         |      | ns       |

| DMA write hold time       | tоwн         | Fig A-6    | 20   |         |      | ns       |

| DMA write data setup time | towds        | Fig A-6    | 10   |         |      | ns       |

| DMA write data hold time  | tоwон        | Fig A-6    | 20   |         |      | ns       |

Note) \*1: Master clock cycle

## 5. Analog Characteristics (Conditions; Ta=0~70°C, VDD=5.0 V)

| Item              | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|-------------------|--------|------------|------|------|------|------|

| Input voltage     | VIA    | *1         |      |      | 4.8  | V    |

| Output voltage    | Voa    | *2         |      |      | 4.8  | v    |

| DC offset voltage | CV     | *3         |      | 2.5  |      | v    |

| Offset voltage    | Voff   | *2         |      |      | 0.1  | v    |

| Linearity error   |        | *2         |      | i    | ± 30 | mV   |

| Step error        |        | *2         |      |      | ±1.0 | LSB  |

Note) \*1: Applied to AIN1, AIN2

\*2: Applied to L1, R1, L2, R2

\*3: Applied to CV

# 6. Timing Diagram

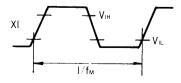

(1) Clock timing

Fig A-1

#### (2) Reset pulse

#### (3) Address/Data write timing

Note: tcsw, tww, and twdh are based on either /CS or /WR being driven to high level.

#### (4) Status/Data read timing

Note: tacc is based on whichever of /CS or /RD goes to the low level last.

> tcsw, trw, and twdh are based on either /CS or /WR being driven to high level.

# (5) DMA read timing

# (6) DMA write timing

# **■ EXTERNAL VIEWS**

• YMZ263B-F

### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

# AGENCY

## YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Toyooka-mura, Iwata-gun, Shizuoka-ken, 438-0192

Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office Namba Tsujimoto Nissei Bldg. 4F

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

■ U.S.A. Office YAMAHA Systems Technology

100 Century Center Court, San Jose,

CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791