# YAMAHA L S I

# **YTD428**

### **IDSU**

#### **DSU LSI for the ISDN Terminal Equipment**

### INTRODUCTION

YTD428 is a LSI which provides the ISDN subscriber interface (two-wire time compression multiplexing operation) and the NT side of the ISDN Basic Rate user-network interface function (digital four-wire time-division full-duplex operation). It is capable of providing the electric characteristics conforming to TTC Standard JT-I430 and JT-G961.

YTD428 incorporates the circuit termination and line termination functions on a single chip allowing the user to easily configure a DSU (Digital Service Unit) that consumes small amount of power at a minimal cost.

In addition, a TTL interface is provided at the T reference point (layer 1 level). This feature is especially effective when combined with YAMAHA's ISDN LSI for S/T reference point interface, YTD423 or YTD418. It allows considerable cost reduction on parts around the pulse transformer when constructing a device with a built-in DSU.

The driver/receiver section of the T reference point interface can be separated from the DSU section and be used independently. The user can enable or disable this feature as necessary.

YAMAHA CORPORATION:

YTD428 CATALOG CATALOG No.:4TD428A2 1998.12

#### ☐ Features

#### **■** Circuit Termination Section

- Conforms to TTC Standard JT-I430 and JT-G961

- Digital four-wire time-division full-duplex operation

- Two-wire time compression multiplexing operation

- Transmission rate at U reference point: 320 kbit/s, at T reference point: 192 kbit/s

- Frame assembling and disassembling function

- State transition control

- Loopback function

- T reference point timing control (switch between short passive bus / extended passive bus, point-to-point)

- U reference point driver control

#### **■** Line Termination Section

- Conforms to TTC Standard JT-G961

- $\bullet \sqrt{f}$  equalizer

- Bridged tap equalizer

#### **■** T Reference Point Interface Section

• The T reference point driver / receiver section can be separated from DSU section, and use independently (TE mode). The user can enable or disable this feature as necessary.

#### ■ Others

- +5 V single power supply

- Low power consumption

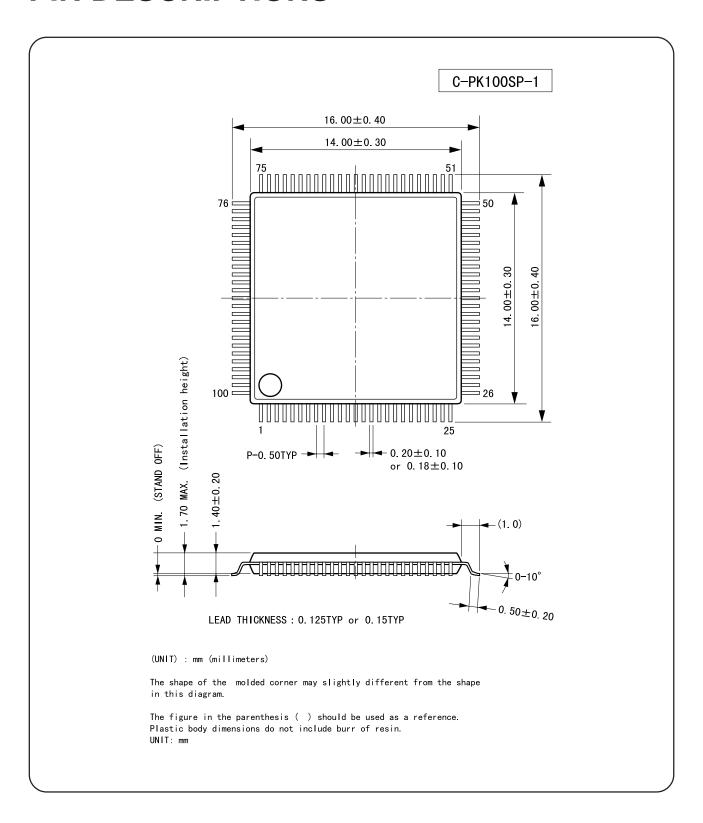

- 100 pin SQFP

# **BLOCK DIAGRAM**

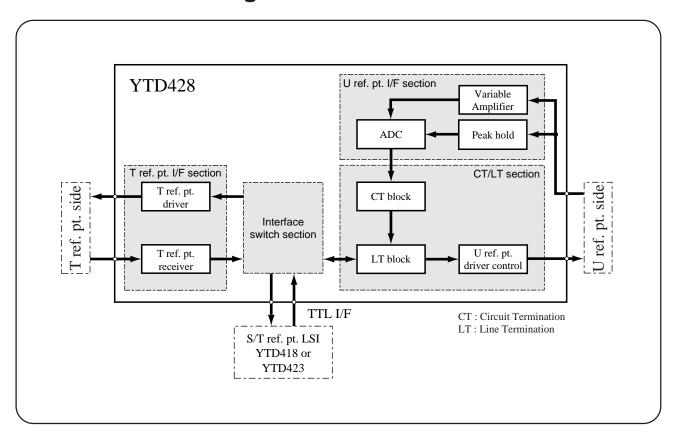

### ☐ Internal Block Diagram

### □ DSU Configuration Example

YTD428 incorporates the circuit termination, line termination, T reference point interface and U reference point interface functions on a single chip allowing the user to easily configure a DSU that consumes small amount of power at a minimal cost. The user can select from the two types of configurations. One is the general configuration in which a transformer is used at the T reference point interface. The other is a configuration in which a TTL interface is used to directly connect to the T reference point LSI.

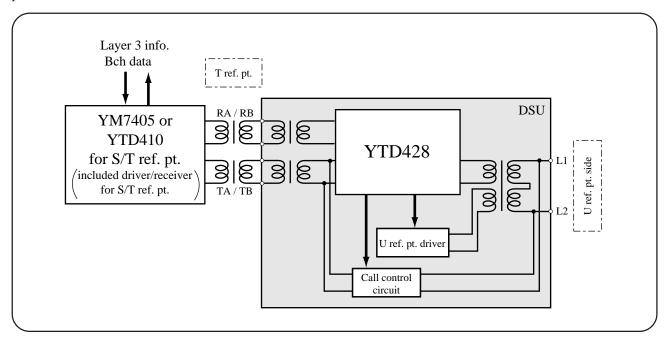

#### ■ Configuration example of a general DSU

Various functions are incorporated on a single chip allowing the user to create a low power-consuming product at a low cost.

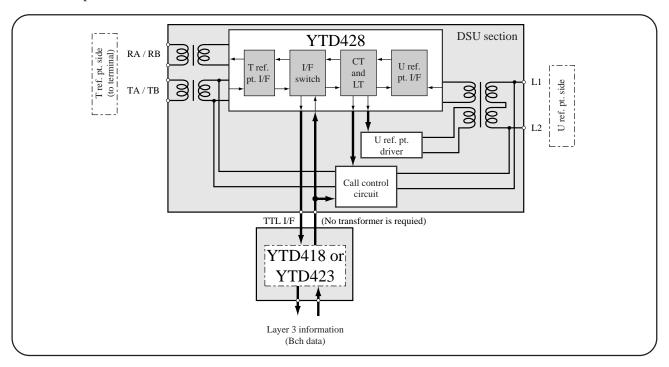

# ■ Configuration example of a device with a built-in DSU that uses a TTL interface at the T ref. pt.

When using YTD428 with YAMAHA'S S/T reference point interface LSI to create a device with a built-in DSU, they can be connected directly through the TTL interface. This results in a reduction of pulse transformer parts.

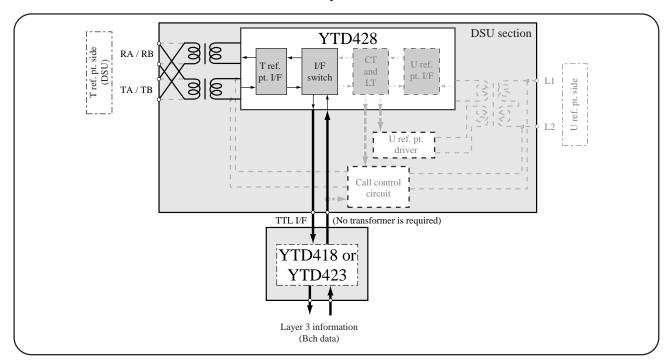

#### **■** Example of using T reference point driver / receiver section independently

By setting the Interface switch, the drive / receiver of the T reference point interface section can be separated from the circuit termination (CT) and line termination (LT) section and be used independently. The user can enable or disable this feature as necessary.

YAMAHA YTD428

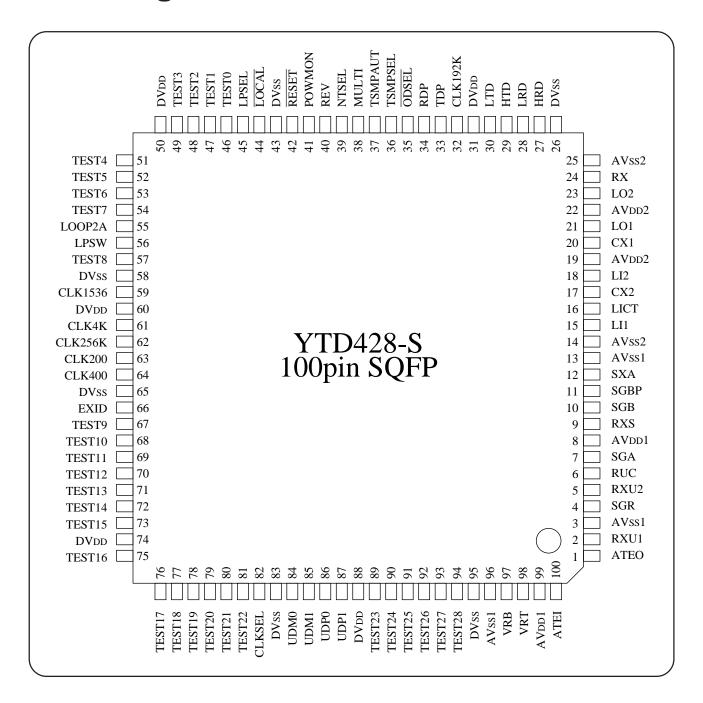

# **Pin Assignments**

# **ELECTRICAL CHARACTERISTICS**

## **☐ Absolute Maximum Ratings**

| Parameter           | Symbol            | Min.      | Max                   | Units |

|---------------------|-------------------|-----------|-----------------------|-------|

| Supply Voltage      | $V_{\mathrm{DD}}$ | Vss - 0.3 | Vss + 7.0             | V     |

| Input Voltage       | VI                | Vss - 0.3 | V <sub>DD</sub> + 0.3 | V     |

| Storage Temperature | Tstg              | - 50      | + 125                 | ° C   |

## **☐** Recommended Operating Conditions

| Parameter             | Symbol          | Range         |

|-----------------------|-----------------|---------------|

| Supply Voltage        | V <sub>DD</sub> | 5.0 V ± 5 %   |

| Operating Temperature | Тор             | -20 ~ +70 ° C |

### □ DC Characteristics

(DVDD = AVDD = 5.0V, DVss = AVss = 0.0 V, Operating Temperature: Top = 25 °C)

| ]              | Parameter                 | Symbol          | Condition | Min.                      | Тур.                | Max.                   | Units |

|----------------|---------------------------|-----------------|-----------|---------------------------|---------------------|------------------------|-------|

| _              | Output Allowable apedance | Zo              | Note 1    | 30                        |                     |                        | kΩ    |

|                | Receive Buffer apedance   | Zi1             | Note 2    | 10                        |                     |                        | МΩ    |

| Analog Voltage | Signal Reference          | Vsg             | Note 3    | 2.45                      | 2.50                | 2.55                   | V     |

| ADC            | Self-Bias VRT             | V <sub>RT</sub> | Note 4    | 0.7AV <sub>DD</sub> - 0.1 | 0.7AV <sub>DD</sub> | $0.7AV_{\rm DD} + 0.1$ | V     |

| ADC            | Self-Bias VRB             | V <sub>RB</sub> | Note 5    | 0.3AV <sub>DD</sub> - 0.1 | 0.3AV <sub>DD</sub> | $0.7AV_{\rm DD} + 0.1$ | V     |

Note 1 With respect to SGR, SXA pins.

Note 2 With respect to RXU1 and RXU2 pins.

Note 3 Set SGR pin to open.

Note 4 With respect to VRT pin.

Note 5 With respect to VRB pin.

$(DV_{DD} = AV_{DD} = 5.0 \text{ V}, T_{op} = -20 \sim 70 \text{ }^{\circ}\text{C})$

| Parameter                                  | Symbol          | Condition | Min.                   | Тур. | Max.       | Units |

|--------------------------------------------|-----------------|-----------|------------------------|------|------------|-------|

| High I and I was Walter (TTI)              | Vih             | (Note 1)  | 2.2                    |      |            | V     |

| High Level Input Voltage (TTL)             | V <sub>IH</sub> | (Note 2)  | 3.0                    |      |            | V     |

| Law level Input Voltage (TTI)              | VIL             | (Note 1)  |                        |      | 0.8        | V     |

| Low level Input Voltage (TTL)              | VIL             | (Note 2)  |                        |      | 0.8        | V     |

| High Level Input Voltage (CMOS)            | V <sub>IH</sub> | (Note 3)  | 3.5                    |      |            | V     |

| Low Level Input Voltage (COMS)             | VIL             | (Note 3)  |                        |      | 1.0        | V     |

| TY 1 I I O I I I I I I I I I I I I I I I I | Vон             | (Note 4)  | DV <sub>DD</sub> - 1.0 |      |            | V     |

| High Level Output Voltage (TTL)            |                 | (Note 5)  | DV <sub>DD</sub> - 1.0 |      |            | V     |

| I I Outroot Vales (TTI)                    | ¥7              | (Note 4)  |                        |      | DVss + 0.4 | V     |

| Low Level Output Voltage (TTL)             | Vol             | (Note 5)  |                        |      | DVss + 0.4 | V     |

| Low Level Output Voltage (Open-D)          | Vol             | (Note 6)  |                        |      | DVss + 0.4 | V     |

| Leak Current                               | IL              |           | -10                    |      | 10         | μΑ    |

| Idle Condition Leak Current                | Ilz             |           | -10                    |      | 10         | μΑ    |

| Power Supply Current                       | Idd             | (Note 7)  |                        | 36   |            | mA    |

- Note 1 With respect to the digital pins other than RESET, POWDET, CLK1536 and TEST23 ~ 28 pins

- Note 2 With respect to RESET, POWDET pins

- Note 3 With respect to CLK1536, TEST23 ~ 28 pins

- Note 4 With respect to the pin other than HRD, LRD pins

Test condition: Output Current "H" level (IoH) = -0.2 mA, Output Current "L" level (IoL) = 1.2 mA

- Note 5 With respect to HRD, LRD pins (when ODSEL = "H"), Test condition: IoH = -0.2 mA, IoL = 1.2 mA

- Note 6 With respect to HRD, LRD pins (when  $\overline{ODSEL} = "L"$ ), Test condition: IoL = 1.2 mA

- Note 7 With using T ref. pt. analog interface

### **□** AC Characteristics

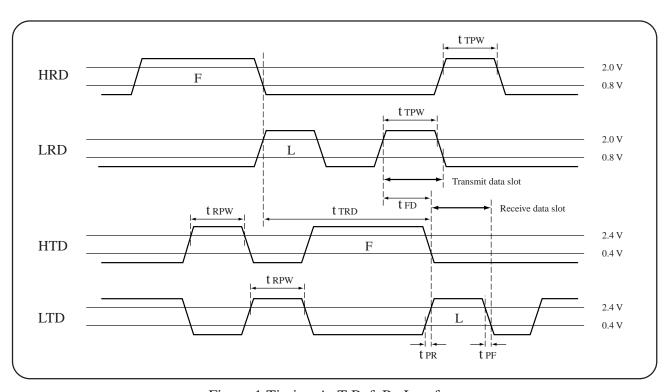

#### ■ T Reference Point Receive Characteristic (NT mode)

$(V_{DD} = 5.0 \text{ V}, T_{op} = -20 \sim 70 \text{ }^{\circ}\text{C}, \text{Load Capacity: } \text{CL} = 50 \text{ pF})$

| Parameter                 | Symbol      | Condition         | Min. | Тур.  | Max. | Units |

|---------------------------|-------------|-------------------|------|-------|------|-------|

| Transmit Pulse Width      | ttpw        |                   | 5.00 | 5.208 | 5.40 | μs    |

| Receive Pulse Width       | trpw        |                   |      | 5.208 |      | μs    |

| Rise Time                 | <b>t</b> PR |                   |      |       | 260  | ns    |

| Fall Time                 | <b>t</b> PF |                   |      |       | 30   | ns    |

| Phase Diffierence between | ttrd        | Note 1            | 10.0 |       | 14.0 | μs    |

| Tx and Rx signals         | ttrd        | Note 2            | 10.0 |       | 42.0 | μs    |

| Phase Difference between  | tрн         | Note 1,<br>Note 3 |      |       | 4.0  | μs    |

| Rx signals                | tрн         | Note 2,<br>Note 3 |      |       | 2.0  | μs    |

Note 1 With respect to using the Fixed timing

Note 2 With respect to using the Adaptive timing

Note 3 This value shows the difference between two terminals which are connected with bus system.

Figure 1 Timing At T Ref. Pt. Interface

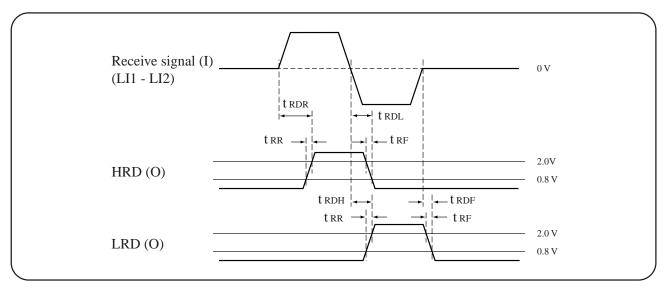

#### ■ T Reference Point Receive Characteristic (TE mode)

$(V_{DD} = 5.0 \text{ V}, T_{op} = -20 \sim 70 \text{ }^{\circ}\text{C}, C_{L} = 50 \text{ pF})$

| Parameter  | Symbol | Condition | Min. | Тур. | Max. | Units |

|------------|--------|-----------|------|------|------|-------|

|            | trdr   |           |      |      | 700  | ns    |

| Dalay Tima | trdl   |           |      |      | 200  | ns    |

| Delay Time | trdh   |           |      |      | 700  | ns    |

|            | trdf   |           |      |      | 700  | ns    |

| Rise Time  | trr    | Note 1    |      |      | 30   | ns    |

| Fall Time  | trf    | Note 2    |      |      | 30   | ns    |

Note 1 With respect to HRD, LRD pins (ODSEL = "H")

Note 2 With respect to HRD, LRD pins

Note 3 Figure 2 shows the timing when RDP = "H". When RDP = "L", the output signal polarity from HRD and LRD pins are inverted.

Figure 2 Receive Timing

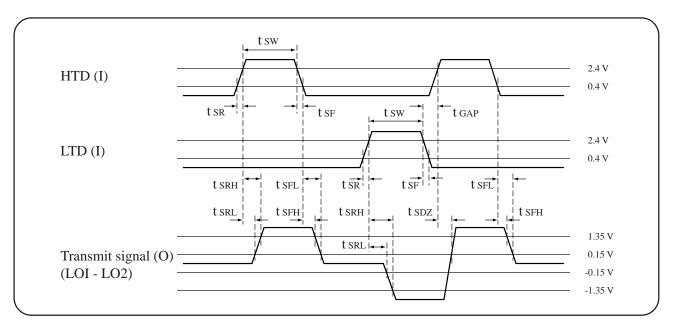

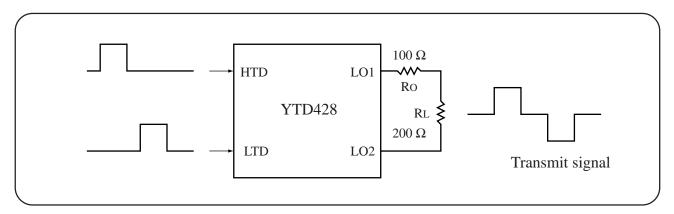

#### ■ T Reference Point Transmit Characteristic (TE mode)

$(V_{DD} = 5.0 \text{ V}, T_{op} = -20 \sim 70 \text{ }^{\circ}\text{C}, C_{L} = 50 \text{ pF})$

| Parameter             | Symbol | Condition | Min. | Тур. | Max. | Units |

|-----------------------|--------|-----------|------|------|------|-------|

| HTD, LTD Pulse Period | tsw    |           | 4.95 |      | 5.45 | μs    |

| HTD, LTD Pulse Gap    | tgap   |           | 0    |      | 260  | ns    |

| HTD, LTD Rise Time    | tsr    |           |      |      | 260  | ns    |

| HTD, LTD Fall Time    | tsf    |           |      |      | 30   | ns    |

|                       | tsrl   | Note 1    | 0    |      | 490  | ns    |

| Transmit Signal       | tsrh   | Note 1    | 490  |      | 1010 | ns    |

| Delay Time            | tsfh   | Note 1    | 0    |      | 165  | ns    |

|                       | tsfl   | Note 1    | 165  |      | 685  | ns    |

| Zero Cross Delay Time | tsdz   | Note 1    | 490  |      | 1010 | ns    |

Note 1 Measuring with RL voltage drop as shown in Figure 4.

Note 2 Figure 3 shows the timing when TDP = "H". When TDP = "L", the output signal polarity from HRD and LRD pins are inverted.

Figure 3 Transmit Timing

Figure 4 Transmit Block Test Circuit

#### **■** Driver, Receiver I/O Impedance

| Parameters               | Symbol | Condition         | Min. | Тур. | Max. | Units |

|--------------------------|--------|-------------------|------|------|------|-------|

| Receiver Input Impedance | Zli    | LI1 - LI2         | 50   |      |      | kΩ    |

| Driver Ouput Impedance   | Zloi   | LO1 - LO2 (Note1) | 50   |      |      | kΩ    |

| Driver Ouput Impedance   | ZL00   | LO1 - LO2 (Note2) |      | 15   |      | Ω     |

Note 1 When no pulse is output.

Note 2 When pulse is output.

# **PIN DESCRIPTIONS**

### **IMPORTANT NOTICE**

- Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. Yamaha assumes no liability for incidental, consequential, or special damages or injury that may result from misapplication or improper use or operation of the Products.

- 4. Yamaha makes no warranty or representation that the Products are subject to intellectual property license from Yamaha or any third party, and Yamaha makes no warranty excludes any liability to the Customer or any third party arising from or related to the Products' infringement of any third party's intellectual property rights, including the patent, copyright, trademark or trade secret rights of any third party.

- 5. Examples of use described herein are merely to indicate the characteristics and performance of Yamaha products. Yamaha assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein. Yamaha makes no warranty with respect to the products, express or implied, including, but not limited to the warranties of merchantability, fitness for a particular use and title.

The specifications of this product are subject to improvement changes without prior notice.

| AGENCY——— | Address inquiries | IAHA CORPORATION ————————————————————————————————————                                                                                                     |

|-----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | ■ Head Office     | 203, Matsunokijima, Toyooka-mura<br>Iwata-gun, Shizuoka-ken, 438-0192<br>Electronic Equipment Business section<br>Tel. 81-539-62-4918 Fax. 81-539-62-5054 |

|           | ■ Tokyo Office    | 2-17-11, Takanawa, Minato-ku,<br>Tokyo, 108-8568<br>Tel. 81-3-5488-5431 Fax. 81-3-5488-5088                                                               |

|           | ■ Osaka Office    | Namba Tsujimoto Nissei Bldg, 4F<br>1-13-17, Namba Naka, Naniwa-ku,<br>Osaka City, Osaka, 556-0011<br>Tel. 81-6-6633-3690 Fax. 81-6-6633-3691              |

|           | ■ U.S.A. Office   | YAMAHA Systems Technology.<br>100 Century Center Court, San Jose, CA95112<br>Tel. 1-408-467-2300 Fax 1-408-437-8791                                       |