# **FAROUDJA**Laboratories YCP 101 Digital Video Enhancer

The YCP 101 Digital Video Enhancer uses Faroudja Labs' patented nonlinear luma and chroma processing technology to enhance the quality of a YUV video signal derived either from a component source or separated from an NTSC or PAL source. The signals are all interpolated at appropriate points in their paths to double the sampling rates. This prevents the bandwidth expansion caused by nonlinear processing from introducing aliasing distortion. In the luma path, small edges above the programmable noise threshold and large edges are processed independently in a manner which gives optimum edge enhancement overall. In the chroma path only large edge enhancement is done, using a luma component factor in the chroma processing. Most of the parameters involved in the process are programmable via the serial control bus, although the built-in default values also allow the device to be used without any external control processor. All I/O paths are 10 bits wide and the internal signal processing is consistent with this.

#### **Features:**

- Digital Luminance and Chrominance Enhancement consistent with 10-bit digital I/O

- Digital YUV outputs

- Input luminance sampling rates up to 30 MHz, output luminance rates up to 60 MHz

- Up to 1150 pixels/line

- Adaptive Digital Averager to reduce cross color with NTSC signal sources and eliminate Hanover blinds with PAL sources

- Can be used in conjunction with FRE 201 Digital Line Doubler as a pre- or post-processor

- Horizontal and Vertical Detail Processors

- 3-Wire Serial Control bus

- 0.5 watts typical power dissipation

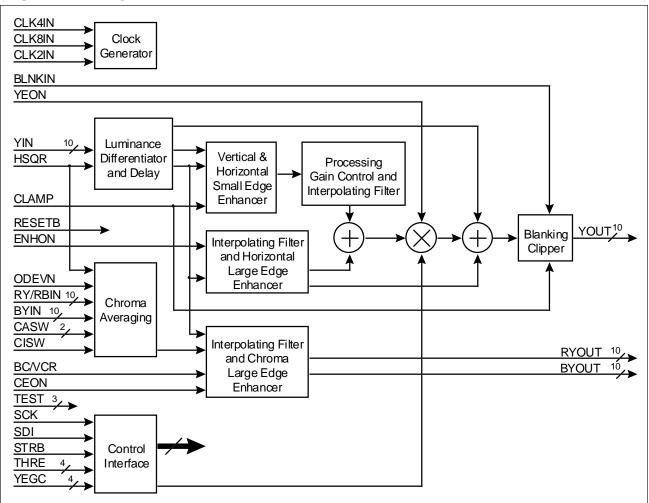

#### Simplified Block Diagram

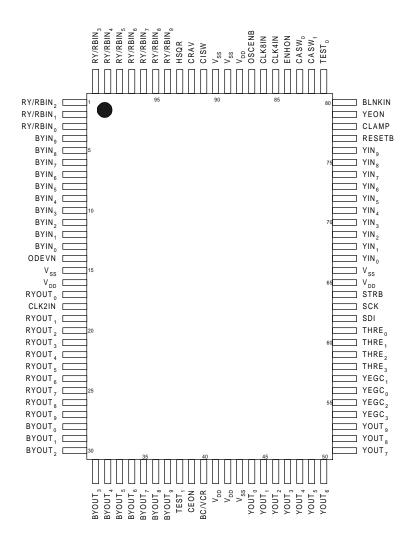

## **Packaging and Pinout Information**

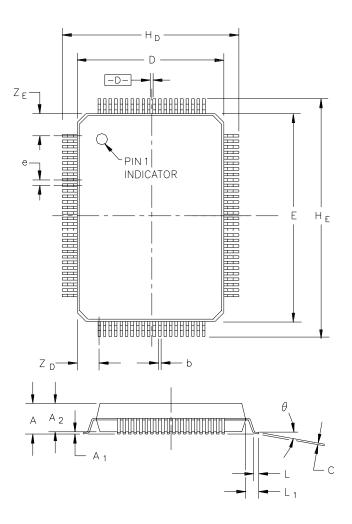

Package: 100-pin PQFP.  $\theta_{ja} = xx \circ C/watt$

### **Pin Connections and Functions**

| Pin #             | Name                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control           | Signals             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 58-61             | THRE <sub>3-0</sub> | Detail processor threshold control. The levels set on these inputs allow the threshold used in the detail processor circuit to be adjusted. The levels can be changed asynchronously as long as the serial control bus is not used. The value can also be set via the serial control interface; any value written in this way will override the value set with the $\text{THRE}_{3-0}$ inputs. A rising edge on the STRB input transfers control to the serial bus and the device must be reset to reactivate the $\text{THRE}_{3-0}$ inputs.                   |

| 79                | YEON                | Luminance enhancement on. When this input is set high the luminance enhancement function will be turned on. When it is set low the function will be turned off.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 54, 55,<br>57, 56 | YEGC <sub>3-0</sub> | Luminance large-edge enhancement gain control. The levels set on these inputs allow the gain of the luminance small-edge enhancement circuit to be adjusted. The levels can be changed asynchronously as long as the serial control bus is not used. The value can also be set via the serial control interface; any value written in this way will override the value set with the YEGC <sub>3-0</sub> inputs. A rising edge on the STRB input transfers control to the serial bus and the device must be reset to re-activate the YEGC <sub>3-0</sub> inputs. |

| 84                | ENHON               | Luminance large-edge enhancement on. When this input is set high this function will be turned on. When it is set low the function will be turned off.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14                | ODEVN               | Odd or even number of pixels/line. This input should be set high for applications with an even number of pixels/line, such as NTSC sampled at $4 \cdot f_{SC}$ . It should be set low for applications with an odd number of pixels/line, such as PAL sampled at $4 \cdot f_{SC}$ .                                                                                                                                                                                                                                                                             |

| 39                | CEON                | Chrominance enhancement on. When this input is set high the chrominance enhancement function will be turned on. When it is set low the function will be turned off.                                                                                                                                                                                                                                                                                                                                                                                             |

| 92                | CRAV                | Chroma averager on. When this input is set high the 2-line chroma averager is turned on. This function should be used with PAL signals only if there is no other chroma averager in the system. When this input is set low the chroma averager is turned off.                                                                                                                                                                                                                                                                                                   |

| 81,38             | TEST <sub>1-0</sub> | Test inputs. These pins should be set high for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 82-83             | CASW <sub>1-0</sub> | Chroma averager mode select. These inputs select the output of the chrominance averaging circuit. The selections are shown in Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 40                | BC/VCR              | Broadcast/VCR signal processing control. When the input signal source is of broadcast quality this input should be set high for optimum processing. When the input source is of typical consumer VCR quality this input should be set low for optimum processing.                                                                                                                                                                                                                                                                                               |

| 91                | CISW                | Chroma input mode switch. When this input is set high, multiplexed R-Y and B-Y signals are input on the $RY/RBIN_{9.0}$ bus at the luminance clock rate and the $BYIN_{9.0}$ bus is not used. When this input is set low the R-Y signal is input on the $RY/RBIN_{9.0}$ bus and the B-Y signal is input on the $BYIN_{9.0}$ bus.                                                                                                                                                                                                                                |

| 77                | RESETB              | Reset. When this input is set low it will reset all the internal registers to the default states.<br>Refer to the section on the control registers for details of these states. The device must be<br>reset after it is powered-up.                                                                                                                                                                                                                                                                                                                             |

| 63                | SCK                 | 3-wire serial control bus clock input. Refer to the section on the serial port for timing details.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 62                | SDI                 | 3-wire serial control bus data input. Data can be written to the control registers via this pin.<br>Refer to the section on the serial port for timing and format details and to the section on the registers for programming information.                                                                                                                                                                                                                                                                                                                      |

| 64                | STRB                | 3-wire serial control bus strobe input. Refer to the section on the serial port for timing details.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin #         | Name                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Si      | gnals                  |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 87            | OSCENB                 | Internal oscillator enable input. This pin should be tied high during normal operation. If the external clocks should be stopped during operation this input should be set low to enable the oscillator. This will provide an internal clock to prevent damage occurring to the device.                                                                                                                                         |

| 76-67         | YIN <sub>9-0</sub>     | 10-bit luminance signal input bus. This signal is sampled on the rising edges of the CLK4IN clock.                                                                                                                                                                                                                                                                                                                              |

| 94-100<br>1-3 | RY/RBIN <sub>9-0</sub> | 10-bit R-Y or multiplexed R-Y and B-Y signal input bus. When CISW is set low the R-Y signal is input on the RY/RBIN <sub>9-0</sub> bus. In this mode the chroma signals are sampled on the rising edges of the CLK2IN clock. When the CISW input is set high, multiplexed R-Y and B-Y signals are input on the RY/RBIN <sub>9-0</sub> bus. In this mode the chroma signals are sampled on the rising edges of the CLK4IN clock. |

| 4-13          | BYIN <sub>9-0</sub>    | 10-bit B-Y signal input bus. When CISW is set low the B-Y signal is input on the BYIN <sub>9-0</sub> bus. In this mode the chroma signals are sampled on the rising edges of the CLK2IN clock. When the CISW input is set high BYIN <sub>9-0</sub> bus is not used and these pins should be tied low.                                                                                                                           |

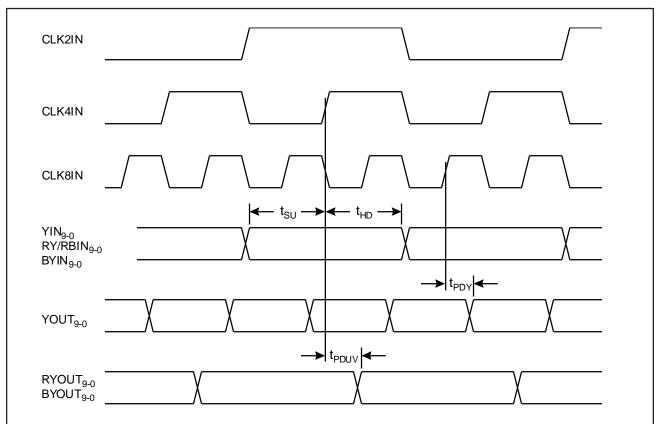

| 86            | CLK8IN                 | Clock input at 2 times the luminance sampling rate. This clock is used for the internal signal processing and output signal timing. Refer to the timing diagrams for the relationships between the clocks.                                                                                                                                                                                                                      |

| 85            | CLK4IN                 | Clock input at the luminance sampling rate. This clock is used for the luma signal timing.<br>Refer to the timing diagrams for the relationships between the clocks.                                                                                                                                                                                                                                                            |

| 18            | CLK2IN                 | Clock input at the chroma sampling rate. This clock is used for the chroma signal timing.<br>Refer to the timing diagrams for the relationships between the clocks.                                                                                                                                                                                                                                                             |

| 93            | HSQR                   | Horizontal frequency square wave input. This signal should be synchronized to the horizontal scanning frequency. The rising edge is used to reset the internal line memory counter.                                                                                                                                                                                                                                             |

| 80            | BLNKIN                 | Blanking input. This signal indicates the blanking period of the composite input signal.                                                                                                                                                                                                                                                                                                                                        |

| 78            | CLAMP                  | Clamp input. This signal should go low during the back porch period of each line.                                                                                                                                                                                                                                                                                                                                               |

| Output        | Signals                |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 53-44         | YOUT <sub>9-0</sub>    | Luminance output bus. The luminance (Y) output signal is available at these pins. The signal is clocked out on the rising edges of the CLK8IN clock.                                                                                                                                                                                                                                                                            |

| 27-19,<br>17  | RYOUT <sub>9-0</sub>   | R-Y chrominance output bus. The R-Y (U) chrominance output signal is available at these pins. The signal is clocked out on the rising edges of the CLK4IN clock.                                                                                                                                                                                                                                                                |

| 37-28         | BYOUT <sub>9-0</sub>   | B-Y chrominance output bus. The R-Y (V) chrominance output signal is available at these pins. The signal is clocked out on the rising edges of the CLK4IN clock.                                                                                                                                                                                                                                                                |

| Power S       | upply Connec           | tions (not shown on Block diagram)                                                                                                                                                                                                                                                                                                                                                                                              |

| See list      | V <sub>SS</sub>        | Ground connections. Connect to the digital ground plane. Pins: 15, 43, 66, 89, 90                                                                                                                                                                                                                                                                                                                                               |

| See list      | V <sub>DD</sub>        | Power connections. Connect to the digital 5.0 volt power supply and decouple to the digital ground plane. Pins: 16, 41, 42, 65, 88                                                                                                                                                                                                                                                                                              |

## **Description of Functional Blocks**

#### **Clock Generation Block**

The internal clocks are derived from the three input clocks, CLK2IN, CLK4IN and CLK8IN, using gating circuits. CLK4IN is used to sample the luminance input and the multiplexed chrominance inputs when CISW is set high. CLK2IN is used to sample the chrominance inputs when CISW is set low. CLK8IN is used for the luminance output clock and CLK4IN is used for the chrominance output clock.

#### Serial Interface Block

The serial Interface block consists of a 3-wire input decoder and a number of control and status registers. When the STRB input is set low the SCK (clock) and SDI (data) inputs are enabled and data is clocked serially through a 64-bit shift register. When the STRB input goes high the first 8 bits of the last 64 bits to enter the register are examined for a valid address (AD<sub>H</sub>). If the address is valid the remaining data is latched into the control registers. Refer to the section on the serial port for timing and format details and to the section on the registers for programming information.

#### Luminance Differentiator and Delay Block

The luminance signal is first resampled with the CLK8IN clock and interpolated up to that sampling rate. It is then processed in the Luminance Differentiator and Delay Block to generate the small- and large-edge functions required in the lumina edge enhancer circuits. This block also contains the delays necessary to time-align the various outputs of the block.

#### Vertical and Horizontal Small-Edge Enhancer Block

The outputs of the differentiator block are passed into the vertical and horizontal small-edge enhancer block. The processing of the vertical (line-to-line) and horizontal (pixel-to-pixel) edges is carried out in two separate subblocks inside this block. Only small edges are processed in this block. The nonlinear transfer function of the processor eliminates all large edges, which are processed separately in the Large-Edge Enhancer Block. An adjustable threshold also prevents the enhancement of very small edges to eliminate luma noise enhancement.

#### Processing Gain control and Low-Pass Filter

The output of the small-edge enhancer is passed into the gain control and low-pass filter block. The gain control circuit allows the amplitude of the signal to be controlled manually. The signal is then interpolated to double the sapling rate to match the output of the horizontal large-edge enhancer block.

#### Horizontal Large-Edge Enhancer Block

The outputs of the differentiator block are passed into the horizontal large-edge enhancer block. Only the horizontal i.e., pixel-to-pixel, edges are processed in this way. The nonlinear transfer function of the processor eliminates all small edges and expands the bandwidth of the signal. Consequently, the sampling rate is first doubled with an interpolating filter to prevent the introduction of aliasing distortion. The output of this block is then summed with the output of the small-edge enhancer/low-pass filter and a delayed version of the direct-path signal in such a way as to provide a seamless integration of the two processing paths and the direct path, resulting in optimum overall enhancement of the luminance signal.

#### **Blanking Clipper**

The blanking clipper is used to make corrections to the blanking level before the final output of the luma signal.

#### **Chroma Adaptive Averager Block**

The chrominance signals are first resampled with the CLK4IN clock and interpolated up to that sampling rate. The signals are then multiplexed if the input is set to separate R-Y and B-Y inputs (CISW set low) an passed into the Adaptive Averaging Filter. The filter is time multiplexed between the R-Y and B-Y signals and averages odd and even lines to eliminate Hanover blinds in signals from PAL coded sources. The transfer function of the averaging filter is adaptively controlled to minimize its effect on horizontal chroma edges. Although the averager can also be used with signals from NTSC coded sources it can be disabled by means of the CASW<sub>1-0</sub> inputs, as shown in Table 1, below:

| Mode | CASW <sub>1-0</sub> | Output of Adaptive Averager Block |

|------|---------------------|-----------------------------------|

| 1    | 00                  | Averager input with 0 line delay  |

| 2    | 01                  | Averager input with 2 line delay  |

| 3    | 10                  | Averager input with 1 line delay  |

| 4    | 11                  | Averager output                   |

Since the averager has a 1 line delay, which matches the delay in the luma path, the normal operating modes will be 3 for (NTSC) and 4 (for PAL).

#### Chroma Large-Edge Enhancer Block

The outputs of the chroma averager block are passed into the chroma large-edge enhancer block, where the R-Y and B-Y signals are demultiplexed to be independently processed. Only the horizontal i.e., line-to-line, chroma edges are processed. The nonlinear transfer function of the processor eliminates all small edges and only the large edges are enhanced to eliminate chroma noise enhancement. Consequently, the sampling rate is first doubled with an interpolating filter to prevent the introduction of aliasing distortion. Consequently, the sampling rate is first doubled with an interpolating filter to prevent the introduction of aliasing distortion. The chroma enhancement process is modulated by the luma signal since major chroma changes are invariably accompanied by luminance changes. The enhanced signals are then added to a delayed version of the directpath signal to generate the R-Y and R-B output signals.

# **Memory Map**

| Regis          | ter  |                 |                                   |                       | Bits |  |  |  |                 | Default            |

|----------------|------|-----------------|-----------------------------------|-----------------------|------|--|--|--|-----------------|--------------------|

| Addr.          | Name | 7 6 5 4 3 2 1 0 |                                   |                       |      |  |  |  | Value           |                    |

| 0 <sub>H</sub> | ADDR |                 | Device_Address <sub>7-0</sub>     |                       |      |  |  |  |                 |                    |

| 1 <sub>H</sub> | HDR  |                 | Header <sub>7-0</sub>             |                       |      |  |  |  |                 | 00 <sub>H</sub>    |

| 2 <sub>H</sub> | THA  |                 | Threshold_Offset <sub>4-0</sub>   |                       |      |  |  |  | 00 <sub>H</sub> |                    |

| 3 <sub>H</sub> | CG   |                 | Chroma_C                          | Bain <sub>3-0</sub>   |      |  |  |  |                 | 60 <sub>H</sub>    |

| 4 <sub>H</sub> | DPA  |                 | Detail_Enhancement <sub>3-0</sub> |                       |      |  |  |  |                 | $B0_{H}$           |

| 5 <sub>H</sub> | CAT  |                 | Chroma_Av_Thesh <sub>3-0</sub>    |                       |      |  |  |  |                 | CO <sub>H</sub>    |

| 6 <sub>H</sub> | DPT  |                 | Detail_Thresh <sub>5-0</sub>      |                       |      |  |  |  |                 | $X0_{H}^{*}$       |

| 7 <sub>H</sub> | YEG  |                 | Luma_Enl                          | n_Gain <sub>3-0</sub> |      |  |  |  |                 | Y0 <sub>H</sub> ** |

Notes: \* The value X of Detail\_Thresh<sub>5-2</sub> is determined by the setting of the  $\text{THRE}_{3-0}$  pins after reset.

\*\* The value Y of Luma\_Enh\_Gain<sub>3-0</sub> is determined by the setting of the YEGC<sub>3-0</sub> pins after reset. All registers are write only.

# **Register Details**

|                                                                | ADDR. Defa           |                           |                      | a of the day         | ina                  |                           |                           |                           |

|----------------------------------------------------------------|----------------------|---------------------------|----------------------|----------------------|----------------------|---------------------------|---------------------------|---------------------------|

| The eight bits in                                              |                      | U                         |                      | ss of the dev        |                      | _                         |                           |                           |

| Bit                                                            | 7                    | 6                         | 5                    | 4                    | 3                    | 2                         | 1                         | 0                         |

| Mnemonic                                                       | Address <sub>7</sub> | Address <sub>6</sub>      | Address <sub>5</sub> | Address <sub>4</sub> | Address <sub>3</sub> | Address <sub>2</sub>      | Address <sub>1</sub>      | Address <sub>0</sub>      |

| Address value                                                  | 1                    | 0                         | 1                    | 0                    | 1                    | 1                         | 0                         | 1                         |

| Address 01 <sub>H</sub> :                                      | HDR. Defau           | ılt value 00 <sub>H</sub> | [                    |                      |                      |                           |                           |                           |

| The eight bits in                                              |                      | gister set the            | operating m          | ode of the de        |                      |                           |                           |                           |

| The eight bits in                                              |                      |                           |                      | ode of the de        | evice:<br>3          | 2                         | 1                         | 0                         |

| Address 01 <sub>H</sub> : The eight bits in<br>Bit<br>Mnemonic |                      | gister set the<br>6       | operating m<br>5     | 4                    | 3                    | 2<br>Address <sub>2</sub> | 1<br>Address <sub>1</sub> | 0<br>Address <sub>0</sub> |

# **Register Details**

| п                                                                                                                               | THA. Defau                                                                                                                                                                                      | lt value 00 <sub>H</sub>                                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                      |                                                                                                                        |                                                            |                                 |                        |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------|------------------------|--|--|--|--|

| The five most s<br>edge (detail) er                                                                                             | -                                                                                                                                                                                               |                                                                                                                                                                         | -                                                                                                                                                       | the threshold                                                                                                                                                        | offset between                                                                                                         | the vertica                                                | l and horizon                   | ital small             |  |  |  |  |

| Bit                                                                                                                             | 7                                                                                                                                                                                               | 6                                                                                                                                                                       | 5                                                                                                                                                       | 4                                                                                                                                                                    | 3                                                                                                                      | 2                                                          | 1                               | 0                      |  |  |  |  |

| Mnemonic                                                                                                                        | Thr_O'set <sub>4</sub>                                                                                                                                                                          | Thr_O'set <sub>3</sub>                                                                                                                                                  | Thr_O'set <sub>2</sub>                                                                                                                                  | Thr_O'set <sub>1</sub>                                                                                                                                               | Thr_O'set <sub>0</sub>                                                                                                 | 0                                                          | 0                               | 0                      |  |  |  |  |

| Default value                                                                                                                   | 0                                                                                                                                                                                               | 0                                                                                                                                                                       | 0                                                                                                                                                       | 0                                                                                                                                                                    | 0                                                                                                                      | 0                                                          | 0                               | 0                      |  |  |  |  |

| Thr_O'set <sub>4-0</sub> :                                                                                                      | as follows:                                                                                                                                                                                     |                                                                                                                                                                         |                                                                                                                                                         | etween the ver                                                                                                                                                       | rtical and horiz                                                                                                       | zontal detai                                               | l enhancemer                    | nt circuit             |  |  |  |  |

|                                                                                                                                 | 00 <sub>H</sub> * =                                                                                                                                                                             | $00_{\rm H}^{*}$ = Zero threshold offset.                                                                                                                               |                                                                                                                                                         |                                                                                                                                                                      |                                                                                                                        |                                                            |                                 |                        |  |  |  |  |

|                                                                                                                                 | 10 <sub>H</sub> =                                                                                                                                                                               | Maximum I                                                                                                                                                               | negative thre                                                                                                                                           | shold offset.                                                                                                                                                        |                                                                                                                        |                                                            |                                 |                        |  |  |  |  |

|                                                                                                                                 | 0F <sub>H</sub> =                                                                                                                                                                               | = Maximum J                                                                                                                                                             | positive thres                                                                                                                                          | shold offset.                                                                                                                                                        |                                                                                                                        |                                                            |                                 |                        |  |  |  |  |

| Bits 2-0 are not                                                                                                                | horizontal<br>(addresses                                                                                                                                                                        | small edge en<br>6 <sub>H</sub> and 7 <sub>H</sub> ) fo                                                                                                                 | nhancement.<br>or more detai                                                                                                                            | Refer to the ils.                                                                                                                                                    | r smaller (neg<br>description of<br>000.                                                                               |                                                            |                                 |                        |  |  |  |  |

|                                                                                                                                 |                                                                                                                                                                                                 | *                                                                                                                                                                       |                                                                                                                                                         | •                                                                                                                                                                    |                                                                                                                        |                                                            |                                 |                        |  |  |  |  |

| The eight bits i<br>Bit                                                                                                         | n the CG regi<br>7                                                                                                                                                                              | 6                                                                                                                                                                       | 5                                                                                                                                                       | 4                                                                                                                                                                    | ment gain leve<br>3<br>0                                                                                               | 2                                                          | 1                               | 0                      |  |  |  |  |

|                                                                                                                                 | $Chr_Gain_3$                                                                                                                                                                                    | 2                                                                                                                                                                       | 1                                                                                                                                                       | 0                                                                                                                                                                    |                                                                                                                        | 0                                                          | 0                               | 0                      |  |  |  |  |

|                                                                                                                                 | Chr_Gain <sub>3</sub><br>0                                                                                                                                                                      | Chr_Gain <sub>2</sub><br>1                                                                                                                                              | 1                                                                                                                                                       | 0                                                                                                                                                                    | 0                                                                                                                      | 0                                                          | 0                               | 0<br>0                 |  |  |  |  |

| Mnemonic<br>Default value<br>Chr_Gain <sub>3-0</sub> :                                                                          | 0<br>These bits<br>$00_{\rm H} = 60_{\rm H}^* =$                                                                                                                                                | 1<br>set the chron<br>= Zero chrom<br>= Default det                                                                                                                     | 1<br>na large edge<br>na large edge<br>ail chroma la                                                                                                    | 0<br>enhancement<br>enhancement<br>urge edge enha                                                                                                                    | 0<br>t gain level, as<br>gain.<br>ancement gain                                                                        | 0<br>follows:                                              |                                 | _                      |  |  |  |  |

| Default value                                                                                                                   | 0<br>These bits<br>$00_{\rm H} = 60_{\rm H}^* =$                                                                                                                                                | 1<br>set the chron<br>= Zero chrom<br>= Default det                                                                                                                     | 1<br>na large edge<br>na large edge<br>ail chroma la                                                                                                    | 0<br>enhancement<br>enhancement<br>urge edge enha                                                                                                                    | 0<br>gain level, as<br>gain.                                                                                           | 0<br>follows:                                              |                                 | _                      |  |  |  |  |

| Default value<br>Chr_Gain <sub>3-0</sub> :<br>Address 04 <sub>H</sub> :                                                         | 0<br>These bits<br>$00_{\rm H} =$<br>$60_{\rm H}^* =$<br>${\rm FF}_{\rm H} =$<br><b>DPA. Defau</b>                                                                                              | 1<br>set the chron<br>Zero chrom<br>Default det<br>Maximum (<br><b>t value B0<sub>H</sub></b>                                                                           | 1<br>na large edge<br>aa large edge<br>ail chroma la<br>detail chroma                                                                                   | 0<br>enhancement<br>enhancement<br>arge edge enha<br>a large edge e                                                                                                  | 0<br>t gain level, as<br>gain.<br>ancement gain<br>nhancement g                                                        | 0<br>follows:<br>ain.                                      | 0                               | 0                      |  |  |  |  |

| Default value<br>Chr_Gain <sub>3-0</sub> :<br>Address 04 <sub>H</sub> :<br>The eight bits i                                     | 0<br>These bits<br>$00_{\rm H} =$<br>$60_{\rm H}^* =$<br>FF <sub>H</sub> =<br><b>DPA. Defau</b><br>n the DPA reg                                                                                | 1<br>set the chrom<br>Zero chrom<br>Default det<br>Maximum<br>Maximum<br>It value B0 <sub>H</sub><br>gister set the                                                     | 1<br>na large edge<br>ail chroma la<br>detail chroma<br>luma small e                                                                                    | 0<br>enhancement<br>enhancement<br>arge edge enha<br>a large edge e                                                                                                  | 0<br>t gain level, as<br>gain.<br>ancement gain<br>nhancement g                                                        | 0<br>follows:<br>ain.<br>ain level, as                     | 0<br>shown below                | 0<br>w:                |  |  |  |  |

| Default value<br>Chr_Gain <sub>3-0</sub> :<br>Address 04 <sub>H</sub> :<br>The eight bits i<br>Bit                              | 0<br>These bits<br>$00_{\rm H} =$<br>$60_{\rm H}^* =$<br>FF <sub>H</sub> =<br><b>DPA. Defau</b><br>n the DPA reg<br>7                                                                           | 1<br>set the chron<br>= Zero chrom<br>= Default det<br>= Maximum o<br>t <b>t value B0<sub>H</sub></b><br>gister set the<br>6                                            | 1<br>na large edge<br>ail chroma la<br>detail chroma<br>luma small e<br>5                                                                               | 0<br>e enhancement<br>enhancement<br>arge edge enha<br>a large edge e<br>edge (detail) e<br>4                                                                        | 0<br>t gain level, as<br>gain.<br>ancement gain<br>nhancement g<br>nhancement g<br>3                                   | 0<br>follows:<br>ain.<br>ain level, as<br>2                | 0<br>s shown below<br>1         | 0<br>w:<br>0           |  |  |  |  |

| Default value<br>Chr_Gain <sub>3-0</sub> :<br>Address 04 <sub>H</sub> :<br>The eight bits i                                     | 0<br>These bits<br>$00_{\rm H} =$<br>$60_{\rm H}^* =$<br>FF <sub>H</sub> =<br><b>DPA. Defau</b><br>n the DPA reg                                                                                | 1<br>set the chron<br>= Zero chrom<br>= Default det<br>= Maximum o<br>t <b>t value B0<sub>H</sub></b><br>gister set the<br>6                                            | 1<br>na large edge<br>ail chroma la<br>detail chroma<br>luma small e                                                                                    | 0<br>e enhancement<br>enhancement<br>arge edge enha<br>a large edge e<br>edge (detail) e<br>4                                                                        | 0<br>t gain level, as<br>gain.<br>ancement gain<br>nhancement g                                                        | 0<br>follows:<br>ain.<br>ain level, as                     | 0<br>shown below                | 0<br>w:                |  |  |  |  |

| Default value<br>Chr_Gain <sub>3-0</sub> :<br>Address 04 <sub>H</sub> :<br>The eight bits i<br>Bit<br>Mnemonic<br>Default value | 0<br>These bits<br>$00_{\rm H} =$<br>$60_{\rm H}^* =$<br>FF <sub>H</sub> =<br><b>DPA. Defaut</b><br>n the DPA reg<br>7<br>Det_Enh <sub>3</sub><br>1<br>These bits                               | set the chron<br>= Zero chrom<br>= Default det:<br>= Maximum of<br><b>It value B0<sub>H</sub></b><br>gister set the<br>6<br>Det_Enh <sub>2</sub><br>0<br>set the small  | 1<br>na large edge<br>ail chroma la<br>detail chroma<br>luma small e<br>5<br>Det_Enh <sub>1</sub><br>1<br>edge (detail)                                 | 0<br>e enhancement<br>enhancement<br>arge edge enha<br>a large edge e<br>edge (detail) e<br>4<br>Det_Enh <sub>0</sub><br>1<br>) enhancemen                           | 0<br>t gain level, as<br>gain.<br>ancement gain<br>nhancement g<br>nhancement g<br>3<br>0                              | 0<br>follows:<br>ain.<br>ain level, as<br>2<br>0<br>0<br>0 | 0<br>shown below<br>1<br>0<br>0 | w:<br>0<br>0<br>0<br>0 |  |  |  |  |

| Default value<br>Chr_Gain <sub>3-0</sub> :<br>Address 04 <sub>H</sub> :<br>The eight bits i<br>Bit<br>Mnemonic                  | 0<br>These bits<br>$00_{\rm H} =$<br>$60_{\rm H}^* =$<br>$FF_{\rm H} =$<br><b>DPA. Defau</b><br>n the DPA reg<br>7<br>Det_Enh <sub>3</sub><br>1<br>These bits<br>level set by<br>$00_{\rm H} =$ | set the chron<br>= Zero chrom<br>= Default deta<br>= Maximum of<br>t value $B0_H$<br>gister set the<br>6<br>Det_Enh <sub>2</sub><br>0<br>set the small<br>t the YEG reg | 1<br>na large edge<br>ail chroma la<br>detail chroma<br>luma small e<br>5<br>Det_Enh <sub>1</sub><br>1<br>edge (detail)<br>gister (or the<br>enhancemen | 0<br>e enhancement<br>enhancement<br>urge edge enha<br>a large edge e<br>edge (detail) e<br>4<br>Det_Enh <sub>0</sub><br>1<br>) enhancemen<br>YEGC3-0 pin<br>t gain. | 0<br>t gain level, as<br>gain.<br>ancement gain<br>nhancement g<br>nhancement g<br>3<br>0<br>0<br>0<br>t gain level re | 0<br>follows:<br>ain.<br>ain level, as<br>2<br>0<br>0<br>0 | 0<br>shown below<br>1<br>0<br>0 | w:<br>0<br>0<br>0      |  |  |  |  |

| Default value<br>Chr_Gain <sub>3-0</sub> :<br>Address 04 <sub>H</sub> :<br>The eight bits i<br>Bit<br>Mnemonic<br>Default value | 0<br>These bits<br>$00_{\rm H} =$<br>$60_{\rm H}^* =$<br>$FF_{\rm H} =$<br><b>DPA. Defau</b><br>n the DPA reg<br>7<br>Det_Enh <sub>3</sub><br>1<br>These bits<br>level set by<br>$00_{\rm H} =$ | set the chron<br>= Zero chrom<br>= Default det<br>= Maximum of<br>t value $B0_H$<br>gister set the<br>6<br>Det_Enh <sub>2</sub><br>0<br>set the small<br>v the YEG ref. | 1<br>na large edge<br>ail chroma la<br>detail chroma<br>luma small e<br>5<br>Det_Enh <sub>1</sub><br>1<br>edge (detail)<br>gister (or the<br>enhancemen | 0<br>e enhancement<br>enhancement<br>urge edge enha<br>a large edge e<br>edge (detail) e<br>4<br>Det_Enh <sub>0</sub><br>1<br>) enhancemen<br>YEGC3-0 pin<br>t gain. | 0<br>t gain level, as<br>gain.<br>ancement gain<br>nhancement g<br>nhancement g<br>3<br>0<br>0<br>0<br>t gain level re | 0<br>follows:<br>ain.<br>ain level, as<br>2<br>0<br>0<br>0 | 0<br>shown below<br>1<br>0<br>0 | w:<br>0<br>0<br>0      |  |  |  |  |

\* Indicates default value

| Bit                                                                                    | 7                                                                                                                                   | 6                                                                                                                                                                       | 5                                                                                                                                          | 4                                                                                                                                          | ld level, as sh<br>3                                                                     | 2                                                                          | 1                                                    | 0                                         |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------|

| Mnemonic                                                                               | Chr Av.                                                                                                                             |                                                                                                                                                                         | Chr_Av <sub>1</sub>                                                                                                                        |                                                                                                                                            | 0                                                                                        | 0                                                                          | 0                                                    | 0                                         |

| Default value                                                                          | 1                                                                                                                                   | 1                                                                                                                                                                       | 0                                                                                                                                          | 0                                                                                                                                          | 0                                                                                        | 0                                                                          | 0                                                    | 0                                         |

| Chr_Av <sub>3-0</sub> :                                                                | averager is<br>$00_{\rm H} =$<br>$C0_{\rm H}^* =$<br>$FF_{\rm H} =$                                                                 | switched int<br>Zero thresh<br>Default thre<br>Maximum                                                                                                                  | to the signal<br>hold.<br>eshold.<br>threshold.                                                                                            | path, as follo                                                                                                                             | ows:                                                                                     | the edge level<br>rom PAL coded                                            |                                                      | ch the                                    |

| Address 06 <sub>H</sub> :                                                              | DPT. Defaul                                                                                                                         | t value set b                                                                                                                                                           | ov nins THR                                                                                                                                | E                                                                                                                                          |                                                                                          |                                                                            |                                                      |                                           |

| The eight bits i                                                                       |                                                                                                                                     |                                                                                                                                                                         |                                                                                                                                            |                                                                                                                                            | hold level, as                                                                           | s shown below:                                                             |                                                      |                                           |

| Bit                                                                                    | 7                                                                                                                                   | 6                                                                                                                                                                       | 5                                                                                                                                          | 4                                                                                                                                          | 3                                                                                        | 2                                                                          | 1                                                    | 0                                         |

| Mnemonic                                                                               | Det_Thr <sub>5</sub>                                                                                                                | $Det_Thr_4$                                                                                                                                                             | Det_Thr <sub>3</sub>                                                                                                                       | Det_Thr <sub>2</sub>                                                                                                                       | Det_Thr <sub>1</sub>                                                                     | Det_Thr <sub>0</sub>                                                       | 0                                                    | 0                                         |

| Default value                                                                          | THRE <sub>3</sub>                                                                                                                   | THRE <sub>2</sub>                                                                                                                                                       | 5                                                                                                                                          | -                                                                                                                                          | 0                                                                                        | 0                                                                          | 0                                                    | 0                                         |

|                                                                                        |                                                                                                                                     |                                                                                                                                                                         | enhancemen                                                                                                                                 |                                                                                                                                            |                                                                                          |                                                                            |                                                      |                                           |

|                                                                                        | FF <sub>H</sub> =<br>The default<br>pins. In the<br>programmi<br>recommend                                                          | - Maximum<br>t value of the<br>is way it is p<br>ng, and still<br>ded. A rising                                                                                         | detail enhand<br>e detail enhar<br>ossible to use<br>have control                                                                          | cement thresh<br>accement thresh<br>the device is<br>over the det<br>sTRB input                                                            | shold is deter<br>in its default :<br>ail enhancem                                       | mined by the se<br>mode, without t<br>ent threshold.<br>ntrol to the serie | he need for<br>A value of                            | r any<br>60 <sub>H</sub> is               |

| Address 07 <sub>H</sub> :                                                              | FF <sub>H</sub> =<br>The default<br>pins. In the<br>programmi<br>recommend<br>must be res                                           | Maximum<br>t value of the<br>is way it is p<br>ng, and still<br>ded. A rising<br>set to re-activ                                                                        | detail enhand<br>e detail enhar<br>ossible to use<br>have control<br>g edge on the<br>vate the THR                                         | cement thresh<br>accement thresh<br>the device is<br>over the det<br>e STRB input<br>$E_{3-0}$ inputs.                                     | shold is deter<br>in its default :<br>ail enhancem                                       | mode, without t<br>ent threshold.                                          | he need for<br>A value of                            | r any<br>60 <sub>H</sub> is               |

|                                                                                        | FF <sub>H</sub> =<br>The default<br>pins. In the<br>programmi<br>recommend<br>must be res<br><b>YEG. Defau</b>                      | Maximum<br>t value of the<br>is way it is p<br>ng, and still<br>ded. A rising<br>set to re-active<br>lt value set                                                       | detail enhand<br>e detail enhar<br>ossible to use<br>have control<br>g edge on the<br>/ate the THR<br>by pins YEC                          | cement thresh<br>accement thresh<br>the device is<br>over the det<br>c STRB input<br>$E_{3.0}$ inputs.                                     | shold is deter<br>in its default<br>ail enhancem<br>t transfers con                      | mode, without t<br>ent threshold.<br>ntrol to the serie                    | he need for<br>A value of<br>al bus and t            | r any<br>60 <sub>H</sub> is               |

| The eight bits i                                                                       | FF <sub>H</sub> =<br>The default<br>pins. In the<br>programmi<br>recommend<br>must be res<br><b>YEG. Defau</b>                      | - Maximum<br>t value of the<br>is way it is p<br>ng, and still<br>ded. A rising<br>set to re-active<br>lt value set<br>gister set the                                   | detail enhand<br>e detail enhan<br>ossible to use<br>have control<br>g edge on the<br>vate the THR<br><b>by pins YEC</b><br>e overall lumi | cement thresh<br>accement thresh<br>e the device is<br>over the det<br>e STRB input<br>$E_{3.0}$ inputs.<br>$GC_{3.0}$<br>nance enhan      | shold is deter<br>in its default<br>ail enhancem<br>t transfers con<br>cement gain,      | mode, without the series of the series as shown below                      | he need for<br>A value of<br>al bus and t            | r any<br>60 <sub>H</sub> is               |

| The eight bits i<br>Bit                                                                | FF <sub>H</sub> =<br>The default<br>pins. In the<br>programmi<br>recommend<br>must be res<br><b>YEG. Defau</b><br>n the YEG re      | Maximum<br>t value of the<br>is way it is p<br>ng, and still<br>ded. A rising<br>set to re-active<br>lt value set<br>gister set the<br>6                                | detail enhand<br>e detail enhan<br>ossible to use<br>have control<br>g edge on the<br>vate the THR<br>by pins YEC<br>overall lumi<br>5     | cement thresh<br>accement thresh<br>the device is<br>over the det<br>s STRB input<br>$E_{3.0}$ inputs.<br>$BC_{3.0}$<br>anance enhant<br>4 | shold is deter<br>in its default<br>ail enhancem<br>t transfers con<br>cement gain,<br>3 | mode, without the series of the series as shown below                      | he need for<br>A value of<br>al bus and t            | r any<br>60 <sub>H</sub> is<br>the device |

| <b>Address 07<sub>H</sub>:</b><br>The eight bits i<br>Bit<br>Mnemonic<br>Default value | FF <sub>H</sub> =<br>The default<br>pins. In the<br>programmi<br>recommend<br>must be res<br><b>YEG. Defau</b><br>n the YEG re<br>7 | Maximum<br>t value of the<br>is way it is p<br>ng, and still<br>ded. A rising<br>set to re-activ<br><b>lt value set</b><br>gister set the<br>6<br>Luma_Enh <sub>2</sub> | detail enhand<br>e detail enhan<br>ossible to use<br>have control<br>g edge on the<br>vate the THR<br>by pins YEC<br>overall lumi<br>5     | cement thresh<br>accement thresh<br>the device is<br>over the det<br>s STRB input<br>$E_{3.0}$ inputs.<br>$BC_{3.0}$<br>anance enhant<br>4 | shold is deter<br>in its default<br>ail enhancem<br>t transfers con<br>cement gain,<br>3 | mode, without the threshold. Introl to the series as shown below 2         | he need for<br>A value of<br>al bus and t<br>w:<br>1 | r any<br>60 <sub>H</sub> is<br>the device |

\* Indicates default value

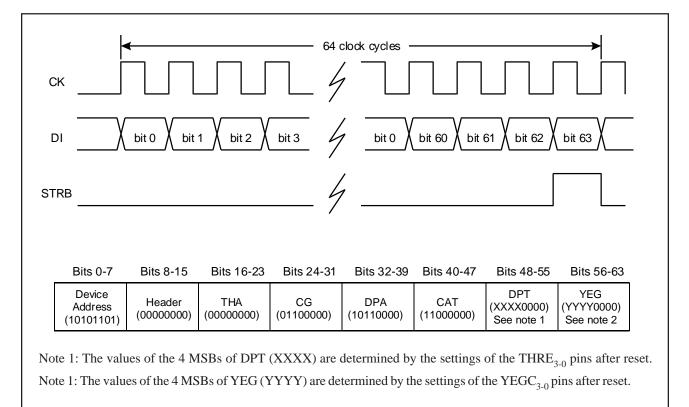

# **Serial Control Bus Operation and Protocol**

The YCP101 is programmed by means of a 3-wire serial bus. If the device is not programmed after a reset it will operate with the default parameter values shown in the register descriptions. The programming protocol requires 8 bytes of data to be written into the device via the DI pin, as shown in the timing diagram below. The bit sequence of each byte is LSB first, MSB last. During the final cycle of the 64 clock cycles the STRB line is pulsed

high to latch the 8 bytes of data into the registers. The first byte is the device address,  $AD_{H}$ , and this is followed by the header byte,  $00_{H}$ , and then the six data bytes, as shown in the diagram below. The data values shown are the default values automatically set up after the device is reset. After the sequence is complete the clock may be stopped or the sequence may be repeated continuously. The maximum clock speed is 14.4 kHz.

# Input and Output Signal Timing

# Input and Output Signal Timing

| Symbol              | Description                                        | Min. | Nom. | Max. | Units | Conditions |  |  |  |

|---------------------|----------------------------------------------------|------|------|------|-------|------------|--|--|--|

| Input S             | Input Signal Timing                                |      |      |      |       |            |  |  |  |

| f <sub>CLK4IN</sub> | Input clock frequency                              |      |      | 30   | MHz   |            |  |  |  |

| f <sub>CLK8IN</sub> | Output clock frequency                             |      |      | 60   | MHz   |            |  |  |  |

| t <sub>SU</sub>     | Input to clock setup                               | TBD  |      |      | nsec. |            |  |  |  |

| t <sub>HD</sub>     | Input to clock hold                                | TBD  |      |      | nsec. |            |  |  |  |

| Output              | Signal Timing                                      |      |      |      |       |            |  |  |  |

| t <sub>PDD</sub>    | CLK8IN to YOUT <sub>9-0</sub> propagation delay    |      |      | TBD  | nsec. |            |  |  |  |

| t <sub>PDA</sub>    | Clock to RY/BYOUT <sub>9-0</sub> propagation delay |      |      | TBD  | nsec. |            |  |  |  |

### **Package Dimensions**

|                | -     | Millimeters |       | Inches |        |       |  |

|----------------|-------|-------------|-------|--------|--------|-------|--|

| Ref.           | Min.  | Тур.        | Max.  | Min.   | Тур.   | Max.  |  |

| A              |       |             | 3.40  |        |        | 0.134 |  |

| A1             | 0.25  |             |       | 0.010  |        |       |  |

| A2             | 2.55  |             | 3.05  | 0.100  |        | 0.120 |  |

| b              | 0.23  |             | 0.38  | 0.009  |        | 0.015 |  |

| C              | 0.13  |             | 0.23  | 0.005  |        | 0.009 |  |

| D              | 13.90 |             | 14.10 | 0.547  |        | 0.555 |  |

| Е              | 19.90 |             | 20.10 | 0.783  |        | 0.791 |  |

| e              |       | 0.65        |       |        | 0.0256 |       |  |

| H <sub>D</sub> | 16.95 |             | 17.45 | 0.667  |        | 0.687 |  |

| H <sub>E</sub> | 22.95 |             | 23.45 | 0.904  |        | 0.923 |  |

| L              | 0.65  |             | 0.95  | 0.025  |        | 0.037 |  |

| L1             |       | 1.60        |       |        | 0.063  |       |  |

| Z <sub>D</sub> |       | 0.5         |       |        | 0.02   |       |  |

| Z <sub>E</sub> |       | 0.5         |       |        | 0.02   |       |  |

| θ              | 0°    |             | 7°    | 0°     |        | 7°    |  |

**FAROUDJA**Laboratories is a registered trademark of Faroudja Laboratories, Inc. (FLI). FLI does not convey any license under its patents for the use of this product, which is covered by the following US patents: 4,030,121, 4,262,304, 4,847,681