### **Key Features**

- Resolutions Up To UXGA 75Hz

- 250ps Long Term Jitter

- 64 Phase Choices

- Zero Offset Error/Offset Drift

# X98021

# 210MHz Triple Video Digitizer with Digital PLL

# PRELIMINARY INFORMATION

#### **FEATURES**

- 210MSPS maximum conversion rate

- · 64 interpixel sampling positions

- Low long-term PLL clock jitter (250ps p-p @ 210MSPS)

- Programmable input bandwidth (100MHz to 780MHz)

- 2 channel input multiplexer

- · RGB and YUV 4:2:2 output formats

- 4 embedded voltage regulators allow operation from single 3.3V supply and enhance performance, isolation

- Completely independent 8 bit gain/10 bit offset control

- CSYNC and SOG support

- · Trilevel Sync detection

- 1090mW typical PD @ 210MSPS

### **APPLICATIONS**

- LCD Monitors and Projectors

- Digital TVs

- Plasma Display Panels

- · RGB Graphics Processing

- Scan Converters

#### **DESCRIPTION**

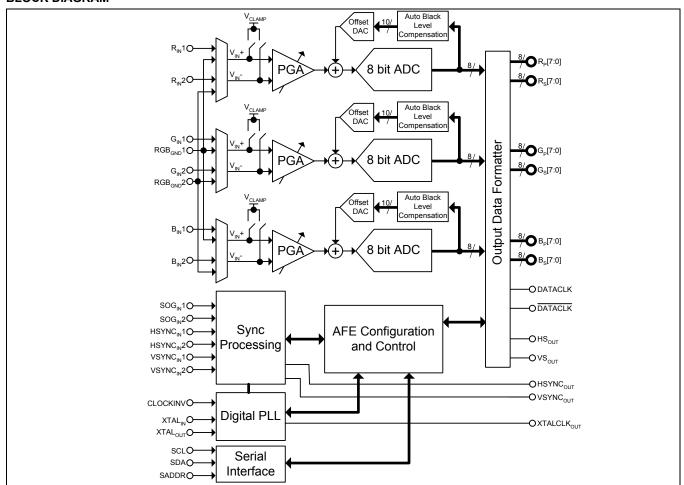

The X98021 3-channel, 8-bit Analog Front End (AFE) contains all the components necessary to digitize analog RGB or YUV graphics signals from personal computers, workstations and video set-top boxes. The fully differential analog design provides high PSRR and dynamic performance to meet the strigent requirements of the graphics display industry. The 210MSPS conversion rate supports resolutions up to UXGA at 75Hz refresh rate, while the front end's high input bandwidth ensures sharp images at the highest resolution.

To minimize noise, the X98021's analog section features 2 sets of pseudo-differential RGB inputs with programmable input bandwidth, as well as internal DC restore clamping (including mid-scale clamping for YUV signals). This is followed by the programmable gain/offset stage and the three 210MSPS Analog-to-Digital Converters (ADCs). All necessary reference voltages are internally generated.

The X98021's digital PLL generates a pixel clock from the analog source's HSYNC or SOG (Sync-On-Green) signals. Pixel clock output frequencies range from 10MHz to 210MHz with long-term clock jitter less than 250ps peak to peak.

### **BLOCK DIAGRAM**