# 8051 Microcontroller Family Compatible

64K X88C64 8192 x 8 Bit

# E<sup>2</sup> Micro-Peripheral

#### **FEATURES**

- CONCURRENT READ WRITE™

- —Dual Plane Architecture

- —Isolates Read/Write Functions Between Planes

- Allows Continuous Execution of Code From One Plane While Writing in the Other Plane

- Multiplexed Address/Data Bus

- —Direct Interface to Popular 8051 Family

- High Performance CMOS

- -Fast Access Time, 120ns

- —Low Power

- -60mA Active Maximum

- —500μA Standby Maximum

- Software Data Protection

- Block Protect Register

- -Individually Set Write Lock Out in 1K Blocks

- Toggle Bit Polling

- -Early End of Write Detection

- Page Mode Write

- Allows up to 32 Bytes to be Written in One Write Cycle

- High Reliability

- -Endurance: 100,000 Write Cycle

- -Data Retention: 100 Years

### **DESCRIPTION**

The X88C64 is an 8K x 8 E<sup>2</sup>PROM fabricated with advanced CMOS Textured Poly Floating Gate Technology. The X88C64 features a Multiplexed Address and Data bus allowing a direct interface to a variety of popular single-chip microcontrollers operating in expanded multiplexed mode without the need for additional interface circuitry.

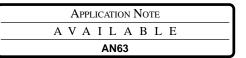

The X88C64 is internally configured as two independent 4K x 8 memory arrays. This feature provides the ability to perform nonvolatile memory updates in one array and continue operation out of code stored in the other array; effectively eliminating the need for an auxiliary memory device for code storage.

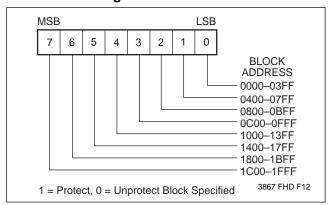

To write to the X88C64, a three-byte command sequence must precede the byte(s) being written. The X88C64 also provides a second generation software data protection scheme called Block Protect. Block Protect can provide write lockout of the entire device or selected 1K blocks. There are eight 1K x 8 blocks that can be write protected individually in any combination required by the user. Block Protect, in addition to Write Control input, allows the different segments of the memory to have varying degrees of alterability in normal system operation.

#### **FUNCTIONAL DIAGRAM**

1

3867 FHD F02

CONCURRENT READ WRITE™ is a trademark of Xicor, Inc.

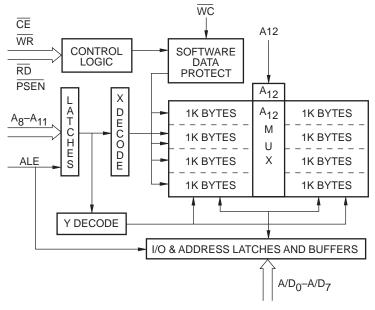

#### PIN DESCRIPTIONS

# Address/Data (A/D<sub>0</sub>-A/D<sub>7</sub>)

Multiplexed low-order addresses and data. The Addresses flow into the device while ALE is HIGH. After ALE transitions from a HIGH to LOW the addresses are latched. Once the addresses are latched these pins input data or output data depending on  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $\overline{\text{PSEN}}$ , and  $\overline{\text{CE}}$ .

## Addresses (A<sub>8</sub>-A<sub>12</sub>)

High order addresses flow into the device when ALE is HIGH and are latched when ALE goes LOW.

## Chip Enable (CE)

The Chip Enable input must be LOW to enable all read/write operations. When  $\overline{CE}$  is HIGH and ALE is LOW, the X88C64 is placed in the low power standby mode.

## **Program Store Enable (PSEN)**

When the X88C64 is to be used in a 8051 based system,  $\overline{\text{PSEN}}$  is tied directly to the microcontroller's  $\overline{\text{PSEN}}$  output.

## Read (RD)

When the X88C64 is to be used in a 8051 based system,  $\overline{RD}$  is tied directly to the microcontroller's  $\overline{RD}$  output.

#### Write (WR)

When the X88C64 is to be used in a 8051 based system,  $\overline{WR}$  is tied directly to the microcontroller's  $\overline{WR}$  output.

# Address Latch Enable (ALE)

Addresses flow through the latches to address decoders when ALE is HIGH and are latched when ALE transitions from a HIGH to LOW.

## Write Control (WC)

The Write Control allows external circuitry to abort a page load cycle once it has been initiated. This input is useful in applications in which a power failure or processor RESET could interrupt a page load cycle. In this case, the microcontroller might drive all signals HIGH, causing bad data to be latched into the E²PROM. If the Write Control input is driven HIGH (before  $t_{BLC}$  Max) after Write ( $\overline{WR}$ ) goes HIGH, the write cycle will be aborted.

When  $\overline{WC}$  is LOW (tied to V<sub>SS</sub>) the X88C64 will be enabled to perform write operations. When  $\overline{WC}$  is HIGH normal read operations may be performed, but all attempts to write to the device will be disabled.

#### **PIN CONFIGURATION**

#### **PIN NAMES**

| Symbol                             | Description                |

|------------------------------------|----------------------------|

| ALE                                | Address Latch Enable       |

| A/D <sub>0</sub> -A/D <sub>7</sub> | Address Inputs/Data I/O    |

| A <sub>8</sub> -A <sub>12</sub>    | Address Inputs             |

| RD                                 | Read Input                 |

| WR                                 | Write Input                |

| PSEN                               | Program Store Enable Input |

| CE                                 | Chip Enable                |

| WC                                 | Write Control              |

| V <sub>SS</sub>                    | Ground                     |

| Vcc                                | Supply Voltage             |

| NC                                 | No Connect                 |

3867 PGM T01.1

#### PRINCIPLES OF OPERATION

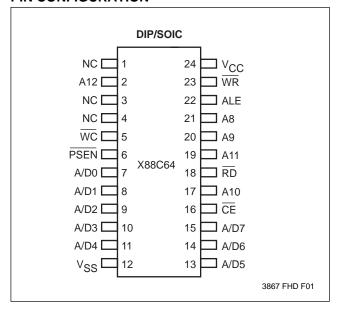

The X88C64 is a highly integrated peripheral device for a wide variety of single-chip microcontrollers. The X88C64 provides 8K bytes of E<sup>2</sup>PROM which can be used either for Program Storage, Data Storage, or a combination of both in systems based upon Harvard (80XX) architectures. The X88C64 incorporates the interface circuitry normally needed to decode the control signals and demultiplex the Address/Data bus to provide a "Seamless" interface.

The interface inputs on the X88C64 are configured such that it is possible to directly connect them to the proper interface signals of the appropriate single-chip microcontroller. In the Harvard type system, the reading of data from the chip is controlled either by the  $\overline{\text{PSEN}}$  or the  $\overline{\text{RD}}$  signal, which essentially maps the X88C64 into both the Program and the Data Memory address map.

The X88C64 is internally organized as two independent planes of 4K bytes of memory with the  $A_{12}$  input selecting which of the two planes of memory are to be accessed. While the processor is executing code out of one plane, write operations can take place in the other plane, allowing the processor to continue execution of code out of the X88C64 during a byte or page write to the device.

The X88C64 also features an advanced implementation of the Software Data Protection scheme, called Block Protect, which allows the device to be broken into 8 independent sections of 1K bytes. Each of these sections can be independently enabled for write operations; thereby allowing certain sections of the device to be secured so that updates can only occur in a controlled environment (e.g. in an automotive application, only at an authorized service center). The desired set-up configuration is stored in a nonvolatile register, ensuring the configuration data will be maintained after the device is powered down.

The X88C64 also features a Write Control input ( $\overline{WC}$ ), which serves as an external control over the completion of a previously initiated page load cycle.

The X88C64 also features the industry standard E<sup>2</sup>PROM characteristics such as byte or page mode write and Toggle Bit Polling.

#### **DEVICE OPERATION**

#### **MODES**

## **Mixed Program/Data Memory**

By properly assigning the address spaces, a single X88C64 can be used as both the Program and Data Memory. This would be accomplished by connecting all of the 8051 control outputs to the corresponding inputs of the X88C64.

In this configuration, one plane of memory could be dedicated to Program Storage and the other plane dedicated to Data Storage. The Data Storage can be fully protected by enabling block protect write lockout.

### TYPICAL APPLICATION

#### **Program Memory Mode**

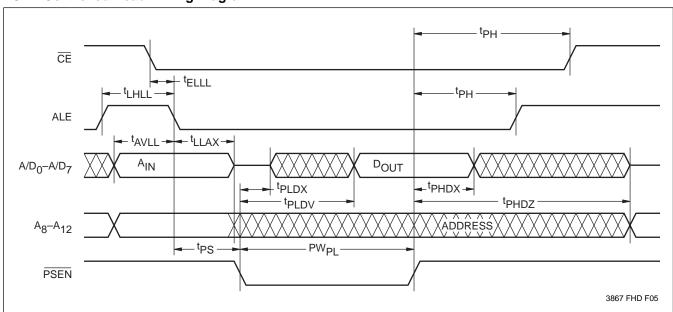

This mode of operation is read-only. The PSEN and ALE inputs of the X88C64 are tied directly to the PSEN and ALE outputs of the microcontroller. The RD and WR inputs are tied HIGH.

When ALE is HIGH, the A/D $_0$ –A/D $_7$  and A $_8$ –A $_{12}$  addresses flow into the device. The addresses, both low and high order, are latched when ALE transitions LOW (V $_{IL}$ ).  $\overline{PSEN}$  will then go LOW and after t $_{PLDV}$ , valid data is presented on the A/D $_0$ –A/D $_7$  pins.  $\overline{CE}$  must be LOW during the entire operation.

# X88C64

## **Data Memory Mode**

This mode of operation allows both read and write functions. The  $\overline{PSEN}$  input is tied to  $V_{IH}$  or to  $V_{CC}$  through a pull-up resistor. The ALE,  $\overline{RD}$ , and  $\overline{WR}$  inputs are tied directly to the microcontroller's ALE,  $\overline{RD}$ , and  $\overline{WR}$  outputs.

## Read

This operation is quite similar to the Program Memory read. A HIGH to LOW transition on ALE latches the

addresses and the data will be output on the AD pins after  $\overline{RD}$  goes LOW ( $t_{RLDV}$ ).

#### Write

A write is performed by latching the addresses on the falling edge of ALE. Then  $\overline{WR}$  is strobed LOW followed by valid data being presented at the A/D<sub>0</sub>–A/D<sub>7</sub> pins. The data will be latched into the X88C64 on the rising edge of  $\overline{WR}$ . To write to the X88C64, a three-byte command sequence must precede the byte(s) being written. (See Software Data Protection.)

#### MODE SELECTION

| CE   | PSEN | RD   | WR   | Mode          | I/O              | Power          |

|------|------|------|------|---------------|------------------|----------------|

| Vcc  | X    | X    | Х    | Standby       | High Z           | Standby (CMOS) |

| HIGH | Х    | Х    | Х    | Standby       | High Z           | Standby (TTL)  |

| LOW  | LOW  | HIGH | HIGH | Program Fetch | D <sub>OUT</sub> | Active         |

| LOW  | HIGH | LOW  | HIGH | Data Read     | D <sub>OUT</sub> | Active         |

| LOW  | HIGH | HIGH |      | Write         | DIN              | Active         |

3867 PGM T02.2

#### PAGE WRITE OPERATION

Regardless of the microcontroller employed, the X88C64 supports page mode write operations. This allows the microcontroller to write from one to thirty-two bytes of data to the X88C64. Each individual write within a page

write operation must conform to the byte write timing requirements. The falling edge of  $\overline{WR}$  starts a timer delaying the internal programming cycle 100 $\mu$ s. Therefore, each successive write operation must begin within 100 $\mu$ s of the last byte written. The following waveforms illustrate the sequence and timing requirements.

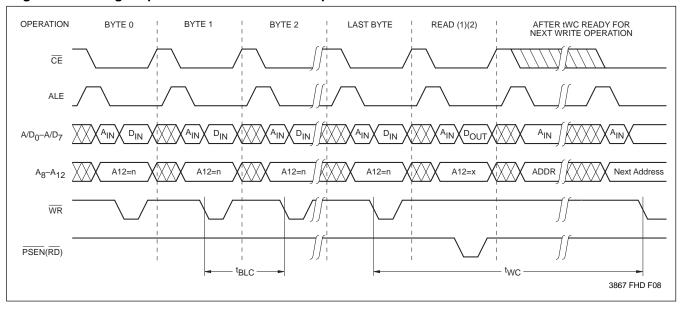

# Page Write Timing Sequence for WR Controlled Operation

**Notes:** (1) For each successive write within a page write cycle A<sub>5</sub>–A<sub>12</sub> must be the same.

- (2) Although it is not illustrated, the microcontroller may interleave read operations between the individual byte writes within the page write operation. Two responses are possible:

- a. Reading from the same plane being written ( $A_{12}$  of Read =  $A_{12}$  of Write) is effectively a Toggle Bit Polling operation.

- b. Reading from the opposite plane being written (A<sub>12</sub> of Read ≠ A<sub>12</sub> of Write) true data will be returned, facilitating the use of a single memory component as both program and data storage.

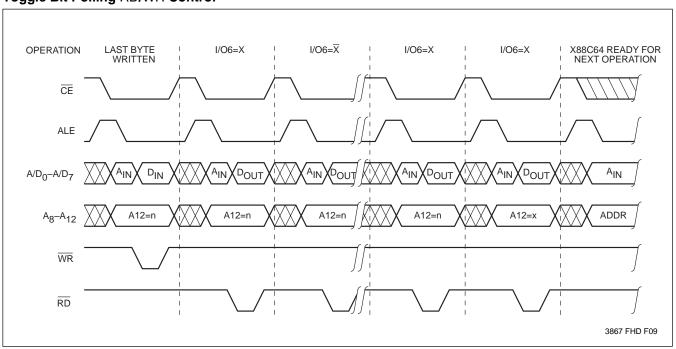

#### **TOGGLE BIT POLLING**

Because the X88C64 typical nonvolatile write cycle time is less than the specified 5ms, Toggle Bit Polling has been provided to determine the early completion of write. During the internal programming cycle I/O $_6$  will toggle from HIGH to LOW and LOW to HIGH on subse-

quent attempts to read the device. When the internal cycle is complete, the toggling will cease and the device will be accessible for additional read or write operations. Due to the dual plane architecture, reads for polling must occur in the plane that was written; that is, the state of  $A_{12}$  during a write must match the state of  $A_{12}$  during Toggle Bit Polling.

# Toggle Bit Polling RD/WR Control

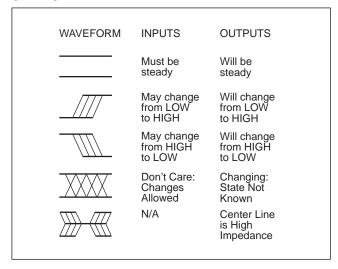

#### **SYMBOL TABLE**

#### DATA PROTECTION

The X88C64 provides two levels of data protection through software control. There is a global software data protection feature similar to the industry standard for E<sup>2</sup>PROMs and a new Block Protect write lockout protection providing a secondary level of data security.

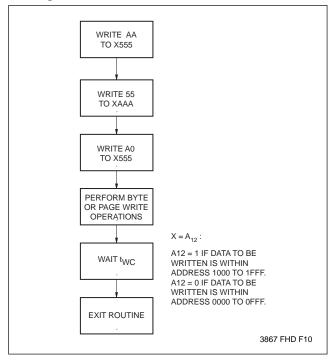

### SOFTWARE DATA PROTECTION

Software Data Protection (SDP) is employed to protect the entire array against inadvertent writes. To write to the X88C64, a three-byte command sequence must precede the byte(s) being written. All write operations, both the command sequence and any data write operations, must conform to the page write timing requirements.

### Writing with SDP

#### **Block Protect Write Lockout**

The X88C64 provides a secondary level of data security referred to as Block Protect write lockout. This is accessed through an extension of the SDP command sequence. Block Protect allows the user to lockout writes to any 1K x 8 blocks of memory. Unlike SDP which prevents inadvertent writes, but still allows easy system access to writing the memory, Block Protect will lockout all attempts unless it is specifically disabled by the host. This could be used to set a higher level of protection in a system where a portion of the memory is used for Program Storage and another portion is used as Data Storage.

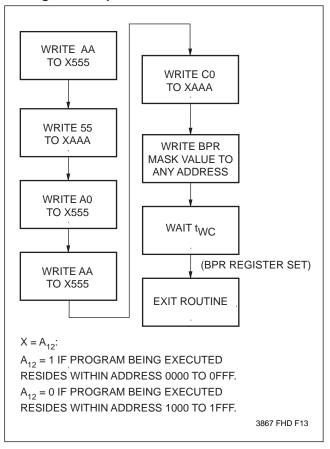

Setting write lockout is accomplished by writing a fivebyte command sequence, opening access to the Block Protect Register (BPR). After the fifth byte is written, the user writes to the BPR, selecting which blocks to protect or unprotect. All write operations, both the command sequence and writing the data to the BPR, must conform to the page write timing requirements.

### **Block Protect Register Format**

## **Setting BPR Sequence**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature under Bias65°C to +135°C  |

|---------------------------------------|

| Storage Temperature65°C to +150°C     |

| Voltage on any Pin with               |

| Respect to V <sub>SS</sub> –1V to +7V |

| D.C. Output Current5 mA               |

| Lead Temperature                      |

| (Soldering, 10 seconds) 300°C         |

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

| Temperature | Min.  | Max.         |

|-------------|-------|--------------|

| Commercial  | 0°C   | +70°C        |

| Industrial  | –40°C | +85°C        |

| Military    | –55°C | +125°C       |

|             |       | 0007 DOM T00 |

3867 PGM T03.1

| Supply Voltage | Limits  |

|----------------|---------|

| X88C64         | 5V ±10% |

3867 PGM T04.1

# D.C. OPERATING CHARACTERISTICS (Over recommended operating conditions unless otherwise specified.)

|                       |                                   | Limits |                       |       |                                                                                                                                |

|-----------------------|-----------------------------------|--------|-----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------|

| Symbol                | Parameter                         | Min.   | Max.                  | Units | Test Conditions                                                                                                                |

| Icc                   | V <sub>CC</sub> Current (Active)  |        | 60                    | mA    | $\overline{CE} = \overline{RD} = V_{IL}$ , All I/O's = Open,Other Inputs = $V_{CC}$                                            |

| ISB1(CMOS)            | V <sub>CC</sub> Current (Standby) |        | 500                   | μΑ    | $\overline{\text{CE}}$ = V <sub>CC</sub> - 0.3V, All I/O's = Open,Other Inputs = V <sub>CC</sub> - 0.3V, ALE = V <sub>IL</sub> |

| I <sub>SB2(TTL)</sub> | V <sub>CC</sub> Current (Standby) |        | 6                     | mA    | CE = V <sub>IH</sub> , All I/O's = Open, Other<br>Inputs = V <sub>IH</sub> , ALE = V <sub>IL</sub>                             |

| ILI                   | Input Leakage Current             |        | 10                    | μΑ    | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                  |

| ILO                   | Output Leakage Current            |        | 10                    | μΑ    | $V_{OUT} = V_{SS}$ to $V_{CC}$ ,<br>$\overline{RD} = V_{IH} = \overline{PSEN}$                                                 |

| V <sub>IL</sub> (3)   | Input LOW Voltage                 | -1     | 0.8                   | V     |                                                                                                                                |

| V <sub>IH</sub> (3)   | Input HIGH Voltage                | 2      | V <sub>CC</sub> + 0.5 | V     |                                                                                                                                |

| VoL                   | Output LOW Voltage                |        | 0.4                   | V     | I <sub>OL</sub> = 2.1 mA                                                                                                       |

| VoH                   | Output HIGH Voltage               | 2.4    |                       | V     | I <sub>OH</sub> = -400 μA                                                                                                      |

3867 PGM T05.2

# **CAPACITANCE** $T_A = +25^{\circ}C$ , f = 1MHz, $V_{CC} = 5V$

| Symbol               | Test                     | Max. | Units | Conditions            |

|----------------------|--------------------------|------|-------|-----------------------|

| C <sub>I/O</sub> (4) | Input/Output Capacitance | 10   | pF    | V <sub>I/O</sub> = 0V |

| C <sub>IN</sub> (4)  | Input Capacitance        | 6    | pF    | V <sub>IN</sub> = 0V  |

3867 PGM T06

## **POWER-UP TIMING**

| Symbol               | Parameter         | Max. | Units |

|----------------------|-------------------|------|-------|

| t <sub>PUR</sub> (4) | Power-Up to Read  | 1    | ms    |

| t <sub>PUW</sub> (4) | Power-Up to Write | 5    | ms    |

3867 PGM T07

Notes: (3)  $V_{IL}$  min. and  $V_{IH}$  max. are for reference only and are not tested.

(4) This parameter is periodically sampled and not 100% tested.

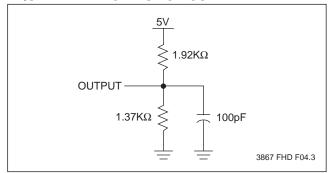

#### A.C. CONDITIONS OF TEST

| Input Pulse Levels | 0V to 3V |

|--------------------|----------|

| Input Rise and     |          |

| Fall Times         | 10ns     |

| Input and Output   |          |

| Timing Levels      | 1.5V     |

3867 PGM T08.1

# **EQUIVALENT A.C. TEST CIRCUIT**

# A.C. CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified.)

# **PSEN Controlled Read Cycle**

| Symbol                | Parameter                        | Min. | Max. | Units |

|-----------------------|----------------------------------|------|------|-------|

| tLHLL                 | ALE Pulse Width                  | 80   |      | ns    |

| tavll                 | Address Setup Time               | 20   |      | ns    |

| t <sub>LLAX</sub>     | Address Hold Time                | 30   |      | ns    |

| tPLDV                 | PSEN Read Access Time            |      | 120  | ns    |

| tphdx                 | Data Hold Time                   | 0    |      | ns    |

| tELLL                 | Chip Enable Setup Time           | 7    |      | ns    |

| PW <sub>PL</sub>      | PSEN Pulse Width                 | 150  |      | ns    |

| tps                   | PSEN Setup Time                  | 30   |      | ns    |

| tpH                   | PSEN Hold Time                   | 20   |      | ns    |

| tPHDZ (5)             | PSEN Disable to Output in High Z |      | 50   | ns    |

| t <sub>PLDX</sub> (5) | PSEN to Output in Low Z          | 10   |      | ns    |

3867 PGM T09

# **PSEN Controlled Read Timing Diagram**

Note: (5) This parameter is periodically sampled and not 100% tested.

# X88C64

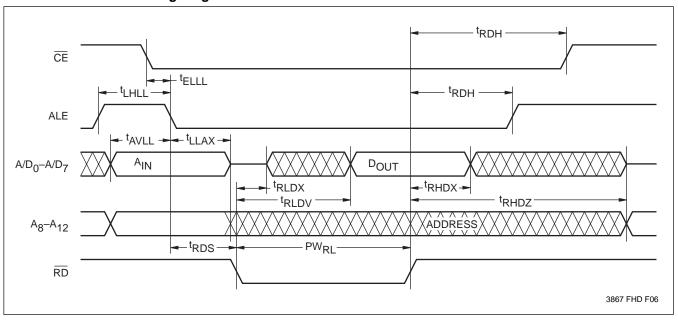

# $\overline{\mathsf{RD}}$ Controlled Read Cycle

| Symbol                | Parameter                      | Min. | Max. | Units   |

|-----------------------|--------------------------------|------|------|---------|

| tLHLL                 | ALE Pulse Width                | 80   |      | ns      |

| tavll                 | Address Setup Time             | 20   |      | ns      |

| t <sub>LLAX</sub>     | Address Hold Time              | 30   |      | ns      |

| t <sub>RLDV</sub>     | RD Read Access Time            |      | 120  | ns      |

| trhdx                 | Data Hold Time                 | 0    |      | ns      |

| telll                 | Chip Enable Setup Time         | 7    |      | ns      |

| PW <sub>RL</sub>      | RD Pulse Width                 | 150  |      | ns      |

| trds                  | RD Setup Time                  | 30   |      | ns      |

| t <sub>RDH</sub>      | RD Hold Time                   | 20   |      | ns      |

| t <sub>RHDZ</sub> (6) | RD Disable to Output in High Z |      | 50   | ns      |

| t <sub>RLDX</sub> (6) | RD to Output in Low Z          | 0    |      | ns      |

| '                     |                                | •    | •    | 3867 PG |

# $\overline{\text{RD}}$ Controlled Read Timing Diagram

Note: (6) This parameter is periodically sampled and not 100% tested.

# X88C64

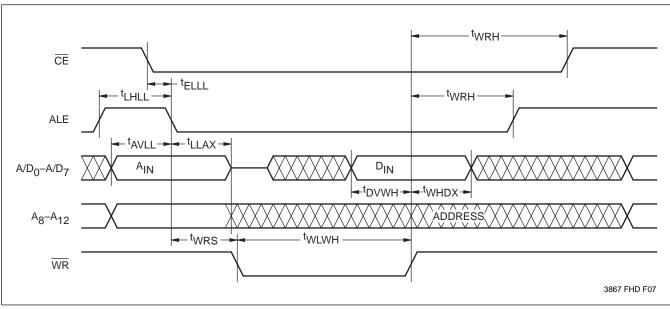

# WR Controlled Write Cycle

| Symbol            | Parameter                   | Min. | Max. | Units |

|-------------------|-----------------------------|------|------|-------|

| tLHLL             | ALE Pulse Width             | 80   |      | ns    |

| tavll             | Address Setup Time          | 20   |      | ns    |

| t <sub>LLAX</sub> | Address Hold Time           | 30   |      | ns    |

| to∨wн             | Data Setup Time             | 50   |      | ns    |

| twhdx             | Data Hold Time              | 30   |      | ns    |

| tELLL             | Chip Enable Setup Time      | 7    |      | ns    |

| twlwh             | WR Pulse Width              | 120  |      | ns    |

| twrs              | WR Setup Time               | 30   |      | ns    |

| twrh              | WR Hold Time                | 20   |      | ns    |

| tBLC              | Byte Load Time (Page Write) | 0.5  | 100  | μs    |

| twc (7)           | Write Cycle Time            |      | 5    | ms    |

#### 3867 PGM T11

# WR Controlled Write Timing Diagram

**Note:** (7) two is the minimum cycle time to be allowed from the system perspective unless polling techniques are used. It is the maximum time the device requires to automatically complete the internal write operation.

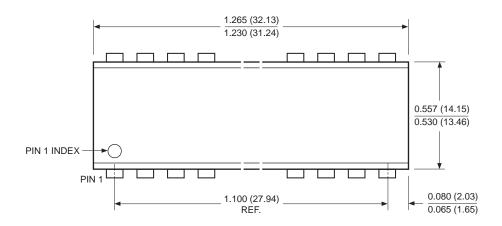

## **PACKAGING INFORMATION**

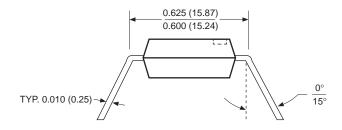

# 24-LEAD PLASTIC DUAL IN-LINE PACKAGE TYPE P

#### NOTE:

- 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

- 2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH

3926 FHD F03

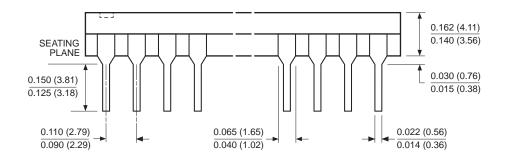

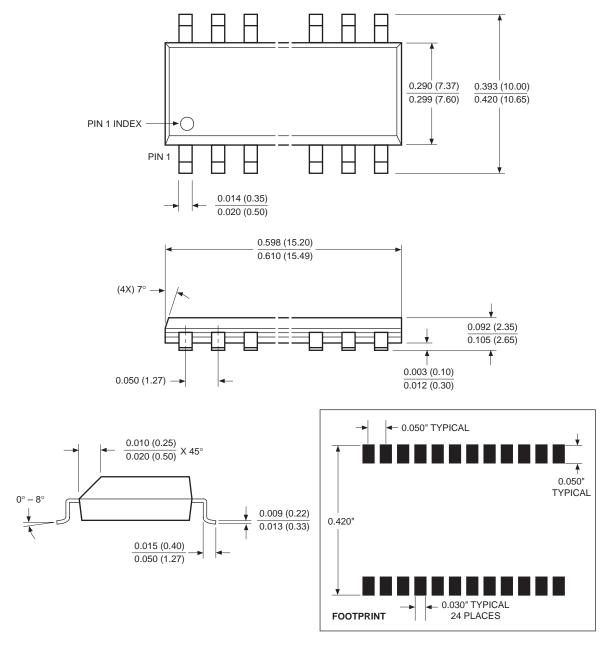

## **PACKAGING INFORMATION**

# 24-LEAD PLASTIC SMALL OUTLINE GULL WING PACKAGE TYPE S

NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

3926 FHD F24

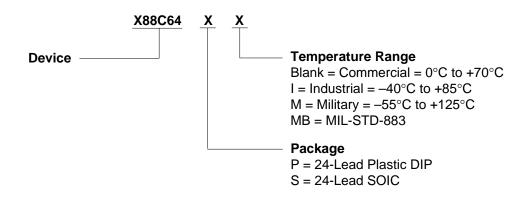

#### ORDERING INFORMATION

#### LIMITED WARRANTY

Devices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness tor any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.

Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, licenses are implied.

#### **US. PATENTS**

Xicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481; 4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829,482; 4,874,967; 4,883,976; 4,980,859; 5,012,132; 5,003,197; 5,023,694. Foreign patents and additional patents pending.

#### LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.

Xicor's products are not authorized for use as critical components in life support devices or systems.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its satety or effectiveness.