### SINGLE-CHANNEL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

SEPTEMBER 2001 REV. P1.1.0

### **GENERAL DESCRIPTION**

The XRT83L30 is a fully integrated single-channel long-haul and short-haul line interface unit for T1(1.544Mbps)  $100\Omega$ , E1(2.048Mbps)  $75\Omega$  or  $120\Omega$  and J1  $110\Omega$  applications.

In long-haul applications the XRT83L30 accepts signals that have passed through cables from 0 feet to over 6000 feet in length and have been attenuated by 0 to 45dB at 772kHz in T1 mode or 0 to 43dB at 1024kHz in E1 mode. In T1 applications, the device generates five transmit pulse shapes to meet the short-haul Digital Cross-Connect (DSX-1) template requirements as well as for Channel Service Units (CSU) Line Build Out (LBO) filters of 0dB, -7.5dB, -15dB and -22.5dB as required by FCC rules. It also provides programmable transmit pulse generator that can be used for arbitrary output pulse shaping allowing performance improvement over a wide variety of conditions.

The XRT83L30 provides both Serial Host microprocessor interface and Hardware mode for programming and control. Both B8ZS and HDB3 encoding and decoding functions are included and can be disabled as required. On-chip crystal-less jitter attenuator (with a 32 or 64 bit FIFO) can be placed either in the receive or the transmit path with loop bandwidths

of less than 3Hz. The XRT83L30 provides a variety of loop-back and diagnostic features as well as transmit driver short circuit detection and receive loss of signal monitoring. It supports internal impedance matching for  $75\Omega,\,100\Omega,\,110\Omega$  and  $120\Omega$  for both transmitter and receiver. For the receiver this is accomplished by internal resistors or through the combination of one single fixed value external resistor and programmable internal resistors. In the absence of the power supply, the transmit output and receive input are tri-stated allowing for redundancy applications. The chip includes an integrated programmable clock multiplier that can synthesize T1 or E1 master clocks from a variety of external clock sources.

### **APPLICATIONS**

- T1 Digital Cross-Connects (DSX-1)

- ISDN Primary Rate Interface

- CSU/DSU E1/T1/J1 Interface

- T1/E1/J1 LAN/WAN Routers

- · Public switching Systems and PBX Interfaces

- T1/E1/J1 Multiplexer and Channel Banks

#### **FEATURES**

(See Page 2)

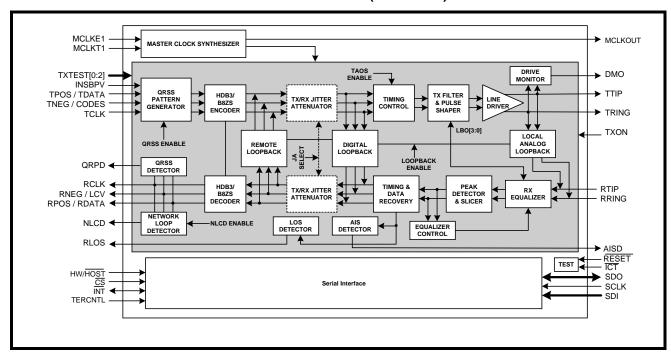

FIGURE 1. BLOCK DIAGRAM OF THE XRT83L30 T1/E1/J1 LIU (HOST MODE)

MCLKE1 MCLKOUT MASTER CLOCK SYNTHESIZER MCLKT1 CLKSEL[2:0] TAOS TXTEST[0:2] ► DMO INSBPV TPOS / TDATA HDB3/ B8ZS ENCODER TTIP TNEG / CODES **TCLK** TRING LBO[3:0] LOCAL ANALOG TXON ORSS ENABLE LOOPBACK LOOPBACK ENABLE QRPD < RCLK 4 PEAK DETECTOR & SLICER HDB3/ B8ZS RTIP DATA RNEG / LCV RRING RPOS / RDATA ◀ LOOP1 LOS DETECTOR EQUALIZER CONTROL LOOP0 NI CD 4 NLCD ENABLE AIS DETECTOR LOOP DETECTOR RLOS < RESET TEST HW/HOST JABW FIFOS TRATIO SR/DR JASEL 0 EQC[4:0] RXTSEL HARWARE CONTROL TXTSEL TCLKE RCLKE TERSEL RXMUTE RXRES0 ATAOS

FIGURE 2. BLOCK DIAGRAM OF THE XRT83L30 T1/E1/J1 LIU (HARDWARE MODE)

### **FEATURES**

- Fully integrated single-channel long-haul or shorthaul transceivers for E1,T1 or J1 applications.

- Adaptive Receive Equalizer for cable attenuation of up to 45dB for T1 and 43dB for E1.

- Programmable Transmit Pulse Shaper for E1,T1 or J1 long-haul and short-haul interfaces.

- Five fixed transmit pulse settings for T1 short-haul applications plus a fully programmable waveform generator for transmit output pulse shaping.

- Programmable Transmit Line Build-Outs (LBO) for T1 long-haul application from 0dB to -22.5dB in three 7.5dB steps.

- Tri-State transmit output and receive input capability for redundancy applications

- Selectable receiver sensitivity from 0 to 36dB or 0 to 45dB cable loss for T1 @772kHz and 0 to 43dB for E1 @1024kHz.

- High receiver interference immunity

- Receive monitor mode handles 0 to 29dB resistive attenuation along with 0 to 6dB of cable attenuation for both T1 and E1 modes.

- Supports  $75\Omega$  and  $120\Omega$  (E1),  $100\Omega$  (T1) and  $110\Omega$  (J1) applications.

- Internal and external impedance matching for  $75\Omega$ ,  $100\Omega$ ,  $110\Omega$  and  $120\Omega$ .

- Transmit return loss meets or exceeds ETSI 300 166 standard

- On-chip digital clock recovery circuit for high input iitter tolerance

- Crystal-less digital jitter attenuator with 32-bit or 64bit FIFO Selectable either in transmit or receive path

- On-chip frequency multiplier generates T1 or E1

Master clocks from variety of external clock sources

- On-chip transmit short-circuit protection and limiting, and driver fail monitor output (DMO)

- Receive loss of signal (RLOS) output

- On-chip HDB3/B8ZS/AMI encoder/decoder

- QRSS pattern generation and detection for testing and monitoring

- Error and Bipolar Violation Insertion and Detection

- Receiver Line Attenuation Indication Output in 1dB steps

- Network Loop-Code Detection for automatic Loop-Back Activation/Deactivation

- Transmit All Ones (TAOS) and In-Band Network Loop Up and Down code generators

- Supports Analog, Remote, Digital and Dual Loop-Back Modes

- Meets or exceeds T1 and E1 short-haul and longhaul network access specifications in ITU G.703,

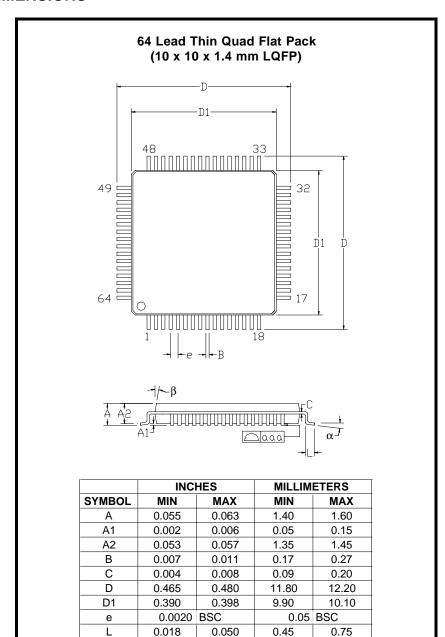

# ORDERING INFORMATION

| PART #              | PACKAGE                                | OPERATING TEMPERATURE RANGE   |

|---------------------|----------------------------------------|-------------------------------|

| XRT83L30            | 64 Pin TQFP                            | -40°C to +85°C                |

| THERMAL INFORMATION | Theta - $J_A = 38^{\circ} \text{ C/W}$ | Theta J <sub>C</sub> = 7° C/W |

# **PACKAGE DIMENSIONS**

Note: Control Dimensions are the Millimeter Column

7° typ

0°

α

β aaa 7°

0.003

0°

7° typ

7°

0.08

SINGLE-CHANNEL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR PRELIMINARY

REV. P1.1.0

## **REVISION HISTORY**

Rev. A1.0.0 Advanced version.

Rev. P1.1.0 Preliminary release.

## NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2001 EXAR Corporation

Datasheet September 2001.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.