XRT71D00

## DS3/E3 JITTER ATTENUATOR IC

REV. P1.0.0

#### FEBRUARY 2000

## **GENERAL DESCRIPTION**

The XRT71D00 is a single chip IC which accepts "jittery" clock and data signals from a LIU, internally reduces and smooths the clock and data jitter, then ouputs the smoothed data to the Terminal Equipment.

#### FEATURES

- Attenuates clock and data jitter present in DS3 or E3 systems

- No external component required

- Compliance with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE,1995 standards

- Meets output jitter generation requirement as specified by ETSI TBR24

- Selectable buffer size of 16 and 32 bits

- Jitter attenuator can be easily disabled

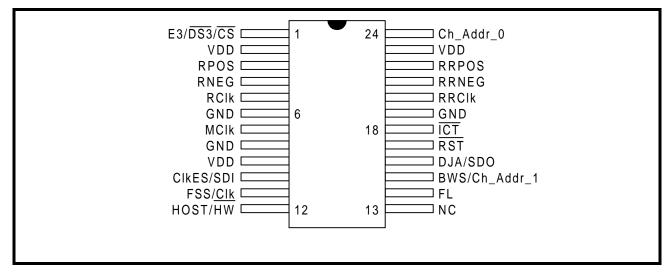

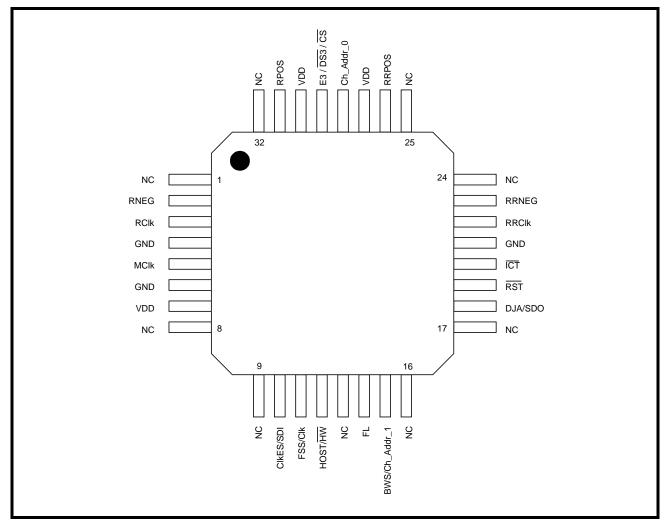

- Available in a 24 pin SOIC or 32 pin TQFP packages

- Single 3.3V or 5.0V supply.

- Operates over commercial temperature range

#### APPLICATIONS

- ETSI TBR24 34Mbit/s D34U and D34S system

- DS3/E3 Digital Multiplex and De-multiplex Equipment

- DS3 and E3 Line Interface

- PCM Test Equipment

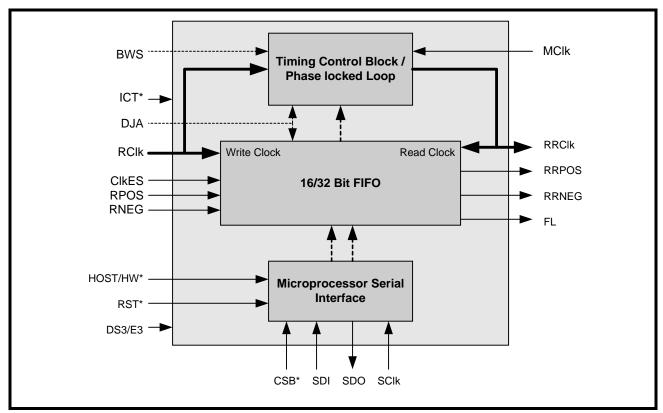

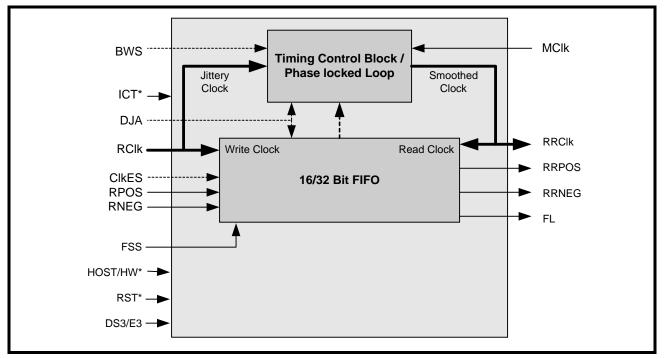

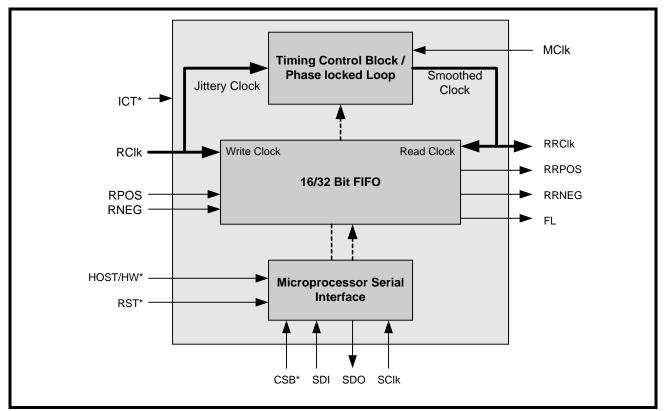

## BLOCK DIAGRAM OF THE XRT71D00 JITTER ATTENUATOR

### PIN OUT OF THE XRT71D00 (24 LEAD SOIC PACKAGE)

#### PIN OUT OF THE XRT71D00 (32 LEAD TFQP PACKAGE)

# TABLE OF CONTENTS

| GENERAL DESCRIPTION                                                                                    | 1          |

|--------------------------------------------------------------------------------------------------------|------------|

| Features                                                                                               | 1          |

| APPLICATIONS                                                                                           | 1          |

| BLOCK DIAGRAM OF THE XRT71D00 JITTER ATTENUATOR                                                        | 1          |

| PIN OUT OF THE XRT71D00 (24 LEAD SOIC PACKAGE)                                                         | 2          |

| PIN OUT OF THE XRT71D00 (32 LEAD TFQP PACKAGE)                                                         | 2          |

| PIN DESCRIPTIONS                                                                                       | 3          |

| ELECTRICAL CHARACTERISTICS                                                                             | 7          |

| ABSOLUTE MAXIMUM RATINGS:                                                                              | 7          |

| SYSTEM DESCRIPTION                                                                                     | 8          |

| Figure 1. Simple Illustration of the XRT71D00 DS3/E3 Jitter Attenuator Device (when it has been config | <b>]</b> - |

| ured to operate in the "Hardware" Mode)                                                                | 8          |

| Figure 2. Simple Illustration of the XRT71D00 DS3/E3 Jitter Attenuator Device (when it has been con-   | -          |

| figured to operate in the "Host" Mode)                                                                 |            |

| BACKGROUND INFORMATION                                                                                 | 9          |

| PRINCIPLE OF OPERATION                                                                                 | 9          |

| THE MICROPROCESSOR SERIAL INTERFACE 1                                                                  |            |

| TABLE 1: ROLE OF MICROPROCESSOR SERIAL INTERFACE PINS WHEN THE XRT71D00 DEVICE IS OPERATING IN THI     | Е          |

| "Hardware" Mode                                                                                        |            |

| TABLE 2: Addresses and Bit Formats of the XRT71D00 Command Registers                                   |            |

| Figure 3. Microprocessor Serial Interface Data Structure1                                              |            |

| Figure 4. Timing Diagram for the Microprocessor Serial Interface                                       | 2          |

| PACKAGE INFORMATION                                                                                    | 3          |

| 24 LEAD SOIC PACKAGE DIMENSIONS 1                                                                      | 3          |

| 32 LEAD TQFP PACKAGE DIMENSIONS 1                                                                      | 4          |

| ORDERING INFORMATION                                                                                   | 5          |

| REVISION HISTORY 1                                                                                     | 6          |

# LIST OF FIGURES

| FIGURE 1. SIMPLE ILLUSTRATION OF THE XRT71D00 DS3/E3 JITTER ATTENUATOR DEVICE (WHEN IT HAS BEEN CON | - |

|-----------------------------------------------------------------------------------------------------|---|

| FIGURED TO OPERATE IN THE "HARDWARE" MODE) 8                                                        | 8 |

| FIGURE 2. SIMPLE ILLUSTRATION OF THE XRT71D00 DS3/E3 JITTER ATTENUATOR DEVICE (WHEN IT HAS BEEN     |   |

| CONFIGURED TO OPERATE IN THE "HOST" MODE)                                                           | Э |

| FIGURE 3. MICROPROCESSOR SERIAL INTERFACE DATA STRUCTURE                                            | 2 |

| FIGURE 4. TIMING DIAGRAM FOR THE MICROPROCESSOR SERIAL INTERFACE                                    | 2 |

# LIST OF TABLES

| TABLE 1: ROLE OF MICROPROCESSOR SERIAL INTERFACE PINS WHEN THE XRT71D00 DEVICE IS OPERATING IN TH | ΙE |

|---------------------------------------------------------------------------------------------------|----|

| "Hardware" Mode                                                                                   | 10 |

| TABLE 2: Addresses and Bit Formats of the XRT71D00 Command Registers                              | 10 |

## **PIN DESCRIPTIONS**

## **PIN DESCRIPTION**

| 32 LEAD<br>PIN # | 24 Lead<br>Pin # | NAME        | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------------|------------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                | -                | NC          | ***  | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 2                | 4                | RNEG        | I    | Receive Negative Data (Jittery) Input.<br>Data that is input on this pin is sampled on either the rising or falling edge<br>of RClk depending on the setting of the ClkES pin (pin 10).<br>If ClkES is "high", then RNEG will be sampled on the falling edge of RClk.<br>If ClkES is "low", then RPOS will be sampled on the rising edge of RClk.<br>This pin is typically tied to the "RNEG" output pin of the LIU IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 3                | 5                | RClk        | I    | <b>Acceive Clock (Jittery) Input.</b><br>his is input that the user should route the "jittery" 44.736MHz or<br>4.368MHz clock signal (from the LIU IC).<br>his pin is typically tied to the "RClk" output pin of the LIU IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 4                | 6                | GND         | ***  | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 5                | 7                | MClk        | Ι    | Master Clock Input.Reference clock for internal PLL. 44.736MHz+/-20ppm or 34.368MHz+/-20ppm. This clock must be continuous and jitter free with duty cyclebetween 30 to 70%.Note: It is permissible to use either the EXClk signal or TClk signals(which are applied to the XRT7300 LIU IC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 6                | 8                | GND         | ***  | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 7                | 9                | VDD         | ***  | Analog Positive Supply: 3.3V or 5.0V ± 5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 8                | -                | NC          | ***  | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 9                | -                | NC          | ***  | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 10               | 10               | CIKES/(SDI) | Ι    | Clock Edge Select Input/Serial Data Input Pin.<br>The exact functionality of this input pin depends upon whether the<br>XRT71D00 device is configured to operate in the "HOST" or "Hardware"<br>Mode.<br>Hardware Mode—Clock Edge Select Input<br>The status of this pin determines the sampling edge on RClk to RPOS/<br>RNEG and RRPOS/RRNEG data update on RRClk edge.<br>When high: RPOS/RNEG is sampled on falling edge of RClk and<br>RRPOS/RRNEG is updated on rising edge of RClk.<br>When low: RPOS/RNEG is sampled on rising edge of RClk and<br>RRPOS/RRNEG is updated on falling edge of RClk.<br>When low: RPOS/RNEG is sampled on rising edge of RClk.<br>When low: RPOS/RNEG is complete on falling edge of RClk.<br>When low: RPOS/RNEG is updated on falling edge of RClk.<br>Host Mode—Serial Data Input<br>Whenever the user wishes to read or write data into the Command Regis-<br>ters, over the Microprocessor Serial Interface; the user is expected to<br>apply the "Read/Write" bit, the Address Values (of the Command Regis-<br>ters) and Data Value to be written (during "Write" Operations) to this pin.<br>This input will be sampled on the rising edge of the SClk pin (pin 11). |  |  |  |  |

## PIN DESCRIPTION

| 32 LEAD<br>PIN # | 24 LEAD<br>PIN # | NAME              | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11               | 11               | FSS/(SClk)        | Ι    | FIFO Size Select Input/Serial Clock Input.<br>The exact functionality of this input pin depends upon whether the<br>XRT71D00 device is operating in the Hardware of the Host Mode.<br>Hardware Mode—FIFO Size Select Input<br>When high: Selects 32 bits FIFO.<br>When low: Selects 16 bits FIFO.<br>Host Mode—Microprocessor Serial Interface Clock Signal<br>This signal will be used to (1) sample the data, on the SDI pin, on the rising<br>edge of this signal. Additionally, during "Read" operations, the Micropro-<br>cessor Serial Interface will update the SDO output on the falling edge of<br>this signal.                                                                                                                                                                                                                                                                                               |

| 12               | 12               | HOST/HW           |      | <b>Host/HW Mode Select:</b><br>This input pin permits the user to enable or disable the Microprocessor<br>Serial Interface (e.g., consisting of the SDI, SDO, SCIk, CSB and<br>REG_RESET* pins).<br>Setting this input pin "high" enables the Microprocessor Serial Interface (or<br>configures the XRT71D00 device to operate in the "Host" Mode). In this<br>mode, the user is expected to configure the XRT71D00 device by writing<br>data into the "on-chip" Command Register via the Microprocessor Serial<br>Interface. As a consequence, when the XRT71D00 is operating in the<br>"Host" Mode, then it will ignore the states of many of the discrete input<br>pins. Setting this input pin "low" disables the Microprocessor Serial Inter-<br>face (e.g., configures the XRT71D00 device to operate in the "Hardware"<br>Mode). In this mode, many of the external input control pins will be func-<br>tional. |

| 13               | 13               | NC                | ***  | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14               | 14               | FL                | 0    | <b>FIFO Full/Empty Alarm Output indicator.</b><br>This output pin is driven high whenever the internal FIFO comes within two-bits of either being completely empty or completely full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15               | 15               | BWS/<br>Ch_Addr_1 | Ι    | <ul> <li>Bandwidth Select Input/Channel Addr_1 Assignment Input.<br/>The exact functionality of this input pin depends upon whether the<br/>XRT71D00 device is operating in the Hardware Mode or in the "Host<br/>Mode".</li> <li>Hardware Mode—Bandwidth Select Input:<br/>Connect this pin high to select wide jitter transfer bandwidth, and connect<br/>low to select narrow jitter transfer bandwidth.</li> <li>NOTE: The exact jitter transfer bandwidths (that will be configured for<br/>either of these settings), will be defined in the next revision of this data<br/>sheet.</li> <li>Host Mode—Channel_Addr_1 Assignment Input:<br/>This input pin, along with pin 24 permits the user to assign a "Channel<br/>Address" to the XRT71D00 device.</li> </ul>                                                                                                                                               |

| 16               | -                | NC                | ***  | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17               | -                | NC                | ***  | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

4

## PIN DESCRIPTION

| 32 LEAD<br>PIN # | 24 LEAD<br>Pin # | Nаме          | Түре  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|------------------|------------------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 18               | 16               | DJA/<br>(SDO) | I/(O) | <ul> <li>Disable Jitter Attenuator Input/Serial Data Output pin:</li> <li>The exact functionality of this input pin depends upon whether the XRT71D00 device is operating in the "Hardware" or "Host" Mode.</li> <li>Hardware Mode—Disable Jitter Attenuator Input pin:</li> <li>This input permits the user to enable or disable the Jitter Attenuator IC.</li> <li>When this input pin "high", the data and clock signals, that enter the chip via the RPOS/RRNEG and RClk input pins are passed directly to RRPOS,RRNEG and RRClk, without any jitter attenuation.</li> <li>Host Mode—Serial Data Output pin:</li> <li>This pin will serially output the contents of the specified Command Register, during "Read" Operations. The data, on this pin, will be updated on the falling edge of the SClk input signal. This pin will be tri-stated upon completion of data transfer.</li> <li>Note: The user is advised to the this pin to GND, if the XRT71D00 device has been configured to operate in the "HOST" Mode.</li> </ul> |  |  |  |

| 19               | 17               | RST           | I     | <b>Reset Input.</b> (Active-Low)<br>A high-low transition will re-center the internal FIFO, and will clear the<br>Command Registers (for Host Mode operation). Resetting this pin may<br>corrupt data within the device.<br>For normal operation, the user should pull this pin to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 20               | 18               | ICT           | I     | In Circuit Testing Input. Active low.<br>With this pin tied to ground, all output pins will be in high impedance me<br>for in-circuit-testing.<br>For normal operation this input pin should be tied to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 21               | 19               | GND           | ***   | Digital Ground:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 22               | 20               | RRClk         | 0     | <b>Receive Output (De-jittered) Clock.</b><br>This is the pin, that the "smoothed" (e.g., de-jittered) 44.736MHz or<br>34.368MHz clock signal will be output from. Further, this clock signal is<br>also used to clock out the contents of the "Recovered" data (via the<br>RRPOS and RRNEG output pins).<br>If ClkES is "low", then the XRT71D00 device will output data, via the<br>RRPOS and RRNEG output pin, upon the falling edge of this clock signal.<br>If ClkES is "high", then the XRT71D00 device will output data, via the<br>RRPOS and RRNEG output pin, upon the falling edge of this clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 23               | 21               | RRNEG         | 0     | Receive Negative Data (De-Jittered) Output.<br>De-jittered negative data output. Updated on the rising or falling edge of<br>RRClk, depending upon the state of the ClkES input pin (or bit-field set-<br>ting).<br>If ClkES is "low", then the XRT71D00 device will output data via this pin,<br>upon the falling edge of the RRClk clock signal.<br>If ClkES is "high", then the XRT71D00 device will output data via the pin,<br>upon the rising edge of the RRClk clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 24               | -                | NC            | ***   | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 25               | -                | NC            | ***   | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

**X** EXAR PRELIMINARY

#### REV. P1.0.0

#### PIN DESCRIPTION

| 32 LEAD<br>PIN # | 24 LEAD<br>PIN # | Nаме           | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------|------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 26               | 22               | RRPOS          | 0    | Receive Positive Data (De-Jittered) Output.<br>De-jittered positive data output. Updated on the rising or falling edge of<br>RRClk (see pin 9), depending upon the state of the ClkES input pin (or bit-<br>field setting).<br>If ClkES is "low", then the XRT71D00 device will output data via this pin,<br>upon the falling edge of the RRClk clock signal.<br>If ClkES is "high",. then the XRT71D00 device will output data via this pin,<br>upon the rising edge of the RRClk clock signal.                                                                                              |  |  |  |

| 27               | 23               | VDD            | ***  | Digital Positive Supply Voltage: 3.3V or 5.0V ± 5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 28               | 24               | Ch_Addr_0      | I    | <b>Channel Addr_0 Assignment Input.</b><br>This input pin, along with pin 15 permits the user to assign a "Channel Address" to the XRT71D00 device.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 29               | 1                | E3/DS3<br>(CS) | 1    | <ul> <li>T3/E3 Select Input/Chip Select Input:<br/>The exact functionality of this input pin depends upon whether the XRT71D00 device has been configured to operate in the "Host" or "Hardware" Mode.</li> <li>Hardware Mode—E3/DS3* Select Input:<br/>Connect this pin low to select T3 and high to select E3 operation.</li> <li>HOST Mode—Chip Select Input:<br/>The Local Microprocessor must assert this pin (e.g., set it to "0") in order to enable communication with the XRT7300, via the Microprocessor Serial Interface. (Note: This pin is internally pulled "high".)</li> </ul> |  |  |  |

| 30               | 2                | VDD            | ***  | Digital Positive Supply Voltage: 3.3V or 5.0V ± 5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 31               | 3                | RPOS           | I    | Receive Positive Data (Jittery) Input.<br>Data that is input on this pin is sampled on either the rising or falling edge<br>of RClk depending on the setting of the ClkES pin (pin 10).<br>If ClkES is "high", then RPOS will be sampled on the falling edge of RClk.<br>If ClkES is "low", then RPOS will be sampled on the rising edge of RClk.<br>This pin is typically tied to the "RPOS" output pin of the LIU IC.                                                                                                                                                                       |  |  |  |

| 32               | -                | NC             | ***  | Not Bonded Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

## **ELECTRICAL CHARACTERISTICS**

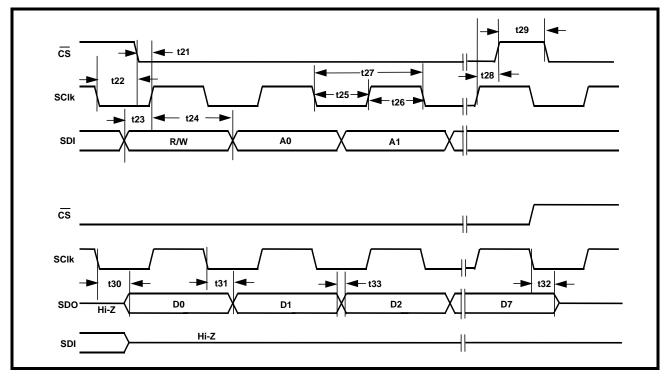

|        | AC ELECTRICAL CHARACTERISTICS                         |     |     |     |        |  |  |  |  |  |  |  |

|--------|-------------------------------------------------------|-----|-----|-----|--------|--|--|--|--|--|--|--|

|        | MICROPROCESSOR SERIAL INTERFACE TIMING (SEE FIGURE 4) |     |     |     |        |  |  |  |  |  |  |  |

| SYMBOL | PARAMETER                                             | Min | Түр | ΜΑΧ | UNITS. |  |  |  |  |  |  |  |

| t21    | CSB Low to Rising Edge of SClk Setup Time             | 50  |     |     | ns     |  |  |  |  |  |  |  |

| t22    | SCIk to CSB Hold Time                                 | 20  |     |     | ns     |  |  |  |  |  |  |  |

| t23    | SDI to Rising Edge of SCIk Setup Time                 | 50  |     |     | ns     |  |  |  |  |  |  |  |

| t24    | SDI to Rising Edge of SClk Hold Time                  | 50  |     |     | ns     |  |  |  |  |  |  |  |

| t25    | SClk "Low" Time                                       | 240 |     |     | ns     |  |  |  |  |  |  |  |

| t26    | SClk "High" Time                                      | 240 |     |     | ns     |  |  |  |  |  |  |  |

| t27    | SCIk Period                                           | 500 |     |     | ns     |  |  |  |  |  |  |  |

| t28    | SCIk to CSB Hold Time                                 | 50  |     |     | ns     |  |  |  |  |  |  |  |

| t29    | CSB "Inactive" Time                                   | 250 |     |     | ns     |  |  |  |  |  |  |  |

| t30    | Falling Edge of SCIk to SDO Valid Time                |     |     | 200 | ns     |  |  |  |  |  |  |  |

| t31    | Falling Edge of SCIk to SDO Invalid Time              |     |     | 100 | ns     |  |  |  |  |  |  |  |

| t32    | Falling Edge of SClk, or rising edge of CSB to High Z |     | 100 |     | ns     |  |  |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| DC ELECTRICAL CHARACTERISTICS (TA=25°C, VDD=5.0V±5%, unless otherwise specified). |                 |       |     |      |       |  |  |  |  |

|-----------------------------------------------------------------------------------|-----------------|-------|-----|------|-------|--|--|--|--|

| PARAMETER                                                                         | SYMBOL          | Min   | Түр | ΜΑΧ  | UNITS |  |  |  |  |

| Power Supply Voltage                                                              | VDD             | 3.135 | 5.0 | 5.25 | V     |  |  |  |  |

| Input High Voltage                                                                | VIH             | 2.0   |     | 5.25 | V     |  |  |  |  |

| Input Low Voltage                                                                 | V <sub>IL</sub> | -0.5  | _   | 0.8  | V     |  |  |  |  |

| Output High Voltage @ IOH=-5mA                                                    | VOH             | 2.4   | _   | —    | V     |  |  |  |  |

| Output Low Voltage @ IOL=5mA                                                      | VOL             | —     |     | 0.4  | V     |  |  |  |  |

| Input Leakage Current(except Input pins with Pull-up resistor.                    | IL              | —     |     | ± 10 | μΑ    |  |  |  |  |

| Input Capacitance                                                                 | CI              |       | 5.0 | —    | pF    |  |  |  |  |

| Output Load Capacitance                                                           | CL              |       |     | 25   | pF    |  |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS:**

| Supply Range          | -0.5 V to + 6.0 V                        |

|-----------------------|------------------------------------------|

| ESD Rating            | > 2000 V on all pins                     |

| Operating Temperature | -40 <sup>0</sup> C to +85 <sup>0</sup> C |

| Storage Temperature   | -65°C to + 150°C                         |

## SYSTEM DESCRIPTION

The XRT71D00 is a fully integrated and self contained DS3/E3 jitter attenuator designed to attenuate jitter the incoming clock and data in PCM system. The XRT71D00 device was designed to attenuate the jitter (of the incoming clock and data) such that the following specifications could be met.

ETSI TBR 24

ITU-T G.751

ITU-T G.752

ITU-T G.755

Bellcore GR-499-CORE Category I and II Equipment Jitter Requirements.

Additionally, the XRT71D00 device can also be used to reduce and limit the amount of jitter, in the recovered line clock signal, in order to support loop-timing applications.

Figure 1 presents a simple block diagram of the XRT71D00 device, (when it is configured to operate in the "Hardware" Mode); and Figure 2 presents a simple block diagram of the XRT71D00 device, (when it is configured to operate in the "Host" Mode.

# FIGURE 1. SIMPLE ILLUSTRATION OF THE XRT71D00 DS3/E3 JITTER ATTENUATOR DEVICE (WHEN IT HAS BEEN CONFIGURED TO OPERATE IN THE "HARDWARE" MODE)

FIGURE 2. SIMPLE ILLUSTRATION OF THE XRT71D00 DS3/E3 JITTER ATTENUATOR DEVICE (WHEN IT HAS BEEN CONFIGURED TO OPERATE IN THE "HOST" MODE)

The XRT71D00 DS3/E3 Jitter Attenuator IC consists of the following functional blocks:

- Timing Control Block

- The "Jitter-Attenuator" PLL

- The "2-Channel 16/32 Bit FIFO".

## **BACKGROUND INFORMATION**

In PCM systems, jitter is defined as the instantaneous variation of data edges compared to a perfect clock. Jitter on incoming data can occur due to any of the following sources:

- 1. The pattern of the incoming line signal

- 2. Imperfect timing recovery circuit in the system.

- 3. Cross-talk Noise

- 4. Inter-Symbol Interference/Signal Distortion

#### PRINCIPLE OF OPERATION

The XRT71D00 DS3/E3 Jitter Attenuator accepts a "jittery" clock and data from an LIU IC; via the RClk, RPOS and RNEG input pins. This "jittery" recovered data is clocked into the "16/32 bit FIFO" via the "jittery clock" signal (at the RClk input pin). In parallel, this same jittery clock signal is also input into the "Jitter

Attenuator PLL". The "Jitter Attenuator PLL" is a "Narrow-Band" PLL that is used to:

- 1. Track the jittery RClk signal, (from the LIU IC); and

- **2.** To regenerate this signal (with considerably less jitter).

In Figures 1 and 2, this "de-jittered" clock is labeled "Smoothed Clock". This "Smoothed Clock" is now used to "Read Out" the "Recovered Data" from the 16/32 bit FIFO. This "Smoothed Clock" will also be output (to the Terminal Equipment) via the "RRClk" output pin. Likewise, the "Smoothed Recovered Data" will output (to the Terminal Equipment) via the RR-POS and RRNEG output pins.

The XRT71D00 device is designed to work as a companion device with XRT7300 (STS-1/DS3/E3) Line Interface Unit.

In order to recover the data correctly by the receiver and to satisfy input jitter tolerance, the clock recovery circuit inside the Line Interface Unit such as XRT7300 must have enough bandwidth to track the incoming data timing variation. As a result, the recovered clock will be jittery and is not suitable to be used as a transmit clock source in looped-time mode situation. In

particular, with E3 system, TBR24 specifies the maximum output jitter must be no more than 0.4UIpp when measured between 100Hz to 800KHz. This means a jitter attenuator with bandwidth less than 100Hz is required to be compliant with the standard in looped-timing. ITU G.751 is another application where low bandwidth jitter attenuator is needed to smooth the gapped clock output in the de-multiplexer system.

#### THE MICROPROCESSOR SERIAL INTERFACE

The XRT71D00 device can be configured to operate in either the "Hardware" Mode or in the "Host" Mode. Each of these modes will be discussed below. The XRT71D00 device can be configured to operate in the "Hardware Mode" by tying the "Host/ $\overline{HW}$ " input pin (pin 12) to GND.

When the XRT71D00 device is operating in the "Hardware Mode", then the following is true.

- 1. The Microprocessor Serial Interface block is disabled .

- **2.** The XRT71D00 device is configured via input pin settings.

Each of the pins associated with the Microprocessor Serial Interface will take on their alternative role, as defined in table 1.

#### THE HARDWARE MODE

# TABLE 1: ROLE OF MICROPROCESSOR SERIAL INTERFACE PINS WHEN THE XRT71D00 DEVICE IS OPERATING IN THE "HARDWARE" MODE

| PIN NUMBER<br>(32 PIN TQFP) | PIN NUMBER<br>(24 PIN SOIC) | PIN NAME      | FUNCTION, WHILE IN THE HARDWARE<br>MODE |

|-----------------------------|-----------------------------|---------------|-----------------------------------------|

| 10                          | 10                          | CIKES (SDI)   | CIKES                                   |

| 11                          | 11                          | FSS (SClk)    | FSS                                     |

| 15                          | 15                          | BWS/Ch_Addr_0 | BWS                                     |

| 18                          | 16                          | DJA/(SDO)     | DJA                                     |

| 28                          | 24                          | Ch_Addr_1     | None                                    |

| 29                          | 1                           | E3/DS3/(CS)   | E3/DS3                                  |

#### THE HOST MODE

The XRT71D00 device can be configured to operate in the "Host" Mode by tying the "Host/ $\overline{HW}$ " input pin (pin 12) to VDD.

When the XRT71D00 is operating in the "Host Mode", then the following is true.

The Microprocessor Serial Interface block is enabled. Many configuration selections are made by writing the appropriate data into on-chip command Registers via the Microprocessor Serial Interface.

#### THE MICROPROCESSOR SERIAL INTERFACE

The XRT71D00 DS3/E3 Jitter Attenuator IC permits the user to have access to the "on-chip" Command

Registers. Through these Command Registers, the user can configure the XRT71D00 device into a widevariety of modes. This section discusses the following:

#### THE DESCRIPTION OF THE COMMAND REGISTERS.

- 1. A description on how to use the Microprocessor Serial Interface.

- 2. Description of the Command Registers

- **3.** A listing of these Command Registers, their Addresses, and their bit-formats are listed below in Table 2.

#### TABLE 2: ADDRESSES AND BIT FORMATS OF THE XRT71D00 COMMAND REGISTERS

| Address | Command<br>Register | CH_ADDR_<br>1 | CH_ADDR_<br>0 | Түре | D5    | D4     | D3  | D2  | D1    | D0  |

|---------|---------------------|---------------|---------------|------|-------|--------|-----|-----|-------|-----|

| 0x05    | CR5                 | 0             | 0             | R/W  | PkSEL | E3/DS3 | DJA | BWS | CIKES | FSS |

| 0x0D    | CR13                | 0             | 1             | R/W  | PkSEL | E3/DS3 | DJA | BWS | CIKES | FSS |

| 0x15    | CR21                | 1             | 0             | R/W  | PkSEL | E3/DS3 | DJA | BWS | CIkES | FSS |

Some of the fields within Table 2 deserve some explanation. The Microprocessor Serial Interface was

designed such that the XRT71D00 device could be operated in conjunction with other Exar LIU ICs, as described below.

- A Microprocessor can configure both the XRT7300 DS3/E3/STS-1 LIU IC and a single XRT71D00 device via a single CS, SDI, SDO and SClk input and output pins.

- A Microprocessor can configure both the XRT7302 Dual Channel DS3/E3/STS-1 LIU IC and two XRT71D00 devices (one associated with each channel of the XRT7302 device) via a single CS, SDI, SDO and SCIk input and output pins.

- A Microprocessor can configure both the XRT73L03 Triple Channel DS3/E3/STS-1 LIU IC and three XRT71D00 devices (one associated with each channel of the XRT73L03 device) via a single CS, SDI, SDO and SCIk input and output pins.

#### OPERATING THE MICROPROCESSOR SERIAL INTERFACE.

The XRT7300 Serial Interface is a simple four-wire interface that is compatible with many of the microcontrollers available in the market. This interface consists of the following signals:

CS—Chip Select (Active Low)

SClk—Serial Clock

SDI—Serial Data Input

SDO—Serial Data Output

#### USING THE MICROPROCESSOR SERIAL INTERFACE

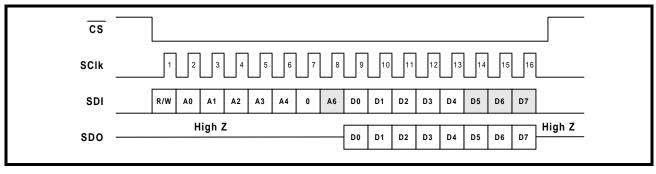

The following instructions, for using the Microprocessor Serial Interface, are best understood by referring to the diagram in Figure 3.

In order to use the Microprocessor Serial Interface the user must first provide a clock signal to the SClk input pin. Afterwards, the user will initiate a "Read" or "Write" operation by asserting the "active-low" Chip Select input pin  $\overline{(CS)}$ . It is important to assert the  $\overline{CS}$ pin (e.g., toggle it "low") at least 50ns prior to the very first rising edge of the clock signal.

Once the  $\overline{CS}$  input pin has been asserted the type of operation and the target register address must now be specified by the user. The user provides this information to the Microprocessor Serial Interface by writing eight serial bits of data into the SDI input. Note: each of these bits will be "clocked" into the SDI input, on the rising edge of SClk. These eight bits are identified and described below.

#### BIT 1—"R/W" (READ/WRITE) BIT

This bit will be clocked into the SDI input, on the first rising edge of SCIk (after  $\overline{CS}$  has been asserted). This bit indicates whether the current operation is a

"Read" or "Write" operation. A "1" in this bit specifies a "Read" operation; whereas, a "0" in this bit specifies a "Write" operation.

Bits 2 through 5: The four (4) bit Address Values (labeled A0, A1, A2 and A3)

The next four rising edges of the SClk signal will clock in the 4-bit address value for this particular Read (or Write) operation. The address selects the Command Register, within the XRT7300 device that the user will either be reading data from, or writing data to. The user must supply the address bits to the SDI input pin, in ascending order with the LSB (least significant bit) first.

#### BITS 6 AND 7:

The next two bits, A4 and A5 must be set to "0", as shown in Figure 3.

#### Віт 8—А6

The value of "A6" is a "don't care".

Once these first 8 bits have been written into the Microprocessor Serial Interface, the subsequent action depends upon whether the current operation is a "Read" or "Write" operation.

#### READ OPERATION

Once the last address bit (A3) has been clocked into the SDI input, the "Read" operation will proceed through an idle period, lasting three SCIk periods. On the falling edge of SCIk Cycle #8 (see Figure 3 ) the serial data output signal (SDO) becomes active. At this point the user can begin reading the data contents of the addressed Command Register (at Address [A3, A2, A1, A0]) via the SDO output pin. The Microprocessor Serial Interface will output this five bit data word (D0 through D4) in ascending order (with the LSB first), on the falling edges of the SCIk pin. As a consequence, the data (on the SDO output pin) will be sufficiently stable for reading (by the Microprocessor), on the very next rising edge of the SCIk pin.

#### WRITE OPERATION

Once the last address bit (A3) has been clocked into the SDI input, the "Write" operation will proceed through an idle period, lasting three SCIk periods. Prior to the rising edge of SCIk Cycle # 9 (see Figure 3 ) the user must begin to apply the eight bit data word, that he/she wishes to write to the Microprocessor Serial Interface, onto the SDI input pin. The Microprocessor Serial Interface will latch the value on the SDI input pin, on the rising edge of SCIk. The user must apply this word (D0 through D7) serially, in ascending order with the LSB first.

#### Note:

A4 and A5 are always "0". R/W = "1" for "Read" Operations R/W = "0" for "Write" Operations Denotes a "don't care" value (shaded areas) SIMPLIFIED INTERFACE OPTION The user can simplify the design of the circuitry connecting to the Microprocessor Serial Interface by tying both the SDO and SDI pins together, and reading data from and/or writing data to this "combined" signal. This simplification is possible because only one of these signals are active at any given time. The inactive signal will be tri-stated.

## **PACKAGE INFORMATION**

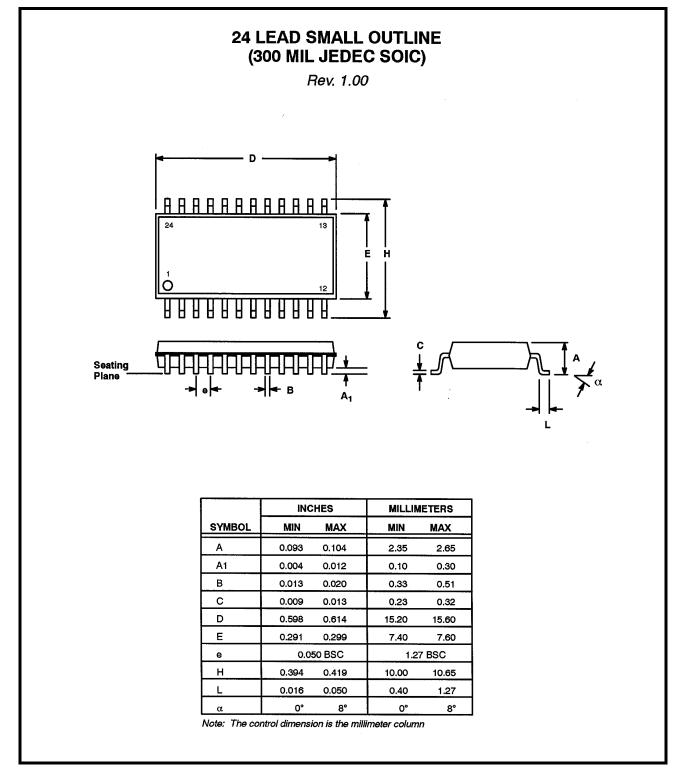

## 24 LEAD SOIC PACKAGE DIMENSIONS

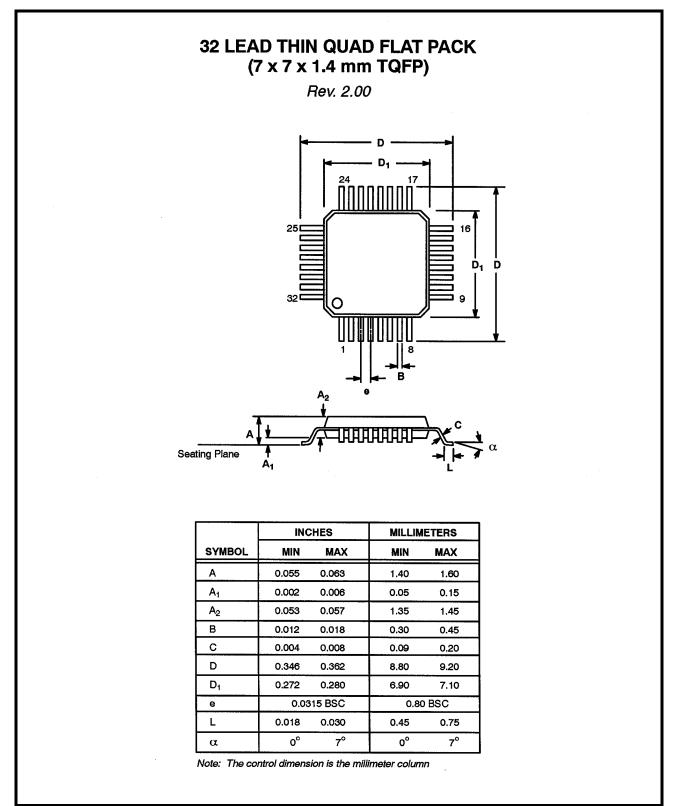

## 32 LEAD TQFP PACKAGE DIMENSIONS

## **ORDERING INFORMATION**

| PART NUMBER | PACKAGE                      | OPERATING TEMPERATURE RANGE              |

|-------------|------------------------------|------------------------------------------|

| XRT71D00ID  | 24 Lead JEDEC SOIC (300 mil) | -40 <sup>0</sup> C to +85 <sup>0</sup> C |

| XRT71D00IQ  | 32 Lead TQFP                 | -40 <sup>0</sup> C to +85 <sup>0</sup> C |

XRT71D00

PRELIMINARY

REV. P1.0.0

### **REVISION HISTORY**

Pin (15)/15 changed to BWS/Ch\_Addr\_1, pin (24)/28 changed to Ch\_Addr\_0, Added D5 to table 2, Corrected HW\*, DS3\*, CSB\*, RST\*, ICT\* to HW, DS3, CS, RST, ICT, changed date to February 2000.

**/** EXAR

**DS3/E3 JITTER ATTENUATOR IC**

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation ration is adequately protected under the circumstances.

Copyright 2000 EXAR Corporation

Datasheet February 2000

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.