June 1997-3

#### **FEATURES**

- Fully Integrated T1 Transceiver

- Low Power Consumption (normally 225mW)

- Recovered Data and Clock Outputs

- Driver Performance Monitor

- Internal Transmit LBO for Line Lengths Between 0 to 655 Feet

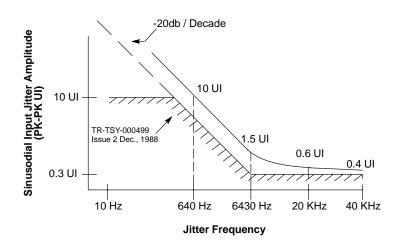

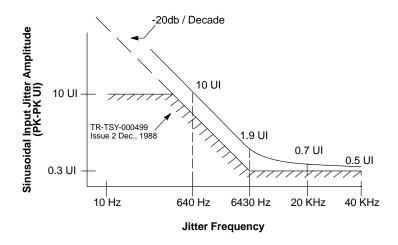

- Compliance with TR-TSY-000499, 43802 and 43801

Input Jitter Tolerance Specifications

#### **APPLICATIONS**

- Interfacing T1 Network Equipment such as Multiplexers, Channel Banks and DSX-1 Switching Systems

- Interfacing Customer Premises Equipment such as CSUs, PBXs, T1 Measurement and Test Equipment

#### **GENERAL DESCRIPTION**

The XR-T5684 is a fully integrated PCM line transceiver intended for DSX-1 digital cross-connect applications. It combines both transmit and receive circuitry in a 28 pin PLCC or PDIP package. The receiver extracts data from AMI coded input signal, and outputs synchronized clock and unipolar RPOS and RNEG data by means of an external 8X or 16X oversampling clock. The oversampling clock is necessary only for applications where the clock recovery

feature is required. The transmitter of the device pre-shapes the transmit pulse internally, providing the appropriate pulse shape at the cross-connect for line lengths ranging from 0 to 655 feet. The XR-T5684 is manufactured using advanced CMOS technology and requires only a single +5V power supply.

#### **ORDERING INFORMATION**

| Part No.   | Package              | Operating<br>Temperature Range |

|------------|----------------------|--------------------------------|

| XR-T5684IJ | 28 Lead PLCC         | -40 to + 85°C                  |

| XR-T5684IP | 28 Lead 600 Mil PDIP | -40 to + 85°C                  |

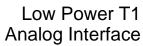

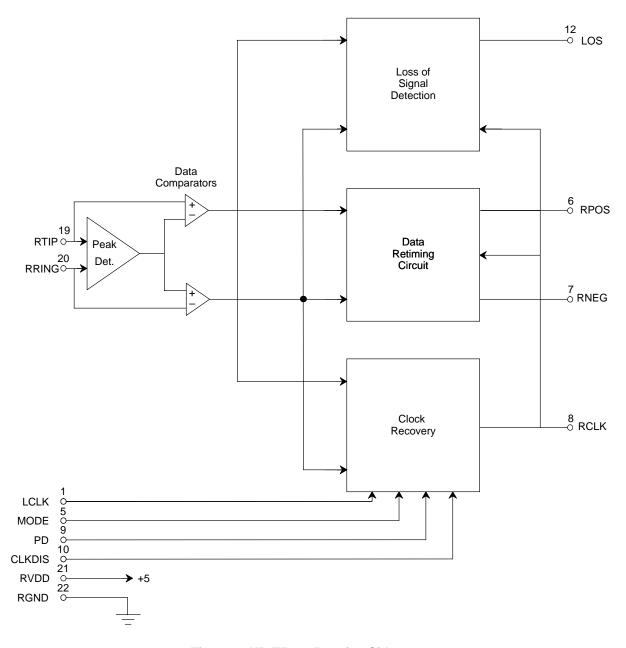

#### **BLOCK DIAGRAM**

Figure 1. XR-T5684 Receive Side

Figure 2. XR-T5684 Transmit Side

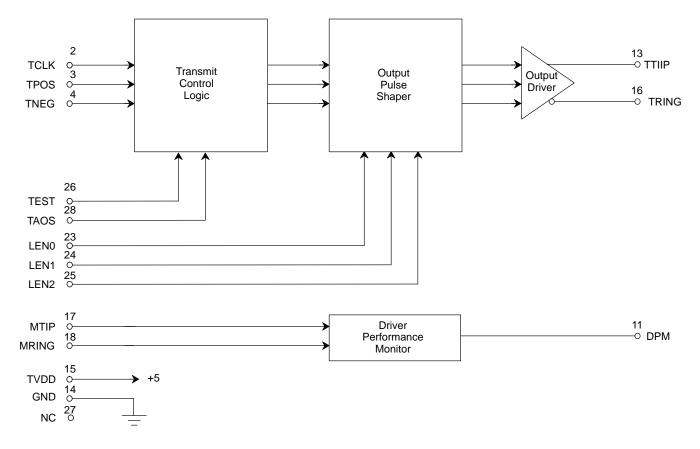

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| Pin # | Symbol | Туре | Description                                                                                                                                                                                                                                                                                                           |

|-------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | LCLK   | I    | Oversampling Clock. 8X or 16X input clock for receive clock recovery circuit. 8X=12.352MHz±200ppm with pin 9 set to low. 16X=24.704MHz ±200ppm with pin 9 set to high.                                                                                                                                                |

| 2     | TCLK   | 1    | Transmit Clock. T1=1.544MHz±50ppm.                                                                                                                                                                                                                                                                                    |

| 3     | TPOS   | ı    | <b>Transmit Positive Data</b> . A positive NRZ data on this pin causes a positive pulse to be transmitted on TTIP. TPOS is sampled on the falling edge of TCLK.                                                                                                                                                       |

| 4     | TNEG   | ı    | <b>Transmit Negative Data</b> . A positive NRZ data on this pin causes a negative pulse to be transmitted on TRING. TNEG is sampled on the falling edge of TCLK.                                                                                                                                                      |

| 5     | MODE   | I    | Receive Output Data Select. With this pin set to high, the extracted data at RPOS and RNEG are re-timed using the recovered clock RCLK. With this pin set to low, the received data have no relation to RCLK and are typically stretched by 80nS before being sent to the output. This pin is pulled down internally. |

| 6     | RPOS   | 0    | <b>Receive Positive Data Output</b> . A positive pulse on this pin corresponds to a positive pulse on RTIP.                                                                                                                                                                                                           |

| 7     | RNEG   | 0    | <b>Receive Negative Data Output</b> . A positive pulse on this pin corresponds to a positive pulse on RRING.                                                                                                                                                                                                          |

| 8     | RCLK   | 0    | Receive Clock Output. Recovered clock using oversampling clock applied to pin 1. See MODE select of pin 5 and PD of pin 9.                                                                                                                                                                                            |

| 9     | PD     | I    | <b>Programmable Divider</b> . The state of this pin determines the oversampling clock applied to pin 1. When LCLK=16X1.544MHz, set PD to high. When LCLK=8X1.544MHz, set PD to low. This pin is pulled down internally.                                                                                               |

| 10    | CLKDS  | ı    | <b>Clock Disable</b> . With this pin set to high, the recovered clock at pin 8 is disabled. This function is provided for applications where upon input data loss, the output clock can be inhibited by connecting LOS to CLKDS externally. This pin is pulled down internally.                                       |

| 11    | DPM    | 0    | <b>Driver Performance Monitor</b> . Used as an early warning signal on non-functioning T1 links. If no signal is present on MTIP and MRING for 63 clock cycles. DPM goes high until a next pulse is detected.                                                                                                         |

### PIN DESCRIPTION (CONT'D)

| Pin # | Symbol | Туре | Description                                                                                                                                                                                                     |

|-------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | LOS    | 0    | <b>Loss of Signal.</b> This pin goes high either when the input signal at RTIP and RRING drops to below 0.4V peak or after 175 zeros are detected. The 175 zeros detection is active only when LCLK is applied. |

| 13    | TTIP   | 0    | <b>Transmit Positive Data.</b> Transmit AMI signal is driven to the line via a step-up transformer from this pin.                                                                                               |

| 14    | TGND   |      | Transmitter Supply Ground. This pin can be connected to RGND externally.                                                                                                                                        |

| 15    | TVDD   | 0    | 5 V ±5% Transmitter Supply.                                                                                                                                                                                     |

| 16    | TRING  | 0    | <b>Transmit Negative Data.</b> Transmit AMI signal is driven to the line via a step-up transformer from this pin.                                                                                               |

| 17    | MTIP   | I    | <b>Driver Performance Monitor Input.</b> This pin is normally connected to TTIP for monitoring the driver's activity. It is pulled high internally.                                                             |

| 18    | MRING  | I    | <b>Driver Performance Monitor Input.</b> This pin is normally connected to TRING for monitoring the driver's activity. It is pulled high internally.                                                            |

| 19    | RTIP   | l ı  | Receive Tip Input. The AMI receive signal is input to this pin via a centre-tapped transformer.                                                                                                                 |

| 20    | RRING  | l ı  | Receive Ring Input. The AMI receive signal is input to this pin via a centre-tapped transformer.                                                                                                                |

| 21    | RVDD   |      | 5 V ±5% Receive Supply. This pin can be connected to TVDD externally.                                                                                                                                           |

| 22    | RGND   |      | Receive Supply Ground. This pin is also connected to the substrate of the device.                                                                                                                               |

| 23    | LEN0   | ı    | Pulse Shaper Select Pin. Least significant bit.                                                                                                                                                                 |

| 24    | LEN1   | ı    | Pulse Shaper Select Pin. Second significant bit.                                                                                                                                                                |

| 25    | LEN2   | ı    | Pulse Shaper Select Pin. Most significant bit.                                                                                                                                                                  |

| 26    | TEST   | ı    | Factory Test Pin. This pin must be grounded for normal operation.                                                                                                                                               |

| 27    | N/C    |      | No Connection Pin. This pin can be grounded or left floating.                                                                                                                                                   |

| 28    | TAOS   | I    | <b>Transmit All Ones Select.</b> Setting TAOS high causes continuous AMI ones to be transmitted to the line at the frequency set by TCLK.                                                                       |

#### **ELECTRICAL CHARACTERISTICS**

Test Conditions: TA = -40 to + 85  $^{\circ}$ C, RV<sub>DD</sub> and TV<sub>DD</sub> = 5V  $\pm$  5%, RGND and TGND = 0V.

| Symbol                            | Parameter                                   | Min. | Тур.   | Max.      | Unit         | Conditions                                                                                                    |  |  |

|-----------------------------------|---------------------------------------------|------|--------|-----------|--------------|---------------------------------------------------------------------------------------------------------------|--|--|

| DC ELECTR                         | DC ELECTRICAL CHARACTERISTICS               |      |        |           |              |                                                                                                               |  |  |

| Recommended Operating Conditions  |                                             |      |        |           |              |                                                                                                               |  |  |

| V <sub>DD</sub> /TV <sub>DD</sub> | DC Supply Voltage                           | 4.75 | 5      | 5.25      | V            |                                                                                                               |  |  |

| PD                                | Total Power Disapation                      |      |        | 400       | mW           | 100% ones density & max. line length @ 5.25V and with 16X oversampling clock running.                         |  |  |

| PD                                | Normal Power Dissipation                    |      | 225    |           | mW           | 50% ones density & 300 feet line length @5.0V and with over-sampling clock disabled.                          |  |  |

| Inputs                            |                                             |      |        |           |              |                                                                                                               |  |  |

| V <sub>IH</sub>                   | High Level Input <sup>1</sup>               | 2.0  |        |           | V            |                                                                                                               |  |  |

| $V_{IL}$                          | Low Level Input <sup>1</sup>                |      |        | 0.8       | V            |                                                                                                               |  |  |

| I <sub>IL</sub>                   | Input Leakage Current                       |      |        | ±10       | μΑ           | Pins = TCLK, TPOS, TNEG,<br>LEN0/1/2.                                                                         |  |  |

| Outputs                           |                                             |      |        |           |              |                                                                                                               |  |  |

| V <sub>OH</sub>                   | High Level Output <sup>2</sup>              | 2.4  |        |           | V            |                                                                                                               |  |  |

| $V_{OL}$                          | Low Level Output <sup>2</sup>               |      |        | 0.4       | V            |                                                                                                               |  |  |

| Analog Spec                       | ifications                                  |      |        |           |              |                                                                                                               |  |  |

| VPA                               | AMI Output Pulse Amplitudes                 | 2.4  | 3.0    | 3.6       | V            | Measured at DSX-1 using a 1:1.36 step up transformer with all line length select as shown in <i>Table 1</i> . |  |  |

| TXJA                              | Jitter added by the transmitter             |      |        |           |              |                                                                                                               |  |  |

|                                   | 10Hz - 40KHz <sup>3</sup>                   |      | 0.025  |           | UI           |                                                                                                               |  |  |

|                                   | Broad Band <sup>3</sup>                     |      | 0.05   |           | UI           |                                                                                                               |  |  |

| RXS                               | Receiver Sensitivity<br>Below DSX(0dB=2.4V) | 6    |        |           | dB           |                                                                                                               |  |  |

| RLOS                              | Receiver Loss of Signal<br>Threshold        |      | 0.4    |           | V            |                                                                                                               |  |  |

|                                   | Number of Consecutive Zeros before LOS      | 160  | 175    | 190       |              |                                                                                                               |  |  |

| RTH                               | Receiver Data Slicing<br>Threshold          |      | 70     |           | % of<br>peak |                                                                                                               |  |  |

| AC CHARAC                         | TERISTICS                                   |      |        |           |              |                                                                                                               |  |  |

| TCLKf                             | Clock Frequency                             |      | 1.544  |           | MHz          |                                                                                                               |  |  |

|                                   | TCLK Clock Duty Cycle                       | 40   | 50     | 60        | %            |                                                                                                               |  |  |

| LCLKf                             | Frequency 8X                                |      | 12.352 |           | MHz          |                                                                                                               |  |  |

| LCLKf                             | 16X                                         |      | 24.704 |           | MHz          |                                                                                                               |  |  |

|                                   | LCLK Clock Tolerance                        |      |        | $\pm$ 200 | ppm          |                                                                                                               |  |  |

|                                   | LCLK Clock Duty Cycle                       | 35   | 50     | 65        | %            |                                                                                                               |  |  |

- <sup>1</sup> All input pins except RTIP, RRING, MTIP and MRING.

- All output pins except TTIP and TRING.

Input clock to TCLK is jitter free.

Pin 5 Set to low.

### **ELECTRICAL CHARACTERISTICS (CONT'D)**

Test Conditions: TA = -40 to + 85  $^{\circ}$ C, RV<sub>DD</sub> and TV<sub>DD</sub> = 5V  $\pm$  5%, RGND and TGND = 0V.

| Symbol | Parameter                                                | Min. | Тур. | Max. | Unit | Conditions |

|--------|----------------------------------------------------------|------|------|------|------|------------|

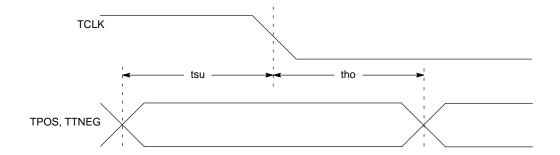

| tsu    | TPOS/TNEG to TCLK Setup<br>Time                          | 25   |      |      | ns   |            |

| tho    | TCLK to TPOS/TNEG Hold<br>Time                           | 25   |      |      | ns   |            |

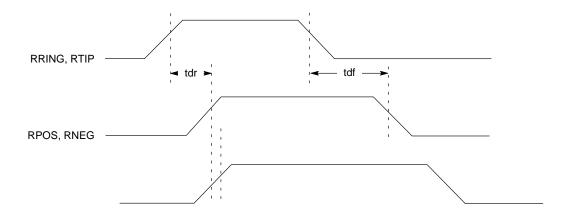

| tdr    | RTIP/RRING Rising to RPOS/<br>RNEG Rising <sup>4</sup>   | 15   | 30   | 120  | ns   |            |

| tdf    | RTIP/RRING Falling to RPOS/<br>RNEG Falling <sup>4</sup> | 60   | 120  | 250  | ns   |            |

|        | RCLK Duty Cycle                                          |      | 50   |      | %    |            |

| tsu    | RPOS/RNEG to RCLK Falling<br>Setup Time                  |      | 300  |      | ns   |            |

| tho    | RCLK Falling to RPOS/RNEG<br>Hold Time                   |      | 324  |      | ns   |            |

#### Notes

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage (continuous) .....-0.5V, +7V Supply Current (continuous) ..... 20mA to -20mA Storage Temperature .....-65°C to + 150°C

<sup>&</sup>lt;sup>1</sup> All input pins except RTIP, RRING, MTIP and MRING.

<sup>&</sup>lt;sup>2</sup> All output pins except TTIP and TRING. <sup>3</sup> Input clock to TCLK is jitter free.

<sup>&</sup>lt;sup>4</sup> Pin 5 Set to low.

#### SYSTEM DESCRIPTION

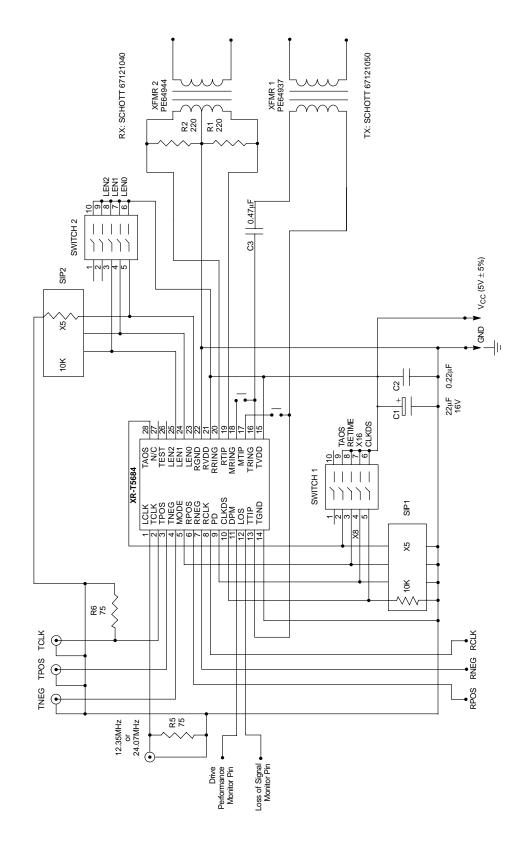

The device consists of receiver and transmitter circuitry with separate power supplies to reduce crosstalk between the two sections.

#### **RECEIVER**

The receiver is sensitive to the entire cable length from the cross-connect and requires no external equalization networks. The receive AMI input signal is applied to RTIP and RRING through a center-grounded transformer. The positive pulse is input to RTIP and the negative pulse is input to RRING.

Comparators are used to slice the data on RTIP and RRING. The slicing level of the comparators are dynamically set at around 70% of peak level of the input signal to ensure optimum signal-to-noise ratio. With Mode Select (pin 5) set to low, the clock recovery feature is bypassed and the output data from the comparators are typically stretched by 80nS before output to RPOS and RNEG respectively.

A positive data at RPOS corresponds to a positive pulse received at RTIP and a positive data at RNEG corresponds to a positive pulse received at RRING.

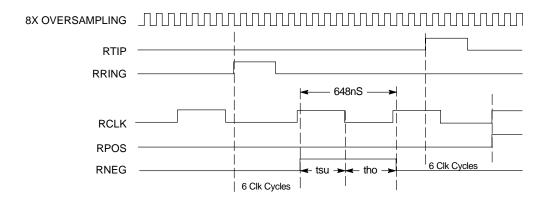

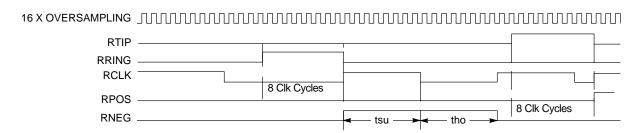

With Mode Select (pin 5) set to high and an oversampling clock applied to pin 1, the recovered data can be synchronized with RCLK at pin 8. The clock recovery circuit extracts the timing contents from the incoming data transitions by means of an 8X or 16X divider. If there is no data on the input, the divider operates in its free running mode, generating a equal mark-and-space ratio output clock. This free running mode will be interrupted if a positive pulse is detected; the resultant mark-and-space ratio of the output clock is then determined by the position of the occurrence of the positive data relative to its free running position. See timing diagram in *Figure 3* and *Figure 4*.

In all cases, the output data RPOS and RNEG remains stable on the falling edge of RCLK so as to be sampled correctly. The input jitter tolerance with an 8X oversampling clock is shown in *Figure 6* and that with a 16X oversampling clock is shown in *Figure 5*.

Figure 3. Receiver Clock and Data Switching Characteristics

Figure 4. Typical Receive Timing Diagram Using 8X Oversampling Clock.

Figure 5. Typical Receive Timing Diagram Using 16X Oversampling Clock

Figure 6. XR-T5684 Input Jitter Tolerance Using 8X Oversampling Clock

Another function of the receiver is the signal quality monitor that reports loss of signal when the input level on RTIP and RRING falls below 0.4V or upon detection of  $175\pm15$  consecutive zeros in the incoming data stream. The zero detection circuit is active only when LCLK clock is applied. In both cases, the receiver reports loss of signal by setting LOS high, and at the same time, RPOS and RNEG are forced to low. Under the loss of signal conditions, the receiver will continue to recover data and will return to its normal operation if a valid data is detected on RTIP and RRING.

#### **TRANSMITTER**

The transmitter is designed to take dual rail NRZ data, plus a synchronized input clock and produces a bipolar signal with the appropriate shape for transmission to the line.

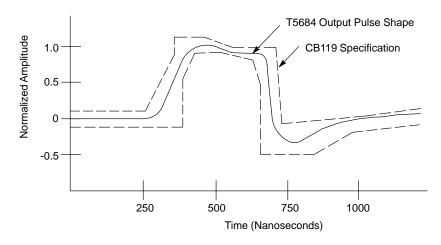

After sampling by the falling edge of TCLK, TPOS and TNEG data are processed by a digital to analog converter together with a slew-control circuit to generate output pulses at TTIP and TRING with the appropriate amplitude and shape to meet the cross-connect template specified in CB 119. A typical output pulse is shown in *Figure 7*. In order to meet the amplitude requirement with a single +5V supply, the transmit signal is driven to the line differentially via a 1:1.36 step-up transformer.

Pulse shaping is selectable through input control pins LEN2, LEN1 and LEN0 for line lengths ranging from 0 to 655 feet of ABAM cable as illustrated in *Table 1*.

| LEN2 | LEN1 | LEN0 | Line Length Selected (ft.) |

|------|------|------|----------------------------|

| 0    | 1    | 1    | 0 - 133                    |

| 1    | 0    | 0    | 133 - 266                  |

| 1    | 0    | 1    | 266 - 399                  |

| 1    | 1    | 0    | 399 - 533                  |

| 1    | 1    | 1    | 533 - 655                  |

Table 1. ABAM or ALVYN Cable Type Line Length Selection

The transmitter can be set to transmit a continuous AMI encoded all ones signal to the line by forcing TAOS high. In this mode, input data TPOS and TNEG are ignored and the frequency of the transmitted signal is determined by TCLK.

With TTIP connected to MTIP and TRING connected to MRING, the driver monitor can detect a non-functional T1 transmitter by monitoring the activity at its input. If no signal is presented on MTIP and MRING for 63 TCLK clock cycles, DPM goes high until the next AMI signal is detected.

Figure 7. Receiver Clock and Data Switching Characteristics

Figure 1. Application Schematic Diagram

Figure 2. Receiver Clock and Data Switching Characteristics

Figure 3. Receiver Clock and Data Switching Characteristics

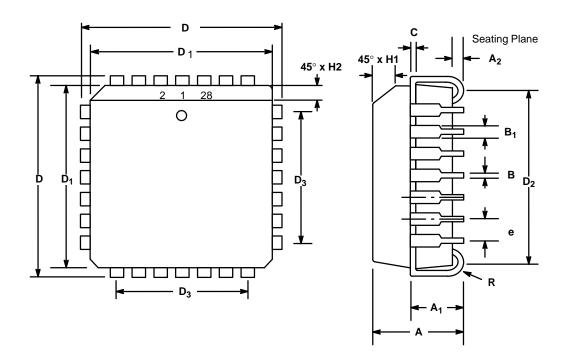

## 28 LEAD PLASTIC LEADED CHIP CARRIER (PLCC)

Rev. 1.00

|                | INC   | CHES    | MILLI | MILLIMETERS |  |  |

|----------------|-------|---------|-------|-------------|--|--|

| SYMBOL         | MIN   | MAX     | MIN   | MAX         |  |  |

| Α              | 0.165 | 0.180   | 4.19  | 4.57        |  |  |

| A <sub>1</sub> | 0.090 | 0.120   | 2.29  | 3.05        |  |  |

| A <sub>2</sub> | 0.020 | —.      | 0.51  |             |  |  |

| В              | 0.013 | 0.021   | 0.33  | 0.53        |  |  |

| B <sub>1</sub> | 0.026 | 0.032   | 0.66  | 0.81        |  |  |

| С              | 0.008 | 0.013   | 0.19  | 0.32        |  |  |

| D              | 0.485 | 0.495   | 12.32 | 12.57       |  |  |

| D <sub>1</sub> | 0.450 | 0.456   | 11.43 | 11.58       |  |  |

| D <sub>2</sub> | 0.390 | 0.430   | 9.91  | 10.92       |  |  |

| D <sub>3</sub> | 0.3   | 00 typ. | 7.6   | 2 typ.      |  |  |

| е              | 0.0   | 50 BSC  | 1.2   | 7 BSC       |  |  |

| H1             | 0.042 | 0.056   | 1.07  | 1.42        |  |  |

| H2             | 0.042 | 0.048   | 1.07  | 1.22        |  |  |

| R              | 0.025 | 0.045   | 0.64  | 1.14        |  |  |

Note: The control dimension is the inch column

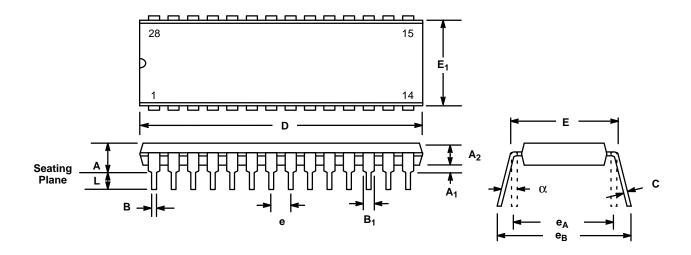

# 28 LEAD PLASTIC DUAL-IN-LINE (600 MIL PDIP)

Rev. 1.00

|                | INC   | HES    | MILLIN | METERS |

|----------------|-------|--------|--------|--------|

| SYMBOL         | MIN   | MAX    | MIN    | MAX    |

| Α              | 0.160 | 0.250  | 4.06   | 6.35   |

| A <sub>1</sub> | 0.015 | 0.070  | 0.38   | 1.78   |

| A <sub>2</sub> | 0.125 | 0.195  | 3.18   | 4.95   |

| В              | 0.014 | 0.024  | 0.36   | 0.56   |

| B <sub>1</sub> | 0.030 | 0.070  | 0.76   | 1.78   |

| С              | 0.008 | 0.014  | 0.20   | 0.38   |

| D              | 1.380 | 1.565  | 35.05  | 39.75  |

| Е              | 0.600 | 0.625  | 15.24  | 15.88  |

| E <sub>1</sub> | 0.485 | 0.580  | 12.32  | 14.73  |

| е              | 0.10  | 0 BSC  | 2.5    | 4 BSC  |

| e <sub>A</sub> | 0.60  | 00 BSC | 15.2   | 24 BSC |

| e <sub>B</sub> | 0.600 | 0.700  | 15.24  | 17.78  |

| L              | 0.115 | 0.200  | 2.92   | 5.08   |

| α              | 0°    | 15°    | 0°     | 15°    |

Note: The control dimension is the inch column

### **Notes**

#### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1997 EXAR Corporation Datasheet June 1997

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.