#### FOUR CHANNEL, DS3 ATM UNI/CLEAR-CHANNEL FRAMER

DECEMBER 2000 REV. P1.0.0

#### **GENERAL DESCRIPTION**

The XRT72L74 Four Channel DS3 ATM User Network Interface (UNI)/Clear Channel Framer is designed to function as either a DS3 ATM UNI or Clear channel framer. For ATM UNI applications, this device provides the ATM Physical Layer (Physical Medium Dependent and Transmission Convergence sublayers) interface for both the public and private networks at DS3 rates. For Clear-Channel framer applications, this device supports the transmission and reception of "user data" via the DS3 payload bits.

The XRT72L74 incorporates Receive, Transmit, Microprocessor Interface, Performance Monitor, Test and Diagnostic and Line Interface Unit Scan Drive sections.

#### **APPLICATIONS**

- Private User Network Interfaces

- ATM Switches

- ATM Concentrators

- DSLAM Equipment

- DS3 Frame Relay Equipment

#### **FEATURES**

- Compliant with UTOPIA Level 1 and 2 with 8 or 16 Bit Interface Specification and supports UTOPIA Bus speeds of up to 50 MHz

- Contains on-chip 16 cell FIFO in both the Transmit (TxFIFO) and Receive Directions (RxFIFO)

- Contains on-chip 54 byte Transmit OAM Cell buffer and a 108 byte Receive OAM cell buffer, for transmission, reception and processing of OAM cells.

- Supports PLCP or ATM Direct Mapping modes

- · Supports M13 and C-Bit Parity Framing Formats

- Supports DS3 Clear Channel Framing Applications

- · Includes PRBS Generator and Receiver

- Supports Local, Remote-Line, Cell, and PLCP Loop-backs

- Interfaces to 8 or 16 Bit wide Motorola and Intel μPs

- Low power 3.3V, 5V input tolerant, CMOS

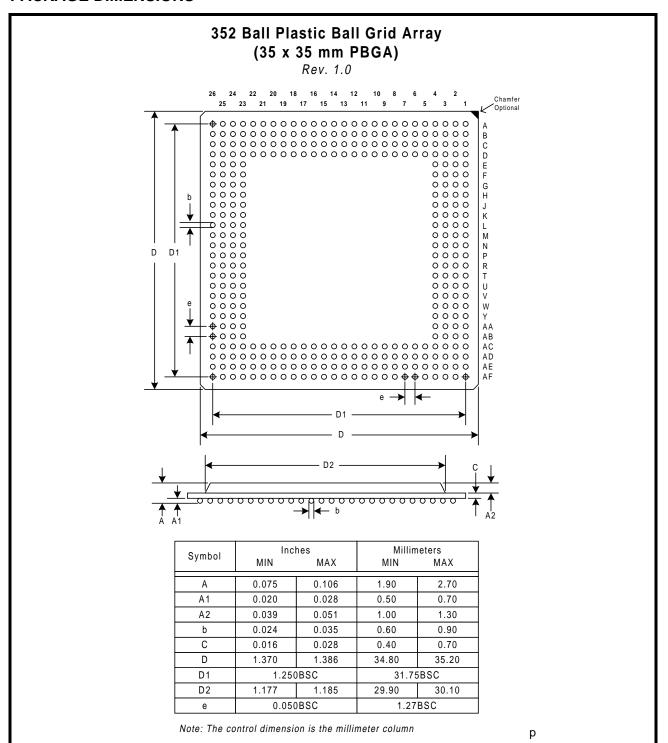

- 352 pin PBGA Package

- 1 and 3 channel versions also available

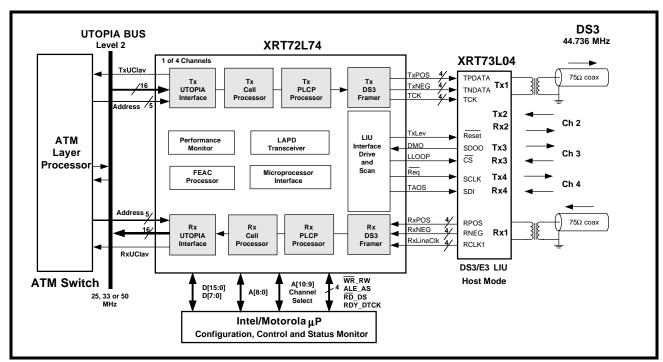

FIGURE 1. XRT72L74 SIMPLIFIED BLOCK DIAGRAM WITH SYSTEM INTERFACES

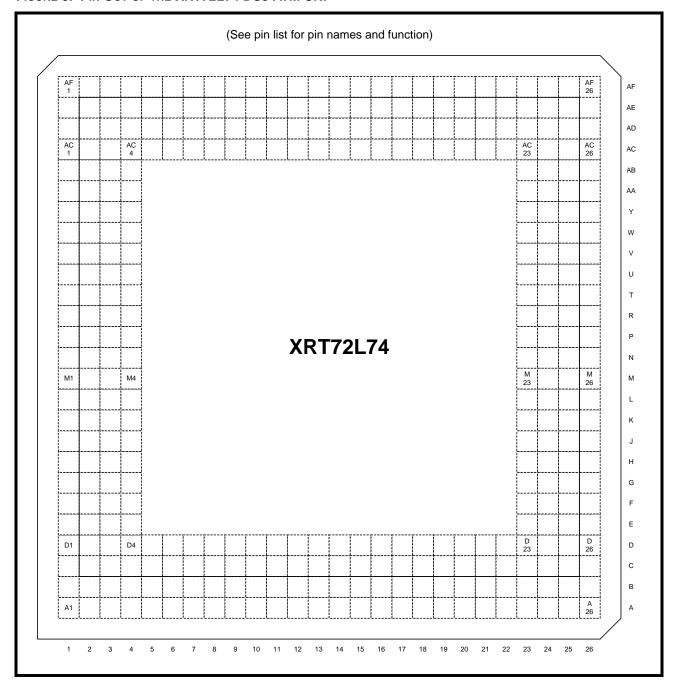

FIGURE 2. BLOCK DIAGRAM OF THE XRT72L74 DS3 UNI

#### SYSTEM/FUNCTIONAL DESCRIPTION

The XRT72L74 has 4 identical channels (0, 1, 2, 3), the descriptions below apply to each channel.

#### **FUNCTIONAL DESCRIPTION**

The XRT72L74 DS3 ATM UNI/Framer IC can be configured to operate in either the "ATM UNI" or in the "Clear-Channel-Framer" Mode.

A brief listing of the features and description for each of these operating modes is presented below.

#### THE ATM UNI MODE OF OPERATION

When the XRT72L74 UNI/Framer has been configured to operate in the "ATM UNI" Mode, it can functionally be subdivided into 6 different sections, as shown in Figure 2.

- Receive Section

- Transmit Section

- Microprocessor Interface Section

- Performance Monitor Section

- Test and Diagnostic Section

- · Line Interface Unit Scan Drive Section

The features of each of these functional sections are briefly outlined below.

#### THE RECEIVE SECTION

The purpose of the Receive Section of the XRT72L74 DS3 ATM UNI is to allow a local ATM Layer (or ATM Adaptation Layer) processor to receive ATM cell data from a remote piece of equipment via a public or leased DS3 transport medium.

The Receive Section of the XRT72L74 DS3 UNI consists of the following functional blocks.

- Receive DS3 Framer Block

- Receive PLCP (Physical Layer Convergence Protocol) Processor Block

- Receive Cell Processor Block

- Receive UTOPIA Interface Block

Each of these functional blocks, within the Receive Section of the UNI Framer will do the following:

#### The Rx DS3 Framer Block

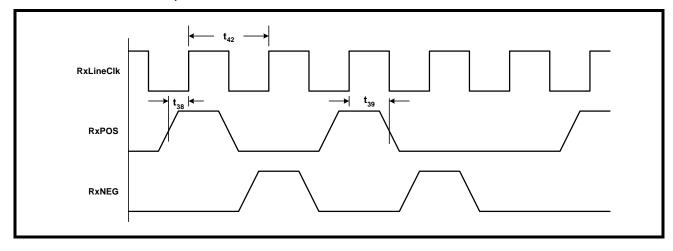

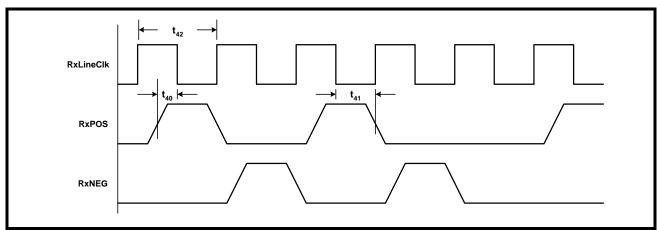

- Capable of receiving data, from the LIU IC, in either the "Single-Rail" or "Dual-Rail" mode.

- Capable of "sampling" the "inbound" DS3 data (at the "RxPOS" and "RxNEG" input pins) upon either the rising or falling edge of the "RxLineClk" signal.

- The Receive DS3 Framer will synchronize to the incoming DS3 data stream and remove or process the DS3 Framing/Overhead Bits. This procedure will result in either extracting PLCP frame data or "Direct-Mapped" ATM Cell data, from the payload portion of the incoming DS3 data stream.

- The Receive DS3 Framer can be used to receive FEAC (Far End Alarm & Control) messages via an on-chip FEAC Transceiver.

- The Receive DS3 Framer includes an on-chip LAPD Receiver along with 88 bytes of on-chip RAM that can receive incoming path maintenance data link messages from the Remote Terminal Equipment.

- Detects and generates interrupts upon "Detection of P and CP-bit Errors", "Change of State in LOS, AIS, OOF and FERF", "Receipt of New LAPD (PMDL) Message", "Validation and Removal of FEAC Message".

**Note:** The Receive DS3 Framer supports both M13 and C-bit Parity Frame Formats.

#### The Rx PLCP Processor Block

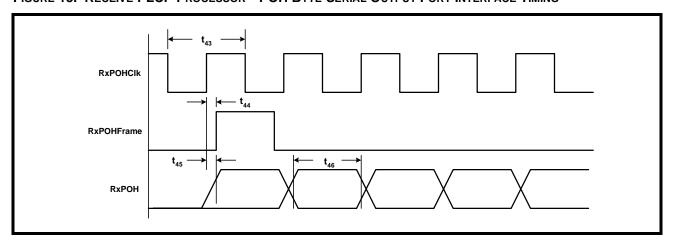

• The Receive PLCP Processor will identify the frame boundary of each incoming PLCP frame, extract and process the overhead bytes of these PLCP frames (applies only if the UNI is operating in the PLCP Mode). The Receive PLCP Processor will also perform some error checking on the incoming PLCP frames. The Receive PLCP Processor will inform the Remote Terminal Equipment of the results of this error-checking by internally routing these results to the "Near-End" Transmit PLCP Processor, for transmission back out to the RemoteTerminal Equipment.

#### The Rx Cell Processor Block

- The Receive Cell Processor will perform the following functions:

- Cell Delineation

- HEC Byte Verification of incoming cells (optional)

- Cell-payload de-scrambling (optional)

- Idle cell detection and removal (optional)

- User and OAM Cell Filtering (optional)

- OAM Cell Processing (optional)

- The UNI provides 108 bytes of on-chip RAM that allows for the reception and processing of selected OAM cells.

- The Receive Cell Processor block will also verify the CRC-10 value within all received OAM cells, per ITU-T I.610.

- Detects and generates interrupts upon "Detection of HEC Byte errors", "Change in LCD (Loss of Cell Delineation) condition" and "Receipt of OAM Cell".

#### The Receive UTOPIA Interface Block

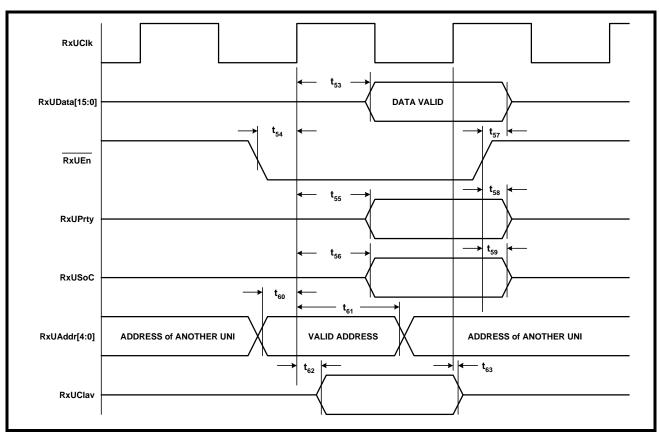

- Provides a "UTOPIA Level -2" compliant interface to either the ATM or the ATM Adaptation Layer.

- Can be configured to operate in either the "Single-PHY" or "Multi-PHY" Modes.

- Supports either "Cell-Level" or "Octet-Level" Handshaking.

- Receive UTOPIA Data Bus can be configured to be either 8 or 16-bits wide.

- The RxFIFO, within the Receive UTOPIA Interface block will temporarily hold any ATM cells that pass through the Receive Cell Processor, where they can be read out by the ATM Layer processor, over the Receive UTOPIA Data Bus.

- The size of the "RxFIFO" is 16 cells.

- Supports read operations (from the ATM Layer device) at rates upto 50MHz.

- Detects and generates interrupts upon "Detection of RUNT cells" and "Overrun of RxFIFO".

#### THE TRANSMIT SECTION

The purpose of the Transmit section of the XRT72L74 DS3 ATM UNI is to allow a local ATM Layer (or ATM Adaptation Layer) processor to transmit ATM Cell data to a remote piece of equipment via a public or leased DS3 transport medium.

The Transmit Section of the XRT72L74 DS3 UNI consists of the following functional blocks.

- Transmit UTOPIA Interface Block

- Transmit Cell Processor Block

- Transmit PLCP Processor Block

- Transmit DS3 Framer Block

Each of these functional blocks, within the Transmit Section (of the UNI/Framer) will do the following:

#### **Transmit UTOPIA Interface Block**

Can be configured to operate in either the "Single-PHY" or Multi-PHY" Mode.

- Supports either the "Cell-Level" or "Octet-Level" Handshaking Mode.

- Transmit UTOPIA Data Bus can be configured to be either 8 or 16-bits wide.

- Allow the ATM Layer processor to write ATM cells into the Transmit FIFO (within the Transmit UTOPIA Interface block) via a standard UTOPIA Level 2 interface.

- The size of the "TxFIFO" is 16 cells. However, the operating depth can be configured to be 4, 8, 12 or 16 cells.

- Supports write operations (from the ATM Layer device) at rates upto 50MHz.

- Detects and generates interrupts upon "Detection of Parity Errors", "Detection of RUNT cells" and "Overrun of TxFIFO".

#### **Transmit Cell Processor Block**

- The Transmit Cell Processor will read in ATM cells from the Transmit FIFO (if available) for further processing.

- If no cell is available within the Transmit FIFO, then

the Transmit Cell Processor will automatically generate an Idle cell. The UNI is equipped with on-chip

registers to allow for the generation of customized

Idle cells.

- The UNI provides 54 bytes of on-chip RAM that allows for the generation and transmission of "userspecified" OAM cells. The Transmit Cell Processor will generate and transmit these OAM cells upon software command.

- The Transmit Cell Processor block will also compute and insert a CRC-10 value into each "outbound" OAM cell, per ITU-T I.610.

- The Transmit Cell Processor will (optionally) scramble the Cell Payload bytes and (optionally) compute and insert the HEC (Header Error Check) byte. This HEC byte will be inserted into the fifth octet of each cell prior to being transferred to the Transmit PLCP Processor (or the Transmit DS3 Framer).

#### **Transmit PLCP Processor Block**

• The Transmit PLCP Processor will pack 12 ATM cells into each PLCP frame and automatically determine the nibble-stuffing option of the current PLCP frame. These PLCP frames will also include an overhead byte that reflect BIP-8 (Bit Interleaved Parity) calculation results, a byte that reflects the current stuffing option status of the current PLCP frame, Path Overhead and Identifier bytes, and diagnostic-related bytes reflecting any detected BIP-8 errors and alarm conditions detected in the Receive section of the UNI chip.

#### **Transmit DS3 Framer Block**

- These PLCP frames (or "Direct Mapped" ATM cells) will be inserted into the payload of an outgoing DS3 frame, for transmission to the "Remote" Terminal, by the Transmit DS3 Framer.

- The Transmit DS3 Framer will transmit FEAC (Far End Alarm & Control) messages to the Remote Terminal Equipment via an on-chip FEAC Transceiver.

- Additionally, the Transmit DS3 Framer can transmit path maintenance data link messages to the Remote Terminal Equipment via the on-chip LAPD Transmitter.

- Generates interrupts upon "Completion of Transmission of LAPD and FEAC" Messages.

Note: The Transmit DS3 Framer will support either M13 or C-bit Parity Framing Formats.

#### CLEAR-CHANNEL-FRAMING MODE OF OPERA-TION

When the XRT72L74 has been configured to operate in the "Clear-Channel Framer" mode, it can be functionally subdivided into 6 different sections.

- · Receive Section

- Transmit Section

- Microprocessor Interface Section

- Performance Monitor Section

- · Test and Diagnostic Section

- Line Interface Unit Scan/Drive Section.

The features of each of the "Receive" and "Transmit" Section (for Clear-Channel Framer applications) are listed below.

#### THE RECEIVE SECTION

The purpose of the Receive Section of the XRT72L74 Clear-Channel DS3 Framer is to allow a given Terminal to receive data from a remote terminal, which is being transported over a DS3 data stream.

The Receive Section of the XRT72L74 Clear-Channel DS3 Framer IC consists of the following functional blocks.

- Receive DS3 Framer block

- Receive Overhead Data Output Interface block

- Receive Payload Data Output Interface block

It should be noted that the "Receive DS3 Framer" block is also active, when the XRT72L74 has been configured to operate in the "ATM UNI" Mode.

Each of these functional blocks, within the Receive Section of the Framer will do the following.

- The Receive DS3 Framer block will synchronize to the incoming DS3 data stream. All "inbound" DS3 data will be routed to the "Receive Payload Data Output Interface" block. All overhead bits (which are extracted from each "inbound" DS3 frame) will be routed to the "Receive Overhead Data Output Interface" block.

- The Receive DS3 Framer block can also be used to receive FEAC (Far-End-Alarm & Control) messages and PMDL (Path Maintenance Data Link) messages via the "on-chip" Receive HDLC Controller block.

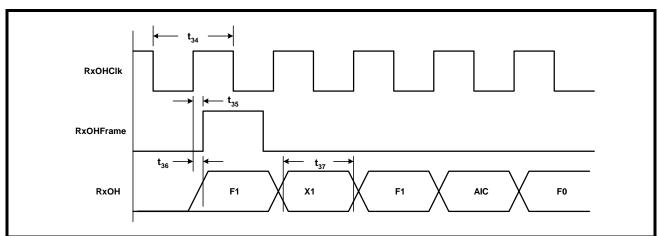

- The Receive Overhead Output Interface block outputs all overhead bits, which have been received via the "inbound" DS3 data stream. The purpose of the "Receive Overhead Output Interface" block is to permit external circuitry (within the local terminal equipment) to have access to these overhead bits, for additional processing.

- The Receive Payload Data Output Interface block outputs all data bits which have been received via the XRT72L74 device, to the local terminal equipment. Since the "Receive Payload Data Output Interface" block outputs both "payload" and "overhead" data bits, to the local terminal equipment; the "Receive Payload Data Output Interface" block also includes an "Overhead Indicator" output pin. This output pin pulses "High" whenever an overhead bit is being output via the "Receive Payload Data Output Interface" block.

#### THE TRANSMIT SECTION

The purpose of the Transmit Section of the XRT72L74 Clear-Channel DS3 Framer is to allow a local terminal to transmit data to a remote terminal equipment, via a DS3 transport medium.

The Transmit Section of the XRT72L74 Clear-Channel DS3 Framer consists of the following functional blocks.

- Transmit Payload Data Input Interface block

- Transmit Overhead Data Input Interface block

- Transmit DS3 Framer block

It should be noted that the "Transmit DS3 Framer" block is also active, whenever the XRT72L74 has been configured to operate in the "ATM UNI" Mode.

The Transmit Section of the Clear-Channel DS3 Framer will:

Accept all "user" data, (which is required to be transported to the Remote Terminal Equipment via

a DS3 data stream) via the "Transmit Payload Data Input Interface block.

- Optionally accepts and insert overhead bits (into the "outbound" DS3 data-stream) via the "Transmit Overhead Input Interface block.

- The Transmit DS3 Framer block will accept payload data (from the Transmit Payload Data Input Interface block) and overhead data (from the Transmit Overhead Data Input Interface block) and will create a DS3 data stream. If no overhead data is inserted via the "Transmit Overhead Data Input interface" block, then the "Transmit DS3 Framer" block will insert its own values for the overhead bits.

- The Transmit DS3 Framer block will transmit FEAC (Far-End-Alarm & Control) messages to the remote terminal equipment via an "on-chip" FEAC Transmitter.

- The Transmit DS3 Framer block will also transmit PMDL (Path Maintenance Data Link) Messages to the remote terminal equipment via an "on-chip" LAPD Transmitter.

#### THE MICROPROCESSOR INTERFACE SECTION

The Microprocessor Interface Section allows a user (or a local "housekeeping" processor) to do the following:

- To configure the UNI/Framer IC into a wide variety of operating modes; by writing data into any one of a large number of "read/write" registers.

- To monitor many aspects of the UNI/Framer's performance by reading data from any one of a large number of "read/write" and "read-only" registers.

- To run in a "polling" or "interrupt-driven" environment.

The UNI/Framer IC contains an extensive interrupt

structure consisting of a wide range of interrupt

enable and interrupt status registers.

- To command the UNI/Framer IC to transmit OAM cells, FEAC messages and/or LAPD Messages frames, upon software command.

- To read in and process received OAM cells, FEAC messages and/or Path Maintenance Data Link Messages from the UNI/Framer IC.

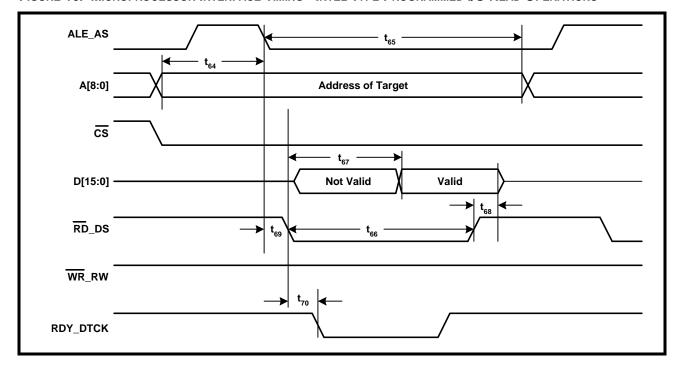

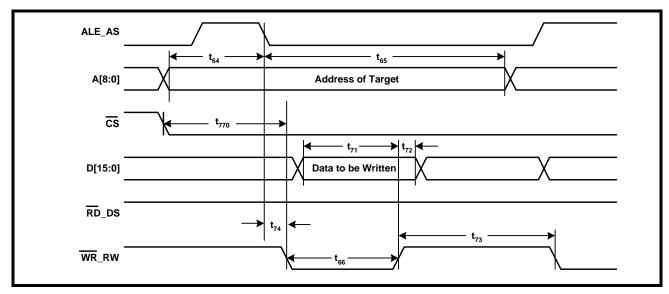

- The Microprocessor Interface allows the user to interface the XRT72L74 DS3 UNI/Framer to either an Intel type or Motorola type processor. Additionally, the Microprocessor Interface can be configured to operate over an 8-bit or 16-bit data bus.

- The Microprocessor Interface section includes a "Loss of Clock Signal" protection feature that automatically completes (or terminates) a "Read/Write" operation, should a "Loss of Clock Signal" event occur.

#### PERFORMANCE MONITOR SECTION

The Performance Monitor Section of the XRT72L74 DS3 UNI/Framer consists of a large number of "Reset-upon-Read" and "Read-Only" registers that contains cumulative and "one-second" statistics that reflect the performance/health of the UNI/Framer chip/system. These cumulative and "one-second" statistics are kept on the following parameters.

- Number of Line Code Violation events detected by the Receive DS3 Framer

- Number of Framing Bit (F- and M-bit) errors detected by the Receive DS3 Framer

- Number of P-bit Errors detected by the Receive DS3 Framer

- Number of CP-bit Errors detected by the Receive DS3 Framer.

- Number of FEBE Events detected by the Receive DS3 Framer

- Cumulative number of BIP-8 errors, detected by the Receive PLCP Processor

- Number of PLCP framing errors, detected by the Receive PLCP Processor

- Cumulative sum of the FEBE value, in the incoming G1 bytes (within each PLCP frame), received by the Receive PLCP Processor

- Number of Single-bit HEC byte Errors detected

- Number of Multi-bit HEC byte Errors detected

- Number of Received Idle Cells

- Number of Received Valid (User and OAM) cells discarded

- Number of Discarded Cells

- · Number of Transmitted Idle Cells

- · Number of Transmitted Valid Cells

#### **TEST AND DIAGNOSTIC SECTION**

The Test and Diagnostic Section allows the user to perform a series of tests in order to verify proper functionality of the UNI/Framer chip and/or the user's system. The "Test and Diagnostic" section provides the UNI IC with the following capabilities.

Allows the UNI/Framer to operate in the Line, Cell, and PLCP Loop-back Modes.

#### FOR ATM UNI APPLICATIONS

Contains an internal Test Cell Generator and an internal Test Cell Receiver. The Test Cell Generator will generate Test Cells with "user-defined" header byte patterns. The Test Cell Generator will also fill the payload portion of these test cells with bytes from an on-chip PRBS generator.

- The Test Cell Generator can generate test cells in "One Shot" Mode (e.g., a burst of 1024 test cells) or in "Continuous" Mode (e.g., a continuous stream of test cells).

- The Test Cell Receiver will identify and collect the Test Cells for further analyses, based upon the "user-defined" header byte patterns. Additionally, the Test Cell Receiver will report the occurrence of any errors by incrementing an on-chip register.

## FOR CLEAR-CHANNEL FRAMING APPLICATIONS

- Contains an internal PRBS pattern generator and receiver. The PRBS pattern generator will generate and insert a PRBS pattern into the DS3 payload bits.

- The PRBS receiver will receive these DS3 frames, and will attempt to acquire "PRBS Lock" with this DS3 frame data. Additionally, the PRBS Receiver

will report the occurrence of any errors by incrementing an on-chip register.

#### LINE INTERFACE DRIVE AND SCAN SECTION

The Line Interface Drive and Scan Section allows the user to monitor and control many aspects of the XRT73L04 E3/DS3/STS-1 Line Interface Unit, via onchip registers, within the UNI IC. This feature eliminates the need for glue logic to interface the XRT72L74 DS3 UNI/Framer to the XRT73L04 DS3 Line Interface Unit IC.

The On-Chip Line Interface Drive register allows the user to control the state of 6 output pins. The function of these output pins, when asserted, are tabulated below.

#### **CLEAR CHANNEL MODE OPERATION**

| Signal Name | Function of Output Pin                                                                                                                                                                                                                                                                                          |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | Receive Equalizer By-Pass:                                                                                                                                                                                                                                                                                      |  |

| Req         | "1" configures the XRT73L04 to shut off its internal Receive Equalizer.                                                                                                                                                                                                                                         |  |

|             | "0" configures the XRT73L04 to enable its internal Receive Equalizer.                                                                                                                                                                                                                                           |  |

|             | Transmit "All Ones" Pattern.                                                                                                                                                                                                                                                                                    |  |

| TAOS        | "1" configures the XRT73L04 LIU IC to overwrite the DS3 data that is output via the TxPOS and TxNEG outputs, and transmit an "All Ones" pattern onto the line.                                                                                                                                                  |  |

|             | "0" configures the XRT73L04 LIU IC to transmit data, as is applied to it via the TPDATA and TNDATA input pins.                                                                                                                                                                                                  |  |

|             | B3ZS Encoder Disable/Enable Select.                                                                                                                                                                                                                                                                             |  |

| EncoDis     | "1" disables the B3ZS Encoder, within the XRT73L04.                                                                                                                                                                                                                                                             |  |

|             | "0" enables the B3ZS Decoder within the XRT73L04.                                                                                                                                                                                                                                                               |  |

|             | Transmit Output Signal Line Build Out Select.                                                                                                                                                                                                                                                                   |  |

|             | Setting this bit-field to "1" disables the Transmit Line Build Out circuitry within the XRT73L04. In this case, the XRT73L04 will generate an "unshaped" square wave signal out onto the line (via the TTIP and TRING output pins).                                                                             |  |

| TxLev       | Note: In order to configure the XRT73L04 to generate a line signal that complies with the Transmit Output Pulse Template Requirements (per Bellcore GR-499-CORE), this setting is advised if the cable length between the Transmit Output of the XRT73L04 and the DSX-3 Cross-Connect is greater than 225 feet. |  |

|             | Setting this bit-field to "0" enables the Transmit Line Build Out circuitry within the XRT73L04. In this case, the XRT73L04 will generate a "shaped" square wave out onto the line (via the TTIP and TRING output pins).                                                                                        |  |

|             | Note: In order to configure the XRT73L04 to generate a line signal that complies with the Transmit Output Pulse Template Requirements (per Bellcore GR-499-CORE), this setting is advised if the cable length between the Transmit Output of the XRT73L04 and the DSX-3 Cross-Connect is less than 225 feet.    |  |

| Signal Name | Function of Output Pin                                                                                             |  |

|-------------|--------------------------------------------------------------------------------------------------------------------|--|

|             | Remote Loop-Back Mode Select:                                                                                      |  |

|             | This bit-field, along with LLOOP can be used to configure the XRT73L04 into one of four different Loop-Back modes. |  |

|             | Setting RLOOP to "1" (with LLOOP = 0) configures the XRT73L04 to operate in the Remote Loop-Back Mode.             |  |

| RLOOP       | Setting RLOOP to "1" (with LLOOP = 1) configures the XRT73L04 to operate in the "Digital Local Loop-Back" Mode.    |  |

|             | Setting RLOOP to "0" (with LLOOP = 1) configures the XRT73L04 to operate in the "Analog Local Loop-Back" Mode.     |  |

|             | Setting RLOOP to "0" (with LLOOP = 0) configures the XRT73L04 to operate in the "Normal" (No-Loop-Back) Mode.      |  |

|             | Local Loop-Back Mode Select:                                                                                       |  |

|             | This bit-field along with RLOOP can be used to configure the XRT73L04 into one of four different Loop-Back modes.  |  |

|             | Setting LLOOP to "1" (with RLOOP = 0) configures the XRT73L04 to operate in the "Analog Local Loop-Back" Mode.     |  |

| LLOOP       | Setting LLOOP to "1" (with RLOOP = 1) configures the XRT73L04 to operate in the "Digital Local Loop-Back" Mode.    |  |

|             | Setting LLOOP to "0" (with RLOOP = 0) configures the XRT73L04 to operate in the "Normal" (No-Loop-Back) Mode.      |  |

|             | Setting LLOOP to "0" (with RLOOP = 1) configures the XRT73L04 to operate in the "Remote Loop-Back" Mode.           |  |

• The On-Chip Line Interface Scan Register allows the user to monitor the state of 3 input pins. The

function of these input pins, when asserted, are tabulated below.

| SIGNAL NAME | FUNCTION OF INPUT PIN IF ASSERTED                                                                                                           |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| DMO         | Indicates that the "Drive Monitor" circuitry within the XRT73L04 has not detected any bipolar signals within the last 128 ± 32 bit periods. |  |

| RLOL        | Indicates that the "Clock Recovery" circuit, within the XRT73L04 has lost "lock" with the incoming DS3 line signal.                         |  |

| RLOS        | Indicates that the XRT73L04 is declaring an LOS (Loss of Signal) Condition.                                                                 |  |

#### **FEATURES**

#### TRANSMIT AND RECEIVE SECTIONS

#### UTOPIA INTERFACE BLOCKS

- Compliant with UTOPIA Level 2 Interface Specification (e.g., supports Single-PHY or Multi-PHY operation).

- 8-bit or 16-bit wide UTOPIA Data Bus operation in the Transmit and Receive Directions.

- The UTOPIA Data Bus runs at clock rates of 25 MHz, 33 MHz and 50 MHz

- Supports both Octet-Level and Cell-Level Handshaking between the UNI and the ATM Layer processor.

- The Transmit UTOPIA Interface block performs parity checking of ATM cell data that is written into it, by the ATM Layer processor. Will optionally discard errored cells.

- Contains on-chip 16 cell FIFO in the Transmit Direction (TxFIFO)

- The TxFIFO can be configured to operate with depths of 4, 8, 12 or 16 cells

- Contains on-chip 16 cell FIFO in the Receive Direction (RxFIFO)

#### TRANSMIT CELL PROCESSOR BLOCK

- Optionally computes and inserts HEC byte into all cells (user, OAM and Idle).

- Optionally scrambles the payload of each cell.

- Idle cells are automatically generated when no user cells are available in the TxFIFO.

- UNI contains on-chip registers that support the generation/transmission of default or custom Idle cells.

- UNI contains the on-chip "Transmit OAM Cell" buffer (54 bytes) that allows the user to write in and store the contents of OAM cells, in preparation for transmission.

- OAM cells are transmitted upon software command.

- Performs "Data Path Integrity" check on all incoming cell data, originating from the ATM Layer processor.

- Provides a serial input port to allow the user to insert the GFC (Generic Flow Control) field externally into the GFC nibble field of an outbound (e.g., Transmit direction) valid ATM Cell.

#### RECEIVE CELL PROCESSOR BLOCK

- Performs cell delineation on either "Direct Mapped" ATM cell data or PLCP frames.

- Verifies the HEC bytes of incoming cells and corrects most cells with single bit errors. Cells with multi-bit errors are detected and are optionally discarded.

- (Optionally) Performs filtering of Idle Cells.

- (Optionally) Performs filtering of User and OAM cells.

- UNI contains on-chip buffer space ("Receive OAM Cell" buffer) that allows for the reception and processing of selected OAM cells.

- Optionally de-scrambles the payload of each cell.

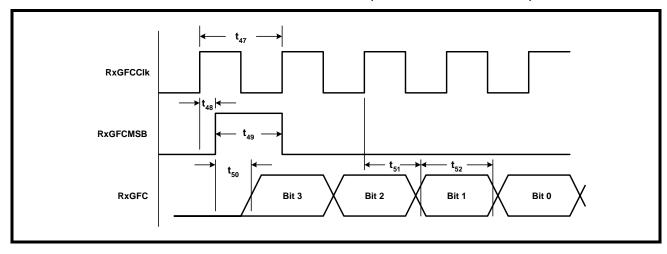

- Provides a serial output port that allows the user to read the GFC value of an incoming (e.g., Receive direction) ATM Cell.

- Inserts the "Data Path Integrity Check" patterns in all cells that are written to the RxFIFO.

#### TRANSMIT PLCP PROCESSOR BLOCK

- Can be disabled to support the "Direct Mapped" ATM mode.

- Packs 12 ATM cells into each PLCP frame along with various other overhead bytes.

- The Transmit PLCP Processor will automatically determine its own stuffing options.

- Overhead bytes include those that support BIP-8 calculations (B1), indicator of stuff-option status for

- current PLCP frame (C1), diagnostic byte that reflects alarms conditions that were detected in the Receive Section of the UNI (G1); and Path Overhead bytes.

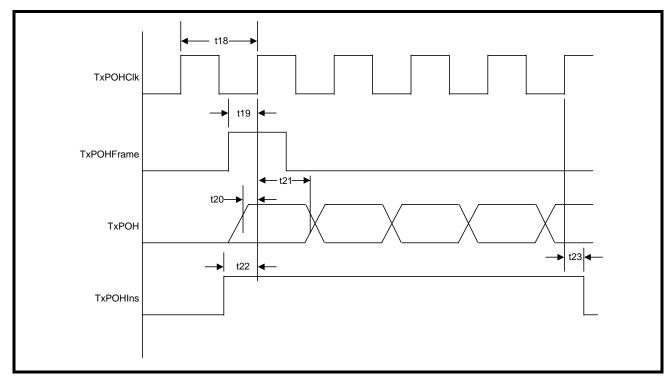

- Provides a serial input port for user to insert PLCP Overhead Bytes externally.

#### RECEIVE PLCP PROCESSOR BLOCK

- Can be disabled to support the "Direct Mapped" ATM mode.

- Determines the frame boundaries of incoming PLCP frames (from the Receive DS3 Framer).

- Extracts and processes the PLCP frame overhead bytes.

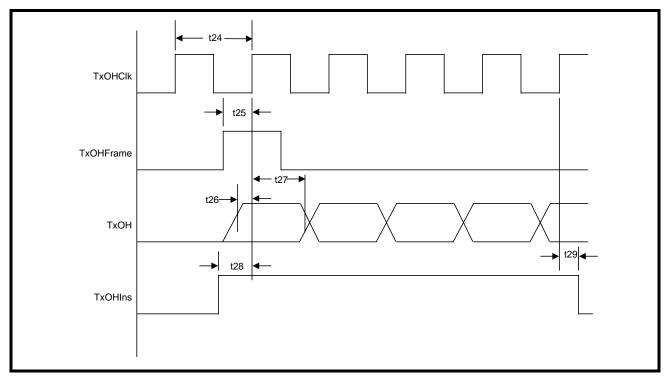

- Provides a serial output port for user to read in the contents of the PLCP Overhead Bytes from the incoming data.

#### TRANSMIT/RECEIVE DS3 FRAMER BLOCK

- Supports the M13 and C-bit Parity Framing Formats.

- Transmit and Receive DS3 Framers can transmit/ receive data in the Unipolar or the Bipolar (AMI or B3ZS line codes) format.

- The Transmit DS3 Framer provides a serial input port that allows the user to insert his/her own values for the overhead bits of the "outbound" DS3 frames.

- The Receive DS3 Framer provides a serial output port that allows the user access to the values of the overhead bits of the "incoming" DS3 frames.

- The Receive DS3 Framer can be configured to sample the incoming DS3 data (at the RxPOS and RxNEG input pins) via the rising edge or falling edge of the Receive Line Clock (RxLineClk) input.

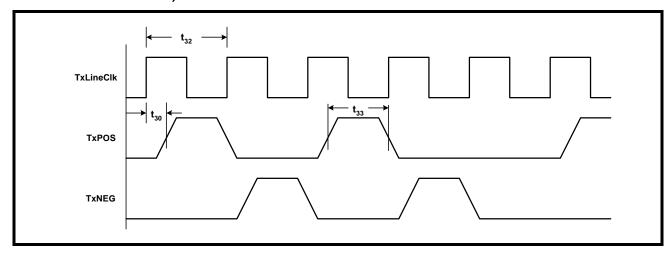

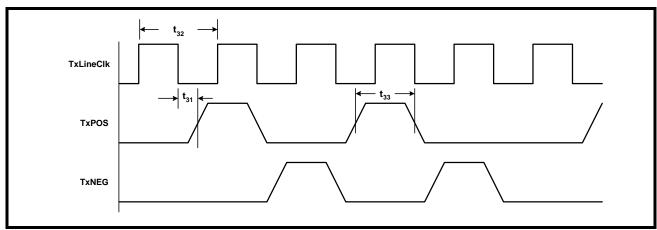

- The Transmit DS3 Framer can be configured to update the "outbound" DS3 data (at the TxPOS and TxNEG output pins) at the rising edge or falling edge of the Transmit Line Clock (TxLineClk) output.

- UNI includes on-chip RAM space to support the transmission and reception of path maintenance data link messages via an on-chip LAPD Transceiver

- UNI includes on-chip registers to support the transmission and reception of FEAC (Far End Alarm & Control) messages via an on-chip FEAC Transceiver.

- Contains on-chip FEAC Transceiver.

- · Contains on-chip LAPD Transceiver.

#### MICROPROCESSOR INTERFACE SECTION

Can be interfaced to Motorola or Intel type of microprocessors/microcontrollers

# XRT72L74 FOUR CHANNEL, DS3 ATM UNI/CLEAR-CHANNEL FRAMER REV. P1.0.0

**PRELIMINARY**

- Microprocessor interface supports 8 bit wide or 16bit wide read/write accesses.

- Supports polled or interrupt-driven environments.

- Supports burst mode "Read and Write" operations between the "local" microprocessor and the UNI onchip registers and RAM locations.

- Includes a "Loss of Clock Signal" protection feature that terminates "Read/Write" cycles with the local μP, during a "Loss of Clock signal" event.

#### PERFORMANCE MONITOR SECTION

Contains numerous on-chip "Read-Only" registers that allows the user to monitor the overall "health" of the system.

#### TEST AND DIAGNOSTIC SECTION

• Supports Line, PLCP, and Cell Loop-back Modes

- · Supports Line-Side Testing

- Contains an on-chip Test Cell Generator and an onchip Test Cell Receiver

- Test Cell Generator can generate a "continuous" stream of test cells, or a "one-shot" burst of 1024 test cells.

- The Test Cell Receiver identifies, collects and evaluates Test Cells for errors.

- The Test Cell Receiver also reports the occurrence of errors to the user.

#### LINE INTERFACE DRIVE AND SCAN SECTION

• Consists of an on-chip "Read/Write" register that allows the user to control the state of 6 output pins.

Consists of an on-chip "Read-Only" register that allows the user to monitor the state of 3 input pins.

FIGURE 3. PIN OUT OF THE XRT72L74 DS3 ATM UNI

## **ORDERING INFORMATION**

| PART NUMBER | PACKAGE                  | OPERATING TEMPERATURE RANGE |

|-------------|--------------------------|-----------------------------|

| XRT72L74IQ  | 35 x 35 mm 352 ball PBGA | -40°C to +85°C              |

## FOUR CHANNEL, DS3 ATM UNI/CLEAR-CHANNEL FRAMER REV. P1.0.0

## **PRELIMINARY**

## LIST BY PIN NUMBER

| LIST BY PIN NUMBER |              |  |

|--------------------|--------------|--|

| Pin                | PIN NAME     |  |

| A1                 | TxOHIns_1    |  |

| A2                 | RxLineClk_0  |  |

| А3                 | TxOHIns_0    |  |

| A4                 | LLOOP_3      |  |

| A5                 | LLOOP_0      |  |

| A6                 | TxOHClk_1    |  |

| A7                 | TxFrameRef_3 |  |

| A8                 | TxFrameRef_0 |  |

| A9                 | EncoDis_1    |  |

| A10                | TxFrame_2    |  |

| A11                | TxFrame_0    |  |

| A12                | TxAISEn_0    |  |

| A13                | DMO_2        |  |

| A14                | RLOOP_2      |  |

| A15                | RLOOP_0      |  |

| A16                | TxLev_1      |  |

| A17                | RxFrame_3    |  |

| A18                | RxFrame_1    |  |

| A19                | Req_2        |  |

| A20                | RxOHFrame_3  |  |

| A21                | TAOS_3       |  |

| A22                | TAOS_0       |  |

| A23                | RxOHClk_1    |  |

| A24                | RxOH_3       |  |

| A25                | RxOH_1       |  |

| A26                | RxRed_3      |  |

| B1                 | TxPOS_0      |  |

| B2                 | TxOHIns_2    |  |

| В3                 | RxPOS_0      |  |

| B4                 | RxNEG_0      |  |

| B5                 | TxOHClk_3    |  |

| В6                 | TxOHClk_0    |  |

| <b>PIN</b> B7 - | PIN NAME     |

|-----------------|--------------|

|                 |              |

| RΩ              | TxFrameRef_2 |

| БО              | EncoDis_3    |

| В9              | EncoDis_0    |

| B10             | TxFrame_1    |

| B11             | TxAISEn_3    |

| B12             | DMO_3        |

| B13             | DMO_1        |

| B14             | RLOOP_1      |

| B15             | TxLev_3      |

| B16             | TxLev_0      |

| B17             | RxFrame_2    |

| B18             | RxFrame_0    |

| B19             | Req_1        |

| B20 F           | RxOHFrame_2  |

| B21             | TAOS_2       |

| B22             | RxOHClk_3    |

| B23             | RxOHClk_0    |

| B24             | TxInClk_3    |

| B25             | RxOH_2       |

| B26             | RxOH_0       |

| C1              | TxOHIns_3    |

| C2              | TxInClk_0    |

| C3              | GND          |

| C4              | LLOOP_2      |

| C5              | TxOHClk_2    |

| C6              | TxPOS_1      |

| C7 -            | TxFrameRef_1 |

| C8              | TxNEG_1      |

| C9              | TxFrame_3    |

| C10             | RxPOS_1      |

| C11             | TxAISEn_2    |

| C12             | RxNEG_1      |

| C13             | DMO_0        |

| PIN | PIN NAME    |

|-----|-------------|

| C14 | TxNEG_2     |

| C15 | TxLev_2     |

| C16 | TxPOS_2     |

| C17 | RxNEG_2     |

| C18 | Req_3       |

| C19 | RxPOS_2     |

| C20 | RxOHFrame_1 |

| C21 | TAOS_1      |

| C22 | RxOHClk_2   |

| C23 | TxNEG_3     |

| C24 | GND         |

| C25 | RxLineClk_3 |

| C26 | RxRed_2     |

| D1  | TxNEG_0     |

| D2  | TxOHFrame_1 |

| D3  | TxOHFrame_0 |

| D4  | GND         |

| D5  | LLOOP_1     |

| D6  | GND         |

| D7  | TxInClk_1   |

| D8  | VDD         |

| D9  | EncoDis_2   |

| D10 | GND         |

| D11 | RxLineClk_1 |

| D12 | TxAISEn_1   |

| D13 | GND         |

| D14 | RLOOP_3     |

| D15 | VDD         |

| D16 | TxInClk_2   |

| D17 | GND         |

| D18 | RxLineClk_2 |

| D19 | VDD         |

| D20 | Req_0       |

| PIN | PIN NAME    |

|-----|-------------|

|     |             |

| D21 | RxOHFrame_0 |

| D22 | TxPOS_3     |

| D23 | GND         |

| D24 | RxPOS_3     |

| D25 | RxRed_1     |

| D26 | RxNEG_3     |

| E1  | TxLineClk_3 |

| E2  | TxOHFrame_3 |

| E3  | TxOHFrame_2 |

| E4  | TxLineClk_0 |

| E23 | RxRed_0     |

| E24 | RxAIS_1     |

| E25 | RxAIS_2     |

| E26 | RxAIS_3     |

| F1  | TxOH_1      |

| F2  | TxLineClk_2 |

| F3  | TxOH_0      |

| F4  | VDD         |

| F23 | GND         |

| F24 | RLOS_2      |

| F25 | RLOS_3      |

| F26 | RxAIS_0     |

| G1  | 8KRef_0     |

| G2  | TxOH_3      |

| G3  | TxOH_2      |

| G4  | TxLineClk_1 |

| G23 | RLOS_1      |

| G24 | RxOOF_2     |

| G25 | RxOOF_3     |

| G26 | RLOS_0      |

| H1  | 8KRef_3     |

| H2  | 8KRef_2     |

| H3  | 8KRef_1     |

|     |             |

**EXAR**

REV. P1.0.0

| PIN | PIN NAME               |

|-----|------------------------|

| H4  | VDD                    |

| H23 | VDD                    |

| H24 | RxLOS_3                |

| H25 | RxOOF_0                |

| H26 | RxOOF_1                |

| J1  | TxOHInd/<br>TxPFrame_2 |

| J2  | TxOHInd/<br>TxPFrame_1 |

| J3  | TxOHInd/<br>TxPFrame_0 |

| J4  | TxOHInd/<br>TxPFrame_3 |

| J23 | RxLOS_2                |

| J24 | RxPRed_3               |

| J25 | RxLOS_0                |

| J26 | RxLOS_1                |

| K1  | StuffCtl_2             |

| K2  | StuffCtl_1             |

| K3  | StuffCtl_0             |

| K4  | GND                    |

| K23 | GND                    |

| K24 | RxPRed_0               |

| K25 | RxPRed_1               |

| K26 | RxPRed_2               |

| L1  | TxPOHFrame_1           |

| L2  | TxPOHFrame_0           |

| L3  | StuffCtl_3             |

| L4  | TxPOHFrame_2           |

| L23 | RxPLOF_3               |

| L24 | RxPLOF_0               |

| L25 | RxPLOF_1               |

| L26 | RxPLOF_2               |

| M1  | TxSerData/<br>TxPOH_1  |

| PIN | PIN NAME                |

|-----|-------------------------|

| M2  | TxSerData/<br>TxPOH_0   |

| МЗ  | TxPOHFrame_3            |

| M4  | VDD                     |

| M23 | RxSerClk/<br>RxPOHClk_3 |

| M24 | RxSerClk/<br>RxPOHClk_0 |

| M25 | RxSerClk/<br>RxPOHClk_1 |

| M26 | RxSerClk/<br>RxPOHClk_2 |

| N1  | TxPOHClk_0              |

| N2  | TxSerData/<br>TxPOH_3   |

| N3  | TxSerData/<br>TxPOH_2   |

| N4  | TxPOHClk_1              |

| N23 | GND                     |

| N24 | RLOL_1                  |

| N25 | RLOL_2                  |

| N26 | RLOL_3                  |

| P1  | TxPOHIns_0              |

| P2  | TxPOHClk_3              |

| P3  | TxPOHClk_2              |

| P4  | GND                     |

| P23 | RLOL_0                  |

| P24 | RxSerData/<br>RxPOH_1   |

| P25 | RxSerData/<br>RxPOH_2   |

| P26 | RxSerData/<br>RxPOH_3   |

| R1  | TxPOHIns_3              |

| R2  | TxPOHIns_2              |

| R3  | TxPOHIns_1              |

| R4  | GPIO_0                  |

| PIN | PIN NAME               |

|-----|------------------------|

|     |                        |

| R23 | VDD                    |

| R24 | RxPOHFrame_2           |

| R25 | RxPOHFrame_3           |

| R26 | RxSerData/<br>RxPOH_0  |

| T1  | GPIO_3                 |

| T2  | GPIO_2                 |

| Т3  | GPIO_1                 |

| T4  | TMS                    |

| T23 | RxPOHFrame_1           |

| T24 | RxOHInd/<br>RxPFrame_2 |

| T25 | RxOHInd/<br>RxPFrame_3 |

| T26 | RxPOHFrame_0           |

| U1  | TDI                    |

| U2  | TCK                    |

| U3  | TRST                   |

| U4  | GND                    |

| U23 | GND                    |

| U24 | RxPOOF_3               |

| U25 | RxOHInd/<br>RxPFrame_0 |

| U26 | RxOHInd/<br>RxPFrame_1 |

| V1  | TestMode               |

| V2  | Reset                  |

| V3  | TDO                    |

| V4  | A10                    |

| V23 | RxPOOF_2               |

| V24 | RxLCD_3                |

| V25 | RxPOOF_0               |

| V26 | RxPOOF_1               |

| W1  | A7                     |

| W2  | A8                     |

| PIN  | PIN NAME   |

|------|------------|

| W3   | A9         |

| W4   | VDD        |

| W23  | VDD        |

| W24  | RxLCD_0    |

| W25  | RxLCD_1    |

| W26  | RxLCD_2    |

| Y1   | A4         |

| Y2   | A5         |

| Y3   | A6         |

| Y4   | D12        |

| Y23  | RxGFCClk_3 |

| Y24  | RxGFCClk_0 |

| Y25  | RxGFCClk_1 |

| Y26  | RxGFCClk_2 |

| AA1  | A2         |

| AA2  | А3         |

| AA3  | D13        |

| AA4  | A1         |

| AA23 | VDD        |

| AA24 | RxUData3   |

| AA25 | RxGFCMSB_2 |

| AA26 | RxGFCMSB_3 |

| AB1  | CS         |

| AB2  | D11        |

| AB3  | A0         |

| AB4  | D8         |

| AB23 | RxUData7   |

| AB24 | RxGFCMSB_0 |

| AB25 | RxUData2   |

| AB26 | RxGFCMSB_1 |

| AC1  | D14        |

| AC2  | WR_RW      |

| AC3  | D9         |

## FOUR CHANNEL, DS3 ATM UNI/CLEAR-CHANNEL FRAMER

REV. P1.0.0

## PRELIMINARY

|      | PIN NAME     |

|------|--------------|

| AC4  | GND          |

| AC5  | D4           |

| AC6  | TxGFCClk_3   |

| AC7  | D0           |

| AC8  | VDD          |

| AC9  | TxUSoC       |

| AC10 | GND          |

| AC11 | TxUAddr0     |

| AC12 | TxUData12    |

| AC13 | GND          |

| AC14 | TxUData6     |

| AC15 | VDD          |

| AC16 | TxCellTxed_0 |

| AC17 | GND          |

| AC18 | RxUEn        |

| AC19 | VDD          |

| AC20 | RxUAddr3     |

| AC21 | GND          |

| AC22 | RxUData12    |

| AC23 | GND          |

| AC24 | RxUData6     |

| AC25 | RxGFC_3      |

| AC26 | RxUData1     |

| AD1  | RDY_DTCK     |

| AD2  | D10          |

| AD3  | GND          |

| AD4  | D5           |

| AD5  | Width16      |

| AD6  | D1           |

| AD7  | TxGFC_0      |

| AD8  | TxUClav      |

| AD9  | TxUEn        |

| AD10 | TxUClk       |

| Pin  | PIN NAME     |  |  |  |

|------|--------------|--|--|--|

| AD11 | TxUAddr3     |  |  |  |

| AD12 | TxUData15    |  |  |  |

| AD13 | TxUData11    |  |  |  |

| AD14 | TxUData8     |  |  |  |

| AD15 | TxUData5     |  |  |  |

| AD16 | TxUData2     |  |  |  |

| AD17 | RxClk        |  |  |  |

| AD18 | RxUSoC       |  |  |  |

| AD19 | RxCellRxed_0 |  |  |  |

| AD20 | RxCellRxed_3 |  |  |  |

| AD21 | RxUData15    |  |  |  |

| AD22 | RxUAddr0     |  |  |  |

| AD23 | RxUData9     |  |  |  |

| AD24 | GND          |  |  |  |

| AD25 | RxUData5     |  |  |  |

| AD26 | RxGFC_2      |  |  |  |

| AE1  | D15          |  |  |  |

| AE2  | ALE_AS       |  |  |  |

| AE3  | D6           |  |  |  |

| AE4  | Int          |  |  |  |

| AE5  | D2           |  |  |  |

| AE6  | TxGFCClk_1   |  |  |  |

| AE7  | TxGFC_1      |  |  |  |

| AE8  | TxGFC_3      |  |  |  |

| AE9  | TxGFCMSB_1   |  |  |  |

| AE10 | TxGFCMSB_3   |  |  |  |

| AE11 | TxUAddr2     |  |  |  |

| AE12 | TxUData14    |  |  |  |

| AE13 | TxUData10    |  |  |  |

| AE14 | TxUPrty      |  |  |  |

| AE15 | TxUData4     |  |  |  |

| AE16 | TxUData1     |  |  |  |

| AE17 | TxCellTxed_1 |  |  |  |

| PIN  | PIN NAME     |

|------|--------------|

| AE18 | RxUClav      |

| AE19 | RxCellRxed_1 |

| AE20 | RxUData14    |

| AE21 | RxUAddr2     |

| AE22 | RxUData11    |

| AE23 | RxUPrty      |

| AE24 | RxUData8     |

| AE25 | GND          |

| AE26 | RxUData4     |

| AF1  | RD_DS        |

| AF2  | D7           |

| AF3  | MOTO/Intel   |

| AF4  | D3           |

| AF5  | TxGFCClk_0   |

| AF6  | TxGFCClk_2   |

| AF7  | TxGFC_2      |

| AF8  | TxGFCMSB_0   |

| AF9  | TxGFCMSB_2   |

| AF10 | TxUAddr4     |

| AF11 | TxUAddr1     |

| AF12 | TxUData13    |

| AF13 | TxUData9     |

| AF14 | TxUData7     |

| AF15 | TxUData3     |

| AF16 | TxUData0     |

| PIN  | PIN NAME     |

|------|--------------|

| AF17 | TxCellTxed_2 |

| AF18 | TxCellTxed_3 |

| AF19 | RxCellRxed_2 |

| AF20 | RxUAddr4     |

| AF21 | RxUAddr1     |

| AF22 | RxUData13    |

| AF23 | RxGFC_0      |

| AF24 | RxUData10    |

| AF25 | RxGFC_1      |

| AF26 | RxUData0     |

| PIN#                                                                                                        | NAME                                                  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Micropro                                                                                                    | ocessor Interface                                     |      |                                                                                                                                                                                                                                                                                                                                                                 |

| AB3<br>AA4<br>AA1<br>AA2<br>Y1<br>Y2<br>Y3<br>W1<br>W2                                                      | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7          | I    | Address Bus Input (Microprocessor Interface): These pins are used to select the on-chip UNI register and RAM space for READ/WRITE operations with the "local" microprocessor.                                                                                                                                                                                   |

| W3<br>V4                                                                                                    | A9<br>A10                                             | I    | Channel Selection:  A9 A10 Channel  0 0 0 1 0 1 0 1 2 1 1 3                                                                                                                                                                                                                                                                                                     |

| AC7<br>AD6<br>AE5<br>AF4<br>AC5<br>AD4<br>AE3<br>AF2<br>AB4<br>AC3<br>AD2<br>AB2<br>Y4<br>AA3<br>AC1<br>AE1 | D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 | I/O  | Bi-Directional Data Bus (Microprocessor Interface Section): These pins function as the Microprocessor Interface bi-directional data bus and is intended to be interfaced to the "local" microprocessor. This pin is inactive if the Microprocessor Interface block is configured to operate over an 8 bit data bus.                                             |

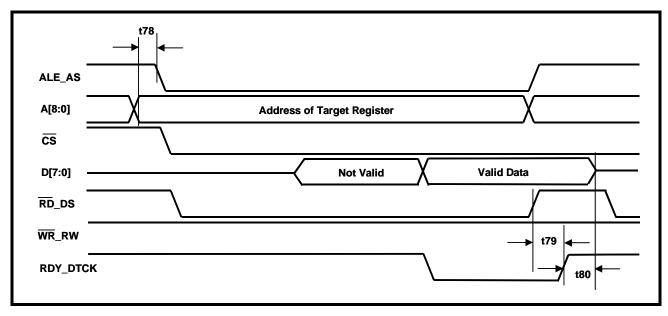

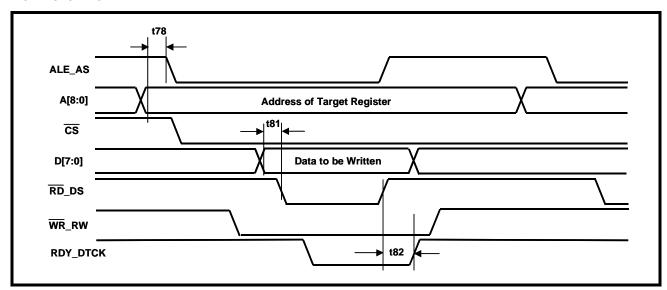

| AE2                                                                                                         | ALE_AS                                                | I    | Address Latch Enable/Address Strobe: This input is used to latch the address (present at the Microprocessor Interface Address Bus, A[8:0]) into the UNI Microprocessor Interface circuitry and to indicate the start of a READ/WRITE cycle. This input is active-"High" in the Intel Mode (MOTO = "Low") and active-"Low" in the Motorola Mode (MOTO = "High"). |

| AB1                                                                                                         | <u>CS</u>                                             | I    | Chip Select Input: This active-"Low" input signal selects the Microprocessor Interface Section of the UNI/Framer and enables Read/Write operations between the "local" microprocessor and the UNI/Framer on-chip registers and RAM locations.                                                                                                                   |

| AE4                                                                                                         | Īnt                                                   | 0    | Interrupt Request Output: This open-drain, active-"Low" output signal will be asserted when the UNI/Framer is requesting interrupt service from the local microprocessor. This output pin should typically be connected to the "Interrupt Request" input of the local microprocessor.                                                                           |

| PIN# | NAME       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AF3  | MOTO/Intel | I    | Motorola/Intel Processor Interface Select Mode:  This input pin allows the user to configure the Microprocessor Interface to interface with either a "Motorola-type" or "Intel-type" microprocessor/microcontroller. Tying this input pin to VDD, configures the microprocessor interface to operate in the Motorola mode (e.g., the UNI/Framer can be readily interfaced to a "Motorola type" local microprocessor). Tying this input pin to GND configures the microprocessor interface to operate in the Intel Mode (e.g., the UNI/Framer can be readily interfaced to an "Intel type" local microprocessor).                                                                                                                                                                                                                                                                                                                                                                          |

| AF1  | RD_DS      | I    | Read Data Strobe (Intel Mode): If the microprocessor interface is operating in the Intel Mode, then this input will function as the RD (READ STROBE) input signal from the local $\mu$ P. Once this active-"Low" signal is asserted, then the UNI/Framer will place the contents of the addressed registers (within the UNI/Framer IC) on the Microprocessor Data Bus (D[15:0]). When this signal is negated, the Data Bus will be tri-stated. Data Strobe (Motorola Mode): If the microprocessor interface is operating in the Motorola mode, then this pin will function as the active-"Low" Data Strobe signal.                                                                                                                                                                                                                                                                                                                                                                        |

| AD1  | RDY_DTCK   | 0    | READY or DTACK: This active-"Low" output pin will function as the READY output, when the microprocessor interface is running in the "Intel" Mode; and will function as the DTACK output, when the microprocessor interface is running in the "Motorola" Mode.  Intel Mode—READY Output.  When the UNI negates this output pin (e.g., toggles it "Low"), it indicates (to the $\mu$ P) that the current READ or WRITE cycle is to be extended until this signal is asserted (e.g., toggled "High").  Motorola Mode:—DTACK (Data Transfer Acknowledge) Output.  The UNI Framer will assert this pin in order to inform the local microprocessor that the present READ or WRITE cycle is nearly complete. If the UNI Framer requires that the current READ or WRITE cycle be extended, then the UNI will delay its assertion of this signal. The 68000 family of $\mu$ Ps requires this signal from its peripheral devices, in order to quickly and properly complete a READ or WRITE cycle. |

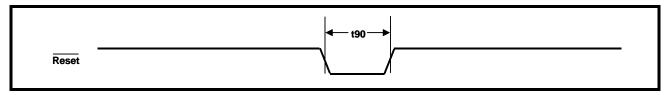

| V2   | Reset      | I    | Reset Input: When this active-"Low" signal is asserted, the UNI Framer will be asynchronously reset. Additionally, all outputs will be "tri-stated", and all on-chip registers will be reset to their default values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AD5  | Width16    | I    | Microprocessor Interface Block Data Bus Width Selector: This input pin permits the user to configure the microprocessor interface of the UNI/Framer, to operate over either an 8 or 16 bit wide bi-directional data bus. Tying this pin to VDD configures the Microprocessor Interface Data Bus width to be 16 bits. Tying this pin to GND configures the Microprocessor Interface Data Bus width to be 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AC2  | WR_RW      | I    | Write Data Strobe (Intel Mode): If the microprocessor interface is operating in the Intel Mode, then this active-"Low" input pin functions as the WR (Write Strobe) input signal from the $\mu$ P. Once this active-"Low" signal is asserted, then the UNI will latch the contents of the $\mu$ P Data Bus, into the addressed register (or RAM location) within the UNI/Framer IC. R/W Input Pin (Motorola Mode): When the Microprocessor Interface Section is operating in the "Motorola Mode", then this pin is functionally equivalent to the "R/W*" pin. In the Motorola Mode, a "READ" operation occurs if this pin is at a logic "1". Similarly, a WRITE operation occurs if this pin is at a logic "0".                                                                                                                                                                                                                                                                           |

| PIN#                     | NAME                                     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|--------------------------|------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Test and                 | Test and Diagnostic                      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| U2                       | TCK                                      | I    | Test Clock: Boundry Scan clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                          |                                          |      | Note: This input pin should be pulled "Low" for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| U1                       | TDI                                      | ı    | Test Data In: Boundry Scan Test data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                          |                                          |      | Note: This input pin should be pulled "Low" for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| V3                       | TDO                                      | 0    | Test Data Out: Boundry Scan test data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| V1                       | TestMode                                 | ***  | Factory Test Mode Pin: The user should tie this pin to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| T4                       | TMS                                      | I    | Test Mode Select: Boundary Scan Mode Select input pin. This input pin should be pulled "Low" for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| U3                       | TRST                                     | I    | Test Mode Reset: Boundary Scan Mode Reset input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                          |                                          |      | Note: This input pin should be pulled "low" for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Line Inte                | erface Drive and S                       | can  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| C13<br>B13<br>A13<br>B12 | DMO_0<br>DMO_1<br>DMO_2<br>DMO_3         | I    | "Drive Monitor Output" Input (from the XRT73L04 LIU IC):  This input pin is intended to be tied to the DMO output pin of the XRT73L04 E3/DS3/STS-1 LIU IC. The user can determine the state of this input pin by reading Bit 2 (DMO) within the Line Interface Scan Register (Address = 0x73). If this input signal is "High", then it means that the drive monitor circuitry (within the XRT73L04 LIU IC) has not detected any bipolar signals at the MTIP and MRING inputs within the last 128 ± 32 bit-periods. If this input signal is "Low", then it means that bipolar signals are being detected at the MTIP and MRING input pins of the XRT73L04 device.  Note: If the designer is not using the XRT73L04 E3/DS3/STS-1 LIU IC, then this input pin can be used for other purposes.                                                                              |  |  |

| R4<br>T3<br>T2<br>T1     | GPIO_0<br>GPIO_1<br>GPIO_2<br>GPIO_3     | I/O  | General Purpose Input/Output pins:  Each of these pin can be configured to function as either input or output pins. If a given pin is configured to function as an Input pin, then the state of this input pin can be monitored by reading Bit X within the "XXX" Register (Address Location = 0x###).  If a given pin is configured to function as a Output pin, then the state of this output pin can be controlled by writing the appropriate value into Bit X within the "XXX" Register.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| A5<br>D5<br>C4<br>A4     | LLOOP_0<br>LLOOP_1<br>LLOOP_2<br>LLOOP_3 | 0    | Local Loop-back Output Pin (to the XRT73L04 E3/DS3/STS-1 LIU IC): This output pin is intended to be connected to the LLOOP input pin of the XRT73L04 LIU IC. This input pin, along with "RLOOP" permits the user to configure the XRT73L04 LIU IC to operate in either of the following three (3) loop-back modes.  • Analog Local Loop-Back Mode  • Digital Local Loop-Back Mode  • Remote Loop-Back Mode. For a detailed description on how to configure the XRT73L04 to operate in each of these loop-back modes, please see Section Writing a "1" to bit 1 of the "Line Interface Drive Register" (Address = 0x72) will cause this output pin to toggle "High". Writing a "0" to this bit-field will cause the RLOOP output to toggle "Low".  Note: If the user is not using the XRT73L04 DS3/E3/STS-1 LIU IC, then this output pin can be used for other purposes. |  |  |

| PIN#                     | NAME                                     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|