### A. General Description:

The USB micro-controller is the best choice for MP3 player, MMC/CompactFlash™/SmartMedia™ card reader/writer, voice recorder and devices with USB port as an interface to transfer information. It is a multi-function chip with excellent performance and low cost. Because all the devices designed by this controller that do not need to have the mechanical parts, which have the properties of fully anti vibration and extremely low power consumption. By using this one chip solution, all the efforts from R/D to production will reduce a lot and this will simplify the RMA problems also

#### **B. Features:**

- 1. Support Transfer Interfaces:

- USB Interface

- ATA/IDE Interface

- 2. Support ICE Mode for ICE Emulation during Product Design R/D Period

- 3. Support Flash ROM (Flash EPROM) for In-System Programming through USB Port or RS232 Port:

- 0x0000h~0xFFFFh: 64KB

- 4. 8051 RAM Mode:

- Internal RAM 256 Bytes.

RAM 0H–127H can be addressed directly and indirectly as the same as in 8051. Address pointers are R0 and R1 of the selected register bank.

RAM 128H–255H can only be addressed indirectly as the same as in 8051. Address pointers are R0, R1 of the selected registers bank.

Internal MOVX RAM:

0x0000h~0x0FFFh: 4KB (Internal and USB Registers)

0x1000h~0x27FFh: 6KB (On Chip)

External MOVX RAM:

0x2800h~0xFFFFh: 54KB

- 5. Support SRAM Buffer (Dual Buffer Mode):

- A Buffer (256+8 = 264 Words)

- B Buffer (256+8 = 264 Words)

- 6. Support MP3 Decoder Chips:

- MICRONAS MAS3507D

- ST Microelectronics STA013

- TLI TL7230MD (Samsung)

- 7. Support Solid State Storage Cards:

- SmartMedia<sup>™</sup> Card (Capacity up to 128MB)

- CompactFlash™ Card

- MultiMedia Card (Capacity up to 32MB/Card)

- 8. Support Specification Versions:

- SmartMedia<sup>™</sup> Electrical Specification Version 1.10

SmartMedia™ Physical Format Specification Version 1.10

SmartMedia™ Format Specification Version 1.10

USB Specification Reversion 1.1

Support one CONTROL transfer, one interrupt transfer and two BULK transfer

Support MP3 USB uC interface.

Endpoint:

Endpoint 0: 16 bytes control transfer.

Endpoint 1: 64\*2 bytes bulk transfer for IN transaction.

Endpoint 2: 64\*2 bytes bulk transfer for OUT transaction.

Endpoint 3: 8byte interrupt transfer for IN transaction.

Data Payload:

Endpoint 0: max 16 bytes Endpoint 1: max 64 bytes

Endpoint 2: max 64 bytes

### Endpoint 3: max 8 bytes

- MultiMediaCard System Specification 1.4

- CompactFlash™ Specification Version 1.4

- PC Card Standard Release 7.0

- 9. Host Transfer Rate for SmartMedia™/CompactFlash™: 16.6MB/s (PIO4)

- 10. Transfer Rate for USB Interface: "Full speed" Up to12Mbits/sec

- 11. Support ADPCM CODEC for Voice Recorder

- 12. Support I<sup>2</sup>C Interface for LCD Controller Chip

- 13. 128-Pin or 100-Pin QFP Package

- 14. Operating Voltage: 3.0V~5.5V (\* Note 1)

- 15. USB bus-powered capability

- 16. Power Saving implemented:

- Power-down mode

- Idle mode

- 17. Working Frequency: 12MHz

\*Note 1: For USB system, operating voltage is 3.0V~3.6V.

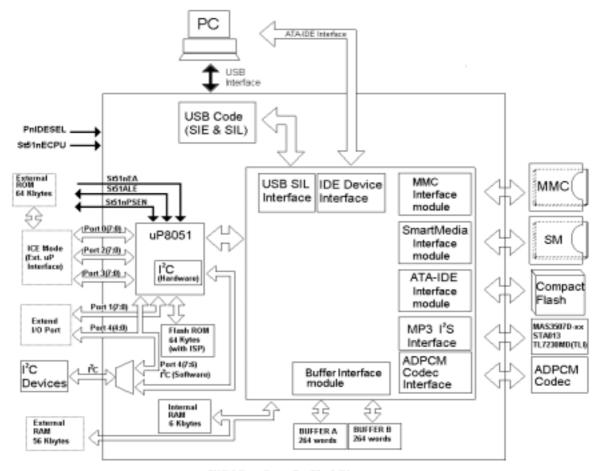

### **C. FUNCTION BLOCK DIAGRAM:**

USB Micro-Controller Block Diagram

#### **FUNCTIONAL DESCRIPTION**

The W78E717E architecture consists of a core controller surrounded by various registers, four general purpose I/O ports, one special purpose programmable 4-bits I/O port, 256 bytes of RAM, three timer/counters, a serial port. The processor supports 111 different opcodes and references both a 64K program address space and a 64K data storage space.

### **Timers 0, 1, and 2**

Timers 0, 1, and 2 each consist of two 8-bit data registers. These are called TL0 and TH0 for Timer 0, TL1 and TH1 for Timer 1, and TL2 and TH2 for Timer 2. The TCON and TMOD registers provide control functions for timers 0, 1. The T2CON register provides control functions for Timer 2. RCAP2H and RCAP2L are used as reload/capture registers for Timer 2. The operations of Timer 0 and Timer 1 are the same as in the W78C51. Timer 2 is a 16-bit timer/counter that is configured and controlled by the T2CON register. Like Timers 0 and 1, Timer 2 can operate as either an external event counter or as an internal timer, depending on the setting of bit C/T2 in T2CON. Timer 2 has three operating modes: capture, auto-reload, and baud rate generator. The clock speed in capture or auto-reload mode is the same as that of Timers 0 and 1.

#### **External Interrupts**

The W78E717E has four external interrupts, which are called /INT0, /INT1, /INT2, /INT3. The IT0 and IT1 bits in the TCON register determine if these interrupts are level triggered (ITn=0) or falling edge triggered (ITn=1). The interrupt bit will be reset by the interrupt hardware if it was an edge triggered interrupt. It is the programmer's responsibility to ensure that the external event that generates a level triggered interrupt is satisfied and that the input is removed before the end of the interrupt service routine. The /INT0 will be used if Card (Smart Media Card, CompactFlash Card and MutiMedia Card) transfer data interrupt was enabled. The /INT1 will be used if USB transfer interrupt was enabled The /INT2 will be used when I2C was enable

### INT2/INT3

Two additional external interrupts,  $\overline{\text{INT2}}$  and  $\overline{\text{INT3}}$ , whose functions are similar to those of external interrupt 0 and 1 in the standard 80C52. The functions/status of these interrupts are determined/shown by the bits in the XICON (External Interrupt Control) register. The XICON register is bit-addressable but is not a standard register in the standard 80C52. Its address is at 0C0H. To set/clear bits in the XICON register, one can use the "SETB ( $\overline{\text{CLR}}$ ) bit" instruction. For example, "SETB 0C2H" sets the EX2 bit of XICON.

### Clock

The W78E717E is designed to use either a crystal oscillator or an external clock. Internally, the clock is divided with two before it is used by default. This makes the W78E717E relatively insensitive to duty cycle variations in the clock.

#### Crystal Oscillator

The W78E717E incorporates a built-in crystal oscillator. To make the oscillator work, a crystal must be connected across pins XTAL1 and XTAL2. In addition, a load capacitor must be connected from each pin to ground, and a resistor must also be connected from XTAL1 to XTAL2 to provide a DC bias when the crystal frequency is above 12 MHz.

#### **External Clock**

An external clock should be connected to pin XTAL1. Pin XTAL2 should be left unconnected. The XTAL1 input is a CMOS-type input, as required by the crystal oscillator. As a result, the external clock signal should have an input one level of greater than 3.5 volts.

### **Power Management**

#### **Idle Mode**

The idle mode is entered by setting the IDL bit in the PCON register. In the idle mode, the internal clock to the processor is stopped. The peripherals and the interrupt logic continue to be clocked. The processor will exit idle mode when either an interrupt or a reset occurs.

#### **Power-down Mode**

When the PD bit in the PCON register is set, the processor enters the power-down mode. In this mode all of the clocks are stopped, including the oscillator. To exit from power-down mode is by a hardware reset or external interrupts  $\overline{\text{INT0}}$  to  $\overline{\text{INT1}}$  when enabled and set to level triggered.

#### Reset

The external RESET signal is sampled at S5P2. To take effect, it must be held high for at least two machine cycles while the oscillator is running. An internal trigger circuit in the reset line is used to deglitch the reset line when the W78E717E is used with an external RC network. The reset logic also has a special glitch removal circuit that ignores glitches on the reset line. During reset, the ports are initialized to FFH, the stack pointer to 07H, PCON (with the exception of bit 4) to 00H, and all of the other SFR registers except SBUF to 00H. SBUF is not reset.

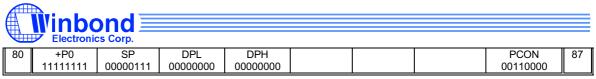

### W78E717E Special Function Registers (SFRs) and Reset Values

| F8 |                    |                   |                    |                    |                   |                   |                    |                    | FF |

|----|--------------------|-------------------|--------------------|--------------------|-------------------|-------------------|--------------------|--------------------|----|

| F0 | +B<br>00000000     |                   |                    |                    |                   |                   | CHPENR<br>00000000 |                    | F7 |

| E8 |                    |                   |                    |                    |                   |                   |                    |                    | EF |

| E0 | +ACC<br>00000000   |                   |                    |                    |                   |                   |                    |                    | E7 |

| D8 | +P4<br>xxxx1111    |                   |                    |                    |                   |                   |                    |                    | DF |

| D0 | +PSW<br>00000000   |                   |                    |                    |                   |                   |                    |                    | D7 |

| C8 | +T2CON<br>00000000 |                   | RCAP2L<br>00000000 | RCAP2H<br>00000000 | TL2<br>00000000   | TH2<br>00000000   |                    |                    | CF |

| C0 | XICON<br>00000000  |                   |                    |                    | SFRAL<br>00000000 | SFRAH<br>00000000 | SFRFD<br>00000000  | SFRCN<br>00000000  | C7 |

| B8 | +IP<br>00000000    |                   |                    |                    |                   |                   |                    | CHPCON<br>0xx00000 | BF |

| В0 | +P3<br>00000000    |                   |                    |                    |                   |                   |                    |                    | B7 |

| A8 | +IE<br>00000000    |                   |                    |                    |                   |                   |                    |                    | AF |

| A0 | +P2<br>11111111    |                   |                    |                    |                   |                   |                    |                    | A7 |

| 98 | +SCON<br>00000000  | SBUF<br>xxxxxxxxx |                    |                    |                   |                   |                    |                    | 9F |

| 90 | +P1<br>11111111    |                   |                    |                    |                   |                   |                    |                    | 97 |

| 88 | +TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TH0<br>00000000   | TH1<br>00000000   |                    |                    | 8F |

### W78E717E

#### Notes:

- 1.The SFRs marked with a plus sign (+) are both byte- and bit-addressable.

- 2. The text of SFR with bold type characters is extension function registers.

### Port 4 (D8H)

| BIT | NAME | FUNCTION                                                                                               |

|-----|------|--------------------------------------------------------------------------------------------------------|

| 7   | P47  | I2C used                                                                                               |

| 6   | P46  | I2C used                                                                                               |

| 5   | P45  | Default Read/Write internal MOVX register, Read/Write signal of P36 and P37 will output at set to low. |

| 4   | P44  | Port 4 General purpose I/O                                                                             |

| 3   | P43  | Port 4 General purpose I/O with interrupt 2.                                                           |

| 2   | P42  | Port 4 General purpose I/O                                                                             |

| 1   | P41  | Port 4 General purpose I/O                                                                             |

| 0   | P40  | Port 4 General purpose I/O                                                                             |

Port 4, SFR P4 at address D8H, is a 4-bit multipurpose programmable I/O port. Each bit can be configured individually by software. P4.0–P4.3 is a bi-directional I/O port which is same as port 1, P4.2 and P4.3 also serve as external interrupt  $\overline{\text{INT3}}$  and  $\overline{\text{INT2}}$  if enabled.

### XICON - external interrupt control (C0H)

| Ì | PX3 | EV2 | IF3 | IT2 | PX2          | EV2 | IE2 | ITO |

|---|-----|-----|-----|-----|--------------|-----|-----|-----|

|   | LV2 |     | IES | 113 | Γ <b>Λ</b> Ζ |     | ICZ | 112 |

PX3: External interrupt 3 priority high if set

EX3: External interrupt 3 enable if set

IE3: If IT3 = 1, IE3 is set/cleared automatically by hardware when interrupt is detected/serviced

IT3: External interrupt 3 is falling-edge/low-level triggered when this bit is set/cleared by software

PX2: External interrupt 2 priority high if set

EX2: External interrupt 2 enable if set

IE2: If IT2 = 1, IE2 is set/cleared automatically by hardware when interrupt is detected/serviced

IT2: External interrupt 2 is falling-edge/low-level triggered when this bit is set/cleared by software

### **Eight-source interrupt information:**

| INTERRUPT SOURCE     | VECTOR<br>ADDRESS | POLLING<br>SEQUENCE WITHIN<br>PRIORITY LEVEL | ENABLE<br>REQUIRED<br>SETTINGS | INTERRUPT<br>TYPE<br>EDGE/LEVEL |

|----------------------|-------------------|----------------------------------------------|--------------------------------|---------------------------------|

| External Interrupt 0 | 03H               | 0 (highest)                                  | IE.0                           | TCON.0                          |

| Timer/Counter 0      | 0BH               | 1                                            | IE.1                           | -                               |

| External Interrupt 1 | 13H               | 2                                            | IE.2                           | TCON.2                          |

| Timer/Counter 1      | 1BH               | 3                                            | IE.3                           | =                               |

| Serial Port          | 23H               | 4                                            | IE.4                           | -                               |

| Timer/Counter 2      | 2BH               | 5                                            | IE.5                           | -                               |

| External Interrupt 2 | 33H               | 6                                            | XICON.2                        | XICON.0                         |

| External Interrupt 3 | 3BH               | 7 (lowest)                                   | XICON.6                        | XICON.3                         |

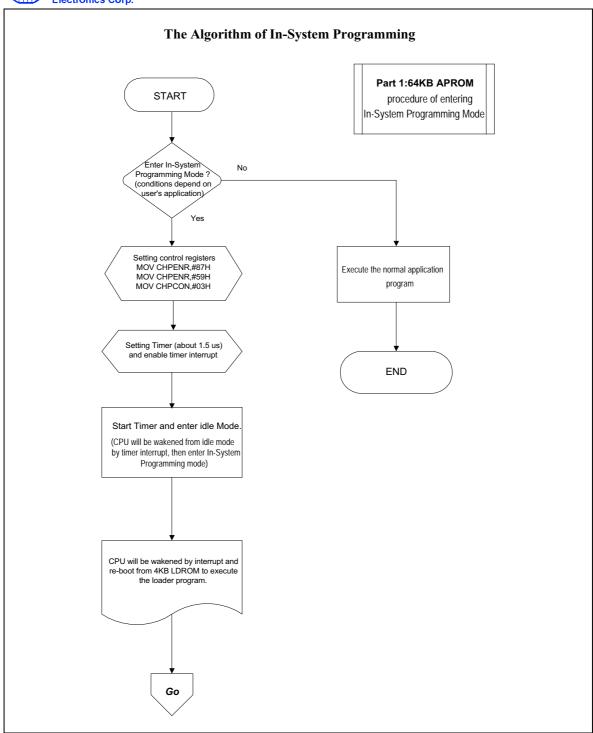

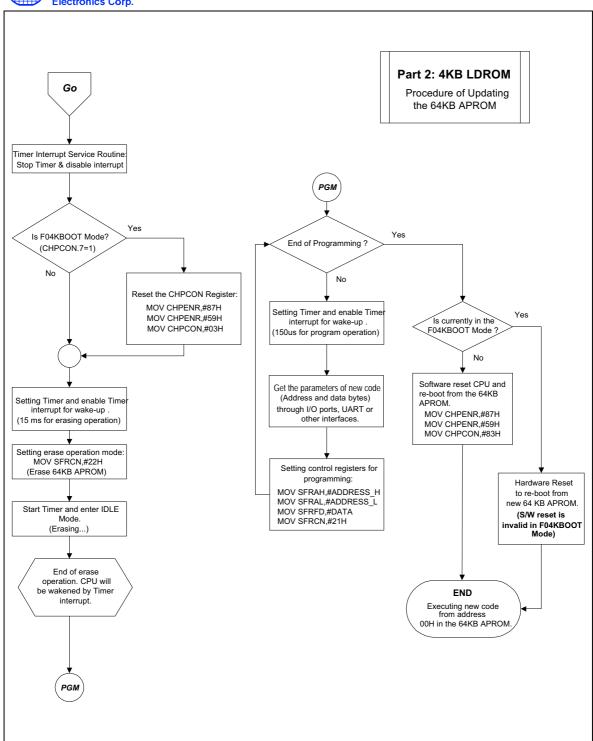

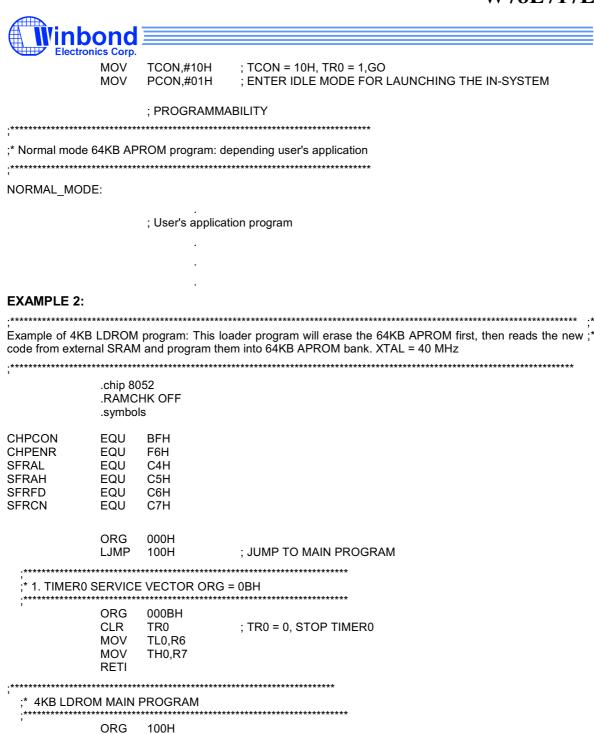

### In-System Programming (ISP) Mode

The W78E717E equips one 64K byte of main MTP-ROM bank for application program (called APROM) and one 4K byte of auxiliary MTP-ROM bank for loader program (called LDROM). In the normal operation, the microcontroller executes the code in the APROM. If the content of APROM needs to be modified, the W78E717E allows user to activate the In-System Programming (ISP) mode by setting the CHPCON register. The CHPCON is read-only by default, software must write two specific values 87H, then 59H sequentially to the CHPENR register to enable the CHPCON write attribute. Writing CHPENR register with the values except 87H and 59H will close CHPCON register write attribute. The W78E717E achieves all in-system programming operations including enter/exit ISP Mode, program, erase, read ... etc, during device in the idle mode. Setting the bit CHPCON.0 the device will enter in-system programming mode after a wake-up from idle mode. Because device needs proper time to complete the ISP operations before awaken from idle mode, software may use timer interrupt to control the duration for device wake-up from idle mode. To perform ISP operation for revising contents of APROM, software located at APROM setting the CHPCON register then enter idle mode, after awaken from idle mode the device executes the corresponding interrupt service routine in LDROM. Because the device will clear the program counter while switching from APROM to LDROM, the first execution of RETI instruction in interrupt service routine will jump to 00H at LDROM area. The device offers software reset for switching back to APROM while the content of APROM has been updated completely. Setting CHPCON register bit 0, 1 and 7 to logic-1 will result software reset to reset the CPU. The software reset serves as a external reset. This in-system programming feature makes the job easy and efficient in which the application needs to update firmware frequently. In some applications, the in-system programming feature makes it possible to easily update the system firmware without opening the chassis.

**SFRAH, SFRAL:** The objective address of on-chip MTP-ROM in the in-system programming mode. SFRFAH contains the high-order byte of address, SFRFAL contains the low-order byte of address.

**SFRFD:** The programming data for on-chip MTP-ROM in programming mode.

**SFRCN:** The control byte of on-chip MTP-ROM programming mode.

### SFRCN (C7)

| BIT        | NAME      | FUNCTION                                                                   |

|------------|-----------|----------------------------------------------------------------------------|

| 7          | ı         | Reserve.                                                                   |

| 6          | WFWIN     | On-chip MTP-ROM bank select for in-system programming.                     |

|            |           | = 0: 64K bytes MTP-ROM bank is selected as destination for re-programming. |

|            |           | = 1: 4K bytes MTP-ROM bank is selected as destination for re-programming.  |

| 5          | OEN       | MTP-ROM output enable.                                                     |

| 4          | CEN       | MTP-ROM chip enable.                                                       |

| 3, 2, 1, 0 | CTRL[3:0] | The flash control signals                                                  |

| MODE W | VFWIN | CTRL<3:0> | OEN | CEN | SFRAH, SFRAL | SFRFD |

|--------|-------|-----------|-----|-----|--------------|-------|

|--------|-------|-----------|-----|-----|--------------|-------|

| Erase 64KB APROM   | 0 | 0010 | 1 | 0 | Х          | Х        |

|--------------------|---|------|---|---|------------|----------|

| Program 64KB APROM | 0 | 0001 | 1 | 0 | Address in | Data in  |

| Read 64KB APROM    | 0 | 0000 | 0 | 0 | Address in | Data out |

| Erase 4KB LDROM    | 1 | 0010 | 1 | 0 | X          | Х        |

| Program 4KB LDROM  | 1 | 0001 | 1 | 0 | Address in | Data in  |

| Read 4KB LDROM     | 1 | 0000 | 0 | 0 | Address in | Data out |

# In-System Programming Control Register (CHPCON) CHPCON (BFH)

| BIT | NAME        | FUNCTION                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   |             | When this bit is set to 1, and both FBOOTSL and FPROGEN are set to 1. It will                                                                                                                                                         |

|     | (I OHIWODE) | enforce microcontroller reset to initial condition just like power on reset. This action will re-boot the microcontroller and start to normal operation. To read this bit in logic-1 can determine that the F04KBOOT mode is running. |

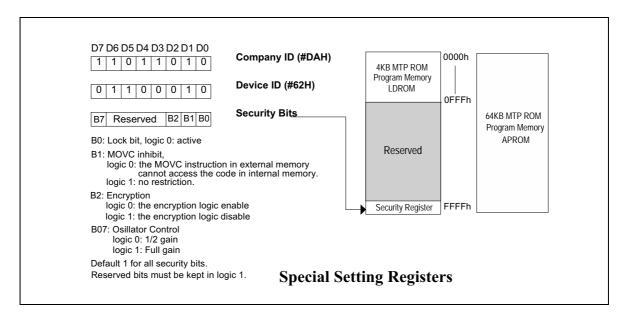

### **SECURITY**

During the on-chip MTP-ROM programming mode, the MTP-ROM can be programmed and verified repeatedly. Until the code inside the MTP-ROM is confirmed OK, the code can be protected. The protection of MTP-ROM and those operations on it are described below.

The W78E717E has several Special Setting Registers, including the Security Register and Company/Device ID Registers, which can not be accessed in programming mode. Those bits of the Security Registers can not be changed once they have been programmed from high to low. They can only be reset through erase-all operation. The contents of the Company ID and Device ID registers have been set in factory. The Security Register is located at the 0FFFFH of the LDROM space.

#### Lock bit

This bit is used to protect the customer's program code in the W78E717E. It may be set after the programmer finishes the programming and verifies sequence. Once this bit is set to logic 0, both the MTP ROM data and Special Setting Registers can not be accessed again.

### **MOVC Inhibit**

This bit is used to restrict the accessible region of the MOVC instruction. It can prevent the MOVC instruction in external program memory from reading the internal program code. When this bit is set to logic 0, a MOVC instruction in external program memory space will be able to access code only in the external memory, not in the internal memory. A MOVC instruction in internal program memory space will always be able to access the ROM data in both internal and external memory. If this bit is logic 1, there are no restrictions on the MOVC instruction.

### Encryption

This bit is used to enable/disable the encryption logic for code protection. Once encryption feature is enabled, the data presented on port 0 will be encoded via encryption logic. Only whole chip erase will reset this bit.

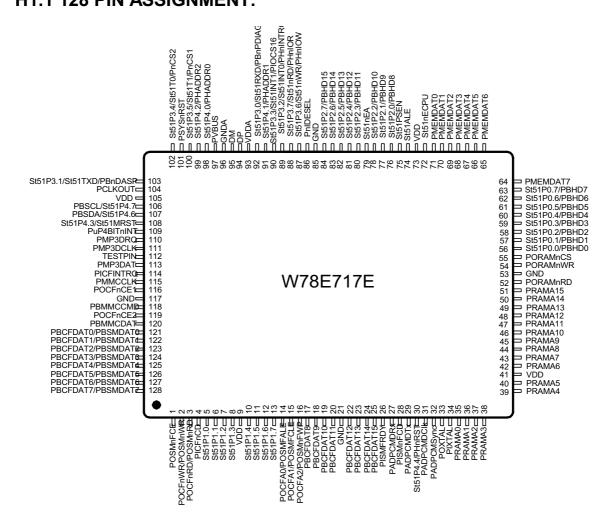

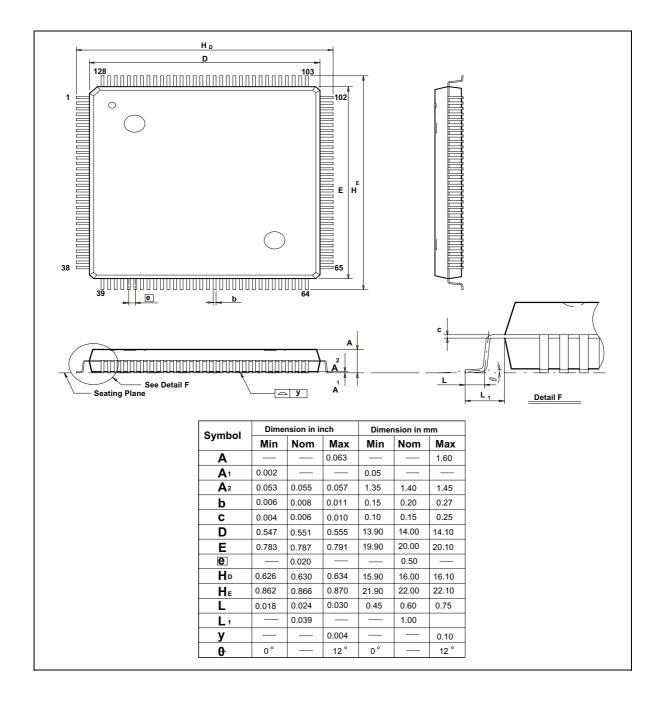

### **D. PIN ASSIGNMENT:**

### **USB Interface Pins: 5**

| ITEM     | Symbols | Pin #   | Pin Type | Description          |  |

|----------|---------|---------|----------|----------------------|--|

| I I CIVI | Symbols | LQFP128 | гіптуре  | Description          |  |

| 1        | DP      | 94      | I/O      | USB Port.            |  |

| 2        | DM      | 95      | I/O      | USB Port.            |  |

| 3        | VDDA    | 93      | I        | Analog power supply. |  |

| 4        | GNDA    | 96      | I        | Analog power ground. |  |

| 5        | PVBUS   | 97      | I        | USB Port.            |  |

### **SRAM and External ROM Interface Pins: 27**

| ITEM     | Symbols      | Pin #                                               | Pin Type           | Description                                       |  |

|----------|--------------|-----------------------------------------------------|--------------------|---------------------------------------------------|--|

| I I EIVI | Symbols      | LQFP128                                             | гштур <del>с</del> | Description                                       |  |

| 1        | PORAMnCS     | 55                                                  | 0                  | St51 External RAM Chip selects Strobe. Low active |  |

| 2        | PORAMnWR     | 54                                                  | 0                  | St51 External RAM Write Strobe. Low active        |  |

| 3        | PORAMnRD     | 52                                                  | 0                  | St51 External RAM Read Strobe. Low active         |  |

| 4        | PRAMA[15:0]  | 51,50,49,48,47,46,45,44,43,42,40,39,<br>38,37,36,35 | 0                  | St51 External ROM/RAM Address Bus.                |  |

| 5        | PMEMDAT[7:0] | 64,65,66,67,68,69,70,71                             | I/O                | St51 External ROM/RAM DATA I/O Port.              |  |

## MP3 (I<sup>2</sup>S Interface Pins): 3

| ITEM     | Symbole  | Pin #                     | Din Tyne | Description                                                                              |  |

|----------|----------|---------------------------|----------|------------------------------------------------------------------------------------------|--|

| I I LIVI | Symbols  | Symbols Pin Type  LQFP128 |          | Description                                                                              |  |

| 1        | PM P3DRQ | 110                       | I        | MP3 Data Request Pin (connect to MP3 decoder DRQ pin)                                    |  |

| 2        | PMP3DCLK | 111                       | 0        | MP3 Data Clock Pin (connect to MP3 decoder CLK pin), the frequency is about 128K ~ 2MHz. |  |

| 3        | PMP3DAT  | 113                       | 0        | MP3 Data Output Pin (connect to MP3 decoder DAT pin)                                     |  |

## I<sup>2</sup>C Interface Pins (within interrupt Pin): 3

| ITEM | Symbols           | Pin #<br>LQFP128 | Pin Type | Description                                                                                                                                                                                                                          |

|------|-------------------|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PBSCL<br>St51P4.7 | 106              | I/O      | General purpose I/O, DDC port serial clock I/O  Schmitt trigger input  V <sub>IH</sub> /V <sub>IL</sub> =0.7V <sub>DD</sub> /0.3V <sub>DD</sub> , V+/V-=~0.6V <sub>DD</sub> /0.4V <sub>DD</sub> Open-drain output, sink current: 8mA |

| 2    | PBSDA<br>St51P4.6 | 107              | I/O      | General purpose I/O, DDC port serial data I/O  Schmitt trigger input  V <sub>IH</sub> /V <sub>IL</sub> =0.7V <sub>DD</sub> /0.3V <sub>DD</sub> , V+/V-=~0.6V <sub>DD</sub> /0.4V <sub>DD</sub> Open-drain output, sink current: 8mA  |

| 3    | PuP4BITnINT       | 109              | I        | 4bit microprocessor interrupt in by this pin.                                                                                                                                                                                        |

### IDE Device Interface and SmartMedia™ Interface Pins: 28

| ITEM     | Symbols   | Pin #   | Pin Type | Description                                                                      |

|----------|-----------|---------|----------|----------------------------------------------------------------------------------|

| I I LIVI | Symbols   | LQFP128 | гіптуре  | Description                                                                      |

| 1        | POCFnRD   | 3       | 0        | IDE Read Enable (connect to IDE Interface<br>Storage Device nRD pin)             |

| ,        | POSMnRD   | 3       | O        | SmartMedia™/Flash Read Enable. (connect to Flash Memory RE/WE pin)               |

| 2        | POCFnWR   | 2       | 0        | IDE Write Enable (connect to IDE Interface<br>Storage Device nWR pin)            |

| 2        | POSMnWR   | 2       | )        | SmartMedia™/Flash Write Enable (connect to Flash Memory RE/WE pin)               |

| 3        | POCFnCE1  | 116     | 0        | IDE Device Chip Enable (connect to IDE Interface Storage Device CE1 pin)         |

| 4        | POCFnCE2  | 119     | 0        | IDE Device Chip Enable (connect to IDE Interface Storage Device CE2 pin).        |

| 5        | PICFINTRQ | 114     | ı        | IDE Device interrupt request. (connect to IDE Interface Storage Device INT pin). |

| 6        | PISMFRDY  | 26      | I        | SmartMedia™/Flash Ready/BSY signal.<br>Connect to flash memory pin Ready/nBusy.  |

|    | Electronics Corp. |                                  |     |                                                                                                                      |  |

|----|-------------------|----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------|--|

|    | POCFA[2:0]        | 16,15,14                         | 0   | PBIDEAddr[15:0] pins connect directly to IDE Interface Storage Device Address Bus[15:0].                             |  |

|    |                   |                                  |     | PSMnFWP- SmartMedia™/Flash Write<br>Protect. Connect to Flash Memory WP pin.                                         |  |

| 7  | POSMnFWP          | 16                               |     | PSMFCLE- SmartMedia™/Flash Command                                                                                   |  |

|    | POSMFCLE          | 15                               | 0   | Latch Enable. Connect to Flash Memory CLE pin.                                                                       |  |

|    | POSMFALE          | 14                               |     | PSMFALE- SmartMedia™/Flash Address<br>Latch Enable. Connect to Flash Memory ALE<br>pin.                              |  |

| 8  | PBCFDAT[7:0]      | 128,127,126,125, 124,123,122,121 | I/O | PBIDEDat[7:0] pins are direct connect to Storage Device (with IDE interface) Data Bus[7~0].                          |  |

|    | PBSMDAT[7:0]      |                                  |     | PBSMDat[7:0] pins connect directly to SmartMedia™/Flash Data Bus[0:7].                                               |  |

| 9  | PBCFDAT[15:8]     | 25,24,23,22,20,19,18,17          | I/O | PBIDEDat[15:8] pins are direct connect to Storage Device (with IDE interface) Data Bus[15~8].                        |  |

| 10 | PICFnCD           | 4                                | I   | This pin is a Card Detect Pin. Connect to the IDE Interface Storage Device Card Detect pin. It is internal pull high |  |

| 11 | PISMnFCD          | 28                               | I   | SmartMedia™/Flash Card Detect. Connect to the SmartMedia™ pin 11. It is internal pull high                           |  |

| 12 | POSMnFCE          | 1                                | 0   | SmartMedia™/Flash Chip Enable. Connect to Flash Memory CE pin. It is internal pull high                              |  |

### MultiMediaCard Interface Pins: 3

| ITEM     | Symbols  | Pin #   | Pin Type | Description                                                      |  |

|----------|----------|---------|----------|------------------------------------------------------------------|--|

| I I EIVI | Symbols  | LQFP128 | гіптуре  | Description                                                      |  |

| 1        | PMMCCLK  | 115     | 0        | MultiMediaCard Clock Pin. The frequency is about 200K ~ 12.5MHz. |  |

| 2        | PBMMCCMD | 118     | I/O      | MultiMediaCard Command/Response Pin.                             |  |

| 3        | PBMMCDAT | 120     | I/O      | MultiMediaCard Data Input/Output Pin.                            |  |

### ADPCM Codec (Winbond W6620) Interface Pins: 4

| ITEM      | Symbols | Pin #   | Pin Type | Description |

|-----------|---------|---------|----------|-------------|

| I I I EIV | Symbols | LQFP128 | Ріп туре | Description |

| 1 | PADPCMDRx  | 27 | I | This pin is used to receive input data, controlled by PADPCMClk and PADPCMSync. Connect directly to ADPCMCodec DT pin.                                |

|---|------------|----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | PADPCMDTx  | 29 | 0 | This pin is used to transmission output data controlled by PADPCMClk and PADPCMSync. Connect directly to ADPCMCodec DR pin.                           |

| 3 | PADPCMCIk  | 31 | 0 | This pin is to receive bit clock or clock for transmission. The frequency varies from 128KHz to 2MHz. Connect directly to ADPCMCodec BCLKT&BCLKR pin. |

| 4 | PADPCMSync | 32 | 0 | This pin is to output 8KHz pulse train to receive / transmit frame syncs, Connect directly to ADPCMCodec FST&FSR pin.                                 |

### IDE Host Interface/External St51 Microprocessor Pins: 42

|      |                |         | 1        |                                                                                                     |  |

|------|----------------|---------|----------|-----------------------------------------------------------------------------------------------------|--|

| ITEM | Symbols        | Pin #   | Pin Type | Description                                                                                         |  |

|      | <b>G</b> j26.6 | LQFP128 | , , , ,  | 2008.i.p.to.i.                                                                                      |  |

|      | St51P3.7       |         |          | Bi-directional I/O with internal pull-ups. It is also                                               |  |

| 1    | (St51nRD)      | 88      | I/O      | used for St51 microprocessor External Data<br>Memory Read Strobe.                                   |  |

|      | PHnIOR         |         |          | Host I/O Read signals. It's active low and includes the internal pull-up resistors.                 |  |

|      | St51P3.6       |         |          | Bi-directional I/O with internal pull-ups. It is also used for St51 microprocessor External Data    |  |

| 2    | (St51nWR)      | 87      | I/O      | Memory Write Strobe.                                                                                |  |

|      | PHnIOW         |         |          | Host I/O Write signals. It's active low and includes the internal pull-up resistors.                |  |

|      | St51P3.5       | 100     | I/O      | Bi-directional I/O with internal pull-ups. It is also used for St51 microprocessor Timer 1 External |  |

| 3    | (St51T1)       |         |          | input.                                                                                              |  |

|      | PnCS1          |         | I        | Card enable 1(When True IDE mode transfer is set).                                                  |  |

|      | St51P3.4       |         | I/O      | Bi-directional I/O with internal pull-ups. It is also used for St51 microprocessor Timer 0 External |  |

| 4    | (St51T0)       | 102     |          | input.                                                                                              |  |

|      | PnCS2          |         | I        | Card enable 2(When True IDE mode transfer is set).                                                  |  |

| 5    | St51P3.3       | an      | 0        | The St51 microprocessor Ext.Int1 source output when ICE Mode is setting.                            |  |

|      | (St51INT1)     | 90      |          | Super whom the mode is setting.                                                                     |  |

|    | Electronics Corp.      |                         |      |                                                                                                                                                       |  |

|----|------------------------|-------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | PIOCS16                |                         |      | In True IDE mode this output signal is asserted low when this device is expecting a word data transfer cycle                                          |  |

| 6  | St51P3.2<br>(St51INT0) | 89                      | 0    | The St51 microprocessor Ext.Int0 source output when ICE Mode is setting.                                                                              |  |

|    | PHnINTRQ               | -                       |      | Host interrupt request (When True IDE mode transfer is set)                                                                                           |  |

| 7  | St51P3.1<br>(St51TXD)  | 103                     | 1/0  | Bi-directional I/O with internal pull-ups. It is also used for St51 microprocessor Serial Port 0 Output.                                              |  |

|    | PBnDASP                |                         |      | Drive Active or Slave Present (When True IDE mode transfer is set)                                                                                    |  |

| 8  | St51P3.0<br>(St51RXD)  | 92 I/O                  | 1/0  | Bi-directional I/O with internal pull-ups. It is also used for St51 microprocessor Serial Port 0 input.                                               |  |

|    | PBnPDIAG               |                         | ,, 0 | Status changed or pass diagnostic (When True IDE mode transfer is set)                                                                                |  |

|    | St51P4.4               | 30                      | I/O  | St51 microprocessor Port4 (Extra port, general purpose I/O).                                                                                          |  |

| 9  | PHnRST                 |                         | I    | Host reset signal. When active, it initiates the control registers and resets St51 microprocessor. This signal is active low.                         |  |

| 10 | St51P4.3               | 400                     | I/O  | St51 microprocessor Port4 (Extra port, general purpose I/O).                                                                                          |  |

| 10 | St51MRST               | 108                     | I    | For external St51 microprocessor reset when ICE Mode.                                                                                                 |  |

| 11 | St51P4[2:0]            | 99,91,98                | I/O  | St51 microprocessor Port4 (Extra port, general purpose I/O).                                                                                          |  |

|    | PHADDR[2:0]            |                         | I    | Host address bus 0~2(True IDE Interface)                                                                                                              |  |

| 13 | St51P1[7:0]            | 13,12,11,10,8,7,6,5     | I/O  | St51 microprocessor Port1 (General purpose I/O).                                                                                                      |  |

| 14 | St51P0[7:0]            | 63,62,61,60,59,58,57,56 | 1/0  | St51 microprocessor Port0 (General purpose I/O). This port also provides a multiplexed low order address/data bus during accesses to external memory. |  |

|    | PBHD[7:0]              |                         |      | Host data bus 0~7.  Support 8-bit or 16-bit data transfer.                                                                                            |  |

| 45 | St51P2[7:0] |                         |     | St51 microprocessor Port2 (General purpose I/O). This port also provides the upper address for accesses to external memory.                                                     |

|----|-------------|-------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | PBHD[15:8]  | 84,83,82,81,80,78,77,76 | 1/0 | Host data bus 8~15.  Support 8-bit or 16-bit data transfer                                                                                                                      |

| 16 | St51nEA     | 79                      | I   | This pin force St51 microprocessor to execute out of external ROM. '0' External ROM Select. It is no pull up resistor.                                                          |

| 17 | St51ALE     | 74                      | 0   | It is used to enable the address latch that separates the address from the data on St51 Port0[7:0].                                                                             |

| 18 | St51nPSEN   | 75                      | 0   | Enable the external ROM data onto the St51Port0 address/data bus during fetch and MOVC operation. When internal ROM access is performed, no strobe signal outputs from this pin |

| 19 | St51nECPU   | 72                      | I   | This pin is used to enable the internal('1') St51 or External('0') St51 microprocessor. It is no pull up resistor.                                                              |

| 20 | PnIDESEL    | 86                      | I   | Select IDE interface('1') or St51 Microprocessor interface('0'). It is no pull up resistor.                                                                                     |

### **Global Signal Pins: 13**

| ITEM | Symbols  | Pin #        | Pin Type | Description                                                                                                                                                                                                      |  |

|------|----------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|      | Symbols  | LQFP128      | тштуре   | Description                                                                                                                                                                                                      |  |

| 1    | PSYSnRST | 101          | I        | System Reset Signal, active low.                                                                                                                                                                                 |  |

| 2    | PIXTAL   | 34           | 1        | Crystal input pad.                                                                                                                                                                                               |  |

| 3    | POXTAL   | 33           | 0        | Crystal Output pad.                                                                                                                                                                                              |  |

| 5    | PCLKOUT  | 104          | 0        | Clock output. The clock frequency can be modifying by the Firm Ware, it can divide the main clock by CLK/(2*n+2) and output to the system, which needs the clock, ex PIXTAL=12MHz, the frequency is about 24MHz. |  |

| 6    | VDD      | 9,41,73,105  | I        | +5V / + 3.3 Power Supply                                                                                                                                                                                         |  |

| 7    | GND      | 21,53,85,117 | I        | Ground                                                                                                                                                                                                           |  |

| 8    | TESTPIN  | 112          | I        | Test Mode, PLL enable('0') or PLL disable('1' internal strong pull low.                                                                                                                                          |  |

### E. USB and Card Interface Register Definition:

Use MOVX @DPTR in 8051 to read/write the register. The addresses are shown as below,

| NO.  | ADDRESS<br>(HEX) | Description                                                               | Reset Value<br>(Hex) |

|------|------------------|---------------------------------------------------------------------------|----------------------|

|      |                  | Host IDE I/O Interface Register                                           |                      |

| E.1  | 0x0100h          | Data Register (CF_DATA)                                                   | 00h                  |

| E.2  | 0x0101h          | Feature Register (Write Only) (CF_FEATURE)                                | -                    |

| E.3  | 0x0101h          | Error Register (Read Only) (CF_ERR_REG)                                   | 00h                  |

| E.4  | 0x0102h          | Sector Count Register (CF_SEC_CNT)                                        | 00h                  |

| E.5  | 0x0103h          | Sector Number Register (CF_SEC_NUM)                                       | 00h                  |

| E.6  | 0x0104h          | Cylinder Low Register (CF_CYL_L)                                          | 00h                  |

| E.7  | 0x0105h          | Cylinder High Register (CF_CYL_H)                                         | 00h                  |

| E.8  | 0x0106h          | Device Header Register (CF_DRV_HD)                                        | 00h                  |

| E.9  | 0x0107h          | Command Register (Write Only) (CF_CMD_REG)                                | -                    |

| E.10 | 0x0107h          | Status Register (Read Only) (CF_STAT)                                     | 00h                  |

| E.11 | 0x010Eh          | Device Control Register (Write Only) (CF_DEVICE_CTL)                      | -                    |

| E.12 | 0x010Eh          | Alternate Status Register (Read Only) (CF_ALSTAT)                         | 00h                  |

| E.13 | 0x010Fh          | Drive Address Register (Read Only)                                        | 00h                  |

|      |                  | Top Register                                                              |                      |

| E.14 | 0x0120h          | Disk Interrupt Control Register (DINCTCL)                                 | 00h                  |

| E.15 | 0x0121h          | Disk Interrupt Reason Register (DINTRSN)                                  | 00h                  |

| E.16 | 0x0122h          | System Control Register (SYS_CTL)                                         | 00h                  |

| E.17 | 0x0123h          | Storage & Host to Buffer Direction / FLASH ECC Status Register (BD_ECCTL) | 00h                  |

| E.18 | 0x0124h          | MMCIO Control Register (MMCIO_CTL)                                        | F5h                  |

| E.19 | 0x0125h          | Buffers Direction/Status Register (BD_ST)                                 | 08h                  |

| Electronics Corp. |                           |                                                                            |     |  |  |

|-------------------|---------------------------|----------------------------------------------------------------------------|-----|--|--|

| E.20              | 0x0126h                   | IDE Control Register (STO_CTL)                                             | E0h |  |  |

| E.21              | 0x0127h                   | USB Control Register (USBIDE_CTL)                                          | C8h |  |  |

| E.22              | 0x0128h                   | XTALOUT Frequency Control Register (XTALOUT_CTL)                           | 80h |  |  |

| E.23              | 0x0129h                   | MP3/ADPCM Control Register (DEBUG_REG)                                     | 14h |  |  |

| E.24              | 0x012Ah                   | MP3/ADPCM Control Register (MP3_ADPCM_CTL)                                 | 14h |  |  |

| E.25              | 0x012Bh                   | MP3 Frequency Control \ ADPCM Data Bit Rate Control Register (MP3ADPCMCLK) | 01h |  |  |

| E.26              | 0x012Ch                   | ADPCM Synchronize Register (Frame syncs 8Khz) (ADPCMCLK2)                  | FFh |  |  |

| E.27              | 0x012Dh                   | ADPCM Data Register (ADPCM_DAT_REG)                                        | 00h |  |  |

| E.28              | 0x012Eh                   | Card Detect Direct Register (CARDDETECT)                                   | 27h |  |  |

| E.29              | 0x012Fh                   | CPU Clock Wake Up Counter Register (WAKE_CNT)                              | 41h |  |  |

|                   |                           | A Buffer Register                                                          |     |  |  |

| E.30              | 0x0130h                   | Sector A Buffer Access Low Byte Register (ABUFL)                           | FFh |  |  |

| E.31              | 0x0131h                   | Sector A Buffer Access High Byte Register (ABUFH)                          | FFh |  |  |

| E.32              | 0x0132h                   | A Buffer Device Address Pointer Register (DAP Low 8 Bits) (ADAPL)          | 01h |  |  |

| E.33              | 0x0133h                   | A Buffer Device Address Pointer Register (DAP High 3 Bits) (ADAPH)         | 00h |  |  |

| E.34              | 0x0134h                   | A Buffer Host Address Pointer Register (HAP Low 8 Bits) (AHAPL)            | 00h |  |  |

| E.35              | 0x0135h                   | A Buffer Host Address Pointer (HAP High 3 Bits) (AHAPH)                    | 00h |  |  |

| E.36              | 0x0136h                   | A Buffer Host Stop Pointer Register (HSP Low 8 Bits) (AHSPL)               | FFh |  |  |

| E.37              | 0x0137h                   | A Buffer Host Stop Pointer Register (HSP High 3 Bits) (AHSPH)              | 00h |  |  |

| E.38              | 0x0138h                   | A Buffer Control Register (ABUF_CTL)                                       | 04h |  |  |

|                   | Flash SmartMedia Register |                                                                            |     |  |  |

| E.39              | 0x0140h                   | Flash Manufacturer Code Register (Read Only)                               | 00h |  |  |

| E.40              | 0x0141h                   | Flash Device ID code Register (Read Only)                                  | 00h |  |  |

| E.41              | 0x0142h                   | Flash Command Register (Write Only)                                        | -   |  |  |

| E.42              | 0x0143h                   | Flash Start Address 0 Register (Write Only)                                | -   |  |  |

| ·                 |                           |                                                                            |     |  |  |

## W78E717E

| Electronics Corp. |         |                                                           |         |  |

|-------------------|---------|-----------------------------------------------------------|---------|--|

| E.43              | 0x0144h | Flash Start Address 1 Register (Write Only)               | -       |  |

| E.44              | 0x0145h | Flash Start Address 2 Register (Write Only)               | -       |  |

| E.45              | 0x0146h | Flash Start Address 3 Register for 64,128 MB (Write Only) | -       |  |

| E.46              | 0x0147h | Flash Sequencer Control Register                          | 29h     |  |

| E.47              | 0x0148h | Flash Control Register                                    | 1fh     |  |

| E.48              | 0x0149h | Flash Direct Buffer Access Control Register               | 00h     |  |

| E.49              | 0x014Ah | Flash Data Read/Write Count Low Byte Register             | 00h     |  |

| E.50              | 0x014Bh | Flash Data Read/Write Count High Byte Register            | 20h     |  |

| E.51              | 0x014Ch | Flash Memory Status Register (Read Only)                  | 00h     |  |

| E.52              | 0x014Dh | Flash CLK/MMC Clock Frequency Control Register            | 00h     |  |

| E.53              | 0x014Eh | Flash LBA_L Register                                      | 00h     |  |

| E.54              | 0x014Fh | Flash LBA_H Register                                      | 00h     |  |

|                   |         | MMC Register, Address is the Same as Flash Address        |         |  |

| E.55              | 0x0140h | CRCCode Res.ARG Register                                  | unknown |  |

| E.56              | 0x0141h | CRCCode Encode Register                                   | unknown |  |

| E.57              | 0x0142h | MMC Res.CMN ARG Register                                  | 00h     |  |

| E.58              | 0x0143h | MMC Res ARG.0 Register                                    | 00h     |  |

| E.59              | 0x0144h | MMC Res ARG.1 Register                                    | 00h     |  |

| E.60              | 0x0145h | MMC Res ARG.2 Register                                    | 00h     |  |

| E.61              | 0x0146h | MMC Res ARG.3 Register                                    | 00h     |  |

| E.62              | 0x0148h | MMC Control Register1 (MMC_CTL1)                          | 1f h    |  |

| E.63              | 0x0149h | MMC Control Register2 (MMC_CTL2)                          | 00h     |  |

| E.64              | 0x014Bh | MMC Control Register3 (MMC_CTL3)                          | 00h     |  |

| E.65              | 0x014Eh | DAT CRCCode Low Byte Register (Read Only)                 | 00h     |  |

| E.66              | 0x014Fh | DAT CRCCode High Byte Register (Read Only)                | 00h     |  |

| <u> </u>          | I       | I .                                                       |         |  |

|      |                                                                   |                                                                    | 1   |  |  |  |  |  |  |

|------|-------------------------------------------------------------------|--------------------------------------------------------------------|-----|--|--|--|--|--|--|

|      |                                                                   | External RAM/Buffer Register                                       |     |  |  |  |  |  |  |

| E.67 | 0x0150h                                                           | Sector Buffer Data (Byte) Access Register (RAMBUF)                 | FFh |  |  |  |  |  |  |

| E.68 | 0x0152h                                                           | Device Address Pointer Register (DAP Low 8 Bits) (RAMDAPL)         | 00h |  |  |  |  |  |  |

| E.69 | 0x0153h                                                           | Device Address Pointer Register (DAP High 8 Bits) (RAMDAPH)        | 00h |  |  |  |  |  |  |

| E.70 | 0x0154h                                                           | Buffer Control Register (RAM_CTL)                                  | 00h |  |  |  |  |  |  |

|      | B Buffer Register                                                 |                                                                    |     |  |  |  |  |  |  |

| E.71 | E.71 0x0160h Sector B Buffer Access Low Byte Register (BBUFL) FFh |                                                                    |     |  |  |  |  |  |  |

| E.72 | 0x0161h                                                           | Sector B Buffer Access High Byte Register (BBUFH)                  | FFh |  |  |  |  |  |  |

| E.73 | 0x0162h                                                           | B Buffer Device Address Pointer Register (DAP Low 8 Bits) (BDAPL)  | 00h |  |  |  |  |  |  |

| E.74 | 0x0163h                                                           | B Buffer Device Address Pointer Register (DAP High 1 Bits) (BDAPH) | 00h |  |  |  |  |  |  |

| E.75 | 0x0164h                                                           | B Buffer Host Address Pointer Register (HAP Low 8 Bits) (BHAPL)    | 00h |  |  |  |  |  |  |

| E.76 | 0x0165h                                                           | B Buffer Host Address Pointer Register (HAP High 2 Bits) (BHAPH)   | 00h |  |  |  |  |  |  |

| E.77 | 0x0166h                                                           | B Buffer Host Stop Pointer Register (HSP Low 8 Bits) (BHSPL)       | FFh |  |  |  |  |  |  |

| E.78 | 0x0167h                                                           | B Buffer Host Stop Pointer Register (HSP High 2 Bits (BHSPH)       | 00h |  |  |  |  |  |  |

| E.79 | 0x0168h                                                           | B Buffer Control Register (BBUF_CTL)                               | 04h |  |  |  |  |  |  |

|      |                                                                   | USB Interface Register                                             |     |  |  |  |  |  |  |

| E.80 | 0x0180h                                                           | USB Control Register (UCR)                                         | 08h |  |  |  |  |  |  |

| E.81 | 0x0181h                                                           | USB Pulse Control Register (UPCR)                                  | 00h |  |  |  |  |  |  |

| E.82 | 0x0182h                                                           | Endpoint 0 Received Packet Size Register (Read Only) (EP0PSR)      | 00h |  |  |  |  |  |  |

| E.83 | 0x0183h                                                           | Endpoint 0 Data Output Register (Write Only) (EP0DOR)              | -   |  |  |  |  |  |  |

| E.84 | 0x0183h                                                           | Endpoint 0 Data Input Register (Read Only) (EP0DIR)                | 24h |  |  |  |  |  |  |

| E.85 | 0x0184h                                                           | Endpoint 3 Data Output Register (Write Only) (EP3DOR)              | -   |  |  |  |  |  |  |

| E.86 | 0x0185h                                                           | USB Return Trigger Register (URTR)                                 | 00h |  |  |  |  |  |  |

| E.87 | 0x0186h                                                           | USB Address Register (UAR)                                         | 00h |  |  |  |  |  |  |

| E.88 | 0x0187h                                                           | Interrupt Enable Register (IER)                                    | 00h |  |  |  |  |  |  |

## W78E717E

| E.89 | 0x0188h  | Interrupt Source Register (Read Only) (ISR)           | 00h |

|------|----------|-------------------------------------------------------|-----|

| E.90 | 0x0189h  | Extended Interrupt Enable Register (EIER)             | 00h |

| E.91 | 0x018Ah  | Extended Interrupt Source Register (Read Only) (EISR) | 00h |

| E.92 | 0x018Bh  | FIFO Clear Register (FCR) (Write Only)                | -   |

| E.93 | 0x018Ch  | FIFO Status Register (Read Only) (FSR)                | FBh |

| E.94 | 0x018Dh  | Mode Select Register (MSR)                            | 00h |

| E.95 | 0x018Eh  | Draft/Memory Data Register (DMDR)                     | FFh |

| E.96 | 0x018Fh  | End Point Address Register 1 (EPAR1)                  | 21h |

| E.97 | 0x0190h  | End Point Address Register 2 (EPAR2)                  | 03h |

| E.98 | 0x0191h  | FIFO Address Register (FAR)                           | 00h |

|      |          | Internal MOVX RAM Address (6K Bytes)                  |     |

| E.99 | 0x1000h- | Internal MOVX RAM                                     | 00h |

|      | 0x27FFh  |                                                       |     |

### **E.a REGISTER DESCRIPTION:**

### ♦HOST IDE I/O INTERFACE (0x010Xh)

E.1: Data Register (CF DATA), Address: 0x0100h, Access: R/W

DIRECTION - This register is bi-directional for the drive and host.

ACCESS RESTRUCTIONS - This register can be written or the contents is valid on read when DRQ is set to one.

FUNCTIONAL DESCRIPTION - The data register is 16-bit wide.

**BIT DESCRIPTION -**

| 15 | 14 | 13 | 12   | 11     | 10 | 9 | 8 |

|----|----|----|------|--------|----|---|---|

|    |    |    | Data | (15:8) |    |   |   |

| 7 | 6 | 5 | 4    | 3     | 2 | 1 | 0 |

|---|---|---|------|-------|---|---|---|

|   |   |   | Data | (7:0) |   |   |   |

### E.2: Feature Register (CF\_FEATURE), Address: 0x0101h, Access: Write Only

DIRECTION - This register is write-only by host.

ACCESS RESTRICTION - This register is write-only when BSY and DRQ are both equal to zero.

FUNCTIONAL DESCRIPTION - This register is command specific.

BIT DESCRIPTION -

| 7 | 6 | 5 | 4      | 3          | 2 | 1 | 0 |

|---|---|---|--------|------------|---|---|---|

|   |   |   | Comman | d specific |   |   |   |

### E.3: Error Register (CF\_ERR\_REG), Address: 0x0101h, Access: Read Only

DIRECTION - This register is read-only by host.

ACCESS RESTRICTION - The contents of this register shall be valid when BSY and DRQ are equal to zero and ERR is asserted.

$\label{prop:contains} FUNCTIONAL\ DESCRIPTION\ -\ This\ register\ contains\ the\ operation\ status\ for\ the\ current\ command.$

BIT DESCRIPTION -

| 7 | 6 | _   | 4 | 2 | 2 | 4   | ^ |

|---|---|-----|---|---|---|-----|---|

| / | 0 | ) 5 | 4 | J |   | l I | 0 |

|   |   |     |   |   |   |     |   |

### W78E717E

| Reserves | UNC | МС | IDNF | MCR | ABRT | TKONF | AMNF |

|----------|-----|----|------|-----|------|-------|------|

|          |     |    |      |     |      |       |      |

Bit 7 Reserved.

Bit 6 UNC (Uncorrectable Data Error) indicate an uncorrectable data error has been encountered;

Bit 5 MC (Media Change) is used by removable media devices.

Bit 4 IDNF (ID Not Found) indicates the requested sector's ID field could not be found;

Bit 3 MCR (Media Change Requested) is used by removable media devices.

Bit 2 ABRT (Aborted Command) indicates the requested command has been aborted because the

command code or a command parameter is invalid or some other error has occurred.

Bit 1 TKONF (Track 0 Not Found) indicates the track 0 has not been found during a RECALIBRATE

command;

Bit 0 AMNF (Address Mark Not Found) indicates the data address mark has not been

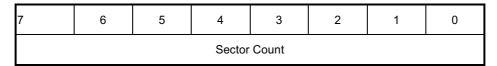

### E.4: Sector Count Register (CF SEC CNT), Address: 0x0102h, Access: R/W

DIRECTION - This register is bi-directional for the drive and host.

ACCESS RESTRICTION - This register is write-only when BSY and DRQ are both equal to zero.

FUNCTIONAL DESCRIPTION - This register contains the number of sector of data requested to be transferred on a read or write operation between the host and the device. If the value in this register is zero, a count of 256 sectors is specified.

BIT DESCRIPTION -

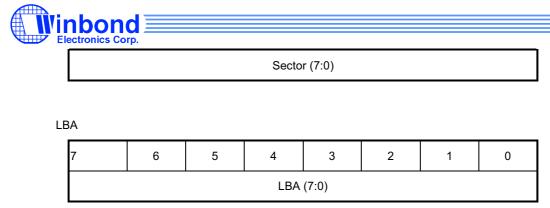

### E.5: Sector Number Register (CF\_SEC\_NUM), Address: 0x0103h, Access: R/W

DIRECTION - This register is bi-directional for the drive and host.

ACCESS RESTRICTION - This register is write-only when BSY and DRQ are both equal to zero.

FUNCTIONAL DESCRIPTION - If the LBA bit is cleared to zero in the Device/Head register, this register contains the starting sector number for any media access. If the LBA bit is set to one in the Device/Head register, this register contains Bits 7-0 of the LBA for any media access.

BIT DESCRIPTION -

CHS

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

### E.6: Cylinder Low Register (CF\_CYL\_L), Address: 0x0104h, Access: R/W

DIRECTION - This register is bi -directional for the drive and host.

ACCESS RESTRICTION - This register is write-only when BSY and DRQ are both equal to zero.

FUNCTIONAL DESCRIPTION – If the LBA bit is cleared to zero in the Device/Head register, this register contains the low order bits of the starting cylinder address for any media access. If the LBA bit is set to one in the Device/Head register, this register contains Bits 15-8 of the LBA for any media access.

BIT DESCRIPTION -

CHS

LBA

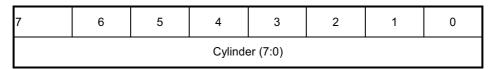

### E.7: Cylinder High Register (CF\_CYL\_H), Address: 0x0105h, Access: R/W

DIRECTION - This register is bi-directional for the drive and host.

ACCESS RESTRICTION - This register is write-only when BSY and DRQ are both equal to zero.

FUNCTIONAL DESCRIPTION - If the LBA bit is cleared to zero in the Device/Head register, this register contains the low order bits of the starting cylinder address for any media access. If the LBA bit is set to one in the Device/Head register, this register contains Bits 23-16 of the LBA for any media access.

BIT DESCRIPTION -

CHS

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

| Cylinder (7:0) |  |

|----------------|--|

|----------------|--|

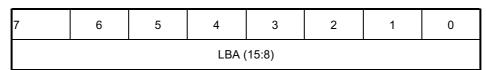

LBA

| 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |

|---|---|---|-------|--------|---|---|---|

|   |   |   | LBA ( | (15:8) |   |   |   |

### E.8: Device/Head Register (CF\_DRV\_HD), Address: 0x0106h, Access: R/W

DIRECTION - This register is bi-directional for the drive and host.

ACCESS RESTRICTION - This register is write-only when BSY and DRQ are both equal to zero.

FUNCTIONAL DESCRIPTION - This register selects the device, defines address translation as CHS or LBA, and provides the head address if CHS mode or LBA (27:24) if LBA mode.

**BIT DESCRIPTION -**

CHS (cylinder-head-sector)

| 7 | 6   | 5 | 4   | 3   | 2   | 1   | 0   |

|---|-----|---|-----|-----|-----|-----|-----|

| 1 | LBA | 1 | DEV | HS3 | HS2 | HS1 | HS0 |

#### LBA (logic block address)

| 7 | 6   | 5 | 4   | 3           | 2 | 1 | 0 |  |

|---|-----|---|-----|-------------|---|---|---|--|

| 1 | LBA | 1 | DEV | LBA (27:24) |   |   |   |  |

Bit 7 Set to one for backward compatibility;

Bit 6 LBA mode if this bit is set to one, otherwise, CHS mode.

Bit 5 Set to one for backward compatibility;

Bit 4 DEV is the device address. When the DEV bit is equal to zero, Device 0 is selected. When the

DEV bit is equal to one, Device 1 is selected.

Bit 3-0 If LBA is equal to zero (CHS), these contain the head address of the starting CHS address. The

$HS3\ bit\ is\ the\ most\ significant\ bit.\ If\ LBA\ is\ equal\ to\ one (LBA),\ these\ bits\ represent\ bits\ 27\ through$

24 of the LBA.

### E.9: Command Register (CF\_CMD\_REG), Address: 0x0107h

DIRECTION - This register is write-only by host.

ACCESS RESTRICTION - This register is write-only when BSY and DRQ are both equal to zero. The contents of this register and all other Command Block registers are not valid while a device is in the Sleep mode.

FUNCTIONAL DESTRIPTION - This register contains the command code being sent to the device. Command execution begins immediately after this register is written.

#### BIT DESCRIPTION

| 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------------|---|---|---|---|---|---|---|--|

| Command Code |   |   |   |   |   |   |   |  |

### E.10: Status Register (CF\_STAT), Address: 0x0107h, Access: Read Only

DIRECTION -This register is read-only by host.

ACCESS RESTRICTION - The contents of this register, except for BSY, will be ignored when BSY is set to one. BSY is valid at all time. The contents of the register and all other Command Block registers are not valid while a device is in the Sleep mode.

FUNCTIONAL DESCRIPTION - This register contains the device status. The contents of this register are updated to reflect the current state of the device and the progress of any command being executed by the device.

#### **BIT DESCRIPTION**

| 7   | 6    | 5  | 4   | 3   | 2    | 1   | 0   |

|-----|------|----|-----|-----|------|-----|-----|

| BSY | DRDY | DF | DSC | DRQ | CORR | IDX | ERR |

Bit 7 BSY (Busy) is set whenever the device has control of the command Block Registers. When the BSY bit is equal to one, writing commands to this register will be ignored

Bit 6 DRDY (Device Ready) is set to indicate that the device is capable of accepting all command codes. This bit shall be cleared at power on.

Bit 5 DF (Device Fault) indicates a device fault error has been detected. The internal status or internal conditions that causes this error to be indicated is vendor specific.

Bit 4 DSC (Device Seek Complete) indicates that the device heads are settled over a track.

Bit 3 DRQ (Data Request) indicates that the device is ready to transfer a word or byte between the host and the device.

Bit 2 CORR (Corrected Data) is used to indicate a correctable data error. The definition of what constitutes a correctable error is vendor specific.

Bit 1 IDX (Index) is vendor specific.

Bit 0 ERR (Error) indicates that an error occurred during execution of the previous command. The bits in the Error register have additional information regarding the cause of the error.

### E.11: Device Control Register (CF\_DEVICE\_CTL), Address: 0x010Eh

This register is used to control the CompactFlash Memory Card interrupt request and to issue an ATA soft reset to The above information is the exclusive intellectual property of Winbond Electronics and shall not be disclosed, distributed or reproduced without permission from Winbond.

the card. The bits are defined as follows:

| 7 | 6 | 5 | 4 | 3 | 2      | 1    | 0 |

|---|---|---|---|---|--------|------|---|

| Х | Х | X | Х | 1 | SW Rst | -IEn | 0 |

Bit 7 This bit is an X (don't care).

Bit 6 This bit is an X (don't care).

Bit 5 This bit is an X (don't care).

Bit 4 This bit is an X (don't care).

Bit 3 This bit is ignored by the CompactFlash Memory Card.

Bit 2 (SW Rst) This bit is set to 1 in order to force the CompactFlash Memory Card to perform an AT Disk

controller Soft Reset operation. This does not change the PCMCIA Card Configuration Registers

(4.3.2 to 4.3.5) as hardware Reset does. The Card remains in Reset until this bit is reset to '0'.

Bit 1 (-IEn) The Interrupt Enable bit enables interrupts when the bit is 0. When the bit is 1, interrupts from the

CompactFlash Memory Card are disabled. This bit also controls the Int bit in the Configuration

and Status Register. This bit is set to 1 at power on and Reset.

Bit 0 This bit is ignored by the CompactFlash Memory Card.

# **E.12: Alternate Status Register (CF\_ALSTAT),** Address: 0x010Eh, Access: Read Only

This register description are same as Status Register.

E.13: Drive Address Register (Read Only), Address: 0x010Fh, Access: Read Only

### **♦TOP REGISTER (0x012Xh)**

E.14: Disk Interrupt Control Register (DINTCTL), Address: 0x0120h, Access: R/W

Bit 7 0: Host Write Command Enable.

1: Host Write Command Disable.

Bit 6 0: Host SRST Enable.

1: Host SRST Disable.

Bit 5 0: USB Interrupt Enable.

1: USB Interrupt Disable.

BIT4 0: MP3Data Request/ ADPCM Data Full Interrupt Enable.

1: MP3Data Request/ ADPCM Data Full Interrupt Disable.

Bit 3 0: External uP4BITINT Input Enable.

1: External uP4BITINT Input Disable.

Bit 2 0: Direct CF/IDE Interrupt Pin Enable.

1: Direct CF/IDE Interrupt Pin Disable.

Bit 1 0: ADPCM Data Require Interrupt Enable.

1: ADPCM Data Require Interrupt Disable.

Bit 0 0: SM/CF/MMC Card Insert/Remove Interrupt Enable.

1: SM/CF/MMC Card Insert/Remove Interrupt Disable.

### E.15: Disk Interrupt Reason Register (DINTRSN), Address: 0x0121h, Access: R/W

Bit 7 1: Host Write Command Interrupt Flag.

Bit 6 1: HOST SRST Interrupt Flag.

Bit 5 1: USB Interrupt Flag.

BIT4 1: MP3Data Request/ ADPCM Data Full Interrupt Flag.

Bit 3 1: EXTERNAL uP4BIT Interrupt Input Flag.

Bit 2 1: DIRECT CF/IDE Interrupt PIN Flag.

Bit 1 1: ADPCM DATA Require Interrupt Flag.

Bit 0 1: SM/CF/MMC Card Insert/Remove Interrupt Flag.

### E.16: System Control Register (SYS\_CTL), Address: 0X0122h, Access: R/W

Bit 7 0: PLL Disable (When USB disable, system run on 12MHz clock).

1: PLL Enable.

Bit 6 CPU Clock Select,

0: CLK48MHz.

1: XTAL 12MHz.

Bit 5 0: Else No Divide.

1: Input Clock Source Divide 2.

Bit 4 CLK48MHz for External USB (SIE & SIL) Circuit:.

0: Enable.

1: Disable.

Bit 3 Clock to Circuit Host.

0: Enable.

1: Disable.

Bit 2 Clock to Circuit USB.

0: Enable.

1: Disable.

Bit 1 Clock to Circuit Buffer.

0: Enable.

1: Disable.

Bit 0 Standby Mode Set.

1: Enable. All circuit clock source will be disable.

0: Disable.

## **E.17: Storage &Host to Buffer Direction / FLASH ECC Status Register (BD\_ECCTL),** Address: 0x0123h Access: Read Only

Bit 7 (Read Only) 0 Storage (CF, SM, MMC) Direct To Buffer A.

1 Storage (CF, SM, MMC) Direct To Buffer B.

Bit 6 (Read Only) 0 Device (USB, PP) Direct To Buffer A.

1 Device (USB, PP) Direct To Buffer B.

Bit 5 (Read Only) 0 Device (MP3) Direct To Buffer A.

1 Device (MP3) Direct To Buffer B.

Bit 4 (Read Only) SM ECC Done.

1: SM ECC Error.

0: SM ECC No Error.

Bit 3 (Read Only) SM Error Correct 2

Bit 1 (Read Only) SM Double Error 1.

1: With Error.

Bit 0 (Read) SM Error Correct 1.

(Write) Set the BUFFER(A/B) Valid with Bit(0)

E.18: MMC Control Register (MMCIO\_CTL), Address: 0x0124h, Access: R/W

**Bit 7**(R) MMCCMDIn Pin Status.

Bit 6(R) MMCDATIn Status.

Bit 5 1: CF\_nRD, CF\_nWE, CF\_nCS1, CF\_nCS2 to High-Z.

Bit 4 Direct Out MMC Data Pin.

1: MMC Data Pin will be Output H.

0: MMC Data Pin will be Output L.

Bit 3 MMC Data Pin Output Gate Control.

1: Enable Output.

0: Disable Output.

Bit 2 Direct Out MMC Command Pin.

1: MMC Command Pin will be Output H.

0: MMC Command Pin will be Output L.

Bit 1 MMC Command Pin Output Gate Control.

1: Enable Output.

0: Disable Output.

Bit 0 Direct Out MMC Clock Pin.

1: MMC Clock Pin will be Output H.

0: MMC Clock Pin will be Output L.

E.19: Buffers Direction/Status Register (BD\_ST), Address: 0x0125h, Access: R/W

Bit 7 0: uP External RAM.

1: Direct to FLASH/CF/MMC.

Bit 6 Reserved.

Bit 5 0: Flash Direct To Buffer A.

1: Flash Direct To Buffer B.

Bit 4 0: Host (USB/IDE) Direct To Buffer A.

1: Host (USB/IDE) Direct To Buffer B.

Bit 3 1: Force MP3\_DAT & Buffer A/B Direction.

Bit 2 0: MP3\_DAT Direct To Buffer A.

1: MP3\_DAT Direct To Buffer B.

Bit 1 1: B Buffer Data Valid/Ready.

Bit 0 1: A Buffer Data Valid/Ready.

E.20: IDE Control Register (STO\_CTL), Address: 0x0126h, Access: R/W

Bit 7 0: Extend 1 (ADPCM) Card Detect Pin Enable.

1: Extend 1 (ADPCM) Card Detect Pin Disable.

Bit 6 0: Extend 2 (ADPCM) Card Detect Pin Enable.

1: Extend 2 (ADPCM) Card Detect Pin Disable.

Bit 5 0: Extend 3 (ADPCM) Card Detect Pin Enable.

1: Extend 3 (ADPCM) Card Detect Pin Disable.

Bit 4 0: IDE 8Bits Transfer Mode Select.

1: Else 16Bits.

Bit 3~2

"11" CPU Interface Select;

"10" MMC Interface Select;

"01" IDE Interface Select;

"00" SM Interface Select;

Bit 1 IDE Read'1'/Write'0' Direction.

Bit 0 Set IDE Direct Buffer Transfer '1'.

E.21: USB Control Register (USBIDE\_CTL), Address: 0x0127h, Access: R/W

Bit 7 HnDASP I.

Bit 6 HnPDIAG\_I.

Bit 5 HnDASP\_noe.

Bit 4 HnPDIAG\_noe.

Bit 3 USB\_RST

1: Reset USB (SIE & SIL).

0: Enable USB (SIE & SIL).

Bit 2 Host either USB or IDE select

1: IDE Interface Select.

0: USB Interface Select.

Bit 1 Device IDE/USB R/W Direction.

1: Read.

0: Write.

Bit 0 1: Set IDE Direct Buffer Transfer

0: Set USB Direct Buffer Transfer

### E.22: XTALOut Frequency Control (XTALOUT\_CTL), Address: 0x0128h, Access: R/W

BIT 7 Clock Out Enable.

0: Enable.

1: Disable.

BIT 6 System Clock Select.

1: Select system clock.

0: Setting by bit (6~0).

BIT 5~0 Base Of 25 MHz:

"0000000": 12.500 MHz -- 80ns

"0000001": 06.250 MHz --160ns

"0000011": 03.125 MHz --320ns

### E.23: MP3/ADPCM Control Register (DEBUG\_REG), Address: 0x0129h, Access: R/W

### Bit (7~5) MMC CMD/DAT I/O Bus Select:

0XX -> Default MMC Bus.

100 -> CF\_DIO(1):MMC\_CMD; CF\_DIO(0):MMC\_DAT;

101 -> CF\_DIO(3):MMC\_CMD; CF\_DIO(2):MMC\_DAT;

110 -> CF\_DIO(5):MMC\_CMD; CF\_DIO(4):MMC\_DAT;

111 -> CF\_DIO(7):MMC\_CMD; CF\_DIO(6):MMC\_DAT;

Bit 4 Reserved.

Bit 3 Reserved.

Bit 2 PADPCMDTx Signal out (use as I/O pin).

Bit 1 PADPCMSync Signal out (use as I/O pin).

Bit 0 PADPCMCLK Signal out (use as I/O pin).

E.24: MP3/ADPCM Control Register (MP3\_ADPCM\_CTL), Address: 0x012Ah, Access: R/W

Bit 7 MP3\_StartPlay

1: Enable,

0: Disable.

Bit 6 Reserved.

Bit 5 1: MP3 I2S Falling Edge output,

0: MP3 I2S Rising Edge output,

Bit 4 1: MP3 DRQ High Active.

0: Low Active.

Bit 3 1: MP3 Data Byte Unit.

0: MP3 Data Bit Unit.

Bit 2 MP3 Data Output Gate.

1: Enable Output.

0: Disable Output.

Bit 1 1: TL7230MD HIP Select.

0: ADPCM Interface.

Bit 0 MMC Card Detect PIN Enable.

0: Enable.

1: Disable.

#### E.25: MP3 Frequency Control \ ADPCM Data Bit Rate Control Register (MP3ADPCMCLK)

Address: 0x012Bh, Access: R/W

Bit 7 ADPCM Enable.

1: Enable,

0: Disable.

Bit 6~4 ADPCM Sample Bit Number (1~8)

Bit 3~0 Base Of CLK MHz: