## 4Mx32 SDRAM

## **FEATURES**

- 53% Space Savings vs. Monolithic Solution

- Reduced System Inductance and Capacitance

- Pinout and Footprint Compatible to SSRAM 119 BGA

- 3.3V Operating Supply Voltage

- Fully Synchronous to Positive Clock Edge

- Clock Frequencies of 133, 125 and 100MHz

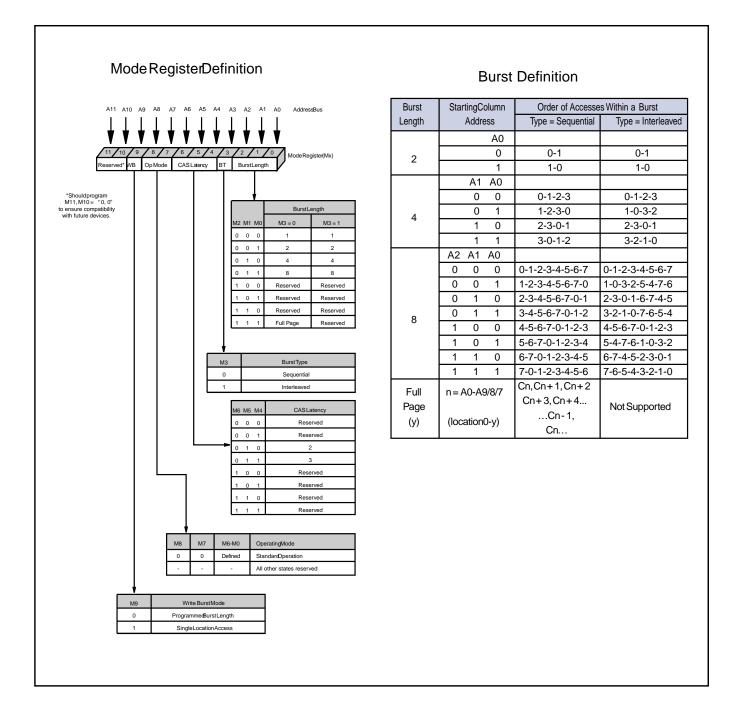

- Burst Operation

- · Sequential or Interleave

- Burst Length = Programmable 1, 2, 4, 8 or Full Page

- · Burst Read and Write

- · Multiple Burst Read and Single Write

- Data Mask Control Per Byte

- Auto and Self Refresh

- Automatic and Controlled Precharge Commands

- Suspend Mode and Power Down Mode

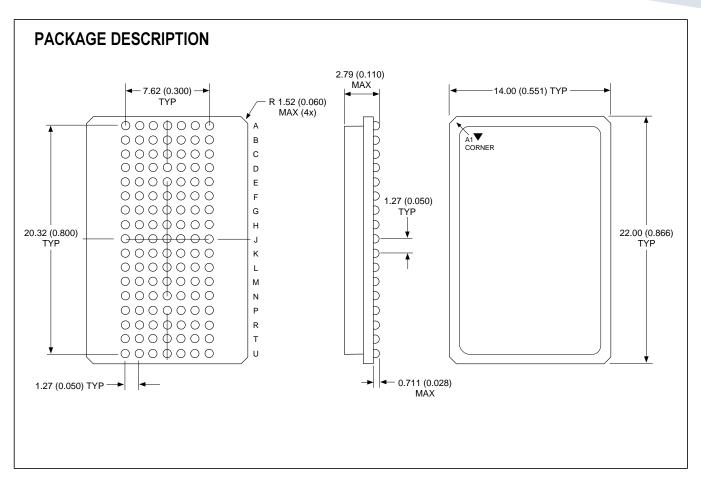

- 119 Pin BGA, JEDEC MO-163

## **DESCRIPTION**

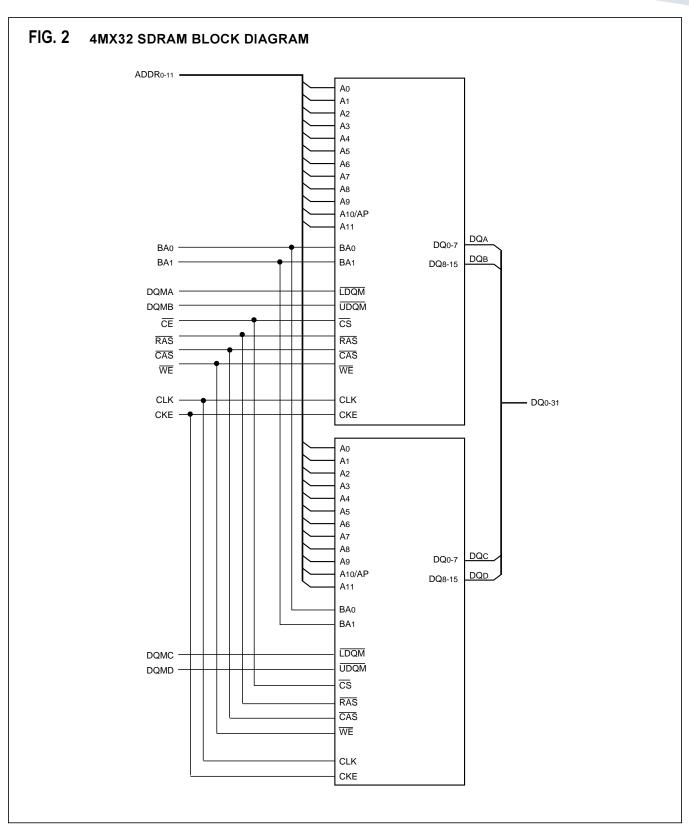

The WED3DL324V is a 4Mx32 Synchronous DRAM configured as 4x1Mx32. The SDRAM BGA is constructed with two 4Mx16 SDRAM die mounted on a multi-layer laminate substrate and packaged in a 119 lead, 14mm by 22mm, BGA.

The WED3DL324V is available in clock speeds of 133MHz, 125MHz and 100MHz. The range of operating frequencies, programmable burst lengths and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

The package and design provides performance enhancements via a 50% reduction in capacitance vs. two monolithic devices. The design includes internal ground and power planes which reduces inductance on the ground and power pins allowing for improved decoupling and a reduction in system noise.

## FIG. 1 PINOUT (TOP VIEW)

|   | 1    | 2   | 3       | 4   | 5    | 6   | 7    |   |

|---|------|-----|---------|-----|------|-----|------|---|

| Α | VDDQ | NC  | BA0     | NC  | A10  | A7  | VDDQ | Α |

| В | NC   | NC  | NC/A12* | CAS | A11  | NC  | NC   | В |

| С | NC   | NC  | BA1     | VDD | A9   | A8  | NC   | С |

| D | DQC  | NC  | VSS     | NC  | VSS  | NC  | DQB  | D |

| E | DQC  | DQC | VSS     | CE  | VSS  | DQB | DQB  | Е |

| F | VDDQ | DQC | VSS     | RAS | VSS  | DQB | VDDQ | F |

| G | DQC  | DQC | DQMC    | NC  | DQMB | DQB | DQB  | G |

| Н | DQC  | DQC | VSS     | CKE | VSS  | DQB | DQB  | Н |

| J | VDDQ | VDD | NC      | VDD | NC   | VDD | VDDQ | J |

| K | DQD  | DQD | VSS     | CLK | VSS  | DQA | DQA  | K |

| L | DQD  | DQD | DQMD    | NC  | DQMA | DQA | DQA  | L |

| М | VDDQ | DQD | VSS     | WE  | VSS  | DQA | VDDQ | М |

| N | DQD  | DQD | VSS     | A1  | VSS  | DQA | DQA  | N |

| Р | DQD  | NC  | VSS     | A0  | VSS  | NC  | DQA  | Р |

| R | NC   | A6  | NC      | VDD | NC   | A2  | NC   | R |

| Т | NC   | NC  | A5      | A4  | А3   | NC  | NC   | T |

| U | VDDQ | NC  | NC      | NC  | NC   | NC  | VDDQ | U |

|   | 1    | 2   | 3       | 4   | 5    | 6   | 7    |   |

### PIN DESCRIPTION

| A0 – A11 | Address Bus                     |  |  |  |  |  |  |

|----------|---------------------------------|--|--|--|--|--|--|

| BA0-1    | Bank Select Addresses           |  |  |  |  |  |  |

| DQ       | Data Bus                        |  |  |  |  |  |  |

| CLK      | Clock                           |  |  |  |  |  |  |

| CKE      | Clock Enable                    |  |  |  |  |  |  |

| DQM      | Data Input/Output Mask          |  |  |  |  |  |  |

| RAS      | Row Address Strobe              |  |  |  |  |  |  |

| CAS      | Column Address Strobe           |  |  |  |  |  |  |

| CE       | Chip Enable                     |  |  |  |  |  |  |

| VDD      | Power Supply pins, 3.3V         |  |  |  |  |  |  |

| VDDQ     | Data Bus Power Supply pins,3.3V |  |  |  |  |  |  |

| VSS      | Ground pins                     |  |  |  |  |  |  |

\*NOTE: Pin B3 is designated as NC/A12. This pin is used for future density upgrades as address pin A12.

## INPUT/OUTPUT FUNCTIONAL DESCRIPTION

| Symbol           | Туре         | Signal | Polarity            | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|--------------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK              | Input        | Pulse  | Positive Edge       | The system clock input. All of the SDRAM inputs are sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                 |

| CKE              | Input        | Level  | Active High         | Activates the CLK signal when high and deactivates the CLK signal when low. By deactivating the clock, CKE low initiates the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                        |

| CE               | Input        | Pulse  | Active Low          | CE disable or enable device operation by masking or enabling all inputs except CLK, CKE and DQM.                                                                                                                                                                                                                                                                                             |

| RAS, CAS<br>WE   | Input        | Pulse  | Active Low          | When sampled at the positive rising edge of the clock, $\overline{\text{CAS}}$ , $\overline{\text{RAS}}$ , and $\overline{\text{WE}}$ define the operation to be executed by the SDRAM.                                                                                                                                                                                                      |

| BA0,BA1          | Input        | Level  | _                   | Selects which SDRAM bank is to be active.                                                                                                                                                                                                                                                                                                                                                    |

|                  |              |        |                     | During a Bank Activate command cycle, Ao-11 defines the row address (RAo-11) when sampled at the rising clock edge.                                                                                                                                                                                                                                                                          |

| A0-11,<br>A10/AP | Input        | Level  | _                   | During a Read or Write command cycle, Ao-7 defines the column address (CAo-7) when sampled at the rising clock edge. In addition to the row address, A10/AP is used to invoke Autoprecharge operation at the end of the Burst Read or Write cycle. If A10/AP is high, autoprecharge is selected and BAo, BA1 defines the bank to be precharged. If A10/AP is low, autoprecharge is disabled. |

|                  |              |        |                     | During a Precharge command cycle, A10/AP is used in conjunction with BA0, BA1 to control which bank(s) to precharge. If A10/AP is high, all banks will be precharged regardless of the state of BA0, BA1. If A10/AP is low, then BA0, BA1 is used to define which bank to precharge.                                                                                                         |

| DQ               | Input/Output | Level  | _                   | Data Input/Output are multiplexed on the same pins                                                                                                                                                                                                                                                                                                                                           |

| DQM              | Input        | Pulse  | Mask<br>Active High | The Data Input/Output mask places the DQ buffers in a high impedance state when sampled high. In Read mode, DQM has a latency of two clock cycles and controls the output buffers like an output enable. In Write mode, DQM has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the Write operation if DQM is high.               |

| VDD, VSS         | Supply       |        |                     | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                   |

| VDDQ             | Supply       |        |                     | Isolated power and ground for the output buffers to improve noise immunity.                                                                                                                                                                                                                                                                                                                  |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                    | Symbol   | Min  | Max  | Units |

|------------------------------|----------|------|------|-------|

| Power Supply Voltage         | VDD/VDDQ | -1.0 | +4.6 | ٧     |

| Input Voltage                | VIN      | -1.0 | +4.6 | ٧     |

| Output Voltage               | Vouт     | -1.0 | +4.6 | ٧     |

| Operating Temperature        | Topr     | -0   | +70  | °C    |

| Storage Temperature          | Тѕтс     | -55  | +125 | °C    |

| Power Dissipation            | Po       | _    | 1.5  | W     |

| Short Circuit Output Current | los      | _    | 50   | mA    |

Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## RECOMMENDED DC OPERATING CONDITIONS

(Voltage Referenced to: Vss = 0V, TA = 0°C to +70°C)

| Parameter                        | Symbol   | Min  | Тур | Max      | Unit |

|----------------------------------|----------|------|-----|----------|------|

| Supply Voltage                   | VDD/VDDQ | 3.0  | 3.3 | 3.6      | V    |

| Input High Voltage               | VIH      | 2.0  | 3.0 | VDD +0.3 | ٧    |

| Input Low Voltage                | VIL      | -0.3 | _   | 0.8      | ٧    |

| Output High Voltage (IoH = -2mA) | Vон      | 2.4  | _   | _        | ٧    |

| Output Low Voltage (IoL = 2mA)   | Vol      | -    | _   | 0.4      | ٧    |

| Input Leakage Voltage            | lıL      | -5   | _   | 5        | μA   |

| Output Leakage Voltage           | loL      | -5   | _   | 5        | μΑ   |

## **CAPACITANCE**

$(TA = 25^{\circ}C, f = 1MHz, VDD = 3.3V)$

| Parameter                     | Symbol          | Max | Unit |

|-------------------------------|-----------------|-----|------|

| Input Capacitance             | C <sub>I1</sub> | 4   | pF   |

| Input/Output Capacitance (DQ) | Cout            | 5   | pF   |

## **OPERATING CURRENT CHARACTERISTICS**

$(Vcc = 3.3V, TA = 0^{\circ}C to +70^{\circ}C)$

| Parameter                                           | Symbol | Conditions                                                             | -7  | -8  | -10 | Units |

|-----------------------------------------------------|--------|------------------------------------------------------------------------|-----|-----|-----|-------|

| Operating Current (One Bank Active) (1)             | ICC1   | Burst Length = 1, trc ≥ trc(min), loL = 0mA                            | 250 | 230 | 200 | mA    |

| Operating Current (Burst Mode) (1)                  | ICC4   | Page Burst, 4 banks active, tccb = 2 clocks                            | 300 | 280 | 230 | mA    |

| Precharge Standby Current in Power Down Mode        | ICC2P  | CKE ≤ VI∟(max), tcc = 15ns                                             | 2   | 2   | 2   | mA    |

|                                                     | ICC2PS | CKE, CLK ≤ V⊩(max), tcc = ∞, Inputs Stable                             | 2   | 2   | 2   | mA    |

| Precharge Standby Current in Non-Power Down Mode    | ICC1N  | CKE = V <sub>IH</sub> , tcc = 15ns<br>Input Change one time every 30ns | 160 | 160 | 160 | mA    |

|                                                     | ICC1NS | CKE ≥ Viн(min), tcc = ∞<br>No Input Change                             | 120 | 120 | 120 | mA    |

| Precharge Standby Current in Power Down Mode        | ICC3P  | CKE ≤ VI∟(max), tcc = 15ns                                             | 12  | 12  | 12  | mA    |

| riositaligo otarias y outroit in riosito pomitinodo | ICC3PS | CKE ≤ VI∟(max), tcc = ∞                                                | 12  | 12  | 12  | mA    |

| Active Standby Current in Non-Power Down Mode       | ICC3N  | CKE = V <sub>IH</sub> , tcc = 15ns<br>Input Change one time every 30ns | 120 | 120 | 120 | mA    |

| (One Bank Active)                                   | ICC3NS | CKE $\ge$ V <sub>I</sub> H(min), tcc = ∞, No Input Change              | 90  | 90  | 90  | mA    |

| Refresh Current (2)                                 | ICC5   | trc ≥ trc(min)                                                         | 460 | 420 | 400 | mA    |

| Self Refresh Current                                | ICC6   | CKE ≤ 0.2V                                                             | 6   | 6   | 6   | mA    |

- 1. Measured with outputs open.

- 2. Refresh period is 64ms.

### **SDRAM AC CHARACTERISTICS**

| <u> </u>                                     | ·      | Symbol   | 133 | BMHz    | 125 | 5MHz    | <u>1001</u> | VIHz    |       |

|----------------------------------------------|--------|----------|-----|---------|-----|---------|-------------|---------|-------|

| Parameter                                    |        | •        | Min | Max     | Min | Max     | Min         | Max     | Units |

| Clock Cycle Time (1)                         | CL = 3 | tcc      | 7   | 1000    | 8   | 1000    | 10          | 1000    | no    |

| Clock Cycle Time (1)                         | CL = 2 | tcc      | 7.5 | 1000    | 10  | 1000    | 12          | 1000    | ns    |

| Clock to valid Output delay (1,2)            |        | tsac     |     | 5.4     |     | 6       |             | 7       | ns    |

| Output Data Hold Time (2)                    |        | tон      | 3   |         | 3   |         | 3           |         | ns    |

| Clock HIGH Pulse Width (3)                   |        | tсн      | 2.5 |         | 3   |         | 3           |         | ns    |

| Clock LOW Pulse Width (3)                    |        | tcL      | 2.5 |         | 3   |         | 3           |         | ns    |

| Input Setup Time (3)                         |        | tss      | 1.5 |         | 2   |         | 2           |         | ns    |

| Input Hold Time (3)                          |        | tsн      | 0.8 |         | 1   |         | 1           |         | ns    |

| CLK to Output Low-Z (2)                      |        | tsLz     | 1.0 |         | 1   |         | 1.5         |         | ns    |

| CLK to Output High-Z                         |        | tsнz     |     | 5.4     |     | 7       |             | 7       | ns    |

| Row Active to Row Active Delay (4)           |        | trrd     | 14  |         | 20  |         | 20          |         | ns    |

| RAS to CAS Delay (4)                         |        | trcd     | 15  |         | 20  |         | 20          |         | ns    |

| Row Precharge Time (4)                       |        | trp      | 15  |         | 20  |         | 20          |         | ns    |

| Row Active Time (4)                          |        | tras     | 37  | 120,000 | 50  | 120,000 | 50          | 120,000 | ns    |

| Row Cycle Time - Operation (4)               |        | trc      | 60  |         | 70  |         | 80          |         | ns    |

| Row Cycle Time - Auto Refresh (4,8)          |        | trec     | 66  |         | 70  |         | 80          |         | ns    |

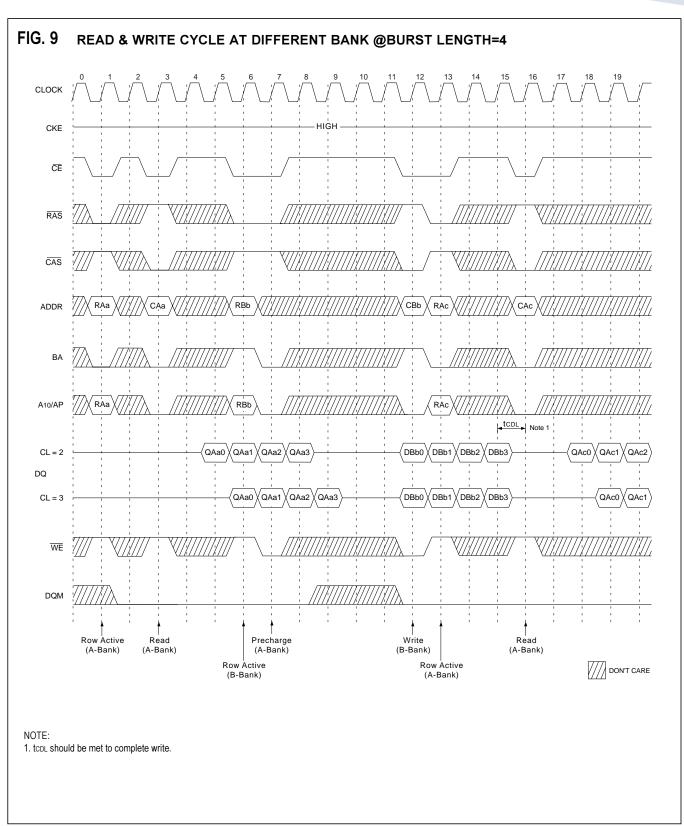

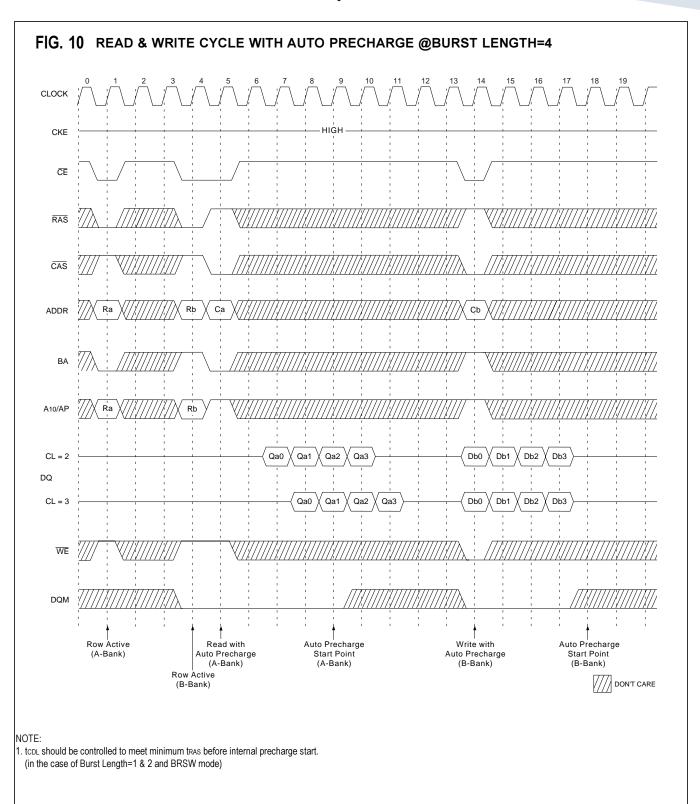

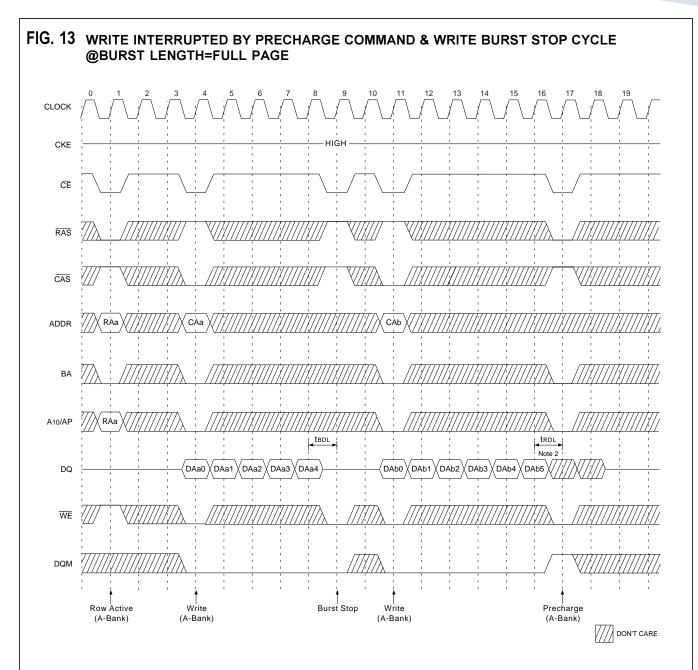

| Last Data in to New Column Address Delay (5) |        | tcdl     | 1   |         | 1   |         | 1           |         | CLK   |

| Last Data in to Row Precharge (5)            |        | trdl     | 2   |         | 2   |         | 2           |         | CLK   |

| Last Data in to Burst Stop (5)               |        | tBDL     | 1   |         | 1   |         | 1           |         | CLK   |

| olumn Address to Column Address Delay (6)    |        | tccD     | 1.0 |         | 1.0 |         | 1.5         |         | CLK   |

| Data Out to High Impedance from Precharge    |        | CL3 tROH | 3   |         | 3   |         | 3           |         | CLIZ  |

|                                              |        | CL2 tROH | 2   |         | 2   |         | 2           |         | CLK   |

- 1. Parameters depend on programmed CAS latency.

- 2. If clock rise time is longer than 1ns (trise/2 -0.5)ns should be added to the parameter.

- 3. Assumed input rise and fall time = 1ns. If trise of trail are longer than 1ns. [(trise = trail)/2] 1ns should be added to the parameter.

- 4. The minimum number of clock cycles required is determined by dividing the minimum time required by the clock cycle time and then rounding up to the next higher integer.

- 5. Minimum delay is required to complete write.

- 6. All devices allow every cycle column address changes.

- 7. In case of row precharge interrupt, auto precharge and read burst stop.

- 8. A new command may be given tRFC after self-refresh exit.

### **COMMAND TRUTH TABLE**

|                           |                            | (                | KE | CE  |     |    | 100 |    | BA             |             |        |   |

|---------------------------|----------------------------|------------------|----|-----|-----|----|-----|----|----------------|-------------|--------|---|

|                           | Previous<br>Cycle          | Current<br>Cycle | CE | RAS | CAS | WE | DQM | DA | A10/AP<br>A9-0 | A12, A11,   | Notes  |   |

| Register                  | Mode Register Set          | Н                | Х  | L   | L   | L  | L   | Х  |                | OP CODE     |        |   |

| Refresh                   | Auto Refresh (CBR)         | Н                | Н  | L   | L   | L  | Н   | Х  | Х              | Х           | Х      |   |

| I/GIIG3II                 | Entry Self Refresh         | Н                | L  | L   | L   | L  | Н   | Х  | Х              | Х           | Х      |   |

| Precharge                 | Single Bank Prechar        | де Н             | Х  | L   | L   | Н  | L   | Х  | BA             | L           | Х      | 2 |

|                           | Precharge all Banks        | Н                | Х  | L   | L   | Н  | L   | Х  | Х              | Н           | Х      |   |

| Bank Activate             |                            | Н                | Х  | L   | L   | Н  | Н   | Х  | BA             | Row Address |        | 2 |

| Write                     |                            | Н                | Х  | L   | Н   | L  | L   | Х  | BA             | L           | Column | 2 |

| Write with Auto           | Precharge                  | Н                | Х  | L   | Н   | L  | L   | Х  | BA             | Н           | Column | 2 |

| Read                      |                            | Н                | Х  | L   | Н   | L  | L   | Х  | BA             | L           | Column | 2 |

| Read with Auto            | Precharge                  | Н                | Х  | L   | Н   | L  | Н   | Х  | BA             | Н           | Column | 2 |

| Burst Termination         | on                         | Н                | Х  | L   | Н   | Н  | L   | Х  | Х              | Х           | Х      | 3 |

| No Operation              |                            | Н                | Х  | L   | Н   | Н  | Н   | Х  | Х              | Х           | Х      |   |

| Device Deselec            | t                          | Н                | Х  | Н   | Х   | Х  | Х   | Х  | Х              | Х           | Х      |   |

| Clock Suspend/            | Clock Suspend/Standby Mode |                  | Х  | Х   | Х   | Х  | Х   | Х  | Х              | Х           | Х      | 4 |

| Data Write/Output Disable |                            | Н                | Х  | Χ   | Х   | Х  | Х   | L  | Х              | Х           | Х      | 5 |

| Data Mask/Outp            | Data Mask/Output Disable   |                  | Х  | Χ   | Х   | Х  | Х   | Н  | Х              | Х           | Х      | 5 |

| Power Down M              | Entry                      |                  | L  | Н   | Х   | Х  | Х   | Х  | Х              | Х           | Х      | 6 |

| I OME! DOMIN              | Exit                       |                  | Н  | Н   | Х   | Х  | Х   | Х  | Х              | Х           | Х      | 6 |

### NOTES:

- 1. All of the SDRAM operations are defined by states of  $\overline{\text{CE}}$ ,  $\overline{\text{WE}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ , and DQM at the positive rising edge of the clock.

- 2. Bank Select (BA), if BA = 0 then bank A is selected, if BA = 1 then bank B is selected.

- During a Burst Write cycle there is a zero clock delay, for a Burst Read cycle the delay is equal to the CAS latency.

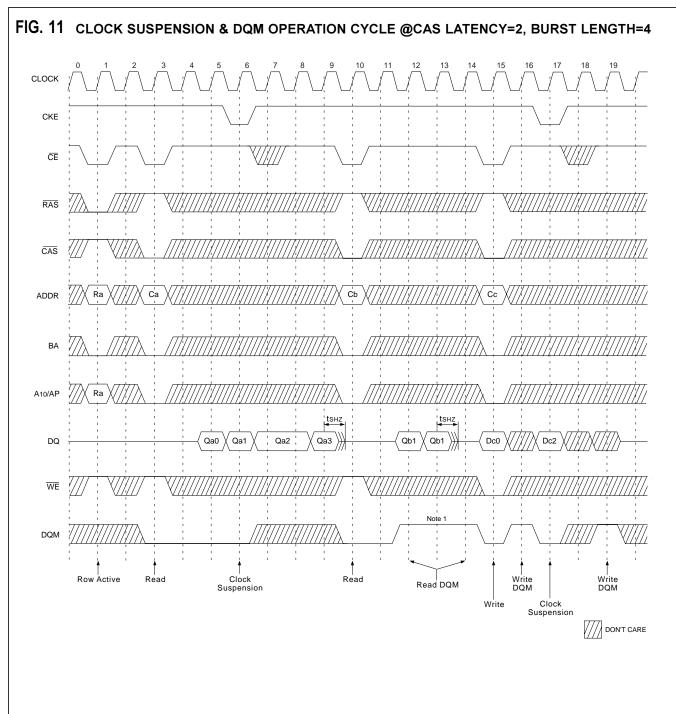

During normal access mode, CKE is held high and CLK is enabled. When it is low, it freezes the internal clock and extends data Read and Write operations. One clock delay is required for mode entry and exit.

- 5. The DQM has two functions for the data DQ Read and Write operations. During a Read cycle, when DQM goes high at a clock timing the data outputs are disabled and become high impedance after a two clock delay. DQM also provides a data mask function for Write cycles. When it activates, the Write operation at the clock is prohibited (zero clock latency).

All banks must be precharged before entering the Power Down Mode. The Power Down Mode does not preform any Refresh operations, therefore the device can't remain in this mode longer than the Refresh period (tREF) of the device. One clock delay is required for mode entry and exit.

## CLOCK ENABLE (CKE0) TRUTH TABLE

|                   | CI                | (E               |    |     | Comr | nand |                   |                |                                                                     |       |

|-------------------|-------------------|------------------|----|-----|------|------|-------------------|----------------|---------------------------------------------------------------------|-------|

| Current State     | Previous<br>Cycle | Current<br>Cycle | CE | RAS | CAS  | WE   | BA <sub>0-1</sub> | <b>A</b> 10-11 | Action                                                              | Notes |

|                   | Н                 | Х                | Х  | Х   | Х    | Х    | Х                 | Х              | INVALID                                                             | 1     |

|                   | L                 | Н                | Н  | Х   | Х    | Х    | Х                 | Х              | Exit Self Refresh with Device Deselect                              | 2     |

|                   | L                 | Н                | L  | Н   | Н    | Н    | Х                 | Х              | Exit Self Refresh with No Operation                                 | 2     |

| Self Refresh      | L                 | Н                | L  | Н   | Н    | L    | Х                 | Х              | ILLEGAL                                                             | 2     |

|                   | L                 | Н                | L  | Н   | L    | Х    | Х                 | X              | ILLEGAL                                                             | 2     |

|                   | L                 | Н                | L  | L   | Х    | Х    | Х                 | X              | ILLEGAL                                                             | 2     |

|                   | L                 | L                | Χ  | Х   | Х    | Х    | Х                 | Х              | Maintain Self Refresh                                               |       |

|                   | Н                 | Х                | Х  | Х   | Х    | Х    | Х                 | Х              | INVALID                                                             | 1     |

| Power Down        | L                 | Н                | Н  | Х   | Х    | Х    | Х                 | Х              | Power Down Mode exit, all banks idle                                | 2     |

| Fower Down        | L                 | Н                | L  | Х   | Х    | Х    | Х                 | Х              | ILLEGAL                                                             | 2     |

|                   | Н                 | Х                | L  | Н   | L    | L    | Х                 |                | Maintain Power Down Mode                                            | 2     |

|                   | Н                 | Н                | Н  | Х   | Х    | Х    |                   |                | 5                                                                   |       |

|                   | Н                 | Н                | L  | Н   | Х    | Х    |                   |                | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                   | Н                 | Н                | L  | L   | Н    | Х    |                   |                |                                                                     |       |

|                   | Н                 | Н                | L  | L   | L    | Н    | Х                 | Х              | CBR Refresh                                                         |       |

|                   | Н                 | Н                | L  | L   | L    | L    | OP                | Code           | Mode Register Set                                                   | 4     |

| All Banks Idle    | Н                 | L                | Н  | Х   | Х    | Х    |                   |                | 5                                                                   |       |

|                   | Н                 | L                | L  | Н   | Х    | Х    |                   |                | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                   | Н                 | L                | L  | L   | Н    | Х    |                   |                | oundin state than table                                             |       |

|                   | Н                 | L                | L  | L   | L    | Н    | Х                 | X              | Entry Self Refresh                                                  | 4     |

|                   | Н                 | Н                | L  | L   | L    | L    | OP                | Code           | Mode Register Set                                                   |       |

|                   | L                 | Х                | Х  | Х   | Х    | Х    | Х                 | Х              | Power Down                                                          | 4     |

|                   | Н                 | Н                | Х  | Х   | Х    | Х    | Х                 | Х              | Refer to the Operations in the Current<br>State Truth Table         |       |

| Any State other   | Н                 | L                | Х  | Х   | Х    | Х    | Х                 | Х              | Begin Clock Suspend next cycle                                      | 5     |

| than listed above | L                 | Н                | Х  | Х   | Х    | Х    | Х                 | Х              | Exit Clock Suspend next cycle                                       |       |

|                   | L                 | L                | Х  | Х   | Х    | Х    | Х                 | Х              | Maintain Clock Suspend                                              |       |

### NOTES:

- 1. For the given Current State CKE must be low in the previous cycle.

- 2. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. The minimum setup time for CKE (tcks) must be satisfied before any command other than Exit is issued.

- 3. The address inputs (A<sub>11</sub>-A<sub>0</sub>) depend on the command that is issued. See the Idle State section of the Current State Truth Table for more information.

- 4. The Power Down Mode, Self Refresh Mode, and the Mode Register Set can only be entered from the all banks idle state.

Must be a legal command as defined in the Current State Truth Table.

## **CURRENT STATE TRUTH TABLE**

|                |    |     |     | Comma  | and                 |                   |                                        |                                          |       |

|----------------|----|-----|-----|--------|---------------------|-------------------|----------------------------------------|------------------------------------------|-------|

| Current State  | CE | RAS | CAS | WE     | B <b>A</b> 0-1      | A11,<br>A10/AP-A0 | Description                            | Action                                   | Notes |

|                | L  | L   | L   | L      | OF                  | Code              | Mode Register Set                      | Set the Mode Register                    | 2     |

|                | L  | L   | L   | Н      | Х                   | Х                 | Auto or Self Refresh                   | Start Auto orSelf Refresh                | 2,3   |

|                | L  | L   | Н   | L      | Х                   | Х                 | Precharge                              | No Operation                             |       |

|                | L  | L   | Н   | Н      | BA                  | Row Address       | Bank Activate                          | Activate the specified bank and row      |       |

| Idle           | L  | Н   | L   | L      | BA                  | Column            | Write w/o Precharge                    | ILLEGAL                                  | 4     |

|                | L  | Н   | L   | Н      | BA                  | Column            | Read w/o Precharge                     | ILLEGAL                                  | 2     |

|                | L  | Н   | Н   | L      | Х                   | Х                 | Burst Termination                      | No Operation                             | 2     |

|                | L  | Н   | Н   | Н      | Х                   | Χ                 | No Operation                           | No Operation                             |       |

|                | Н  | X   | Х   | Х      | X X Device Deselect |                   | Device Deselect                        | No Operation or Power Down               | 5     |

|                | L  | L   | L   | L      | OI                  | Code              | Mode Register Set                      | ILLEGAL                                  |       |

|                | L  | L   | L   | Н      | Х                   | Х                 | Auto or Self Refresh                   | ILLEGAL                                  |       |

|                | L  | L   | Н   | L      | Х                   | Х                 | Precharge                              | Precharge                                | 6     |

|                | L  | L   | Н   | Н      | BA                  | Row Address       | Bank Activate                          | ILLEGAL                                  | 2     |

| Row Active     | L  | Н   | L   | L      | BA                  | Column            | Write                                  | Start Write; Determine if Auto Precharge | 7,8   |

|                | L  | Н   | L   | Н      | BA                  | Column            | Read                                   | Start Read; Determine if Auto Precharge  | 7,8   |

|                | L  | Н   | Н   | L      | Х                   | Х                 | Burst Termination                      | No Operation                             |       |

|                | L  | Н   | Н   | Н      | Х                   | Х                 | No Operation                           | No Operation                             |       |

|                | Н  | Х   | Х   | Х      | Х                   | Х                 | Device Deselect                        | No Operation                             |       |

|                | L  | L   | L   | L      |                     | Code              | Mode Register Set                      | ILLEGAL                                  |       |

|                | L  | L   | L   | Н      | Х                   | Х                 | Auto or Self Refresh                   | ILLEGAL                                  |       |

|                | L  | L   | Н   | L      | X                   | X                 | Precharge                              | Terminate Burst; Start the Precharge     |       |

|                | L  | L   | Н   | Н      | BA                  | Row Address       | Bank Activate                          | ILLEGAL                                  | 4     |

| Read           | L  | Н   | L   | L      | BA                  | Column            | Write                                  | Terminate Burst; Start the Write cycle   | 8,9   |

|                | Ī  | Н   | L   | Н      | BA                  | Column            | Read                                   | Terminate Burst; Start a new Read cycle  | 8,9   |

|                | L  | H   | H   | L      | X                   | X                 | Burst Termination                      | Terminate the Burst                      | 0,0   |

|                |    | Н   | Н   | H      | X                   | X                 | No Operation                           | Continue the Burst                       |       |

|                | Н  | Х   | X   | X      | X                   | X                 | Device Deselect                        | Continue the Burst                       |       |

|                | L  | L   | L   | L      |                     | Code              | Mode Register Set                      | ILLEGAL                                  |       |

|                | L  | L   | L   | Н      | Х                   | X                 | Auto or Self Refresh                   | ILLEGAL                                  |       |

|                | L  | L   | H   | L      | X                   | X                 | Precharge                              | Terminate Burst; Start the Precharge     |       |

|                | L  | L   | Н Н | Н      | BA                  | Row Address       | Bank Activate                          | ILLEGAL                                  | 4     |

| Write          | L  | Н   | L   | L      | BA                  | Column            | Write                                  | Terminate Burst; Start a new Write cycle | 8,9   |

| VVIILE         | L  | Н Н | L   | Н      | BA                  | Column            | Read                                   | Terminate Burst; Start the Read cycle    | 8,9   |

|                | L  | Н Н | Н   | L      | X                   | X                 | Burst Termination                      | Terminate the Burst                      | 0,3   |

|                | L  | Н Н | Н Н | Н      | X                   | X                 | No Operation                           | Continue the Burst                       |       |

|                | Н  | X   | X   | X      | X                   | X                 | Device Deselect                        | Continue the Burst                       |       |

|                | L  |     |     |        |                     |                   |                                        |                                          |       |

|                | -  | L   | L   | L<br>H | X                   | Code X            | Mode Register Set  Auto orSelf Refresh | ILLEGAL<br>ILLEGAL                       |       |

|                | L  | L   | L   |        | X                   | X                 |                                        |                                          | ,     |

| D 1 111        | L  | L   | Н   | L      |                     |                   | Precharge                              | ILLEGAL                                  | 4     |

| Read with      | L  | L   | H   | H      | BA                  | Row Address       | Bank Activate                          | ILLEGAL                                  | 4     |

| Auto Precharge | L  | H   | L   | L      | BA                  | Column            | Write                                  | ILLEGAL                                  |       |

|                | L  | H   | L   | Н      | BA                  | Column            | Read                                   | ILLEGAL                                  |       |

|                | L  | H   | H   | L      | X                   | X                 | Burst Termination                      | ILLEGAL                                  | -     |

|                | L  | Н   | Н   | Н      | X                   | X                 | No Operation                           | Continue the Burst                       |       |

|                | Н  | X   | Х   | Х      | Х                   | Х                 | Device Deselect                        | Continue the Burst                       |       |

## **CURRENT STATE TRUTH TABLE (cont.)**

|                        |    | _        |     | Comma | and            |                   |                      |                                          |               |

|------------------------|----|----------|-----|-------|----------------|-------------------|----------------------|------------------------------------------|---------------|

| Current State          | CE | RAS      | CAS | WE    | B <b>A</b> 0-1 | A11,<br>A10/AP-A0 | Description          | Action                                   | Notes         |

|                        | L  | L        | L   | L     | 01             | P Code            | Mode Register Set    | ILLEGAL                                  |               |

|                        | L  | L        | L   | Н     | Х              | Х                 | Auto or Self Refresh | ILLEGAL                                  |               |

|                        | L  | L        | Н   | L     | Х              | Х                 | Precharge            | ILLEGAL                                  | 4             |

| Write with             | L  | L        | Н   | Н     | BA             | Row Address       | Bank Activate        | ILLEGAL                                  | 4             |

| Auto Precharge         | L  | Н        | L   | L     | BA             | Column            | Write                | ILLEGAL                                  |               |

|                        | L  | Н        | L   | Н     | BA             | Column            | Read                 | ILLEGAL                                  |               |

|                        | L  | Н        | Ι   | L     | Х              | Х                 | Burst Termination    | ILLEGAL                                  |               |

|                        | L  | Н        | Н   | Н     | Х              | Х                 | No Operation         | Continue the Burst                       |               |

|                        | Н  | Х        | Х   | Х     | Х              | Х                 | Device Deselect      | Continue the Burst                       |               |

|                        | L  | L        | L   | L     | OF             | Code              | Mode Register Set    | ILLEGAL                                  |               |

|                        | L  | L        | L   | Н     | Х              | Х                 | Auto or Self Refresh | ILLEGAL                                  |               |

|                        | L  | L        | Н   | L     | Х              | Х                 | Precharge            | No Operation; Bank(s) idle after tre     |               |

|                        | L  | L        | Н   | Н     | BA             | Row Address       | Bank Activate        | ILLEGAL                                  | 4             |

| Precharging            | L  | Н        | 1   | L     | BA             | Column            | Write w/o Precharge  | ILLEGAL                                  | 4             |

|                        | L  | Н.       | L   | Н     | BA             | Column            | Read w/o Precharge   | ILLEGAL                                  | 4             |

|                        | L  | Н.       | Н   | L     | X              | X                 | Burst Termination    | No Operation; Bank(s) idle after trp     | <del>  </del> |

|                        | L  | Н.       | Н   | Н     | X              | X                 | No Operation         | No Operation; Bank(s) idle after trp     |               |

|                        |    | <b> </b> | X   |       | X              | X                 |                      | , , ,                                    |               |

|                        | H  | X        |     | X     |                |                   | Device Deselect      | No Operation; Bank(s) idle after trp     |               |

|                        | L  | L        | L . | L     |                | P Code            | Mode Register Set    | ILLEGAL                                  |               |

|                        | L  | L        | L   | H     | X              | X                 | Auto or Self Refresh | ILLEGAL                                  | <u> </u>      |

|                        | L  | L        | Н   | L     | Х              | Х                 | Precharge            | ILLEGAL                                  | 4             |

|                        | L  | L        | Н   | Н     | BA             | Row Address       | Bank Activate        | ILLEGAL                                  | 4,10          |

| Row Activating         | L  | Н        | L   | L     | BA             | Column            | Write                | ILLEGAL                                  | 4             |

|                        | L  | Н        | L   | Н     | BA             | Column            | Read                 | ILLEGAL                                  | 4             |

|                        | L  | Н        | Н   | L     | Х              | Х                 | Burst Termination    | No Operation; Row active after tRCD      |               |

|                        | L  | Н        | Н   | Н     | Х              | Х                 | No Operation         | No Operation; Row active after tRCD      |               |

|                        | Н  | Х        | Χ   | Х     | Х              | Х                 | Device Deselect      | No Operation; Row active after tRCD      |               |

|                        | L  | L        | L   | L     | Ol             | P Code            | Mode Register Set    | ILLEGAL                                  |               |

|                        | L  | L        | L   | Н     | Х              | Х                 | Auto or Self Refresh | ILLEGAL                                  |               |

|                        | L  | L        | Н   | L     | Х              | Х                 | Precharge            | ILLEGAL                                  | 4             |

|                        | L  | L        | Н   | Н     | BA             | Row Address       | Bank Activate        | ILLEGAL                                  | 4             |

| Write Recovering       | L  | Н        | L   | L     | BA             | Column            | Write                | Start Write; Determine if Auto Precharge | 9             |

|                        | L  | Н        | L   | Н     | BA             | Column            | Read                 | Start Read; Determine if Auto Precharge  | 9             |

|                        | L  | Н        | Н   | L     | Х              | Х                 | Burst Termination    | No Operation; Row active after tDPL      |               |

|                        | L  | Н        | Н   | Н     | Х              | Х                 | No Operation         | No Operation; Row active after topl      |               |

|                        | Н  | Х        | Х   | Х     | Х              | Х                 | Device Deselect      | No Operation; Row active after topL      |               |

|                        | L  | L        | L   | L     |                | P Code            | Mode Register Set    | ILLEGAL                                  |               |

|                        | L  | L        | L   | Н     | Х              | X                 | Auto or Self Refresh | ILLEGAL                                  |               |

|                        | L  | L        | Н   | L     | X              | X                 | Precharge            | ILLEGAL                                  | 4             |

| Meito Deservi          | L  | L        | H   | Н     | BA             | Row Address       | Bank Activate        | ILLEGAL                                  | 4             |

| Write Recovering       |    |          |     |       |                |                   |                      | ILLEGAL                                  |               |

| with Auto<br>Precharge | L  | H        | L   | L     | BA             | Column            | Write                |                                          | 4,9           |

| i iconarye             | L  | H        | L   | H     | BA             | Column            | Read                 | ILLEGAL                                  | 4,9           |

|                        | L  | Н        | Н   | L     | X              | X                 | Burst Termination    | No Operation; Precharge after tDPL       | -             |

|                        | L  | Н        | Н   | Н     | X              | X                 | No Operation         | No Operation; Precharge after tDPL       |               |

|                        | Н  | X        | Х   | Х     | Х              | Х                 | Device Deselect      | No Operation; Precharge after topL       |               |

## **CURRENT STATE TRUTH TABLE (cont.)**

|               | Command |     |     |    |                   |                   |                      |                                           |       |

|---------------|---------|-----|-----|----|-------------------|-------------------|----------------------|-------------------------------------------|-------|

| Current State | CE      | RAS | CAS | WE | BA <sub>0-1</sub> | A11,<br>A10/AP-A0 | Description          | Action                                    | Notes |

|               | L       | L   | L   | L  | OF                | Code              | Mode Register Set    | ILLEGAL                                   |       |

| Refreshing    | L       | L   | L   | Н  | Х                 | Х                 | Auto or Self Refresh | ILLEGAL                                   |       |

|               | L       | L   | Н   | L  | Х                 | Х                 | Precharge            | ILLEGAL                                   |       |

|               | L       | L   | Н   | Н  | BA                | Row Address       | Bank Activate        | ILLEGAL                                   |       |

|               | L       | Н   | L   | L  | BA                | Column            | Write                | ILLEGAL                                   |       |

|               | L       | Н   | L   | Н  | BA                | Column            | Read                 | ILLEGAL                                   |       |

|               | L       | Н   | Н   | L  | Х                 | Х                 | Burst Termination    | No Operation; Idle after tRc              |       |

|               | L       | Н   | Н   | Н  | Х                 | Х                 | No Operation         | No Operation; Idle after tRc              |       |

|               | Н       | Х   | Χ   | Х  | Х                 | Х                 | Device Deselect      | No Operation; Idle after tRc              |       |

|               | L       | L   | L   | L  | OF                | <sup>o</sup> Code | Mode Register Set    | Load mode register                        |       |

|               | L       | L   | L   | Н  | Х                 | Х                 | Auto or Self Refresh | ILLEGAL                                   |       |

|               | L       | L   | Н   | L  | Х                 | Х                 | Precharge            | ILLEGAL                                   |       |

| Mode Register | L       | L   | Н   | Н  | BA                | Row Address       | Bank Activate        | ILLEGAL                                   |       |

| Accessing     | L       | Н   | L   | L  | BA                | Column            | Write                | ILLEGAL                                   |       |

|               | L       | Н   | L   | Н  | BA                | Column            | Read                 | ILLEGAL                                   |       |

|               | L       | Н   | Н   | L  | Х                 | Х                 | Burst Termination    | ILLEGAL                                   |       |

|               | L       | Н   | Н   | Н  | Х                 | Х                 | No Operation         | No Operation; Idle after two clock cycles |       |

|               | Н       | Х   | Х   | Х  | Х                 | Х                 | Device Deselect      | No Operation; Idle after two clock cycles |       |

### NOTES:

- 1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the command is being applied to.

- 2. Both Banks must be idle otherwise it is an illegal action.

- 3. If CKE is active (high) the SDRAM starts the Auto (CBR) Refresh operation, if CKE is inactive (low) then the Self Refresh mode is entered.

- 4. The Current State refers only refers to one of the banks, if BA selects this bank then the action is illegal. If BA selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

- 5. If CKE is inactive (low) than the Power Down mode is entered, otherwise there is a No Operation.

- 6. The minimum and maximum Active time (tras) must be satisfied.

- 7. The RAS to CAS Delay (tRCD) must occur before the command is given.

- 8. Address A10 is used to determine if the Auto Precharge function is activated.

- 9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

The command is illegal if the minimum bank to bank delay time (trrd) is not satisfied.

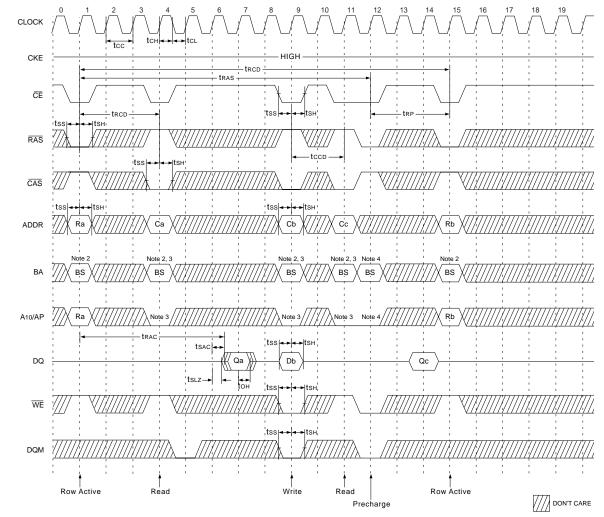

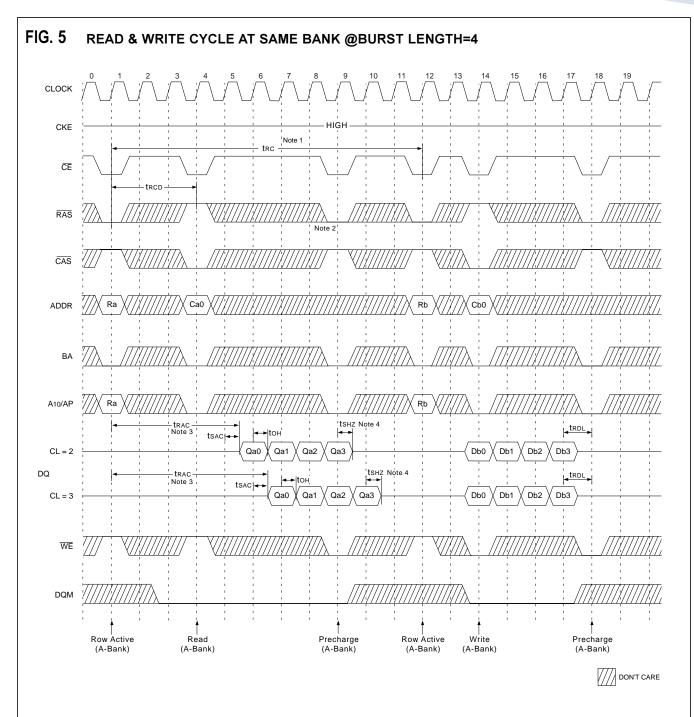

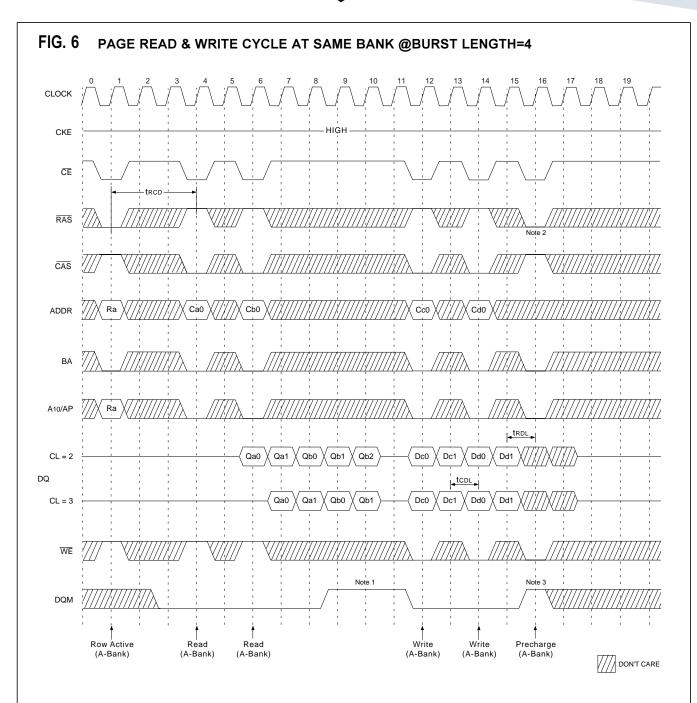

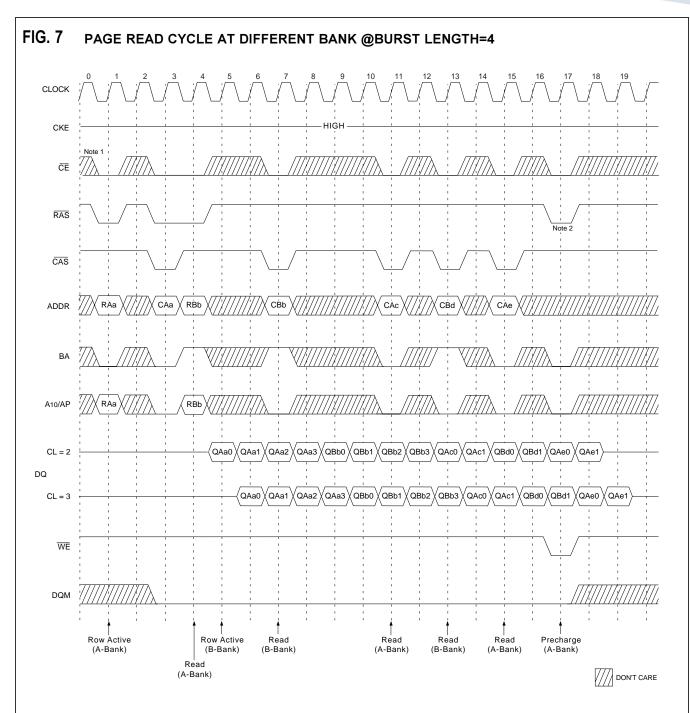

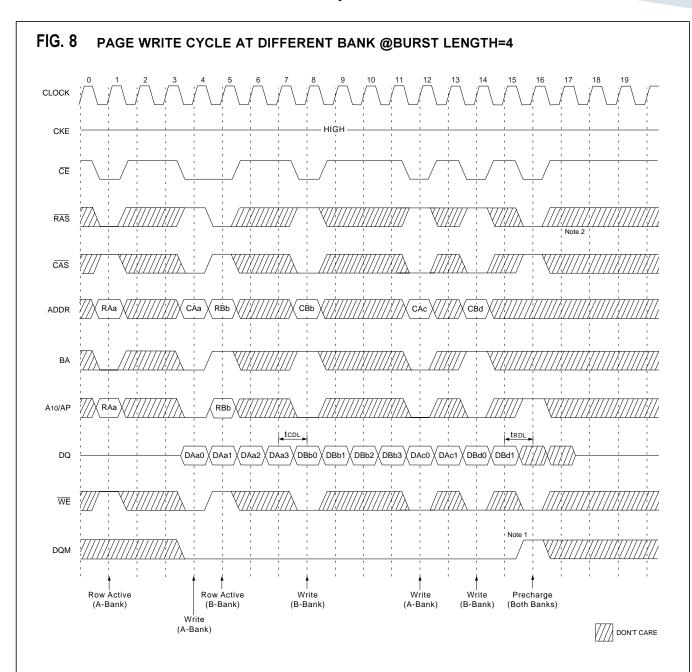

## FIG. 3 SINGLE BIT READ-WRITE CYCLE (SAME PAGE) @CAS LATENCY=3, BURST LENGTH=1

### NOTES:

- All input except CKE & DQM can be don't care when CE is high at the CLK high going edge.

- 2. Bank active & read/write are controlled by BA0~BA1.

| BA0 | BA1 | Active & Read/Write |

|-----|-----|---------------------|

| 0   | 0   | Bank A              |

| 0   | 1   | Bank B              |

| 1   | 0   | Bank C              |

| 1   | 1   | Bank D              |

4. A10/AP and BA0~BA1 control bank precharge when precharge command is asserted.

| A10/AP | BA0 | BA1 | Precharge |

|--------|-----|-----|-----------|

| 0      | 0   | 0   | Bank A    |

| 0      | 0   | 1   | Bank B    |

| 0      | 1   | 0   | Bank C    |

| 0      | 1   | 1   | Bank D    |

| 1      | Х   | Х   | All Banks |

Enable and disable auto precharge function are controlled by A10/AP in read/write command.

| A10/AP | BA0 | BA1 | Operation                                                       |  |  |

|--------|-----|-----|-----------------------------------------------------------------|--|--|

|        | 0   | 0   | Distribute auto precharge, leave bank A active at end of burst. |  |  |

|        | 0   | 1   | Disable auto precharge, leave bank B active at end of burst.    |  |  |

| 0      | 1   | 0   | Disable auto precharge, leave bank C active at end of burst.    |  |  |

|        | 1   | 1   | Disable auto precharge, leave bank D active at end of burst.    |  |  |

|        | 0   | 0   | Enable auto precharge, precharge bank A at end of burst.        |  |  |

| 1      | 0   | 1   | Enable auto precharge, precharge bank B at end of burst.        |  |  |

| '      | 1   | 0   | Enable auto precharge, precharge bank C at end of burst.        |  |  |

|        | 1   | 1   | Enable auto precharge, precharge bank D at end of burst.        |  |  |

- 1. Minimum row cycle times are required to complete internal DRAM operation.

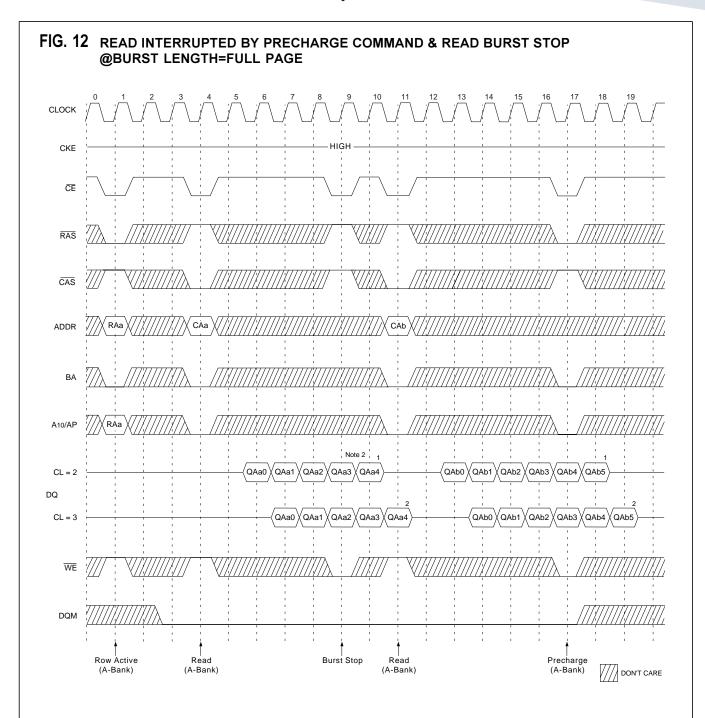

- 2. Row precharge can interrupt burst on any cycle. (CAS Latency 1) number of valid output data is available after Row precharge. Last valid output will be Hi-Z(tsHz) after the clock.

- 3. Access time from Row active command. tcc \*(trcd + CAS | atency 1) + tsac.

- 4. Output will be Hi-Z after the end of burst (1, 2, 4, 8 & full page bit burst).

- To write data before burst read ends, DQM should be asserted three cycles prior to write command to avoid bus contention.

- 2. Row precharge will interrupt writing. Last data input, tRDL before Row precharge, will be written.

- DQM should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle will be masked internally.

- 1.  $\overline{\text{CE}}$  can be don't care when  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$  and  $\overline{\text{WE}}$  are high at the clock high going edge.

- 2. To interrupt a burst read by row precharge, both the read and the precharge banks must be the same.

- 1. To interrupt burst write by Row precharge, DQM should be asserted to mask invalid input data.

- 2. To interrupt burst write by Row precharge, both the write and the precharge banks must be the same.

## NOTE:

1. DQM is needed to prevent bus contention.

- 1. At full page mode, burst is end at the end of burst. So auto precharge is possible.

- 2. About the valid DQs after burst stop, it is same as the case of RAS interrupt. Both cases are illustrated in above timing diagram. See the label 1, 2. But at burst write, Burst stop and RAS interrupt should be compared carefully. Refer to the timing diagram of "Full page write burst stop cycle."

- 3. Burst stop is valid at every burst length.

- 1. At full page mode, burst is end at the end of burst. So auto precharge is possible.

- 2. Data-in at the cycle of interrupted by precharge cannot be written into the corresponding memory cell. It is defined by AC parameter of thot.

DQM at write interrupted by precharge command is needed to prevent invalid write.

DQM should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle will be masked internally.

- 3. Burst stop is valid at every burst length.

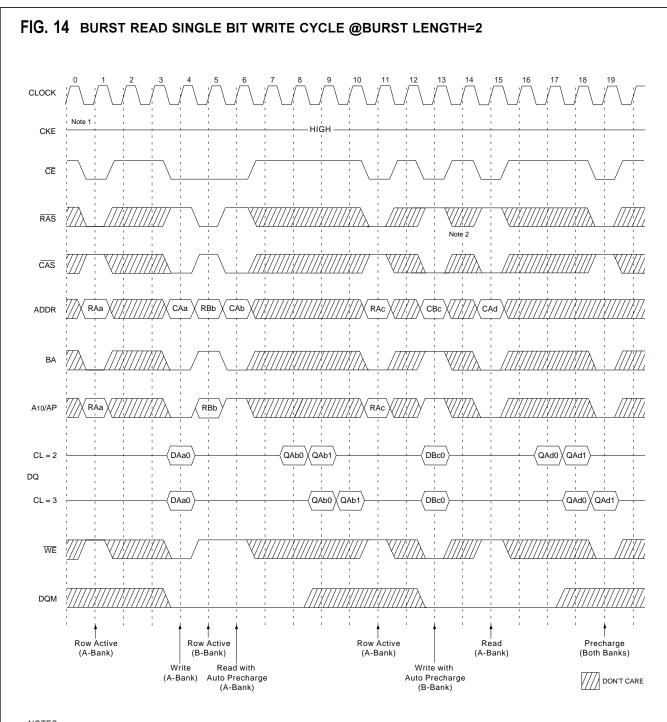

- 1. BRSW mode is enabled by setting A9 "High" at MRS (Mode Register Set). At the BRSW Mode, the burst length at write is fixed to "1" regardless of programmed burst length.

- When BRSW write command with auto precharge is executed, keep it in mind that tras should not be violated. Auto precharge is executed at the burst-end cycle, so in the case of BRSW write command, the next cycle starts the precharge.

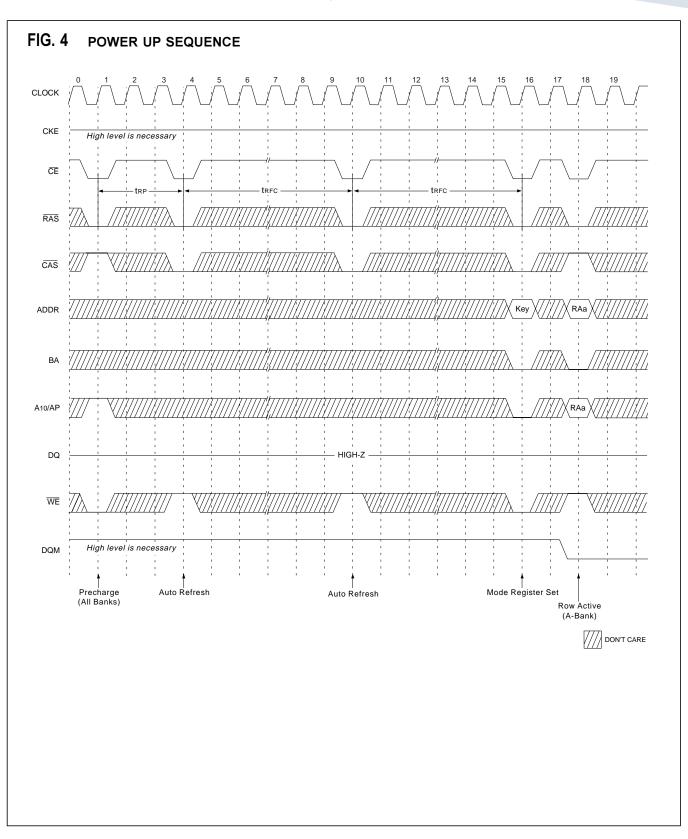

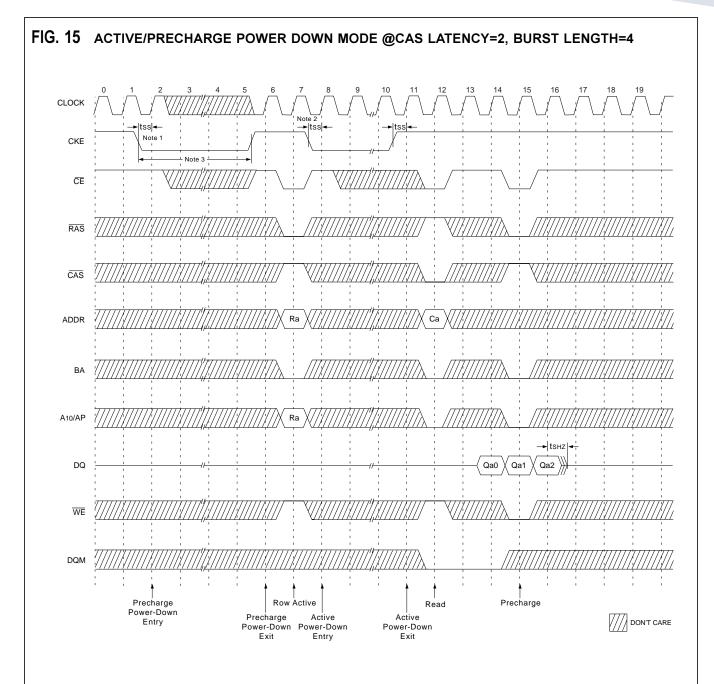

- 1. Both banks should be in idle state prior to entering precharge power down mode.

- 2. CKE should be set high at least 1 CLK + tss prior to Row active command.

- 3. Cannot violate minimum refresh specification (64ms).

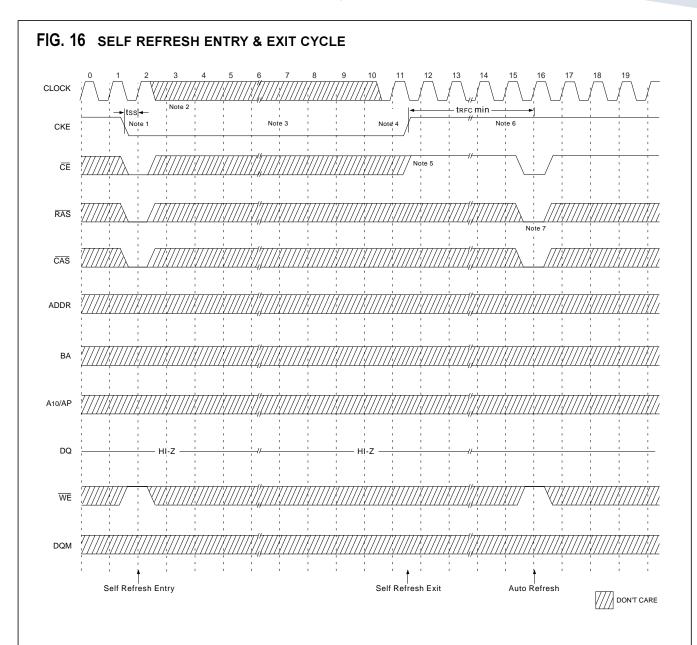

## TO ENTER SELF REFRESH MODE

- 1.  $\overline{\text{CE}}$ ,  $\overline{\text{RAS}}$  &  $\overline{\text{CAS}}$  with CKE should be low at the same clock cycle.

- 2. After 1 clock cycle, all the inputs including the system clock can be don't care except for CKE.

- 3. The device remains in self refresh mode as long as CKE stays "Low."

Once the device enters self refresh mode, minimum tras is required before exit from self refresh.

## TO EXIT SELF REFRESH MODE

- 4. System clock restart and be stable before returning CKE high.

- 5. CE starts from high.

- 6. Minimum trace is required after CKE going high to complete self refresh exit.

- 7. 4K cycle of burst auto refresh is required before self refresh entry and after self refresh exit if the system uses burst refresh.

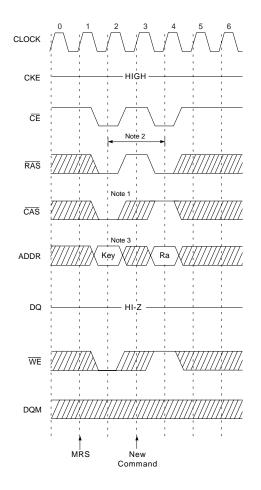

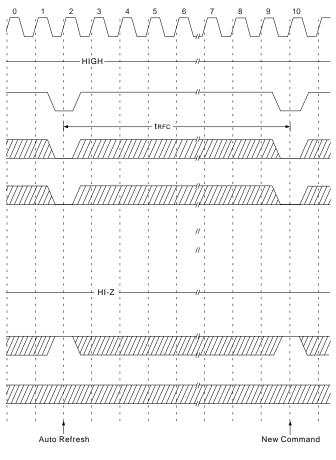

# FIG. 17 MODE REGISTER SET CYCLE

# FIG. 18 AUTO REFRESH CYCLE

DON'T CARE

### NOTES:

Both banks precharge should be completed before Mode Register Set cycle and auto refresh cycle.

## MODE REGISTER SET CYCLE

- 1.  $\overline{\text{CE}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ , &  $\overline{\text{WE}}$  activation at the same clock cycle with address key will set internal mode register.

- 2. Minimum 2 clock cycles should be met before new RAS activation.

- 3. Please refer to Mode Register Set table.

## ORDERING INFORMATION

| PART NUMBER    | CLOCK FREQUENCY | PACKAGE |

|----------------|-----------------|---------|

| WED3DL324V7BC  | 133MHZ          | 119 BGA |

| WED3DL324V8BC  | 125MHZ          | 119 BGA |

| WED3DL324V10BC | 100MHZ          | 119 BGA |