# W3041 IF Receiver with Integrated IF2 Bandpass Filters

#### **Features**

- Root Nyquist approximation 400 kHz or 450 kHz bandpass filters specified for PDC 25 kHz channel and baseband

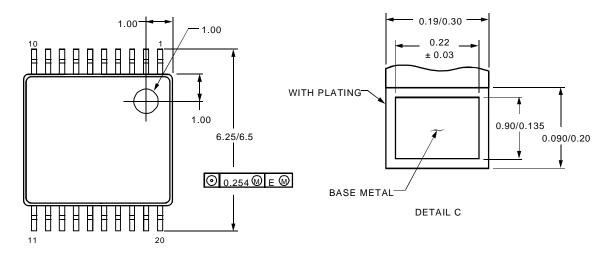

- Small, 20-pin TSSOP package

- Low supply current for long battery life

- Wide-range RSSI

- High-gain limiter

- Low-noise, image-reject IF mixer

- Minimum external components

# **Applications**

■ PDC 800 MHz and PDC 1500 MHz (Japan RCR STD-27) portable receivers

# Description

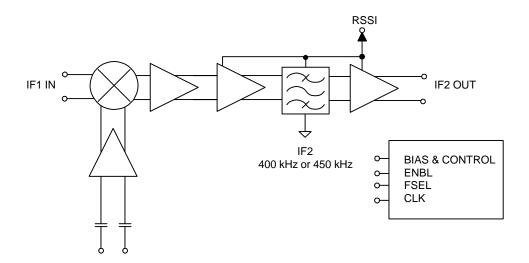

The W3041 is intended for application in cellular telephone receivers made for the Japan Personal Digital Cellular (TDMA PDC) phones. It provides the following functionality:

- IF1 mixer for translating a first IF (IF1) of 120 MHz to 200 MHz to a second IF (IF2) of 400 kHz or 450 kHz

- Integrated active IF2 bandpass filters providing selectivity, phase linearity, and dynamic range sufficient to replace conventional ceramic filters, with center frequency of 400 kHz or 450 kHz (switchable)

- Limiting RSSI amplifier strip for the IF2 filter output

- A local oscillator input buffer with on-chip coupling capacitors

Figure 1. Circuit Block Diagram

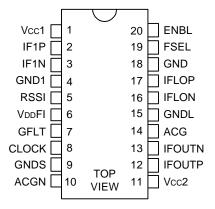

# **Pin Information**

Figure 2. Pin Configuration

**Table 1. Pin Descriptions**

| Pin | Name   | Function                                                                                                             |

|-----|--------|----------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc1   | IF mixer positive power supply                                                                                       |

| 2   | IF1P   | IF1 input (differential input)                                                                                       |

| 3   | IF1N   | IF1 input (differential input)                                                                                       |

| 4   | GND1   | Power supply ground for IF mixer                                                                                     |

| 5   | RSSI   | RSSI output                                                                                                          |

| 6   | VDDFI  | Active filter positive power supply                                                                                  |

| 7   | GFLT   | Ground for integrated filter                                                                                         |

| 8   | CLOCK  | Input for integrated IF2 filter timing clock                                                                         |

| 9   | GNDS   | Substrate ground for second IF section                                                                               |

| 10  | ACGN   | ac ground for limiting amplifier (through external capacitor to pin 14)                                              |

| 11  | Vcc2   | Positive power supply for second IF section                                                                          |

| 12  | IFOUTP | IF2 limiting amplifier output (differential)                                                                         |

| 13  | IFOUTN | IF2 limiting amplifier output (differential)                                                                         |

| 14  | ACG    | ac ground for limiting amplifier (through external capacitor to pin 10)                                              |

| 15  | GNDL   | Power supply ground for LO input buffer                                                                              |

| 16  | IFLON  | IF mixer local oscillator input (differential)                                                                       |

| 17  | IFLOP  | IF mixer local oscillator input (differential)                                                                       |

| 18  | GND    | Ground (no internal connection)                                                                                      |

| 19  | FSEL   | Filter frequency select logic input                                                                                  |

| 20  | ENBL   | Logic enable for all circuits and initiator for calibration of integrated IF2 filter (See Table 5 for requirements.) |

#### Pin Information (continued)

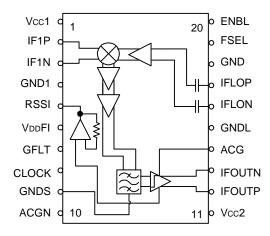

Figure 3 illustrates the pinout interconnections.

Figure 3. Package Footprint

## **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                          | Symbol | Min             | Max  | Unit |

|------------------------------------|--------|-----------------|------|------|

| Ambient Operating Temperature      | TA     | -30             | 100  | °C   |

| Storage Temperature                | Tstg   | <del>-</del> 65 | 150  | °C   |

| Lead Temperature (soldering, 10 s) | _      | _               | 300  | °C   |

| Positive Supply Voltage            | Vcc    | -0.3            | 4.5  | V    |

| Power Dissipation                  | PD     |                 | 100  | mW   |

| ac Peak Input Voltages             | _      | -0.3            | ≤Vcc | Vdc  |

| Digital Voltages                   | _      | -0.3            | ≤Vcc | Vdc  |

# **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent Technologies Microelectronics Group employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the model. No industry-wide standard has been adopted for CDM. However, a standard HBM (resistance =  $1500 \Omega$ , capacitance = 100 pF) is widely used and, therefore, can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters:

| Model                | Rating | Unit |

|----------------------|--------|------|

| HBM                  | TBD    | V    |

| CDM (corner pins)    | TBD    | V    |

| CDM (no corner pins) | TBD    | V    |

# **Operating Ranges**

The W3041 operating ranges are shown in Table 2. Performance is not guaranteed over the full range of all conditions possible within this table. However, the table lists the ranges of external conditions in which the W3041 provides general functionality, which may be useful in specific applications, without risk of permanent damage. The conditions for guaranteed performance are described in Tables 3 and 4.

**Table 2. Operating Ranges**

| Parameter                                                                                                   | Symbol | Min | Тур        | Max | Unit  |

|-------------------------------------------------------------------------------------------------------------|--------|-----|------------|-----|-------|

| Operating Temperature (ambient air; does not include PCB heating)                                           | TA     | -30 | 25         | 85  | °C    |

| Nominal Operating Voltage                                                                                   | Vcc    | 2.7 | _          | 3.3 | V     |

| IF1 Input Frequency                                                                                         | _      | 120 | _          | 200 | MHz   |

| IFLO Frequency (must be <f(if1))< td=""><td>_</td><td>120</td><td>_</td><td>200</td><td>MHz</td></f(if1))<> | _      | 120 | _          | 200 | MHz   |

| IFLO Input Level                                                                                            | VLO    | 100 | 200        | _   | mVp-p |

| IF2 Frequency                                                                                               | IF2    | _   | 400 or 450 | _   | kHz   |

| Clock Input Level                                                                                           |        | 0.5 | _          | Vcc | Vp-p  |

| Clock Input Frequency                                                                                       | _      | _   | 14.4       | _   | MHz   |

## **Control Logic**

**Table 3. Binary Logic Truth Table**

1 = logic high voltage; 0 = logic low voltage.

| ENBL | FSEL | Function      |

|------|------|---------------|

| 1    | Χ    | Active Mode   |

| 0    | Χ    | Sleep Mode    |

| 1    | 1    | IF2 = 450 kHz |

| 1    | 0    | IF2 = 400 kHz |

**Table 4. Clock Frequencies**

| Clock | IF2 (kHz) |          |  |  |  |

|-------|-----------|----------|--|--|--|

| (MHz) | FSEL = 1  | FSEL = 0 |  |  |  |

| 14.4  | 450       | 400      |  |  |  |

Note: Other clock frequencies are available. Consult your Lucent Technologies Microelectronics Group Account Manager.

#### **Electrical Characteristics**

#### Table 5. dc and Digital Electrical Specifications

Conditions unless otherwise noted:  $2.7 \le VCC \le 3.3$  Vdc; TA = 25 °C  $\pm$  3 °C; RL(IFOUT) = 10 k $\Omega$ ; RL(RSSI)  $\ge 40$  k $\Omega$ ; FIF1 = 130.45 MHz; FIFLO = 130 MHz; VLO = 200 mVp-p; FIF2 = 450 kHz; FCLK = 14.4 MHz; VCLK = 0.5 Vp-p.

| Parameter                                                                                | Symbol | Min       | Тур | Max       | Unit     |

|------------------------------------------------------------------------------------------|--------|-----------|-----|-----------|----------|

| Enable Input*                                                                            |        |           |     |           |          |

| Logic High Voltage                                                                       | VIL    | 0.7 * Vcc | -   | Vcc       | V        |

| Logic Low Voltage                                                                        | VIL    | 0         |     | 0.3 * Vcc | ٧        |

| Logic High Current (VIH = 3.3 V)                                                         | lін    |           |     | 10        | μΑ       |

| Logic Low Current (VIL = 0.4 V)                                                          | lı∟    | _         | _   | 10        | μA       |

| Powerup Time (enable low to high): Filter Calibration <sup>†</sup> Other Circuits (RSSI) |        | 1 1       |     | 12<br>180 | μs<br>μs |

| Power Supply Current                                                                     |        |           |     |           |          |

| Active Mode, Vcc = 3.0, ENBL ≥ 2.1 Vdc                                                   | Icc    | _         | 7.0 | _         | mA       |

| Sleep Mode, Vcc = 3.3, ENBL = 0.1 Vdc                                                    | IPDN   | _         | 0.5 | _         | μΑ       |

<sup>\*</sup> To ensure normal operation of the integrated filter, enable voltage (pin 20) must be <1.4 Vdc until Vcc1 = Vcc2 = Vdc (pins 1, 6, 11).

#### Table 6. ac Specifications

Conditions unless otherwise noted:  $2.7 \le VCC \le 3.3 \text{ Vdc}$ ; TA = 25 °C ± 3 °C; RL(IFOUT) = 10 k $\Omega$ ; RL(RSSI)  $\ge 40 \text{ k}\Omega$ ; FIF1 = 130.45 MHz; FIFLO = 130 MHz; VLO = 200 mVp-p; FIF2 = 450 kHz; FCLK = 14.4 MHz; VCLK = 0.5 Vp-p.

| Parameter                                                 | Symbol                                              | Min | Typical | Max             | Unit |  |  |

|-----------------------------------------------------------|-----------------------------------------------------|-----|---------|-----------------|------|--|--|

| Overall Cascaded Specifications (IF1 in to IF2 of         | Overall Cascaded Specifications (IF1 in to IF2 out) |     |         |                 |      |  |  |

| Overall Noise Figure                                      | NF                                                  |     | 15      | _               | dB   |  |  |

| Overall Input-referred IP3 (true power)                   | IIP3                                                |     | -19     | _               | dBm  |  |  |

| Gain Variation within ±9 kHz Deviation (amplitude ripple) |                                                     | 1   | <0.1    | _               | dB   |  |  |

| Overall Group Delay Variation, at  F - Fc  < 10 kHz       |                                                     |     | 18      | _               | μs   |  |  |

| IF1 Mixer Specifications                                  |                                                     |     |         |                 |      |  |  |

| Noise Figure                                              | NF                                                  | _   | 11      | _               | dB   |  |  |

| IF1 Input –1 dB Compression Point (true power)            | P(-1 dB)                                            |     |         | _               | dBm  |  |  |

| Isolation, IFLO to IF1 IN (bidirectional)                 | _                                                   |     |         | -35             | dB   |  |  |

| Image Rejection (reduction of gain for IF1 = IFLO – IF2)  |                                                     |     | -30     | <del>-</del> 25 | dB   |  |  |

<sup>†</sup> Begins when 1.4 < VENBL < (0.7 \* VCc) and Vcc1 = Vcc2 = VDDFI > 2.5 Vdc. CLK signal must be present at > 0.5 Vp-p.

# **Electrical Characteristics** (continued)

#### Table 6. ac Specifications (continued)

Conditions unless otherwise noted:  $2.7 \le VCC \le 3.3$  Vdc; TA = 25 °C  $\pm 3$  °C; RL(IFOUT) = 10 k $\Omega$ ; RL(RSSI) > 40 k $\Omega$ ; FIF1 = 130.45 MHz; FIFLO = 130 MHz; VLO = 200 mVp-p; FIF2 = 450 kHz; FCLK = 14.4 MHz; VCLK = 0.5 Vp-p.

| Parameter                                                                                                                                                       | Symbol | Min       | Тур      | Max      | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|----------|----------|----------|

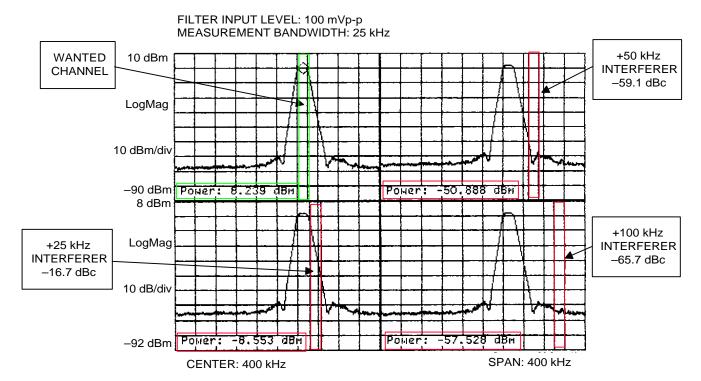

| <b>IF2 Filters</b> (performance of all sections combined in cascade; measurement bandwidth 25 kHz, with minimum clock input level = 0.5 Vp-p clipped sine wave) |        |           |          |          |          |

| Clock Input Impedance (complex magnitude)                                                                                                                       | _      | _         | 7500     | _        | Ω        |

| Rejection at Fc ± 25 kHz                                                                                                                                        | _      | 16        | 19       | _        | dB       |

| Rejection at Fc ± 50 kHz                                                                                                                                        | _      | 50        | 57       | _        | dB       |

| Rejection at Fc ± 100 kHz                                                                                                                                       | _      | 52        | 65       | _        | dB       |

| Rejection at Fc ± 200 kHz                                                                                                                                       | _      | 50        | 65       | _        | dB       |

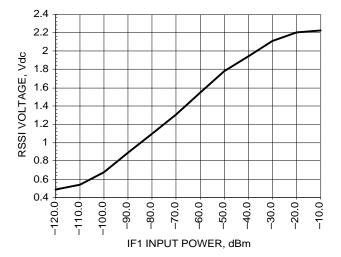

| IF2 Limiting Amplifiers, RSSI                                                                                                                                   |        |           |          |          |          |

| IF2 Output Voltage (ac load RL $\geq$ 10 kΩ, dc load RL $\geq$ 100 kΩ), Differential (divide by 2 for single-ended voltage)                                     | _      | 1.4       | _        | 2.2      | Vp-p     |

| IF2 Output Duty Cycle (sine input)                                                                                                                              | _      | 45        | 50       | 55       | %        |

| IF2 Output Rise or Fall Time (10% to 90%; ac load RL $\geq$ 10 kΩ, dc load RL $\geq$ 100 kΩ)                                                                    | _      | _         | 40       | 100      | ns       |

| RSSI Range (input power)                                                                                                                                        | _      | _         | 90       | _        | dB       |

| RSSI dc Output Range (VMAX – VMIN)                                                                                                                              | _      | _         | 1.6      | _        | Vdc      |

| RSSI Variation: -20 °C to +60 °C, -100 dBm to -40 dBm IF1 Input                                                                                                 | _      | _         | _        | 6        | dB       |

| RSSI Output for No IF1 Input Signal                                                                                                                             | _      | _         | 0.5      | TBD      | Vdc      |

| RSSI Output for –110 dBm IF1 (true power)                                                                                                                       | _      | TBD       | 0.7      | TBD      | Vdc      |

| RSSI Voltage for –70 dBm IF1 (true power)                                                                                                                       | _      | TBD       | 1.3      | TBD      | Vdc      |

| RSSI Voltage for –30 dBm IF1 (true power)                                                                                                                       | _      | TBD       | 2.0      | TBD      | Vdc      |

| RSSI Response Time (10% to 90%): Rise Time Fall Time                                                                                                            | _      |           | 20<br>20 |          | μs<br>μs |

| RSSI Enable Time (IF1 @ -60 dBm in, after VENBL exceeds 0.7 * VCC)                                                                                              |        | TBD       | 25       | TBD      | μs       |

| RSSI Linearity: -105 dBm to -60 dBm IF1 Input -60 dBm to -30 dBm IF1 Input                                                                                      | _<br>_ | –2<br>TBD |          | 2<br>TBD | dB<br>dB |

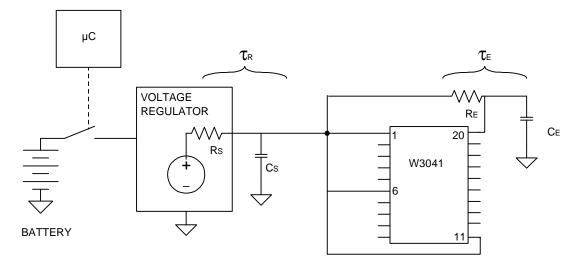

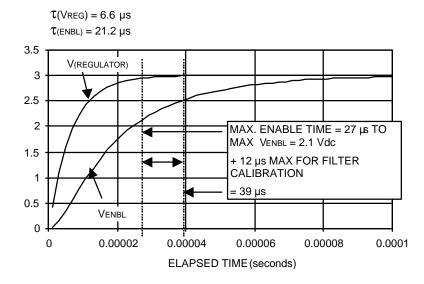

## **Enabling the Power Supply (No Direct Logic to Pin 20)**

If the W3041 application provides logic control of the voltage regulator instead of the W3041 directly, certain precautions must be taken. This is accomplished by connecting a resistor from the positive power supply (pin 1 = Vcc1, pin 6 = VddFI, and pin 11 = Vcc2) to ENBL (pin 20). It is necessary to make sure that the voltage on ENBL

(pin 20) does not exceed 0.46 VCC until the voltage on the positive supply pins (pin 1 = VCC1, pin 6 = VDDFI, and pin 11 = VCC2) is >2.5 Vdc. This requirement can be satisfied with an RC delay circuit requiring one resistor and one capacitor.

To design the RC delay circuit, it is necessary to know:

- Minimum stable voltage regulator output voltage VR

- Time constant of the voltage regulator output TR, usually established by the internal source resistance Rs and external (or internal) regulator filter capacitance (Cs)

The W3041 integrated filter uses an automatic calibration routine that takes about 8  $\mu$ s typically (12  $\mu$ s max). The calibration happens every time ENBL (pin 20) goes high. The calibration routine is initiated at the logic-high threshold (minimum = 0.46 Vcc, maximum = 0.7 Vcc). For the calibration to proceed correctly, the power supply voltage (Vcc1 = Vcc2 = VdpFI) must have risen to >2.5 Vdc.

Refer to the following circuit:

Figure 4. Power Supply Diagram

The goal is to determine the Enable Time Constant  $\tau_{E}$ , from which convenient values of RE and CE can be chosen. The following equation may be used to calculate  $\tau_{E}$ :

$$\tau_{E} = \frac{-\tau_{R} \ln \left(1 - \frac{2.5}{V_{R}}\right)}{0.616}$$

## Enabling the Power Supply (No Direct Logic to Pin 20) (continued)

Example: Suppose the voltage regulator source resistance Rs is 2  $\Omega$  and the voltage regulator output filter capacitor Cs is 3.3  $\mu$ F. The time constant  $\tau$ R is 2 \* 3.3E - 6 = 6.6  $\mu$ s. The voltage regulator output is specified as 3.0  $\pm$  0.1 Vdc, so VR = 2.9 Vdc.

$$\tau_{E} = \frac{-(6.6E - 6) \ln \left(1 - \frac{2.5}{2.9}\right)}{0.616} = (21.2E - 6) s$$

Selecting practical values for components RE and CE using RECE = 21.2E - 6 involves first selecting a standard capacitor value for CE available in small physical size such as 1000 pF. The value for RE can then be found from  $21.2E-6 \div 1000E-12 = 21.2 \text{ k}\Omega$  for which the standard value  $22 \text{ k}\Omega$  can be chosen. Using these values in an *Excel\** plot, the powerup time can be seen by inspection, as shown in Figure 5.

Figure 5. Required Enable Delay for Filter Calibration Circuit

<sup>\*</sup>Excel is a trademark of Microsoft Corporation.

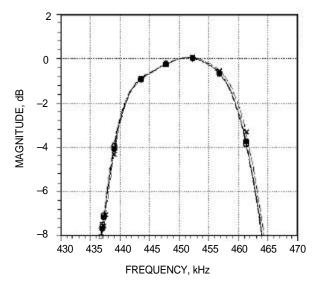

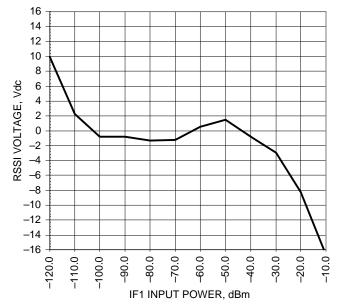

#### **Characteristic Curves**

Conditions unless otherwise noted: VCC = 2.7; IF1 = 130.45 MHz; IFLO = 130.0 MHz @ 150 mVp-p; IF2 = 400 kHz or 450 kHz; CLK = 14.40 MHz; TA = 25 °C; mixer input terminated with 50  $\Omega$  resistor.

80 60 20 0 20 420 430 440 450 460 470 480 FREQUENCY, kHz

Figure 6. 450 kHz IF2 Filter Channel Passband Magnitude

Figure 7. IF2 Bandpass Filter Group Delay Variation

Figure 8. 450 kHz IF2 Filter Rejection

# Characteristic Curves (continued)

Conditions unless otherwise noted: VCC = 2.7; IF1 = 130.45 MHz; IFLO = 130.0 MHz @ 150 mVp-p; IF2 = 400 kHz or 450 kHz; CLK = 14.40 MHz; TA = 25 °C; mixer input terminated with 50  $\Omega$  resistor.

Figure 9. RSSI Response

Figure 10. RSSI Linearity

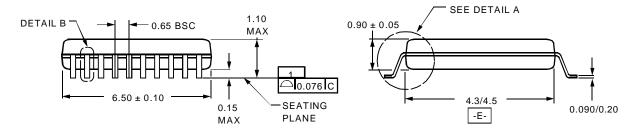

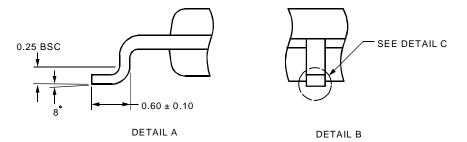

# **Outline Diagram**

#### 20-Pin TSSOP

Dimensions are in millimeters.

5-5499

## **Manufacturing Information**

This device will be assembled in one of the following locations: assembly codes P, M, or T.

### **Ordering Information**

| Device Code | Description              | Package                     | Comcode     |

|-------------|--------------------------|-----------------------------|-------------|

| W3041BCL    | IF Receiver with Filters | 20-pin TSSOP                | 108 191 388 |

| W3041BCL-TR | IF Receiver with Filters | 20-pin TSSOP, tape and reel | 108 191 420 |

| EVB3041     | Evaluation Board         | _                           | 103 325 986 |

Contact your Lucent Technologies Microelectronics Group Account Manager for minimum order requirements.

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET: http://www.lucent.com/micro E-MAIL: docmaster@micro.lucent.com

Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103 N. AMERICA

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

CHINA: Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai 200233 P.R. China Tel. (86) 21 6440 0468, ext. 316, FAX (86) 21 6440 0652

Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 **EUROPE:**

Data Requests: MICROELECTRONICS GROUP DATALINE: **Tel. (44)** 1189 324 299, FAX (44) 1189 328 148 Technical Inquiries: GERMANY: **(49)** 89 95086 0 (Munich), UNITED KINGDOM: **(44)** 1344 865 900 (Ascot),

FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki),

ITALY: (39) 02 6601 1800 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

JAPAN: