### **StaticGuard**

##

## **AVX Multilayer Ceramic Transient Voltage Suppressors ESD Protection for CMOS and Bi Polar Systems**

#### GENERAL INFORMATION

- Typical ESD failure voltage for CMOS and/or Bi Polar is ≥ 200V.

- 15kV ESD pulse (air discharge) per IEC 1000-4-2, Level 4, generates < 20 millijoules of energy.

- Low capacitance (<200pF) is required for high-speed data transmission.

- Low leakage current (I<sub>L</sub>) is necessary for battery operated equipment.

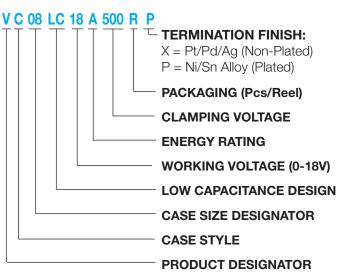

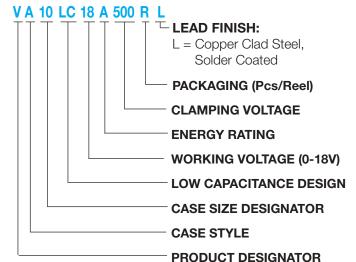

#### **PART NUMBER IDENTIFICATION (See page 2 for details)**

#### <u>Chips</u> <u>Axials</u>

| 111020012201011111011 |                                                              |                     |                   | THOUSANT DEGIGNATION |                     |                     |

|-----------------------|--------------------------------------------------------------|---------------------|-------------------|----------------------|---------------------|---------------------|

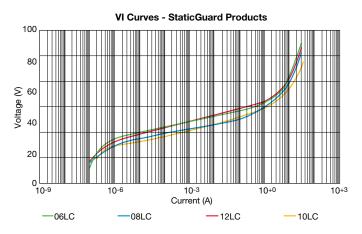

| AVX<br>Part Number    | Working<br>Voltage                                           | Clamping<br>Voltage | Peak<br>Current   | Transient<br>Energy  | Capacitance         | Inductance          |

| Symbol                | V <sub>WM</sub>                                              | V <sub>C</sub>      | l <sub>peak</sub> | E <sub>trans</sub>   | С                   | L                   |

| Units                 | Volts<br>(max.)                                              | Volts<br>(max.)     | Amp<br>(max.)     | Joules<br>(max.)     | pF<br>(typ.)        | nH<br>(typ.)        |

| Test Condition        | <10µA                                                        | 8/20µS†             | 8/20µs            | 10/1000µS            | 0.5Vrms @:<br>1 MHz | di/dt =<br>100mA/ns |

| VC04LC18V500          | See specifications on page 3 and performance data on page 4. |                     |                   |                      |                     |                     |

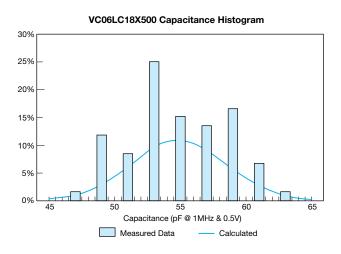

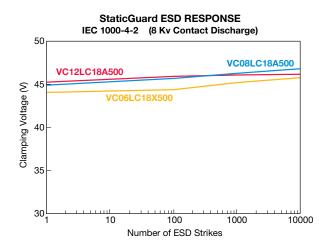

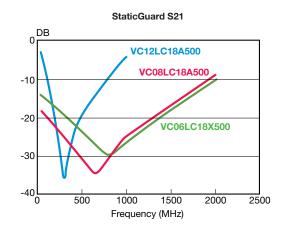

| VC06LC18X500          | ≤18.0                                                        | 50                  | 20                | .05                  | 75                  | <1.0                |

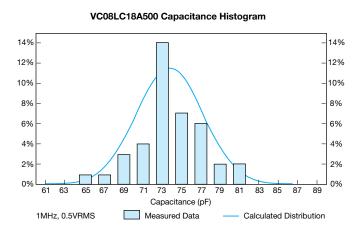

| VC08LC18A500          | ≤18.0                                                        | 50                  | 30                | 0.1                  | 100                 | <1.5                |

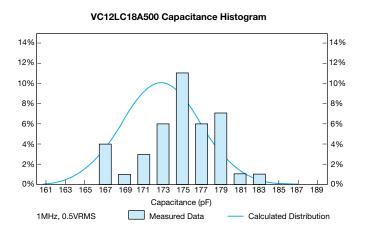

| VC12LC18A500 _ *      | ≤18.0                                                        | 50                  | 30                | 0.1                  | 200                 | <1.7                |

| VA10LC18A500 _ L      | ≤18.0                                                        | 50                  | 30                | 0.1                  | 200                 | <3.5                |

Let Termination Finish: X = Pt/Pd/Ag (Non-Plated)

P = Ni/Sn Alloy (Plated)

\* = Contact Factory for Availability

Lead Finish: L = Copper Clad Steel, Solder Coated

Packaging (Pcs/Reel): see page 2

$V_{\text{wm}}$ —Maximum steady-state DC operating voltage the varistor can maintain and not exceed 50 $\mu$ A leakage current  $V_{\text{c}}$ —Maximum peak voltage across the varistor measured at a specified pulse current and waveform

†Transient Energy Rating <0.05 Joule

Pulse Current & Waveform

0.1 Joule

1A 8/20µS 2A 8/20µS

Dimensions: Millimeters (Inches)

$I_{peak}$ —Maximum peak current which may be applied with the specified waveform without device failure  $E_{tran}$ —Maximum energy which may be dissipated with the specified waveform without device failure

C—Device capacitance measured with zero volt bias 0.5Vrms and 1MHz

L—Device inductance measured with a current edge rate of 100 mA/nS

### **StaticGuard**

# **AVX Multilayer Ceramic Transient Voltage Suppressors ESD Protection for CMOS and Bi Polar Systems**

#### **TYPICAL PERFORMANCE DATA**