#### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

## Features

- Dual Mode STS-48c/STM-16c to Packet/ ATM Framing Device for User Network Interface and Network Node Interface Applications

- Terminates and Generates SONET/SDH Section, Line, and Path Layers

- Dedictated Ports for Section/Line Overhead Access (Extraction/Insertion)

- Extensive SONET/Packet/Cell Performance Monitoring Features

- Programmable Packet/Cell Filtering and Discarding Functionalities

- Industry Compliant Drop Side Packet/Cell Interface for Single-PHY Applications

- Prepared for STS-192/STM-64 Applications

- Provides JTAG TAP controller Conforming to the IEEE 1149.1 standard

- Generic 8-bit Microprocessor Interface

- 16-bit PECL Interface to High-speed MUX/ DEMUX Transceivers

- +3.3V Power Supply

- 0.35 Micron CMOS Technology

- Compliant with SONET and SDH Requirements as Stated in ANSI T1.105, Bellcore GR-253-CORE and ITU-T G.707 Documents

- Compliant with PPP in HDLC-like Framing as Defined in IETF RFC 1619/1661/1662

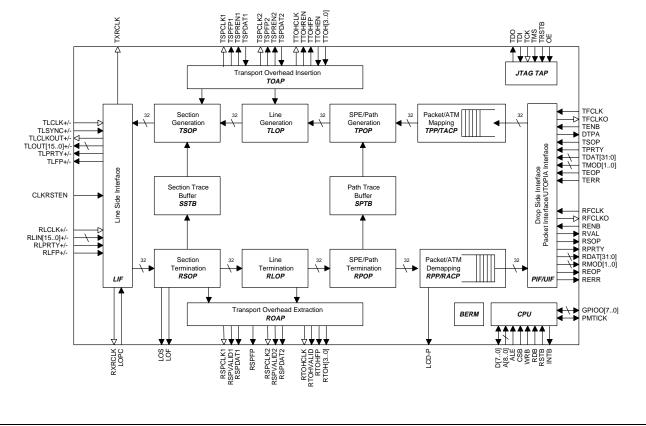

## VSC9112 Block Diagram

Datasheet VSC9112

## Functional Overview

The VSC9112 is a dual mode SONET/SDH to Packet/ATM framing device. In the Packet over SONET (POS) mode, this device can be used in equipment interconnecting IP/PPP/HDLC equipment over public or private SONET/SDH networks. Similarly, in the ATM over SONET (ATM) mode, this device can be used in equipment interconnecting ATM switches. Features of the VSC9112 include: full insertion/extraction of the transport overhead, bit error rate and extensive SONET/packet/cell performance monitoring, packet/cell filtering and discarding functionalities, JTAG TAP controller, and an 8-bit CPU interface with 8 general purpose I/O ports.

When used in conjunction with a high-speed mux/demux tranceiver, this device provides a complete physical layer solution for Packet/ATM over SONET/SDH, LAPS (ITU COM 7-224), and certain Ethernet over SONET/SDH applications at the STS-48 rate. In addition, this device provides the interface for higher bandwidth applications at the STS-192/STM-64 rate.

#### Line Interface (LIF)

- A parity bit, programmable for even/odd parity, is provided each for the incoming and outgoing datapaths.

- A reference clock output derived from the receive clock input can be programmed to be 8kHz, 19MHz, 38MHz, or 78MHz frequency locked to the receive clock.

- A reference clock output derived from the transmit clock input can be programmed to be 8kHz, 19MHz, 38MHz, or 78MHz frequency locked to the transmit clock.

- A Loss of Optical Carrier (LOPC) input signal is provided for monitoring and alarm purposes.

- The TLSYNC, RLFP and TLFP signals are intended to be used in STS-192/STM-64 applications.

#### **Receive Section Overhead Processor (RSOP)**

- Two mechanisms for frame alignment are provided. One is based on searching for A1/A2 framing patterns and the other uses an external frame pulse (RLFP). The latter is intended for STS-192 applications.

- 12/24/48-bit A1/A2 framing patterns are supported.

- Out Of Frame (OOF) and Loss Of Frame (LOF) alarm condition are detected.

- The incoming data stream is optionally descrambled using the generating polynomial  $1 + x^6 + x^7$  with a sequence length of 127.

- Section BIP-8 (B1) errors are detected and accumulated. Both individual and block mode accumulation of B1 error indications are supported.

- The incoming data stream, before descrambling, is monitored for absence of transitions or "all-zero patterns". The Loss Of Signal (LOS) detection and termination criterias are programmable.

- It is possible to force insertion of all "1" in the data stream, except for the Section overhead. The Line AIS (AIS-L) condition may be automatically inserted in case of LOS, LOF, or Loss of Optical Carrier (LOPC) alarm events.

- It is possible to extract the entire Section overhead through the Receive Overhead Access Port (ROAP).

#### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

• The J0, E1, F1, and D1-D3 bytes can be extracted from the Section overhead and inserted into bytes on the special purpose ports of the ROAP.

#### **Receive Line Overhead Processor (RLOP)**

- The Line Remote Defect Indication (RDI-L) and Line Alarm Indication Signal (AIS-L) alarms carried in the K2 byte are extracted and filtered. The filter constants are programmable.

- Line BIP-384 errors carried in the B2 bytes are detected and accumulated. Both individual and block mode accumulation of B2 errors are supported.

- Line REI error indications carried in the M1 byte are accumulated. Both individual and block mode accumulation of M1 error indications are supported.

- The Synchronization Status carried in the S1 byte is extracted and filtered. Unstable and mismatch alarms are supported. The filter constants are programmable.

- The Automatic Protection Switching (APS) bytes, K1 and K2, are extracted and filtered. Unstable alarm is supported. The filter constants are programmable.

- It is possible to extract the entire Line overhead through the ROAP.

- The D4-D12, S1, E2, K1-K2 bytes can be extracted from the Line overhead and inserted into bytes on the special purpose ports of the ROAP.

#### **Receive Path Overhead Processor (RPOP)**

- The H1 and H2 pointer bytes are detected and interpreted according to ANSI T1.105 and ITU-T G.707. The mechanism is programmable to support both SONET and SDH. Path Alarm Indication Signal (AIS-P) and Loss of Pointer (LOP-P) alarm declarations are provided. Several pointer functions are also provided for diagnostic purposes.

- The H1 and H2 pointer bytes are monitored for Concatenation Indication (CI). Loss of Pointer (LOPX) and AIS (AISX) alarm declarations are provided.

- Path BIP-8 errors carried in the B3 byte are detected and accumulated. Both individual and block mode accumulation of B3 errors are supported.

- Path REI error indications carried in the G1 byte are detected and accumulated. Up to 64000 individual errors can be detected per second. Both individual and block mode accumulation of Path REI error indications are supported.

- The Path RDI carried in the G1 byte is detected and programmable.

- The Signal Label carried in the C2 byte is detected, alarmed and is programmable.

#### **Receive Packet Processor (RPP)**

- The byte value used to identify the HDLC Flag Sequence is programmable.

- The detection and discarding of invalid frames are programmable.

- The expected Control Escape byte value and the Octet Destuffing Masking byte are programmable.

Datasheet VSC9112

- The expected Address and Control Field values are programmable.

- The Protocol Field declaration and processing is programmable.

- The Abort Sequence is detected in the incoming HDLC frames.

- The received Frame Check Sequence (FCS) field is verified. The FCS checksum is calculated using either a 16-bit, CRC-CCITT generating polynomial  $1 + x^5 + x^{12} + x^{16}$ , or a 32-bit, CRC-32 generating polynomial  $1 + x + x^2 + x^4 + x^5 + x^7 + x^8 + x^{10} + x^{11} + x^{12} + x^{16} + x^{22} + x^{23} + x^{26} + x^{32}$ .

- The received data is descrambled with the self synchronizing scrambler (SSS) polynomial  $1 + x^{43}$ . Full and/or partial descrambling can be independently enabled/disabled.

- Long and short packet checking are provided and are programmable.

- Self Describing Padding is supported and programmable.

- The storage of the PPP Protocol Field in the Rx FIFO may be enabled/disabled.

- The size of the Rx FIFO size is 4095 words, which may accommodate storage for a total of 16380 PPP Protocol/Information Field bytes.

- The definition of received "errored" HDLC frames is programmable. For these errored HDLC frames two different procedures can be applied.

- A filtering function is provided to perform packet discartion and error marking based on a set of programmable labels. There are four programmable label matching triggers, and one compliment word matching trigger that functions the packet discard and TERR marking.

- The following statistics are provided in the performance monitoring 32-bit counters:

- Received Aborted HDLC frames

- Received FCS errored HDLC frames

- Received Empty HDLC frames

- Received HDLC frames where Address-and-Control-Field-Compression was found

- Received Long packets

- Received Short packets

- Received Invalid Frames

- Received bytes pre-octet destuffing

- Received bytes post-octet destuffing

- Received number of frames excluding Invalid Frames

- Packets discarded by label filtering

- Packets error-marked by label filtering

- Packets stored in the Rx FIFO

- Packets stored in the Rx FIFO that are error marked

- Packet bytes stored in the Rx FIFO

- Number of received PPP padding bytes

#### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

• The SPE Transparent Mode is provided to allow all of the SPE payload to pass directly to the Rx FIFO without further processing.

#### **Receive ATM Cell Processor (RACP)**

- Cell Delineation is provided using shortened cyclic code with a generating polynomial  $1 + x + x^2 + x^8$ . The coset polynomial  $1 + x^2 + x^4 + x^8$  can be added to the calculated HEC check bits before comparison.

- Single-bit header error correction is supported. The dropping of cells during single or multiple error detection is programmable.

- The 48 byte information field is descrambled with a self-synchronizing descrambler polynomial  $1 + x^{43}$ . Descrambling can be enabled/disabled.

- Cells can be filtered based on a programmable cell header pattern in the GFC, PTI, or CLP fields.

- The number of correctable and uncorrectable HEC errors detected, and the number of cells written to the Rx FIFO are monitored.

- The Rx FIFO can accommodate storage of eight ATM cells.

#### Drop Side Interface (POS/ATM Interface)

- A parity bit, programmable for even/odd parity, is provided for each transmit and receive datapaths.

- The Drop Side Interface provides an industry compliant packet interface for POS operations.

- The packet interface supports word-level and packet-level transfer modes.

- The DTPA signal is provided to indicate the waterlevel of the Tx FIFO counted at word level and is programmable.

- It is possible to force reset/flush the contents in the Tx FIFO via the CPU interface.

- It is possible to force reset/flush the contents in the Rx FIFO via the CPU interface.

- The Drop Side Interface provides a Single-PHY UTOPIA-3 interface for ATM operations.

- Two formats of the ATM cells are supported: 52 byte cell or 56 byte cell containing the HEC.

- The UTOPIA-3 interface supports both word-level and cell-level flow control.

#### Transmit ATM Cell Processor (TACP)

- The ATM cells are mapped into the STS-48c SPE or equivalent SDH VC-16-16c. Programmable idle/ unassigned cells are inserted into the cell stream.

- The 48 byte information field is scrambled with a self-synchronizing descrambler polynomial  $1 + x^{43}$ . Scrambling can be enabled/disabled.

- The HEC generator performs a CRC-8 calculation over the first four header octets using the generating polynomial  $1 + x + x^2 + x^8$ . The coset polynomial  $1 + x^2 + x^4 + x^6$  can be added to the result. The HEC is optionally inserted into the fifth octet of the header of cells read from the Tx FIFO.

- The Tx FIFO can accomodate storage of eight ATM cells.

Datasheet VSC9112

#### **Transmit Packet Processor (TPP)**

- The inserted HDLC Flag Sequence byte and the minimum number of Flag Sequence bytes separating HDLC frames are programmable.

- The insertion of the Address and Control fields can be controlled by the HDLC Address-and-Control-Field-Compression mechanism.

- The Address Field inserted after the beginning Flag Sequence is programmable.

- The Control Field inserted after the the Address Field is programmable.

- The Frame Check Sequence (FCS) can be generated using either a 16-bit, CRC-CCITT generating polynomial  $1 + x^5 + x^{12} + x^{16}$ , or a 32-bit CRC-32 generating polynomial  $1 + x + x^2 + x^4 + x^5 + x^7 + x^8 + x^{10} + x^{11} + x^{12} + x^{16} + x^{22} + x^{23} + x^{26} + x^{32}$ .

- Octet Stuffing, or "escaping", can be applied after the FCS generation and partial scrambling, if enabled. The Control Escape byte and the Octet Stuffing Masking byte are programmable. The Asyc-Control-Character-Map (ACCM) can accommodate a maximum of 5 byte values. Each value can be individually enabled/disabled.

- The transmitted data is scrambled with a self-synchronizing scrambler (SSS) polynomial  $1 + x^{43}$ . Full and/or partial scrambling can be independently enabled/disabled.

- The PPP Protocol Field can be generated internally or extracted from the transmit FIFO. The size and value of the inserted Protocol Field are programmable when generated internally.

- The Tx FIFO is programmable in the range from 1 to 4095 words or 16380 bytes of data storage. All valid packet bytes stored in the Tx FIFO are read out and mapped into the PPP Protocol/Information Fields of generated PPP/HDLC frames.

- Two Tx PIF packet transfer modes are supported: packet transfer mode and word transfer mode.

- The TXF\_ERR signal is provided to force insertion of errors into the FCS, or to force abort the transmitted HDLC frame.

- It is possible to force XOR'ing of the transmitted Address, Control or Protocol Fields with a programmable mask value via the CPU interface for diagnostic purposes.

- The following statistics are provided in the performance monitoring 32-bit counters:

- Bytes read from Tx FIFO

- Transmitted good HDLC frames (non-aborted, non-FCS errored)

- Transmitted Aborted HDLC frames

- Transmitted FCS Errored HDLC frames

- Long packets read from Tx FIFO

- Short packets read from Tx FIFO

- Transmitted empty HDLC frames

- Bytes pre octet-stuffing (excluding Abort sequences)

- Bytes post octet-stuffing (excluding Abort sequences)

#### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

• The SPE Transparent Mode is provided to allow the Tx FIFO content to be passed directly into the SPE payload without further processing.

#### Transmit Path Overhead Processor (TPOP)

- The H1 and H2 pointer byte values are programmable to support both SONET and SDH. Several pointer functions are provided for diagnostics purposes. The remaining 47 H1 and H2 bytes are programmable.

- The Path BIP-8 is computed and placed in the B3 byte of the current frame. It is possible to insert B3 errors for diagnostic purposes.

- The number of Path BIP-8 errors detected in the Receive Path Overhead Processor (RPOP) is backreported as Path REI in the G1 byte. Both individual and block mode backreporting for G1 are supported.

- It is possible to enable/disable RDI-P insertion for each of the following alarms: LOS, LOF, AIS-L, AIS-P, LOP-P, TIM-P, UNEQ-P, LCD-P and PLM-P. Both the latest and earlier definitions of RDI-P are supported.

- The Path Signal Label (C2) byte value is programmable.

- The Path Trace (J1) byte value is programmable.

- The F2, H4, Z3, Z4, and Z5 bytes are programmable.

#### Transmit Line Overhead Processor (TLOP)

- It is possible to insert programmable sets of K1 and K2 bytes into the outgoing data stream.

- RDI-L can be automatically inserted during the detection of an LOS, LOF, or AIS-L alarm in the receive data stream.

- The Line BIP-384 code is computed and placed in the B2 bytes of the current frame. It is possible to insert B2 errors for diagnostics purposes.

- The number of Line BIP-384 errors detected in the Receive Line Overhead Processor (RLOP) is backreported as Line REI in the M1 byte. Up to 255 errors can be backreported per frame in individual mode. Both individual and block mode backreporting for M1 are supported. It is possible to insert M1 error indications for diagnostics purposes.

- The Synchronization Status value inserted in the S1 byte is programmable.

- Bytes input to the special purpose ports of the Transmit Overhead Access Port (TOAP) can be inserted into the D4-D12, E2, S1, K1 and K2 bytes of the outgoing Line overhead.

- All bytes in the line overhead that are reserved for national or future international standardization use can be overwritten with 0x00.

- The H1, H2, and H3 bytes from the Transmit Overhead Access Port (TOAP) can be inserted into the H1, H2, and H3 overhead bytes, or applied as an error mask to the H1, H2, and H3 overhead bytes.

Transmit Section Overhead Processor (TSOP)

- It is possible to forced insert all "1"s into the data stream, before scrambling, with the exception of the section overhead. The AIS-L condition can be automatically inserted through activity from the special purpose serial interfaces.

- The Section BIP-8 code is computed and can be placed in the B1 byte of the current frame. It is possible to insert B1 errors for diagnostics purposes.

- The A1 and A2 framing bytes can be inserted into the frame. It is also possible to introduce bit errors in the framing word.

- The J0 byte supports both SONET and SDH formats. The J0 byte can be programmed to a fixed value for interworking with older equipment implementing the C1 indentification byte.

- The Z0 growth bytes supports both SONET and SDH formats. The Z0 bytes can be programmed to carry the C1 identification bytes for interworking with older equipment.

- The outgoing data stream is optionally scrambled using the generating polynomial  $1 + x^6 + x^7$  with a sequence length of 127.

- It is possible to force insert all "0"s in the outgoing data stream after scrambling for diagnostic purposes (LOS).

- Bytes input to the special purpose ports of the TOAP can be inserted into the D1-D3, E1, F1 and J0 bytes of the outgoing Section overhead.

- All bytes in the section overhead that are reserved for national or future international standardization use can be overwritten with 0x00.

- A frame pulse is provided for the outgoing data stream and is programmable.

#### **Receive Overhead Access Port (ROAP)**

- Two identical, but independent, special purpose ports are provided for the extraction of special purpose bytes from the SONET/SDH transport overhead and of certain SONET/SDH alarms specific to automatic protection switching (APS) applications.

- The frame pulse RSPFP is synchronized to the receive drop side frame pulses RXFPOUTA-D.

- The entire section/line transport overhead can be extracted from the serial output port RTOH[3..0].

#### Transmit Overhead Access Port (TOAP)

- Two identical, but independent, special purpose ports are provided for the insertion of special purpose bytes into the SONET/SDH transport overhead and of certain SONET/SDH alarms specific to automatic protection switching (APS) applications.

- The entire transport overhead is captured from the serial input ports TTOH[3..0]. The captured data can be selectively inserted into the corresponding overhead bytes of the transmitted SONET/SDH frame.

#### SONET/SDH Section Trace Buffers (SSTB)

• Three different Section Trace Message (J0) formats are supported in both transmit and receive directions: one byte (SONET) message, 16 byte (SDH) message, and 64 byte (SONET CLLI) message.

#### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

• The received section trace message is checked for persistency. A mismatch alarm is supported.

#### **CPU Interface**

- All configuration bits are both writeable and readable and can be accessed regardless of the device clock source status, except for the reset state. Configuration bits include selection bits, interrupt masking bits, and programmable counter/control values.

- Eight programmable General Purpose Input/Output (GPIO) ports are available for monitoring and controlling external signals. All GPIOs support bistable interrupts when configured as input ports.

- Clock activity monitors are implemented for all input clocks.

#### **Bit Error Rate Monitoring**

- Bit error rate monitoring is based on the Line BIP (B2) error code and is capable of measuring BERs down to  $10^{-10}$ .

- There are four independent BER monitors with individual accumulation periods and alarm thresholds.

- A saturation threshold is implemented for each BER monitor to specify the maximum number of errors that can be accumulated per frame.

- The BER Signal Degrade (BER-SD) alarm is based on BER monitors 1 and 2.

- The BER Signal Fail (BER-SF) alarm is based on BER monitors 3 and 4.

#### JTAG

• Standard IEEE 1149.1 compliant JTAG interface.

#### **Loopback Modes**

- Equipment loopback is supported by looping the output from the Transmit Section Overhead Processor (TSOP), in the transmit direction, back to the input of the Receive Section Overhead Processor (RSOP), in the receive direction.

- Facility loopback is supported by looping the data received on the receive Line Side Interface back to the transmit Line Side Interface.

- Section loopback is supported by looping the output from the Recieve Section Overhead Processor (RSOP) in the receive direction back to the input of the Transmit Section Overhead Processor (TSOP), in the transmit direction.

- Line loopback is supported by looping the output from the Recieve Line Overhead Processor (RLOP) in the receive direction back to the input of the Transmit Line Overhead Processor (TLOP), in the transmit direction.

- Drop side loopback is supported by looping the output from the Tx FIFO to the input of the Rx FIFO. This loopback is supported for both packet and ATM cell mode.

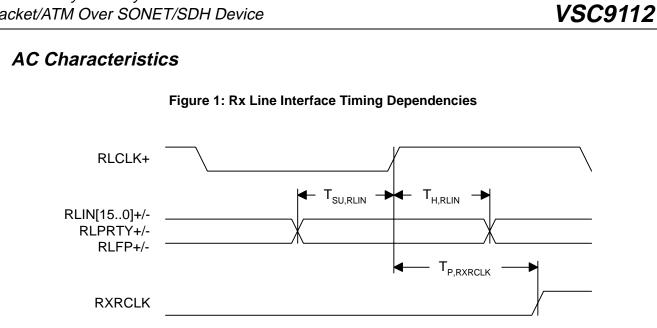

#### Table 1: Rx Line Interface

| Symbol                  | Description                                                          | Min | Max    | Unit |

|-------------------------|----------------------------------------------------------------------|-----|--------|------|

| f <sub>RLCLK</sub>      | RLCLK+/- Clock Frequency (nominal)                                   | -   | 155.52 | MHz  |

| dc <sub>RLCLK</sub>     | RLCLK+/- Duty Cycle                                                  | 40  | 60     | %    |

| T <sub>R/F, RLCLK</sub> | RLCLK+/- Rise/Fall Time                                              | -   | 1.0    | ns   |

| T <sub>SU, RLIN</sub>   | RLIN[150]+/-, RLPRTY+/-, RLFP+/- Setup Time to RLCLK+<br>Rising Edge | 1.5 | -      | ns   |

| T <sub>H, RLIN</sub>    | RLIN[150]+/-, RLPRTY+/-, RLFP+/- Hold Time to RLCLK+<br>Rising Edge  | 1.0 | -      | ns   |

| T <sub>P, RXRCLK</sub>  | RLCLK+ Rising Edge to RXRCLK Rising/Falling Edge                     | 1.0 | 20.0   | ns   |

| f <sub>RXRCLK</sub>     | f <sub>RLCLK</sub> Divided by 2/4/8/19440                            | -   | -      | MHz  |

| dc <sub>RXRCLK</sub>    | RXRCLK Duty Cycle                                                    | 30  | 70     | %    |

| RXRCLK times are fo     | or 50 pF load.                                                       |     |        |      |

Datasheet

## STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

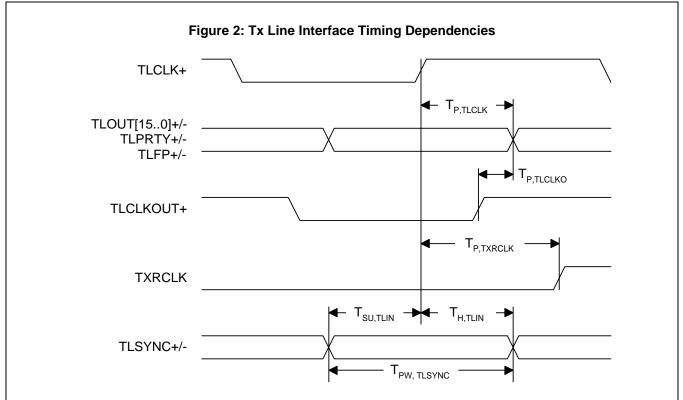

#### Table 2: Tx Line Interface

| Symbol                                                          | Description                                                            | Min | Max    | Unit |

|-----------------------------------------------------------------|------------------------------------------------------------------------|-----|--------|------|

| f <sub>TLCLK</sub>                                              | TLCLK+/- Clock Frequency (nominal)                                     | -   | 155.52 | MHz  |

| dc <sub>TLCLK</sub>                                             | TLCLK+/- Duty Cycle                                                    | 40  | 60     | %    |

| T <sub>R/F, TLCLK</sub>                                         | TLCLK+/- Rise/Fall Time                                                | -   | 1.0    | ns   |

| T <sub>P, TLOUT</sub>                                           | TLCLK+ Rising Edge to TLOUT[150]+/- and TLPRTY+/-,<br>TLFP+/- Valid    | 1.0 | 4.0    | ns   |

| T <sub>P, TXRCLK</sub>                                          | TLCLK+ Rising Edge to TXRCLK Rising/Falling Edge                       | 1.0 | 15.0   | ns   |

| T <sub>P, CLKOUT</sub>                                          | TLCLKOUT+ Rising Edge to TLOUT[150]+/-, TLPRTY+/-,<br>TLFP+/- Valid    | 0   | 1.3    | ns   |

| f <sub>TXRCLK</sub>                                             | f <sub>TLCLK</sub> Divided by 2/4/8/19440                              | -   | -      | MHz  |

| dc <sub>TXRCLK</sub>                                            | TXRCLK Duty Cycle                                                      | 30  | 70     | %    |

| T <sub>SU, TLIN</sub>                                           | TLSYNC +/- Setup Time to TLCLK+ Rising Edge <sup>1)</sup>              | 2.0 |        | ns   |

| T <sub>H, TLIN</sub>                                            | TLSYNC +/- Hold Time to TLCLK+ Rising Edge <sup>1)</sup>               | 1.0 |        | ns   |

| T <sub>PW, TLSYNC</sub>                                         | Minimum Pulse Width of TLSYNC (measured in TLCLK Clock Cycles)         | 2   |        | -    |

| <sup>1)</sup> It is not required that<br>TXRCLK times are for . | T <sub>SU, TLIN</sub> and T <sub>H, TLIN</sub> are met.<br>50 pF load. |     | •      |      |

Datasheet VSC9112

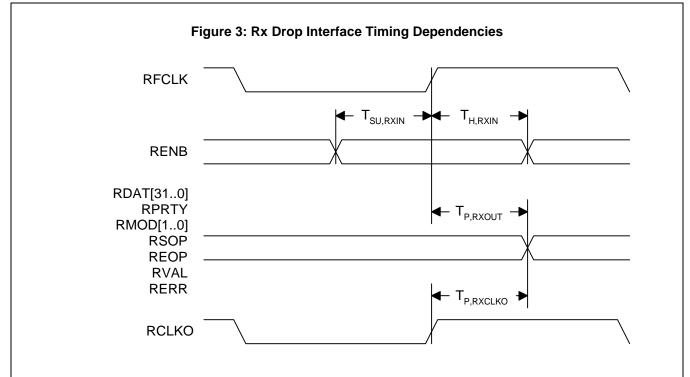

#### Table 3: Rx Drop Interface

| Symbol                                                                                                                             | Description                                                                       | Min | Max                             | Unit             |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|---------------------------------|------------------|

| f <sub>RFCLK</sub>                                                                                                                 | RFCLK Clock Frequency (nominal)                                                   | 50  | 104                             | MHz              |

| dc <sub>RFCLK</sub>                                                                                                                | RFCLK Duty Cycle                                                                  | 40  | 60                              | %                |

| T <sub>R/F, RFCLK</sub>                                                                                                            | RFCLK Rise/Fall Time                                                              | -   | 2.0                             | ns               |

| dc <sub>RFCLKO</sub>                                                                                                               | RFCLKO Duty Cycle                                                                 |     | - (1.0 ns x<br><sub>LK</sub> )% | %                |

| T <sub>SU, RXIN</sub>                                                                                                              | RENB Setup Time to RFCLK Rising Edge                                              | 2.0 | -                               | ns               |

| T <sub>H, RXIN</sub>                                                                                                               | RENB Hold Time to RFCLK Rising Edge                                               | 0.5 | -                               | ns               |

| т                                                                                                                                  | RFCLK Rising Edge to RDATA[310], RPRTY, RMOD[10],                                 | 1.0 | 6.0                             | ns <sup>1)</sup> |

| T <sub>P, RXOUT</sub>                                                                                                              | RSOP, REOP, RVAL and RERR Valid                                                   | 0.5 | 4.2                             | ns <sup>2)</sup> |

| T <sub>P, RXCLKO</sub>                                                                                                             | RFCLKO Rising Edge RDAT[310], RPRTY, RMOD[10],<br>RSOP, REOP, RVAL and RERR Valid | 0.0 | 1.5                             | ns <sup>3)</sup> |

| <ol> <li>Output times are for</li> <li>Output times are for</li> <li>Output times are for</li> <li>Output times are for</li> </ol> | or 5 pF load.                                                                     | 1   | 1                               | L                |

<sup>3)</sup> Output times are for 5 to 15 pF load.

## STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

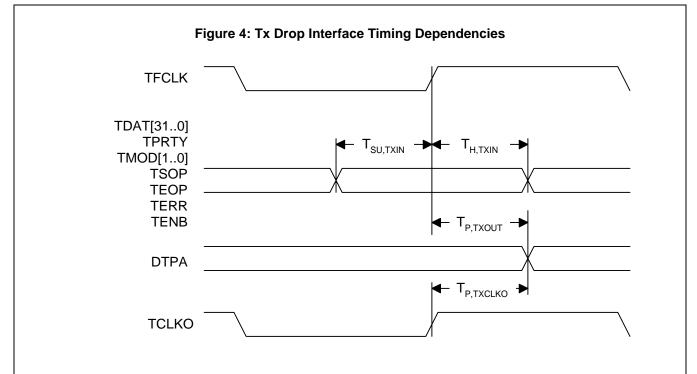

#### Table 4: Tx Drop Interface

| Symbol                                                                                                                         | Description                                                                           | Min | Max                             | Unit             |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|---------------------------------|------------------|

| f <sub>TFCLK</sub>                                                                                                             | TFCLK Clock Frequency                                                                 | 50  | 104                             | MHz              |

| dc <sub>TFCLK</sub>                                                                                                            | TFCLK Duty Cycle                                                                      | 40  | 60                              | %                |

| T <sub>R/F, TFCLK</sub>                                                                                                        | TFCLK Rise/Fall Time                                                                  | -   | 2.0                             | ns               |

| dc <sub>TFCLKO</sub>                                                                                                           | TFCLKO Duty Cycle                                                                     |     | - (1.0 ns x<br><sub>LK</sub> )% | %                |

| T <sub>SU, TXIN</sub>                                                                                                          | TDAT[310], TPRTY, TMOD[10], TSOP, TEOP, TERR and TENB Setup Time to TFCLK Rising Edge | 2.0 | -                               | ns               |

| T <sub>H, TXIN</sub>                                                                                                           | TDAT[310], TPRTY, TMOD[10], TSOP, TEOP, TERR and TENB Hold Time to TFCLK Rising Edge  | 0.5 | -                               | ns               |

| т                                                                                                                              |                                                                                       | 1.0 | 6.0                             | ns <sup>1)</sup> |

| T <sub>P, TXOUT</sub>                                                                                                          | TFCLK Rising Edge to DTPA Valid                                                       | 0.5 | 4.2                             | ns <sup>2)</sup> |

| T <sub>P, TXCLKO</sub>                                                                                                         | TFCLKO Rising Edge to DTPA Valid.                                                     | 0.0 | 1.5                             | ns <sup>3)</sup> |

| <ol> <li>Output times are fo</li> <li>Output times are fo</li> <li>Output times are fo</li> <li>Output times are fo</li> </ol> | r 5 pF load.                                                                          |     |                                 |                  |

Datasheet VSC9112

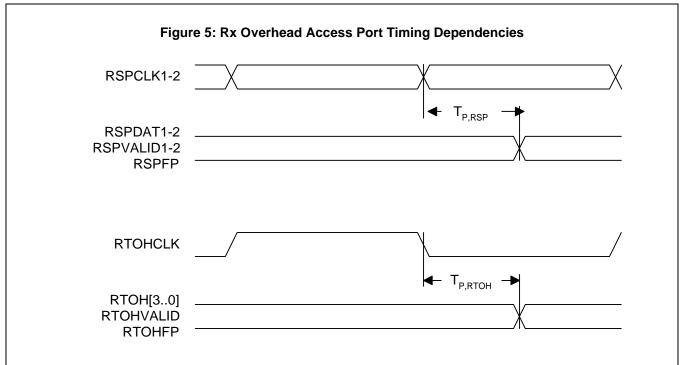

#### Table 5: Rx Overhead Access Port

| Symbol                                                                                                                               | Description                                                                                                           | Min  | Max   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-------|------|

| f <sub>RSPCLK</sub>                                                                                                                  | RSPCLK1-2 Clock Frequency (optionally gapped)                                                                         | -    | 2.16  | MHz  |

| dc <sub>RSPCLK</sub>                                                                                                                 | RSPCLK1-2 Duty Cycle                                                                                                  | 40   | 60    | %    |

| T <sub>R/F, RSPCLK</sub>                                                                                                             | RSPCLK1-2 Rise/Fall Time                                                                                              | -    | 2.0   | ns   |

| T <sub>P, RSP</sub>                                                                                                                  | RSPCLK1-2 Rising/Falling Edge <sup>2)</sup> to RSPDAT1-2,<br>RSPVALID1-2, RSPFP Valid                                 | -6.0 | +15.0 | ns   |

| f <sub>RTOHCLK</sub>                                                                                                                 | RTOHCLK Clock Frequency (nominal)                                                                                     | -    | 38.88 | MHz  |

| dc <sub>RTOHCLK</sub>                                                                                                                | RTOHCLK Duty Cycle                                                                                                    | 40   | 60    | %    |

| T <sub>R/F, RTOHCLK</sub>                                                                                                            | RTOHCLK Rise/Fall Time                                                                                                | -    | 2.0   | ns   |

| T <sub>P, RTOH</sub>                                                                                                                 | RTOHCLK Rising/Falling Edge <sup>3)</sup> to RTOH[03], RTOHVALID,<br>RTOHFP Valid                                     | -3.0 | +7.0  | ns   |

| <ul> <li><sup>2)</sup> Active edge of clock</li> <li><sup>3)</sup> Active edge of clock</li> <li>All output times are for</li> </ul> | is programmable for group of inputs for each independent port.<br>is programmable for group of inputs.<br>50 pF load. |      |       |      |

## STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

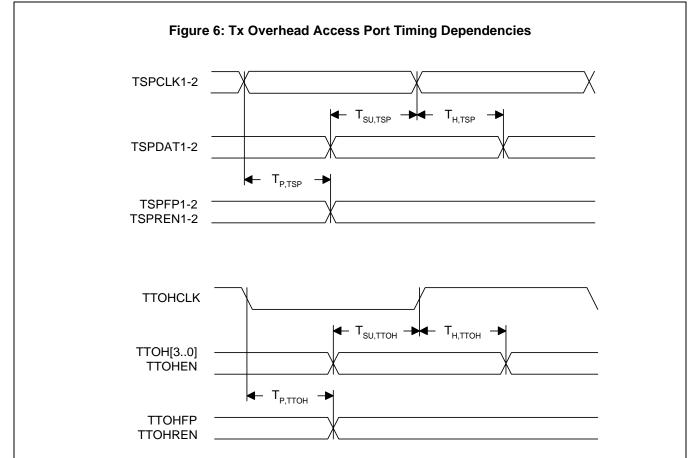

#### Table 6: Tx Overhead Access Port

| Symbol                    | Description                                                                 | Min   | Max   | Unit |

|---------------------------|-----------------------------------------------------------------------------|-------|-------|------|

| f <sub>TSPCLK</sub>       | TSPCLK1-2 Clock Frequency (optionally gapped)                               | -     | 2.16  | MHz  |

| dc <sub>TSPCLK</sub>      | TSPCLK1-2 Duty Cycle                                                        | 40    | 60    | %    |

| T <sub>R/F, TSPCLK</sub>  | TSPCLK1-2 Rise/Fall Time                                                    | -     | 2.0   | ns   |

| T <sub>SU, TSP</sub>      | TSPDAT1-2 Setup Time to TSPCLK1-2 Rising/Falling Edge <sup>5)</sup>         | 25.0  | -     | ns   |

| T <sub>H, TSP</sub>       | TSPDAT1-2 Hold Time to TSPCLK1-2 Rising/Falling Edge <sup>5)</sup>          | 0     | -     | ns   |

| T <sub>P, TSP</sub>       | TSPCLK1-2 Rising/Falling Edge <sup>6)</sup> to TSPREN1-2, TSPFP1-2<br>Valid | -10.0 | +20.0 | ns   |

| f <sub>TTOHCLK</sub>      | TTOHCLK Clock Frequency (nominal)                                           | -     | 38.88 | MHz  |

| dc <sub>TTOHCLK</sub>     | TTOHCLK Duty Cycle                                                          | 40    | 60    | %    |

| T <sub>R/F, TTOHCLK</sub> | TTOHCLK Rise/Fall Time                                                      | -     | 2.0   | ns   |

| T <sub>SU, TTOH</sub>     | TTOH[03], TTOHEN Setup Time to TTOHCLK Rising/Falling Edge <sup>7)</sup>    | 15.0  | -     | ns   |

| T <sub>H, TTOH</sub>      | TTOH[03], TTOHEN Hold Time to TTOHCLK Rising/Falling Edge <sup>7)</sup>     | -1.0  | -     | ns   |

# Datasheet VSC9112

#### Table 6: Tx Overhead Access Port

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                             | Min                                                                   | Max  | Unit |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|----|

| T <sub>P, TTOH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                               | TTOHCLK Rising/Falling Edge <sup>8)</sup> to TTOHREN, TTOHFP<br>Valid | -3.0 | +7.0 | ns |

| <ul> <li><sup>5)</sup> Active edge of clock is programmable for group of inputs for each independent port.</li> <li><sup>6)</sup> Active edge of clock is programmable for group of outputs for each independent port.</li> <li><sup>7)</sup> Active edge of clock is programmable for group of inputs.</li> <li><sup>8)</sup> Active edge of clock is programmable for group of outputs.</li> <li>All output times are for 50 pF load.</li> </ul> |                                                                       |      |      |    |

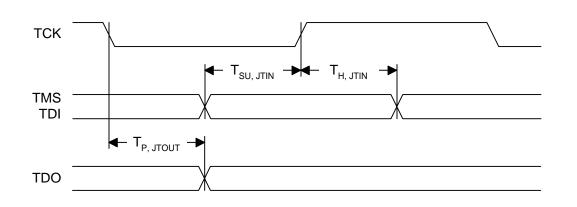

#### Figure 7: JTAG Interface Timing Dependencies

#### Table 7: JTAG Interface

| Symbol                | Description                           | Min | Max | Unit |

|-----------------------|---------------------------------------|-----|-----|------|

| f <sub>TCK</sub>      | TCK Frequency                         | -   | 1   | MHz  |

| dc <sub>TCK</sub>     | TCK Duty Cycle                        | 40  | 60  | %    |

| T <sub>SU, JTIN</sub> | TMS/TDI Setup Time to TCK Rising Edge | 50  | -   | ns   |

| T <sub>H, JTIN</sub>  | TMS/TDI Hold Time to TCK Rising Edge  | 50  | -   | ns   |

| T <sub>P, JOUT</sub>  | TCK Falling Edge to TDO Valid         | 1.5 | 50  | ns   |

Datasheet

VSC9112

# Datasheet VSC9112

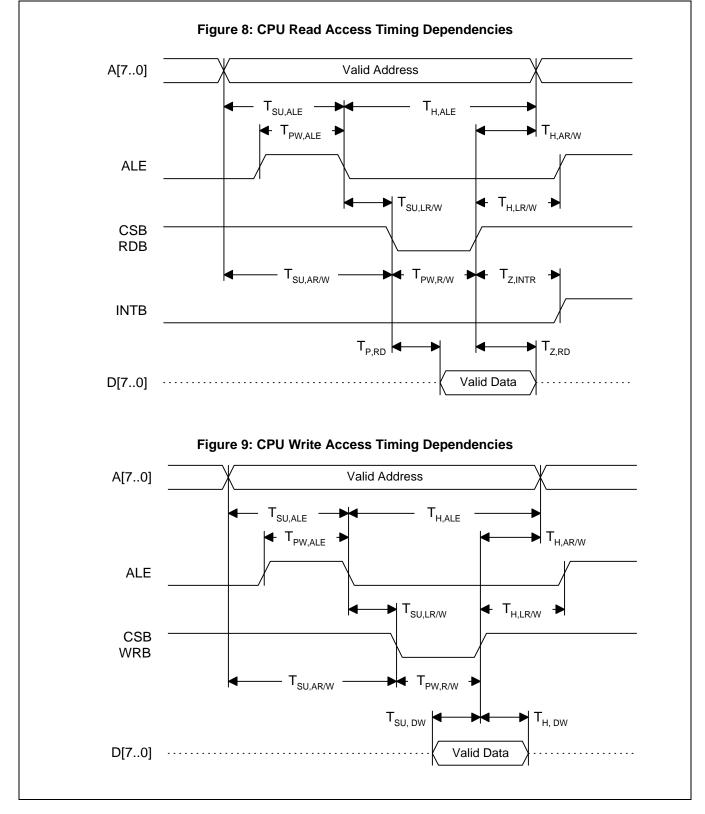

| Symbol                | Description                                       | Min     | Max | Unit |

|-----------------------|---------------------------------------------------|---------|-----|------|

| T <sub>SU, ALE</sub>  | Address to Address Latch Setup Time               | 10      | -   | ns   |

| T <sub>H, ALE</sub>   | Address to Address Latch Hold Time                | 10      | -   | ns   |

| T <sub>PW, ALE</sub>  | Address Latch Pulse Width                         | 20      | -   | ns   |

| T <sub>SU, LR/W</sub> | Latch to Valid Read/Write Setup Time              | 0       | -   | ns   |

| T <sub>H, LR/W</sub>  | Latch to Valid Read/Write Hold Time               | 5       | -   | ns   |

| T <sub>SU, AR/W</sub> | Address to Valid Read/Write Setup Time            | 10      | -   | ns   |

| T <sub>H, AR/W</sub>  | Address to Valid Read/Write Hold Time             | 10 / 5  | -   | ns   |

| T <sub>PW, R/W</sub>  | Valid Read/Write Pulse Width                      | 20 / 25 | -   | ns   |

| T <sub>SU, DW</sub>   | Data to Valid Write Setup Time                    | 20      | -   | ns   |

| T <sub>H, DW</sub>    | Data to Valid Write Hold Time                     | 10      | -   | ns   |

| T <sub>P, RD</sub>    | Valid Read to Valid Data Propagation Delay        |         | 80  | ns   |

| T <sub>Z, RD</sub>    | Valid Read Negated to Output Tristate             | 1       | 25  | ns   |

| T <sub>Z, INTH</sub>  | Valid Read Negated to Interrupt Release/Pull-down |         | 100 | ns   |

| l output times are f  |                                                   | I       | I   | 1    |

#### Table 8: CPU Read/Write Access

### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

## **DC Characteristics**

| Parameters         | Description                        | Min  | Max  | Units | Conditions                        |

|--------------------|------------------------------------|------|------|-------|-----------------------------------|

| V <sub>OH</sub>    | Output HIGH voltage (TTL)          | 2.4  |      | V     | I <sub>OH</sub> = -2,-4,-8,-16 mA |

| V <sub>OL</sub>    | Output LOW voltage (TTL)           |      | 0.5  | V     | I <sub>OL</sub> = 2,4,8,16 mA     |

| V <sub>IH</sub>    | Input HIGH voltage (TTL)           | 2.0  | 5.5  | V     | —                                 |

| V <sub>IL</sub>    | Input LOW voltage (TTL)            | 0    | 0.8  | V     | —                                 |

| I <sub>IT</sub>    | Input current (TTL)                | —    | 10   | μA    | $0V < V_{IN} < 5V$                |

| V <sub>OCM</sub>   | O/P Common Mode Range (PECL)       | 1600 | 2300 | mV    | At Min $\Delta V_{OUT}$           |

| $\Delta V_{OUT75}$ | Differential Output Voltage (PECL) | 1000 | 1500 | mV    | $75\Omega$ to $V_{DD} - 2.0$ V    |

| $\Delta V_{OUT50}$ | Differential Output Voltage (PECL) | 700  | 1200 | mV    | $50\Omega$ to $V_{DD} - 2.0$ V    |

| V <sub>ICM</sub>   | I/P Common Mode Range (PECL)       | 1500 | 1800 | mV    | At Min $\Delta V_{IN}$            |

| $\Delta V_{IN}$    | Differential Input Voltage (PECL)  | 300  | 2600 | mV    | —                                 |

| I <sub>IP</sub>    | Input current (PECL)               | —    | 1000 | μΑ    | $0 V < V_{IN} < 3.3 V$            |

## **Power Dissipation**

| Parameter       | Description                               | (Typ) | (Max) | Units |

|-----------------|-------------------------------------------|-------|-------|-------|

| I <sub>DD</sub> | Power supply current from V <sub>DD</sub> | 833   | 972   | mA    |

| P <sub>D</sub>  | Power dissipation                         | 2.5   | 3.0   | W     |

## Datasheet VSC9112

## Absolute Maximum Ratings(1)

| Power Supply Voltage ( $V_{DD}$ ) Potential to GND  | -0.5V to +4V                     |

|-----------------------------------------------------|----------------------------------|

| Power Supply Voltage ( $V_{DD5}$ ) Potential to GND | -0.5V to +6V                     |

| DC Input Voltage (PECL inputs)                      | 0.5V to $V_{DD} + 0.5V$          |

| DC Input Voltage (TTL inputs)                       | 0.5V to $V_{DD5} + 0.5V$         |

| DC Output Voltage (TTL Outputs)                     | 0.5V to $V_{DD} + 0.5V$          |

| DC Output Voltage (TTL 5V Tolerant Outputs)         | 0.5V to $V_{DD5} + 0.5V$         |

| Output Current (TTL Outputs)                        | +/-50mA                          |

| Output Current (PECL Outputs)                       | +/-50mA                          |

| Case Temperature Under Bias                         | $55^{\circ}$ to $+125^{\circ}$ C |

| Storage Temperature                                 | $65^{\circ}C$ to $+150^{\circ}C$ |

| Maximum Input ESD (Human Body Model)                |                                  |

Note: Caution: Stresses listed under "Absolute Maximummanent damage. Functionality at or exceeding the values listedods may affect device reliability.

## **Recommended Operating Conditions**

| Power Supply Voltage ( <i>V</i> <sub>DD</sub> )+3 | .3V±10%                           |

|---------------------------------------------------|-----------------------------------|

| Power Supply Voltage (V <sub>DD5</sub> )+5        | .0V±10 %                          |

| Operating Temperature Range* ( <i>T</i> )40       | <sup>o</sup> to 95 <sup>o</sup> C |

\* Lower limit of specification is ambient temperature and upper limit is case temperature.

### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

## Package Pin Description

| Signal        | Name                                      | <i>I/O</i> | Туре | Description                                                                                                                                                                                                                                                                                  |

|---------------|-------------------------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLCLK+/-      | Parallel Line<br>Receive Clock            | Ι          | PECL | Clock reference for the 2.5Gb/s receive flow carried in RLIN[150]. The clock frequency is nominally 155.52MHz equivalent to STS-48/STM-16 operation.                                                                                                                                         |

| RLIN[150]+/-  | Parallel Line<br>Receive Data             | I          | PECL | Parallel data bus for the incoming STS-48/STM-16 data stream. RLIN[15] is the most significant bit. RLIN[15] is the first arriving bit on the serial data stream.is sampled on the rising edge of RLCLK+.                                                                                    |

| RLPRTY+/-     | Parallel Line<br>Receive Parity           | Ι          | PECL | Parity input (even/odd parity) for the parallel receive line data, RLIN[150] (optionally include RLFP). RLPRTY is sampled on the rising edge of RLCLK+.                                                                                                                                      |

| RLFP+/-       | Parallel Line<br>Receive Frame<br>Pulse   | I          | PECL | Frame pulse for the receive line interface. RLFP can be used<br>instead of the internal framing circuit (based on A1A2 pat-<br>terns) for synchronizing the receive processor. RLFP is<br>sampled on the rising edge of RLCLK+.<br>RLFP is intended for use in STS-192/STM-64 applications.  |

| RXRCLK        | Receive Reference<br>Clock                | 0          | TTL  | Reference clock derived from RLCLK in a 78MHz/38MHz/<br>19MHz/8kHz version.                                                                                                                                                                                                                  |

| LOPC          | Loss of Optical<br>Carrier                | I          | TTL  | LOPC is monitored and changes in the signal status may<br>cause generation of an interrupt. This allows monitoring of<br>optical failures via the device CPU interface. When LOPC<br>is asserted, the receive processor is optionally clocked by<br>the transmit clock (derived from TLCLK). |

| CLKRSTEN      | Clock Reset<br>Enable                     | I          | TTL  | If CLKRSTEN is asserted, all primary clock outputs (TXR-<br>CLK, RXRCLK, RSPCLK1, RSPCLK2, RTOHCLK,<br>TSPCLK1, TSPCLK2, and TTOHCLK) will halt during<br>master reset. If CLKRSTEN is deasserted, all primary<br>clock outputs will be running during device master reset.                  |

| TLCLK+/-      | Parallel Line<br>Transmit Clock           | Ι          | PECL | Clock reference for the 2.5Gb/s transmit flow carried in TLOUT[150]. The clock frequency is nominally 155.52MHz equivalent to STS-48/STM-16 operation.                                                                                                                                       |

| TLCLKOUT+/-   | Parallel Line<br>Transmit Looped<br>Clock | 0          | PECL | Looped TLCLK signal. Timing for this clock is defined<br>with reference to the TLOUT data bus signals. The clock<br>frequency is nominally 155.52MHz equivalent to STS-48/<br>STM-16 operation (same as TLCLK).                                                                              |

| TLOUT[150]+/- | Parallel Line<br>Transmit Data            | 0          | PECL | Parallel data bus for the outgoing STS-48/ STM-16 data<br>stream. TLOUT[15] is the most significant bit.TLOUT[15]<br>is the first transmitted bit on the serial data stream.<br>TLOUT[150] is generated on the rising edge of the incom-<br>ing TLCLK+.                                      |

| TLPRTY+/-     | Parallel Line<br>Transmit Parity          | 0          | PECL | Parity output (even/odd parity) for the parallel transmitdata,<br>TLOUT[150] (optionally includes TLFP). TLPRTY is<br>generated on the rising edge of TLCLK+.                                                                                                                                |

# Datasheet VSC9112

| Signal    | Name                                      | <i>I/O</i> | Туре | Description                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-------------------------------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLFP+/-   | Parallel Line<br>Transmit Frame<br>Pulse  | 0          | PECL | Frame pulse for the transmit line interface. TLFP is a one clock cycle wide pulse coincident with either the first framing byte (A1), the first paylod byte (first byte followingZ0) or a 24 clock cycle wide pulse coincident with the A2 framing bytes. TLFP is generated on the rising edge of TLCLK+. TLFP is intended for use in STS-192/STM-64 applications. |

| TLSYNC+/- | Synchronization                           | Ι          | PECL | TLSYNC is used for synchronously resetting the device<br>transmit processor only.<br>TLSYNC is intended for use in STS-192/STM-64 applica-<br>tions.                                                                                                                                                                                                               |

| TXRCLK    | Transmit<br>Reference Clock               | 0          | TTL  | Reference clock derived from TLCLK in a 78MHz/38MHz/<br>19MHz/8kHz version.                                                                                                                                                                                                                                                                                        |

| LOS       | Loss Of Signal                            | 0          | TTL  | Status signal indicating if Loss Of Signal (LOS) has been detected. The LOS status is also available in an internal status register bit. The signal is active high.                                                                                                                                                                                                |

| LOF       | Loss Of Frame                             | 0          | TTL  | Status signal indicating if Loss Of Frame (LOF) has been detected. The LOF status is also available in an internal status register bit. The signal is active high.                                                                                                                                                                                                 |

| LCD-P     | Loss of Cell<br>Delineation               | 0          | TTL  | This signal is asserted when the cell delineation state ma-<br>chine is not in SYNC state. This alarm indication is also<br>available via internal register access.                                                                                                                                                                                                |

| RSPFP     | Receive Special<br>Purpose Frame<br>Pulse | 0          | TTL  | Frame reference for special purpose serial output ports<br>RSPDAT <i>x</i> . The frame pulse is a one clock cycle wide pulse<br>coincident with the first bit on the serial dataActive high.<br>RSPFP changes on the falling edge of RSPCLK <i>x</i> .<br>x = [1,2].                                                                                               |

| RSPCLK1   | Receive Special<br>Purpose Clock 1        | Ο          | TTL  | Clock reference for receive special purpose serial output<br>port 1. The clock is a 2.16MHz, 50% duty-cycle signal (op-<br>tionally gapped to match the bandwidth of RSPDAT1.                                                                                                                                                                                      |

| RSPDAT1   | Receive Special<br>Purpose Data 1         | 0          | TTL  | Data output for special purpose serial port 1. RSPDAT1 changes on the falling edge of RSPCLK1.                                                                                                                                                                                                                                                                     |

| RSPVALID1 | Receive Special<br>Purpose Valid 1        | 0          | TTL  | Valid qualifier for special purpose serial port 1.<br>RSPVALID1 is asserted (programmable level) when there<br>is valid data on RSPDAT1. RSPVALID1 changes on the<br>falling edge of RSPCLK1.                                                                                                                                                                      |

| RSPCLK2   | Receive Special<br>Purpose Clock 2        | 0          | TTL  | Clock reference for receive special purpose serial output<br>port 2. The clock is a 2.16MHz, 50% duty-cycle signal (op-<br>tionally gapped to match the bandwidth of RSPDAT2.                                                                                                                                                                                      |

| RSPDAT2   | Receive Special<br>Purpose Data 2         | 0          | TTL  | Data output for special purpose serial port 2. RSPDAT2 changes on the falling edge of RSPCLK2.                                                                                                                                                                                                                                                                     |

### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

| Signal    | Name                                         | <i>I/O</i> | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|----------------------------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSPVALID2 | Receive Special<br>Purpose Valid 2           | 0          | TTL  | Valid qualifier for special purpose serial port 2.<br>RSPVALID2 is asserted (programmable level) when there<br>is valid data on RSPDAT2. RSPVALID2 changes on the<br>falling edge of RSPCLK2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RTOHCLK   | Receive Transport<br>Overhead Clock          | 0          | TTL  | Clock reference for the receive transport overhead port. The clock is a 38.88MHz, 50% duty-cycle signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RTOHVALID | Receive Transport<br>Overhead Valid          | 0          | TTL  | Valid qualifier for the receive transport overhead port.<br>RTOHVALID is asserted (programmable level) when there<br>is valid data on RTOH[30]. RTOHVALID changes on the<br>falling edge of RTOHCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RTOHFP    | Receive Transport<br>Overhead Frame<br>Pulse | 0          | TTL  | Frame reference for the receive transport overhead port.<br>RTOHFP is a one clock cycle wide pulse coincident with<br>the first bit(s) of the first A1 being output on RTOH[30].<br>RTOHFP changes on the falling edge of RTOHCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RTOH[30]  | Receive Transport<br>Overhead Data           | 0          | TTL  | Data output for the receive transport overhead (section and<br>line) bytes extracted from the incoming STS-48 signal.<br>RTOH[30] changes on the falling edge of RTOHCLK.<br>Mode 1: RTOH[3] carries the transport overhead from STS-<br>12 #1 (first interleaved STS-12), RTOH[2] carries the trans-<br>port overhead from STS-12 #2, etc.<br>Mode 2: RTOH[30] carries the entire transport overhead in<br>the order the overhead bytes are received. The most signifi-<br>cant nibble (first received) is output first. RTOH[3] ismost<br>significant bit.                                                                                                                                                               |

| TSPCLK1   | Transmit Special<br>Purpose Clock 1          | 0          | TTL  | Clock reference for the transmit special purpose serialport<br>1. The clock is a 2.16MHz, 50% duty-cycle signal (option-<br>ally gapped to match the bandwidth of TSPDAT1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TSPFP1    | Transmit Special<br>Purpose Frame<br>Pulse 1 | 0          | TTL  | Frame reference for the special purpose serial output port<br>TSPDAT1.<br>Mode 1 (TSPCLK1 continuous): The frame pulse is a one<br>clock cycle wide pulse indicating the start of a new data<br>stream on TSPDAT1. When TSPFP1 is asserted, the first bit<br>of TSPDAT1 is sampled on the second rising edge thereaf-<br>ter. TSPFP1 changes on the falling edge of TSPCLK1.<br>Mode 2 (TSPCLK1 gapped): The frame pulse is a one clock<br>cycle wide pulse (variable width due to the gapped clock)<br>indicating the start of a new data stream on TSPDAT1.<br>When TSPFP1 is asserted, the first bit of TSPDAT1 is sam-<br>pled on the second rising edge thereafter. TSPFP1 changes<br>on the falling edge of TSPCLK1. |

| TSPREN1   | Transmit Special<br>Purpose Read<br>Enable 1 | 0          | TTL  | Read enable signal for the TSPDAT1 data stream. The re-<br>sponse latency from TSPREN1 is asserted until TSPDAT1<br>is sampled is programmable. TSPREN1 changes on the fall-<br>ing edge of TSPCLK1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# Datasheet VSC9112

| Signal  | Name                                             | <i>I/O</i> | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------------------------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSPDAT1 | Transmit Special<br>Purpose Data 1               | Ι          | TTL  | Serial data input for transmit special purpose port 1.<br>TSPDAT1 is sampled on the rising edge of TSPCLK1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TSPCLK2 | Transmit Special<br>Purpose Clock 2              | 0          | TTL  | Clock reference for the transmit special purpose serialport<br>2. The clock is a 2.16MHz, 50% duty-cycle signal (option-<br>ally gapped to match the bandwidth of TSPDAT2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TSPFP2  | Transmit Special<br>Purpose Frame<br>Pulse 2     | 0          | TTL  | Frame reference for the special purpose serial output port<br>TSPDAT2.<br>Mode 1 (TSPCLK2 continuous): The frame pulse is a one<br>clock cycle wide pulse indicating the start of a new data<br>stream on TSPDAT2. When TSPFP2 is asserted, the first bit<br>of TSPDAT_2 is sampled on the second rising edge there-<br>after. TSPFP2 changes on the falling edge of TSPCLK2.<br>Mode 2 (TSPCLK2 gapped): The frame pulse is a one clock<br>cycle wide pulse (variable width due to the gapped clock)<br>indicating the start of a new data stream on TSPDAT2.<br>When TSPFP2 is asserted, the first bit of TSPDAT2 is sam-<br>pled on the second rising edge thereafter. TSPFP2 changes<br>on the falling edge of TSPCLK2. |

| TSPREN2 | Transmit Special<br>Purpose Read<br>Enable 2     | 0          | TTL  | Read enable signal for the TSPDAT2 data stream. The re-<br>sponse latency from TSPREN2 is asserted until TSPDAT2<br>is sampled is programmable. TSPREN2 changes on the fall-<br>ing edge of TSPCLK2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TSPDAT2 | Transmit Special<br>Purpose Data 2               | Ι          | TTL  | Serial data input for transmit special purpose port 2.<br>TSPDAT2 is sampled on the rising edge of TSPCLK2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TTOHCLK | Transmit<br>Transport<br>Overhead Clock          | 0          | TTL  | Clock reference for the transmit transport overhead port.<br>The clock is a 38.88MHz, 50% duty-cycle signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TTOHFP  | Transmit<br>Transport<br>Overhead Frame<br>Pulse | 0          | TTL  | Frame reference for the transmit transport overhead port.<br>TTOHFP is a one clock cycle wide pulse indicating the start<br>of a new data stream on TTOH[30]. The response latency<br>from TTOHFP is asserted until the first bit on TTOH[30]<br>is sampled is programmable (see TTOHREN). TTOHFP<br>changes on the falling edge of TTOHCLK.                                                                                                                                                                                                                                                                                                                                                                                |

| TTOHREN | Transmit<br>Transport<br>Overhead Read<br>Enable | 0          | TTL  | Read enable signal for the TTOH[30] data stream. The re-<br>sponse latency from TTOHREN is asserted until<br>TTOH[30] is sampled is programmable. TTOHREN<br>changes on the falling edge of TTOHCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### STS-48c Physical Layer Packet/ATM Over SONET/SDH Device

| Signal   | Name                                     | <i>I/O</i> | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------------------------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TTOHEN   | Transmit<br>Transport<br>Overhead Enable | Ι          | TTL  | Enable signal for the TTOH[30] data stream. If TTOHEN<br>is asserted, the corresponding byte will be inserted in the<br>corresponding transport overhead byte of the outgoing STS-<br>48 data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |                                          |            |      | Mode 1: Transport overhead for each of the four STS-12<br>channels will be input in bit-serial format on the four data<br>inputs (see TTOH[30] description). If TTOHEN is assert-<br>ed during the first bit of an overhead byte, the corresponding<br>overhead byte on TTOH[3] will be enabled, if TTOHEN is<br>asserted during the third bit of an overhead byte, the corre-<br>sponding overhead byte on TTOH[2] will be enabled (sim-<br>ilar for TTOHEN assertion during fifth and seventh bits).<br>Mode 2: Transport overhead for the entire STS-48 is input<br>as 4-bit nibbles on the TTOH[30] port (see TTOH[30] de-<br>scription). If TTOHEN is asserted during the first nibble of<br>an overhead byte, the corresponding overhead byte is en-<br>abled. |

|          |                                          |            |      | Note: The transmit section and line processing blocks can selectively overwrite/modify overhead bytes inserted through the TTOH interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TTOH[30] | Transmit<br>Transport<br>Ovehead Data    | I          | TTL  | Data input for the transport overhead (section and line)<br>bytes to be inserted in the outgoing STS-48 signal.<br>TTOH[30] is sampled on the rising edge of TTOHCLK.<br>Mode 1: TTOH[3] carries the transport overhead for STS-<br>12 #1 (first interleaved STS-12), TTOH[2] carries the trans-<br>port overhead for STS-12 #2, etc.<br>Mode 2: TTOH[30] carries the entire STS-48 transport<br>overhead in the order the overhead bytes are to be inserted.<br>The most significant nibble (first received) is input first.<br>TTOH[3] is the most significant bit.                                                                                                                                                                                                |