### ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

#### **Features**

- Operates at Either STS-3/STM-1 (155.52Mb/s) or STS-12/STM-4 (622.08Mb/s) Data Rates

- Compatible with Industry ATM UNI Devices

- On Chip Clock Generation of the 155.52MHz or 622.08MHz High-Speed Clock (MUX)

- On-Chip Clock Recovery of the 155.52MHz or 622.08MHz High-Speed Clock (DEMUX)

- 8-Bit Parallel TTL Interface

- SONET/SDH Frame Recovery

- · Lock Detect for Both CRU and CMU

- Loss of Signal (LOS) Input and LOS Detection

- +3.3V/5V Programmable PECL Serial Interface

- Provides Equipment, Facilities and Split Loopback Modes as ell as Loop Timing Mode

- Provides TTL and PECL Reference Clock Inputs

- Meets Bellcore, ITU and ANSI Specifications for Jitter Performance

- Low Power: 1.0 Watts Typical

- 100-Pin PQFP Package

### General Description

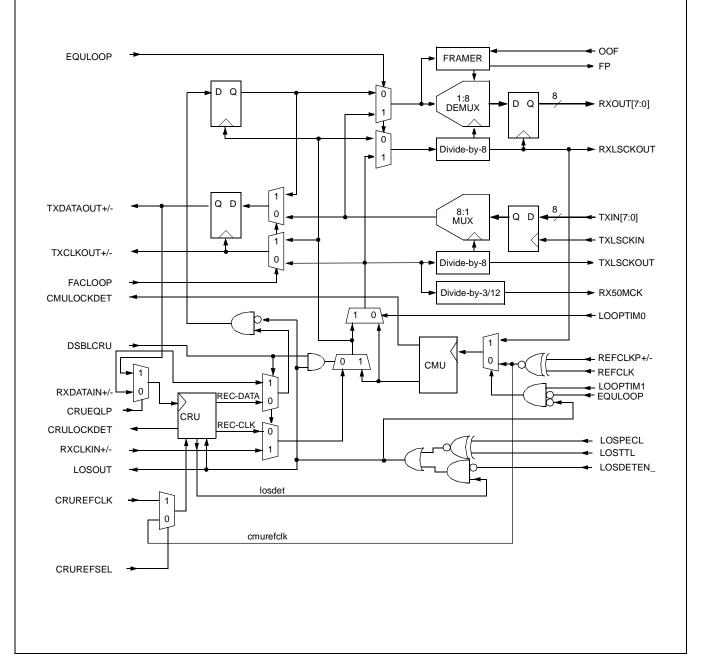

The VSC8113 is an ATM/SONET/SDH compatible transceiver integrating an on-chip Clock Multiplication Unit (CMU) for the high-speed clock as well as a Clock and Data Recovery (CDR) unit with 8-bit serial-to-parallel and parallel-to-serial data conversion. The PLL clock is used for serialization in the transmit direction (MUX). The recovered clock is used for deserialization in the receive direction (DEMUX). The demultiplexer contains SONET/SDH frame detection and recovery. The device provides both facility and equipment loopback modes and two loop timing modes. The VSC8113 is packaged in a 100-pin PQFP with integrated heat spreader for optimum thermal performance and reduced cost. The VSC8113 provides an integrated solution for ATM physical layers and SONET/SDH systems applications.

### Functional Description

The VSC8113 is designed to provide a SONET/SDH-compliant interface between the high-speed optical networks and the lower speed User Network Interface devices such as the PM5355 S/UNI-622. The VSC8113 converts 8-bit parallel data at 77.76Mb/s or 19Mb/s to a serial bit stream at 622.08Mb/s or 155.52Mb/s, respectively. The VSC8113 also provides a Facility Loopback function which loops the received high-speed data and clock (optionally recovered on-chip) directly to the high-speed transmit outputs. A Clock Multiplier Unit (CMU) is integrated into the transmit circuit to generate the high-speed clock for the serial output data stream from input reference frequencies of 19.44, 38.88, 51.84 or 77.76 MHz. The CMU can be bypassed with the received/recovered clock in loop timing mode thus synchronizing the entire part to a single clock. See the Block Diagram for major functional blocks associated with the VSC8113.

The receive section provides the serial-to-parallel conversion, converting the 622Mb/s or 1.55.52Mb/s bit stream to an 8-bit parallel output at 19.44Mb/s or 77.76MHz, respectively. A Clock Recovery Unit (CRU) is integrated into the receive circuit to recover the high-speed clock from the received serial data stream. The receive section provides an Equipment Loopback function which will loop the low-speed transmit data and clock back through the receive section to the 8-bit parallel data bus and clock outputs. The VSC8113 also provides the option of selecting between either its internal CRU's recovered clock and data signals or optics con-

## Data Sheet VSC8113

taining a CRU clock and data signals. (In this mode the VSC8113 operates just like the VSC8111). The receive section also contains a SONET/SDH frame detector circuit which is used to provide frame pluses during the A1, A2 boundary in the serial to parallel converter. This only occurs when OOF is HIGH. Both internal and external LOS functions are supported.

### VSC8113 Block Diagram

## ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

#### **Transmit Section**

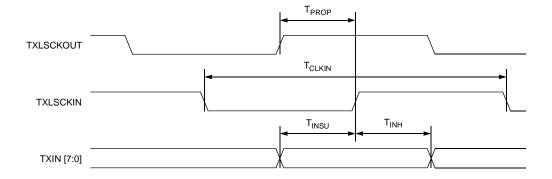

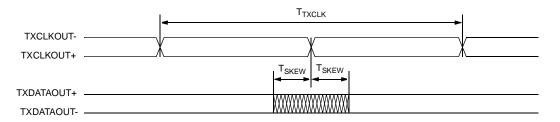

Byte-wide data is presented to TXIN[7:0] and is clocked into the part on the rising edge of TXLSCKIN. See Figure 1. The data is then serialized (MSB leading) and presented at the TXDATAOUT+/- pins. TXDATAOUT is clocked out on the falling edge of TXCLKOUT+. The serial output stream is synchronized to the CMU generated clock which is a phase-locked and frequency scaled version of the input reference clock. External control inputs B0-B2 and STS-12 select the multiply ratio of the CMU for either STS-12 (622Mb/s) or STS-3 (155MbS) transmission (see Table 12). A divide-by-8 version of the CMU clock (TXLSCKOUT) should be used to synchronize the transmit interface of the UNI device to the transmit input registers on the VSC8113 (see *Interconnecting the Byte Clocks* section).

TXDATAOUT+

TXDATAOUTTXCLKOUT+

TXCLKOUTTXCLKOUTTXLSCKIN

TXLSCKUT

TXLSCKOUT

Figure 1: Data and Clock Transmit Block Diagram

#### **Receive Section**

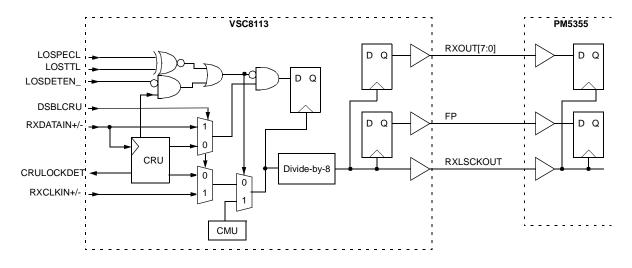

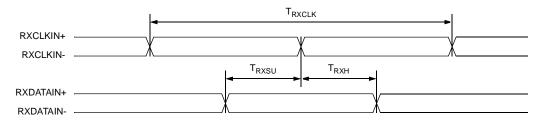

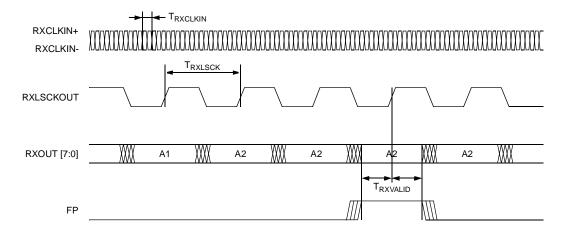

High-speed Non-Return to Zero (NRZ) serial data at 622Mb/s or 155Mb/s are received by the RXDATAIN inputs. The CRU recovers the high-speed clock from the serial data input. The serial data is converted to byte-wide parallel data and presented on RXOUT[7:0] pins. A divide-by-8 version of the high-speed clock (RXLSCKOUT) should be used to synchronize the byte-serial RXOUT[7:0] data with the receive portion of the UNI device. The on-chip CRU is bypassed by setting the DSBLCRU input HIGH. In this mode, the serial input data and corresponding clock are received by the RXDATAIN and RXCLKIN inputs, respectively. RXDATAIN is clocked in on the rising edge of RXCLKIN+. See Figure 2.

The receive section also includes frame detection and recovery circuitry which detects the SONET/SDH frame, aligns the received serial data on byte boundaries, and initiates a frame pulse on FP coincident with the byte-aligned data. The frame recovery is initiated when OOF is held HIGH which must occur at least 4 byte clock cycles before the A1A2 boundary. The OOF input control is a level-sensitive signal, and the VSC8113 will continually perform frame detection and recovery as long as this pin is held HIGH even if one or more frames has been detected. Frame detection and recovery occurs when a series of three A1 bytes followed by three A2 bytes has been detected. The parallel output data on RXOUT[7:0] will be byte-aligned starting on the third A2 byte. When a frame is detected, a single byte clock period long pulse is generated on FP which is synchronized with the byte-aligned third A2 byte on RXOUT[7:0]. The frame detector sends a FP pulse only if OOF is HIGH.

Data Sheet VSC8113

#### Loss of Signal

The VSC8113 features Loss of Signal (LOS) detection. Loss of Signal is declared if the incoming serial data stream has no transition continuously for more than 128 bits. During an LOS condition, the VSC8113 forces the receive data LOW which is an indication for any downstream equipment that an optical interface failure has occurred. The receive section continues to be clocked by the CRU as it is now locked to the "CRUREF-CLK" unless "DSBLCRU" is active, in which case it will be clocked by the CMU. This LOS condition will be removed when the part detects more than 16 transitions in a 128-bit time window. This LOS detection feature can be disabled by applying a high level to LOSDETEN\_ input. The VSC8113 also has a TTL input LOSTTL and a PECL input LOSPECL to force the part into a LOS state. Most optics have a PECL output usually called "SD" or "FLAG" indicating a lack of or presence of optical power. Depending on the optics manufactured, this signal is either active HIGH or active LOW. The LOSTTL and LOSPECL inputs are XNOR'd to generate an internal LOS control signal (see Figure 2). The optics "SD" output should be connected to LOSPECL. The LOSTTL input should be tied LOW if the optics "SD" output is active HIGH. If it's active LOW, tie LOSTTL HIGH. The inverse is true if the optics use "FLAG" for loss of signal.

Figure 2: Data and Clock Receive Block Diagram

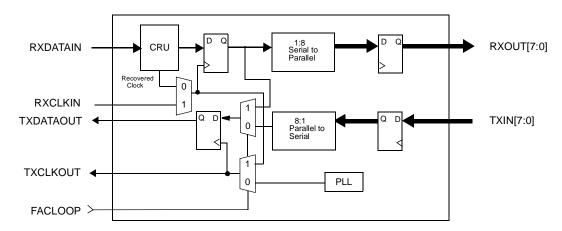

#### **Facility Loopback**

The Facility Loopback function is controlled by the FACLOOP signal. When the FACLOOP signal is set high, the Facility Loopback mode is activated and the high-speed serial receive data (RXDATAIN) is presented at the high-speed transmit output (TXDATAOUT). See Figure 3. In addition, the high-speed received/recovered clock is selected and presented at the high-speed transmit clock output (TXCLKOUT). In Facility Loopback mode the high-speed receive data (RXDATAIN) is also converted to parallel data and presented at the low speed receive data output pins (RXOUT[7:0]). The receive clock (RXCLKIN) is also divided down and presented at the low speed clock output (RXLSCKOUT).

ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

Figure 3: Facility Loopback Data Path

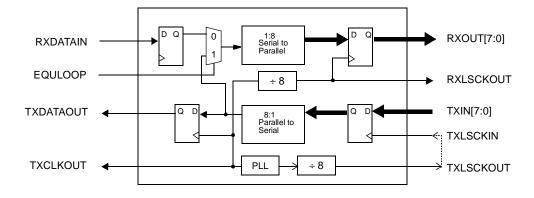

#### **Equipment Loopback**

The Equipment Loopback function is controlled by the EQULOOP signal. When the EQULOOP signal is set HIGH, the Equipment Loopback mode is activated and the high-speed transmit data generated from the parallel to serial conversion of the low-speed data (TXIN[7:0]) is selected and converted back to parallel data in the receiver section and presented at the low speed parallel outputs (RXOUT[7:0]). See Figure 4. The internally generated 155/622MHz clock is used to generate the low-speed receive clock output (RXLSCKOUT). In Equipment Loopback mode, the transmit data (TXIN[7:0]) is serialized and presented at the high-speed output (TXDATAOUT) along with the high-speed transmit clock (TXCLKOUT) which is generated by the on-chip clock multiplier unit.

#### **CRU Equipment Loopback**

Exactly the same as equipment loopback, the point where the transmit data is looped back is moved all the way back to the high-speed I/O. When the CRUEQLP signal is set HIGH, transmit data is looped back to the CRU, replacing RXDATAIN±

Figure 4: Equipment Loopback Data Path

Data Sheet VSC8113

TXLSCKIN

#### **Split Loopback**

Equipment and facility loopback modes can be enabled simultaneously. In this case, high-speed serial data received (RXDATAIN) and received/recovered clock are mux'd through to the high-speed serial outputs (TXDATAOUT) and (TXCLKOUT). The low-speed transmit byte wide bus(TXIN[7:0]) and (TXLSCKIN) are mux'd into the low-speed byte wide receive output bus (RXOUT[7:0]) and (RXLSCKOUT). See Figure 5.

RXDATAIN

CRU

D Q

Serial to Parallel

RXCLKIN

DSBLCRU

TXDATAOUT

RXLSCKOUT

RXLSCKOUT

RXLSCKOUT

TXIN[[7:0]

Figure 5: Split Loopback Datapath

#### **Loop Timing**

TXCLKOUT ◀

LOOPTIM0 mode bypasses the CMU when the LOOPTIM0 input is asserted HIGH. In this mode, the CMU is bypassed by using the receive clock (RXCLKIN), and the entire part is synchronously clocked from a single external source.

LOOPTIM1 mode bypasses the REFCLK input and uses the divide-by-8 version of the receive clock as the reference input to the CMU. This mode is selected by asserting the LOOPTIM1 input HIGH. The part is forced out of this mode if it is in the LOS state or in Equipment Loopback to prevent the CMU from feeding its own clock back.

#### **Clock Synthesis**

The VSC8113 uses an integrated Phase-Locked Loop (PLL) for clock synthesis of the 622MHz high-speed clock used for serialization in the transmitter section. The PLL is comprised of a Phase-Frequency Detector (PFD), an integrating operation amplifier and a Voltage Controlled Oscillator (VCO) configured in classic feedback system. The PFD compares the selected divided down version of the 622MHz VCO (for pins B0-B2, select divide-by ratios of 8, 12, 16 and 32, see Table 12) and the reference clock. The integrator provides a transfer function between input phase error and output voltage control. The VCO portion of the PLL is a voltage controlled ring-oscillator with a center frequency of 622MHz.

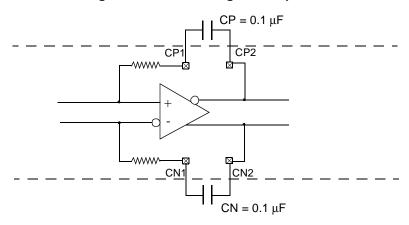

The reactive elements of the integrator are located off-chip and are connected to the feedback loop of the amplifier through the CP1, CP2, CN1 and CN2 pins. The configuration of these external surface-mounted capacitors is shown in Figure 6. Table 1 shows the recommended external capacitor values for the configurable reference frequencies.

Good analog design practices should be applied to the board design for these external components. Tightly controlled analog ground and power planes should be provided for the PLL portion of the circuitry. The dedicated PLL power (VDDANA) and ground (VSSANA) pins should have quiet supply planes to minimize jitter

### ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

generation within the clock synthesis unit. This is accomplished by either using a ferrite bead or a C-L-C choke ( $\pi$  filter) on the (VDDANA) power pins. Note: Vitesse recommends a ( $\pi$  filter) C-L-C choke over using a ferrite bead. All ground planes should be tied together using multiple vias.

The VSC8113 features a lock detect function for the CMU, called CMULOCKDET. It generates low-going pulses when the CMU is locked to the incoming REFCLK. This is accomplished by comparing the phase of the synthesized clock to the reference clock. If the CMULOCKDET output remains HIGH for  $\geq 10 \mu s$ , the CMU is locked.

**Table 1: Recommended External Capacitor Values**

| Reference Frequency [MHz] | Divide Ratio | CP  | CN  | Туре | Size      | Tol.   |

|---------------------------|--------------|-----|-----|------|-----------|--------|

| 19.44                     | 32           | 0.1 | 0.1 | X7R  | 0603/0803 | +/-10% |

| 38.88                     | 16           | 0.1 | 0.1 | X7R  | 0603/0803 | +/-10% |

| 51.84                     | 12           | 0.1 | 0.1 | X7R  | 0603/0803 | +/-10% |

| 77.76                     | 8            | 0.1 | 0.1 | X7R  | 0603/0803 | +/-10% |

**Figure 6: External Integrator Capacitor**

#### **Reference Clocks**

To improve jitter performance and to provide flexibility, an additional differential PECL reference clock input is provided. This reference clock is internally XNOR'd with a TTL reference clock input to generate the reference for the CMU. Vitesse recommends using the differential PECL input and tying the unused TTL reference clock LOW. If the TTL reference clock is used, the positive side of the differential PECL reference clock, REFCLKP+ should be tied to ground. REFCLKP+/- are internally biased with on-chip resistors to 1.65V. See Figure 14 for schematic of internal biasing of differential I/Os.

The CRU has the option of either using the CMU's reference clock or its own independent reference clock, CRUREFCLK. If the CMU reference clock is used, it must be 78MHz. This is accomplished with the control signal CRUREFSEL. The CRUREFCLK should be used if the system is being operated in either a regeneration or looptiming mode. In either of these modes, the quality of the CRUREFCLK is not a concern; thus it can be driven by a simple 77.76MHz crystal—the key is its' independence of the CMU's reference clock.

Data Sheet VSC8113

#### **Clock Recovery**

The fully monolithic CRU) consists of a Phase Detector, a Frequency Detector, a Loop Filter and a Voltage Controlled Oscillator (VCO). The phase detector compares the phase information of the incoming data with the recovered clock. The frequency detector compares the frequency component of the data input with the recovered clock to provide the pull in energy during lock acquisition. The Loop Filter integrates the phase information from the phase and frequency detectors and provides the control voltage to the VCO.

The CRU provides a lock detect function. If the frequencies of the serial data stream and the CRU's recovered clock are different, a data bit in the serial data stream will occasionally be dropped. If the Frequency Detector does not detect this condition in a moving 1.5µs window, the CRULOCKDET output is asserted to signal that the CRU is frequency-locked to the serial data stream. This output is forced LOW if it detects that a data bit is dropped or if the recovered clock frequency drifts more than 5% from the CMU's output frequency.

#### **Jitter Tolerance**

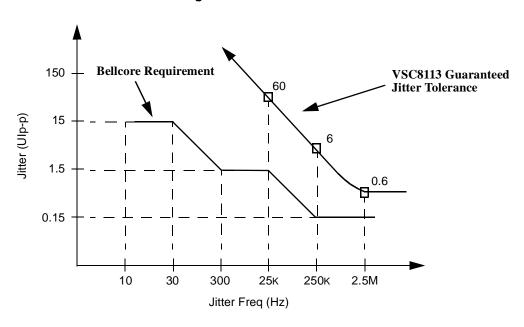

Jitter Tolerance is the ability of the Clock Recovery Unit to track timing variation in the received data stream. The Bellcore and ITU specifications allow the received optical data to contain jitter. The amount that must be tolerated is a function of the frequency of the jitter. At high frequencies, the specifications do not require the CRU to tolerate large amounts, whereas at low frequencies, many unit intervals (bit times) of jitter have to be tolerated. The CRU is designed to tolerate this jitter with margin over the specification limits. See Figure 7. The CRU obtains and maintains lock based on the data transition information. When there is no transition on the data stream, the recovered clock frequency can drift. The VSC8113 can maintain lock over 100 bits of no switching on data stream.

Figure 7: Jitter Tolerance

## ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

### **AC Timing Characteristics**

Figure 8: Receive High-Speed Data Input Timing Diagram

Table 2: Receive High-Speed Data Input Timing (STS-12 Operation)

| Parameter          | Description                                    |     | Тур   | Max | Units |

|--------------------|------------------------------------------------|-----|-------|-----|-------|

| T <sub>RXCLK</sub> | Receive clock period                           | -   | 1.608 | -   | ns    |

| T <sub>RXSU</sub>  | Serial data setup time with respect to RXCLKIN | 250 | -     | -   | ps    |

| T <sub>RXH</sub>   | Serial data hold time with respect to RXCLKIN  | 250 | -     | -   | ps    |

**Table 3: Receive High-Speed Data Input Timing (STS-3 Operation)**

| Parameter          | Description                                    |     | Тур  | Max | Units |

|--------------------|------------------------------------------------|-----|------|-----|-------|

| T <sub>RXCLK</sub> | Receive clock period                           | -   | 6.43 | -   | ns    |

| T <sub>RXSU</sub>  | Serial data setup time with respect to RXCLKIN | 1.5 | -    | -   | ns    |

| $T_{RXH}$          | Serial data hold time with respect to RXCLKIN  | 1.5 | -    | 1   | ns    |

Figure 9: Transmit Data Input Timing Diagram

## Data Sheet VSC8113

Table 4: Transmit Data Input Timing (STS-12 Operation)

| Parameter          | Description                                                              |     | Тур   | Max | Units |

|--------------------|--------------------------------------------------------------------------|-----|-------|-----|-------|

| T <sub>CLKIN</sub> | Transmit data input byte clock period                                    | -   | 12.86 | -   | ns    |

| T <sub>INSU</sub>  | Transmit data setup time with respect to TXLSCKIN                        | 1.0 | -     | -   | ns    |

| T <sub>INH</sub>   | Transmit data hold time with respect to TXLSCKIN                         | 1.0 | -     | -   | ns    |

| T <sub>PROP</sub>  | Maximum allowable propagation delay for connecting TXLSCKOUT to TXLSCKIN | -   | -     | 3.5 | ns    |

Table 5: Transmit Data Input Timing (STS-3 Operation)

| Parameter          | Description                                                                             |     | Тур   | Max | Units |

|--------------------|-----------------------------------------------------------------------------------------|-----|-------|-----|-------|

| T <sub>CLKIN</sub> | Transmit data input byte clock period                                                   | -   | 51.44 | -   | ns    |

| T <sub>INSU</sub>  | Transmit data setup time with respect to TXLSCKIN                                       | 1.0 | -     | -   | ns    |

| $T_{INH}$          | Transmit data hold time with respect to TXLSCKIN                                        | 1.0 | -     | -   | ns    |

| T <sub>PROP</sub>  | Maximum allowable propagation delay for connecting TXLSCKOUT to TXLSCKIN <sup>(1)</sup> | -   | -     | 30  | ns    |

NOTE: (1) Duty cycle for TXLSCKOUT is 50% +/- 10% worst case.

Figure 10: Receive Data Output Timing

Table 6: Receive Data Output Timing Table (STS-12 Operation)

| Parameter            | Description                                                                            |     | Тур   | Max | Units |

|----------------------|----------------------------------------------------------------------------------------|-----|-------|-----|-------|

| T <sub>RXCLKIN</sub> | Receive clock period                                                                   | -   | 1.608 | -   | ns    |

| T <sub>RXLSCK</sub>  | Receive data output byte clock period                                                  | -   | 12.86 | -   | ns    |

| T <sub>RXVALID</sub> | Time data on RXOUT [7:0] and FP is valid before and after the rising edge of RXLSCKOUT | 4.0 | -     | -   | ns    |

| $T_{PW}$             | Pulse width of frame detection pulse FP                                                | -   | 12.86 | -   | ns    |

## ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

Table 7: Receive Data Output Timing (STS-3 Operation)

| Parameter            | Description                                                                           |    | Тур   | Max | Units |

|----------------------|---------------------------------------------------------------------------------------|----|-------|-----|-------|

| T <sub>RXCLKIN</sub> | Receive clock period                                                                  | -  | 6.43  | -   | ns    |

| T <sub>RXLSCKT</sub> | Receive data output byte clock period                                                 | -  | 51.44 | -   | ns    |

| T <sub>RXVALID</sub> | Time data on RXOUT[7:0] and FP is valid before and after the rising edge of RXLSCKOUT | 22 | -     | -   | ns    |

| $T_{PW}$             | Pulse width of frame detection pulse FP                                               | -  | 51.44 | -   | ns    |

Figure 11: Transmit High-Speed Data Timing Diagram

Table 8: Transmit High-Speed Data Timing (STS-12 Operation)

| Parameter          | Description                                                            |   | Тур   | Max | Units |

|--------------------|------------------------------------------------------------------------|---|-------|-----|-------|

| T <sub>TXCLK</sub> | Transmit clock period                                                  | - | 1.608 | -   | ns    |

| T <sub>SKEW</sub>  | Skew between the falling edge of TXCLKOUT+ and valid data on TXDATAOUT | - | -     | 250 | ps    |

**Table 9: Transmit High-Speed Data Timing (STS-3 Operation)**

| Parameter          | Description                                                            |   | Тур  | Max | Units |

|--------------------|------------------------------------------------------------------------|---|------|-----|-------|

| T <sub>TXCLK</sub> | Transmit clock period                                                  | - | 6.43 | -   | ns    |

| T <sub>SKEW</sub>  | Skew between the falling edge of TXCLKOUT+ and valid data on TXDATAOUT | - | -    | 250 | ps    |

Data Sheet VSC8113

### Data Latency

The VSC8113 contains several operating modes, each of which exercise different logic paths through the part. Table 10 bounds the data latency through each path with an associated clock signal.

#### **Table 10: Data Latency**

| Circuit Mode        | Description                                     | Clock<br>Reference | Range of Clock<br>Cycles |

|---------------------|-------------------------------------------------|--------------------|--------------------------|

| Transmit            | Data TXIN [7:0] to MSB at TXDATAOUT             | TXCLKOUT           | 4-13                     |

| Receive             | MSB at RXDATAIN to data on RXOUT[7:0]           | RXCLKIN            | 25-35                    |

| Equipment Loopback  | Byte data TXIN [7:0] to byte data on RXOUT[7:0] | TXCLKOUT           | 27-35                    |

| Facilities Loopback | MSB at RXDATAIN to MSB at TXDATAOUT             | RXCLKIN            | 2-4                      |

### Clock Recovery Unit

#### Table 11: Reference Frequency for the CRU

| CRUREFSEL | STS12                                     | B2 | B1 | B0 | CRUREFCLK<br>Frequency<br>[MHz] | Output<br>Frequency<br>[MHz] |

|-----------|-------------------------------------------|----|----|----|---------------------------------|------------------------------|

| 1         | 1                                         | X  | X  | X  | 77.76 ± 500ppm                  | 622.08                       |

| 1         | 0                                         | X  | X  | X  | 77.76 ± 500ppm                  | 155.52                       |

| 0         | Uses CMU's Reference Clock (see Table 12) |    |    |    |                                 |                              |

### **Clock Multiplier Unit**

#### **Table 12: Reference Frequency Selection and Output Frequency Control**

| STS12 | B2 | B1 | B0 | Reference<br>Frequency<br>[MHz] | Output<br>Frequency<br>[MHz] |

|-------|----|----|----|---------------------------------|------------------------------|

| 1     | 1  | 1  | 0  | 19.44                           | 622.08                       |

| 1     | 0  | 1  | 0  | 38.88                           | 622.08                       |

| 1     | 0  | 0  | 1  | 51.84                           | 622.08                       |

| 1     | 0  | 0  | 0  | 77.76                           | 622.08                       |

| 0     | 1  | 1  | 0  | 19.44                           | 155.52                       |

| 0     | 0  | 1  | 0  | 38.88                           | 155.52                       |

| 0     | 0  | 0  | 1  | 51.84                           | 155.52                       |

| 0     | 0  | 0  | 0  | 77.76                           | 155.52                       |

## ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

#### **Table 13: Clock Multiplier Unit Performance**

| Name                 | Description                                                  | Min | Тур | Max | Units |

|----------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| RCd                  | Reference clock duty cycle                                   | 40  |     | 60  | %     |

| RCj                  | Reference clock jitter (RMS) at 77.76 MHz ref <sup>(1)</sup> |     |     | 13  | ps    |

| RCj                  | Reference clock jitter (RMS) at 51.84 MHz ref <sup>1)</sup>  |     |     | 12  | ps    |

| RCj                  | Reference clock jitter (RMS) at 38.88 MHz ref <sup>(1)</sup> |     |     | 9   | ps    |

| RCj                  | Reference clock jitter (RMS) at 19.44 MHz ref <sup>(1)</sup> |     |     | 5   | ps    |

| $RC_f$               | Reference clock frequency tolerance <sup>(2)</sup>           | -20 |     | +20 | ppm   |

| OCj                  | Output clock jitter (RMS) @ 77.76 MHz ref <sup>(3)</sup>     |     |     | 8   | ps    |

| OCj                  | Output clock jitter (RMS) @ 51.84 MHz ref <sup>(3)</sup>     |     |     | 10  | ps    |

| OCj                  | Output clock jitter (RMS) @ 38.88 MHz ref <sup>(3)</sup>     |     |     | 13  | ps    |

| OCj                  | Output clock jitter (RMS) @ 19.44 MHz ref <sup>(3)</sup>     |     |     | 15  | ps    |

| OCf <sub>range</sub> | Output frequency                                             | 620 |     | 624 | MHz   |

| OCd                  | Output clock duty cycle                                      | 40  |     | 60  | %     |

NOTES: Jitter specification is defined utilizing a 12kHz to 5MHz LP-HP single pole filter.

- (1) These Reference Clock Jitter limits are required for the outputs to meet SONET system level jitter requirements (<10 mUIrms).

- (2) Required to meet SONET output frequency stability requirements.

- (3) Measured.

#### AC Characteristics

#### **Table 14: PECL and TTL Outputs**

| Parameters   | Description           | Min | Тур | Max | Units | Conditions |

|--------------|-----------------------|-----|-----|-----|-------|------------|

| $T_{R,TTL}$  | TTL output rise time  | _   | 2   | _   | ns    | 10%-90%    |

| $T_{F,TTL}$  | TTL output fall time  | _   | 1.5 | _   | ns    | 10%-90%    |

| $T_{R,PECL}$ | PECL output rise time | _   | 350 | _   | ps    | 20%-80%    |

| $T_{F,PECL}$ | PECL output fall time | _   | 350 | _   | ps    | 20%-80%    |

# Data Sheet VSC8113

### **DC Characteristics**

#### **Table 15: PECL and TTL Inputs and Outputs**

| Parameters         | Description                        | Min                        | Тур | Max                                                                    | Units | Conditions                                       |

|--------------------|------------------------------------|----------------------------|-----|------------------------------------------------------------------------|-------|--------------------------------------------------|

| V <sub>OH</sub>    | Output HIGH voltage (PECL)         | _                          | _   | V <sub>DDP</sub> –<br>0.9V                                             | V     | _                                                |

| V <sub>OL</sub>    | Output LOW voltage (PECL)          | 0.7                        | _   | _                                                                      | V     | _                                                |

| V <sub>OCM</sub>   | Output common-mode range (PECL)    | 1.1                        | _   | V <sub>DDP</sub> –<br>1.3V                                             | V     | _                                                |

| $\Delta V_{OUT75}$ | Differential output voltage (PECL) | 600                        | _   | 1300                                                                   | mV    | $75\Omega$ to $V_{DDP} - 2.0V$                   |

| $\Delta V_{OUT50}$ | Differential output voltage (PECL) | 600                        | _   | 1300                                                                   | mV    | $50\Omega$ to $V_{DDP} - 2.0V$                   |

| V <sub>IH</sub>    | Input HIGH voltage (PECL)          | V <sub>DDP</sub> -<br>0.9V | _   | V <sub>DDP</sub> – 0.3V                                                | V     | For single-ended                                 |

| V <sub>IL</sub>    | Input LOW voltage (PECL)           | 0                          | _   | V <sub>DDP</sub> –<br>1.72V                                            | V     | For single-ended                                 |

| $\Delta V_{ m IN}$ | Differential input voltage (PECL)  | 400                        | _   | 1600                                                                   | mV    | _                                                |

| V <sub>ICM</sub>   | Input common-mode range (PECL)     | $1.5 - \Delta V_{IN}/2$    | _   | $\begin{array}{c} V_{DDP}\!-\!1.0 \\ -\Delta V_{IN}\!/\!2 \end{array}$ | V     | _                                                |

| V <sub>OH</sub>    | Output HIGH voltage (TTL)          | 2.4                        | _   | _                                                                      | V     | $I_{OH} = -1.0 \text{mA}$                        |

| V <sub>OL</sub>    | Output LOW voltage (TTL)           | _                          | _   | 0.5                                                                    | V     | $I_{OL} = +1.0$ mA                               |

| V <sub>IH</sub>    | Input HIGH voltage (TTL)           | 2.0                        | _   | 5.5                                                                    | V     | _                                                |

| V <sub>IL</sub>    | Input LOW voltage (TTL)            | 0                          | _   | 0.8                                                                    | V     | _                                                |

| I <sub>IH</sub>    | Input HIGH current (TTL)           | _                          | 50  | 500                                                                    | μΑ    | 2.0V< V <sub>IN</sub> < 5.5V,<br>Typical at 2.4V |

| $I_{IL}$           | Input LOW current (TTL)            | _                          | _   | -500                                                                   | μΑ    | $-0.5V < V_{IN} < 0.8V$                          |

#### **Table 16: Power Supply Currents**

| Parameter      | Description                               | Min | Тур | Max | Units | Conditions |

|----------------|-------------------------------------------|-----|-----|-----|-------|------------|

| $I_{DD}$       | Power supply current from V <sub>DD</sub> | _   | _   | 480 | mA    |            |

| P <sub>D</sub> | Power dissipation (worst case)            | _   | _   | 1.6 | W     |            |

## ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

| Power Supply Voltage (V <sub>DD</sub> ) Potential to GND                                                                                                                               | 0.5V to +4V                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| PECL I/O Supply Voltage (V <sub>DDP</sub> ) Potential to GND                                                                                                                           | 0.5V to +6V                                              |

| DC Input Voltage (PECL inputs)                                                                                                                                                         | 0.5V to V <sub>DDP</sub> +0.5V                           |

| DC Input Voltage (TTL inputs)                                                                                                                                                          | 0.5V to 5.5V                                             |

| DC Output Voltage (TTL outputs)                                                                                                                                                        | 0.5V to V <sub>DD</sub> + 0.5V                           |

| Output Current (TTL outputs)                                                                                                                                                           | ±50m/                                                    |

| Output Current (PECL outputs)                                                                                                                                                          | ±50m                                                     |

| Case Temperature Under Bias                                                                                                                                                            | 55° to +125°                                             |

| Storage Temperature                                                                                                                                                                    | 65°C to +150°C                                           |

| Maximum Input ESD (Human Body Model)                                                                                                                                                   |                                                          |

| NOTE (I) C . C . I' . I I "AI I . M . D . "                                                                                                                                            | be applied to devices one at a time without causin       |

| permanent damage. Functionality at or exceeding the values listed is periods may affect device reliability.                                                                            | not implied. Exposure to these values for extende        |

| permanent damage. Functionality at or exceeding the values listed is periods may affect device reliability.                                                                            | not implied. Exposure to these values for extende        |

| permanent damage. Functionality at or exceeding the values listed is                                                                                                                   |                                                          |

| permanent damage. Functionality at or exceeding the values listed is periods may affect device reliability.<br><b>Recommended Operating Conditions</b> Power Supply Voltage $(V_{DD})$ | +3.3V±5 9                                                |

| permanent damage. Functionality at or exceeding the values listed is periods may affect device reliability.                                                                            | +3.3V±5 9                                                |

| permanent damage. Functionality at or exceeding the values listed is periods may affect device reliability.  Recommended Operating Conditions                                          | +3.3V±5°<br>+3.3V or +5.0V±5°<br>0° Ambient to +70°C Cas |

## Data Sheet VSC8113

## ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

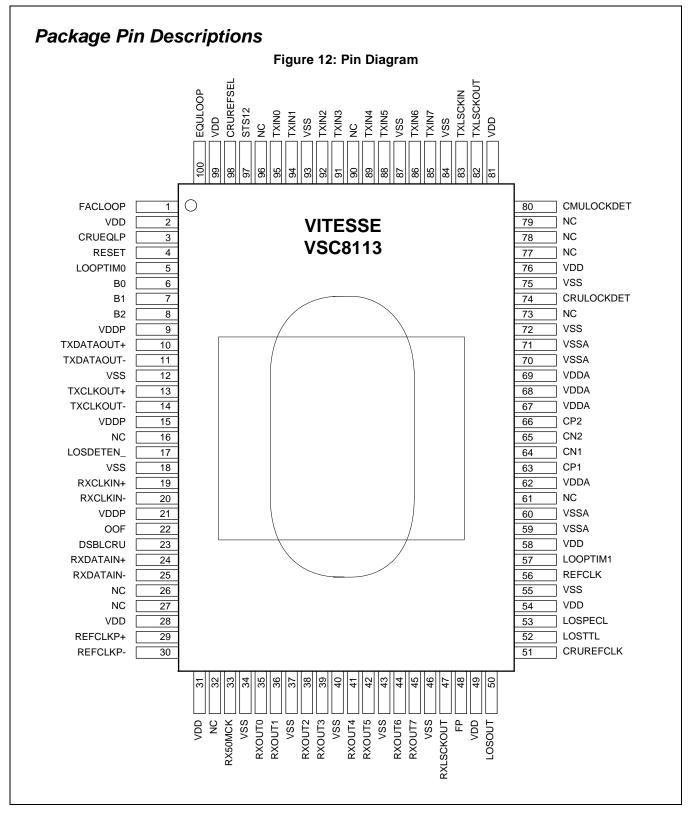

**Table 17: Pin Identifications**

| Pin | Signal     | I/O | Level    | Pin Description                                                                          |  |

|-----|------------|-----|----------|------------------------------------------------------------------------------------------|--|

| 1   | FACLOOP    | I   | TTL      | Facility loopback, loops high-speed receive data and clock directly to transmit outputs. |  |

| 2   | VDD        | _   | +3.3V    | Power Supply                                                                             |  |

| 3   | CRUEQLP    | I   | TTL      | Loops TXDATAOUT to the CRU replacing RXDATAIN+/-                                         |  |

| 4   | RESET      | I   | TTL      | Resets frame detection, dividers, controls; active high                                  |  |

| 5   | LOOPTIM0   | I   | TTL      | Enable loop timing operation; active HIGH                                                |  |

| 6   | В0         | I   | TTL      | Reference clock select, refer to Table 12                                                |  |

| 7   | B1         | I   | TTL      | Reference clock select, refer to Table 12                                                |  |

| 8   | B2         | I   | TTL      | Reference clock select, refer to Table 12                                                |  |

| 9   | VDDP       | _   | +3.3/+5V | +3.3V or +5V power supply for PECL I/Os                                                  |  |

| 10  | TXDATAOUT+ | О   | PECL     | Transmit output, high-speed differential data, true                                      |  |

| 11  | TXDATAOUT- | О   | PECL     | Transmit output, high-speed differential data, complement                                |  |

| 12  | VSS        | _   | GND      | Ground                                                                                   |  |

| 13  | TXCLKOUT+  | О   | PECL     | Transmit high-speed clock differential output, true                                      |  |

| 14  | TXCLKOUT-  | О   | PECL     | Transmit high-speed clock differential output, complement                                |  |

| 15  | VDDP       | _   | +3.3/+5V | +3.3V or +5V power supply for PECL I/Os                                                  |  |

| 16  | NC         | _   | _        | No connection                                                                            |  |

| 17  | LOSDETEN_  | I   | TTL      | Enables internal LOS detection, active LOW                                               |  |

| 18  | VSS        | _   | GND      | Ground                                                                                   |  |

| 19  | RXCLKIN+   | I   | PECL     | Receive high-speed differential clock input, true                                        |  |

| 20  | RXCLKIN-   | I   | PECL     | Receive high-speed differential clock input, complement                                  |  |

| 21  | VDDP       | _   | +3.3/+5V | +3.3V or +5V power supply for PECL I/Os                                                  |  |

| 22  | OOF        | I   | TTL      | Out Of Frame. Frame detection initiated with high level                                  |  |

| 23  | DSBLCRU    | I   | TTL      | Disable on-chip clock recovery unit, active HIGH                                         |  |

| 24  | RXDATAIN+  | I   | PECL     | Receive high-speed differential data input, true                                         |  |

| 25  | RXDATAIN-  | I   | PECL     | Receive high-speed differential data input, complement                                   |  |

| 26  | NC         | _   | _        | No connection                                                                            |  |

| 27  | NC         | _   | _        | No connection                                                                            |  |

| 28  | VDD        | _   | +3.3V    | Power supply                                                                             |  |

| 29  | REFCLKP+   | I   | PECL     | PECL reference clock input, true                                                         |  |

| 30  | REFCLKP-   | I   | PECL     | PECL reference clock input, complement                                                   |  |

| 31  | VDD        |     | +3.3V    | Power supply                                                                             |  |

| 32  | NC         | _   | _        | No connection                                                                            |  |

| 33  | RX50MCK    | О   | TTL      | Constant 51.84MHz ref clock output, derived from the CMU                                 |  |

| 34  | VSS        |     | GND      | Ground                                                                                   |  |

# Data Sheet VSC8113

| Pin | Signal    | I/O | Level  | Pin Description                                   |  |

|-----|-----------|-----|--------|---------------------------------------------------|--|

| 35  | RXOUT0    | О   | TTL    | Receive output data bit0                          |  |

| 36  | RXOUT1    | О   | TTL    | Receive output data bit1                          |  |

| 37  | VSS       | _   | GND    | O Ground                                          |  |

| 38  | RXOUT2    | О   | TTL    | Receive output data bit2                          |  |

| 39  | RXOUT3    | 0   | TTL    | Receive output data bit3                          |  |

| 40  | VSS       | _   | GND    | Ground                                            |  |

| 41  | RXOUT4    | 0   | TTL    | Receive output data bit4                          |  |

| 42  | RXOUT5    | О   | TTL    | Receive output data bit5                          |  |

| 43  | VSS       | _   | GND    | Ground                                            |  |

| 44  | RXOUT6    | О   | TTL    | Receive output data bit6                          |  |

| 45  | RXOUT7    | 0   | TTL    | Receive output data bit7                          |  |

| 46  | VSS       | _   | GND    | Ground                                            |  |

| 47  | RXLSCKOUT | О   | TTL    | Receive byte clock output                         |  |

| 48  | FP        | О   | TTL    | Frame detection pulse                             |  |

| 49  | VDD       | _   | +3.3V  | Power supply                                      |  |

| 50  | LOSOUT    | О   | TTL    | Loss of Signal alarm indicator                    |  |

| 51  | CRUREFCLK | I   | TTL    | Optional external CRU reference clock at77.76MHz  |  |

| 52  | LOSTTL    | I   | TTL    | Loss of Signal Control - TTL input                |  |

| 53  | LOSPECL   | I   | PECL   | Loss of Signal Control- single-ended PECL input   |  |

| 54  | VDD       | _   | +3.3V  | Power supply                                      |  |

| 55  | VSS       | _   | GND    | Ground                                            |  |

| 56  | REFCLK    | I   | TTL    | Reference clock input, refer to Table 12          |  |

| 57  | LOOPTIM1  | I   | TTL    | Enable loop timing operation, active HIGH         |  |

| 58  | VDD       | _   | +3.3V  | Power supply                                      |  |

| 59  | VSSA      | _   | GND    | Analog ground (CMU)                               |  |

| 60  | VSSA      | _   | GND    | Analog ground (CMU)                               |  |

| 61  | NC        | _   | _      | No connection                                     |  |

| 62  | VDDA      | _   | +3.3V  | Analog power supply (CMU)                         |  |

| 63  | CP1       | _   | Analog | CMU external capacitor (see Figure 6 and Table 1) |  |

| 64  | CN1       | _   | Analog | CMU external capacitor (see Figure 6 and Table 1) |  |

| 65  | CN2       | _   | Analog | CMU external capacitor (see Figure 6 and Table 1) |  |

| 66  | CP2       | _   | Analog | CMU external capacitor (see Figure 6 and Table 1) |  |

| 67  | VDDA      | _   | +3.3V  | Analog power supply (CMU)                         |  |

| 68  | VDDA      | _   | +3.3V  | Analog power supply (CRU)                         |  |

| 69  | VDDA      | _   | +3.3V  | Analog power supply (CRU)                         |  |

| 70  | VSSA      |     | GND    | Analog ground (CRU)                               |  |

## ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

| Pin | Signal     | I/O | Level | Pin Description                                                                         |

|-----|------------|-----|-------|-----------------------------------------------------------------------------------------|

| 71  | VSSA       | _   | GND   | Analog ground (CRU)                                                                     |

| 72  | VSS        | _   | GND   | Ground                                                                                  |

| 73  | NC         | _   | _     | No connection                                                                           |

| 74  | CRULOCKDET | О   | TTL   | Lock Detect indicator for clock recovery unit                                           |

| 75  | VSS        | _   | GND   | Ground                                                                                  |

| 76  | VDD        | _   | +3.3V | Power supply                                                                            |

| 77  | NC         | _   | _     | No connection                                                                           |

| 78  | NC         | _   | _     | No connection                                                                           |

| 79  | NC         | _   | _     | No connection                                                                           |

| 80  | CMULOCKDET | О   | TTL   | Lock Detect indicator for clock synthesis unit                                          |

| 81  | VDD        | _   | +3.3V | Power supply                                                                            |

| 82  | TXLSCKOUT  | О   | TTL   | Transmit byte clock out                                                                 |

| 83  | TXLSCKIN   | I   | TTL   | Transmit byte clock in                                                                  |

| 84  | VSS        | _   | GND   | Ground                                                                                  |

| 85  | TXIN7      | I   | TTL   | Transmit input data bit7                                                                |

| 86  | TXIN6      | I   | TTL   | Transmit input data bit6                                                                |

| 87  | VSS        | _   | GND   | Ground                                                                                  |

| 88  | TXIN5      | I   | TTL   | Transmit input data bit5                                                                |

| 89  | TXIN4      | I   | TTL   | Transmit input data bit4                                                                |

| 90  | NC         | _   | _     | No connection                                                                           |

| 91  | TXIN3      | I   | TTL   | Transmit input data bit3                                                                |

| 92  | TXIN2      | I   | TTL   | Transmit input data bit2                                                                |

| 93  | VSS        | _   | GND   | Ground                                                                                  |

| 94  | TXIN1      | I   | TTL   | Transmit input data bit1                                                                |

| 95  | TXIN0      | I   | TTL   | Transmit input data bit0                                                                |

| 96  | NC         | _   | _     | No connection                                                                           |

| 97  | STS12      | I   | TTL   | 155Mb/s or 622Mb/s mode select, refer to Table 12                                       |

| 98  | CRUREFSEL  | I   | TTL   | Selects between CMU's or CRU's REFCLK                                                   |

| 99  | VDD        | _   | +3.3V | Power supply                                                                            |

| 100 | EQULOOP    | I   | TTL   | Equipment loopback, loops low speed byte wide transmit input data to receive output bus |

# Data Sheet VSC8113

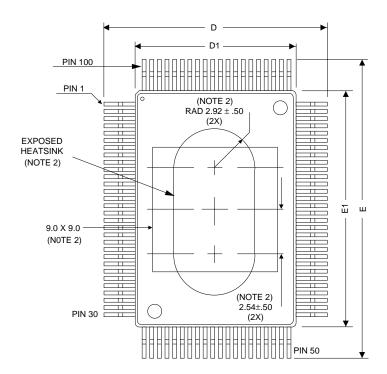

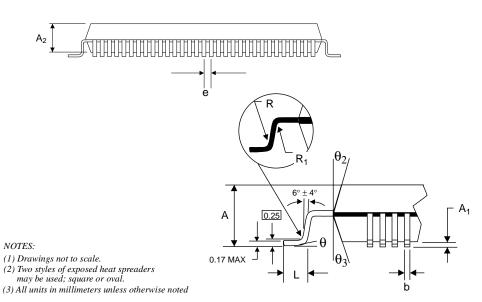

### Package Information

#### 100-Pin PQFP

#### **TOP VIEW**

| Key | mm    | Tolerance |

|-----|-------|-----------|

| A   | 3.40  | MAX       |

| A1  | 0.25  | MIN.      |

| A2  | 2.7   | ±.10      |

| D   | 17.20 | ±.40      |

| D1  | 14.00 | ±.10      |

| Е   | 23.20 | ±.40      |

| E1  | 20.00 | ±.10      |

| L   | 0.80  | ±.2       |

| e   | 0.65  | NOM       |

| b   | 0.30  | ±.10      |

| θ   | 0°-7° |           |

| R   | .30   | +0/1      |

| R1  | .2    | NOM       |

| θ2  | 15°   |           |

| θ3  | 15°   |           |

Package #: 101-202-4 Issue #: 1

### ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

The VSC8113 is manufactured in a 100-pin PQFP package which will have one of two styles of exposed heat spreaders; square or oval. The critical dimensions in the drawing represent the superset of dimensions for both packages. The significant difference between the two packages is in the shape and size of the heatspreader which needs to be considered when attaching a heatsink.

### Package Thermal Characteristics

The VSC8113 is packaged in a thermally-enhanced 100-pin PQFP with an embedded heat sink. The heat sink surface configurations are shown in the package drawings. With natural convection, the case-to-air thermal resistance is estimated to be 27.5°C/W. The air flow versus thermal resistance relationship is shown in Table 18. Junction-to-case thermal resistance is 1.2 °C/W

**Table 18: Thermal Resistance with Airflow**

| Airflow (LFPM) | $\theta_{CA}$ (°C/W) |

|----------------|----------------------|

| 0              | 27.5                 |

| 100            | 23.1                 |

| 200            | 19.8                 |

| 400            | 17.6                 |

| 600            | 16                   |

### **Ordering Information**

The order number for this product is formed by a combination of the device number and package type.

Package

QB: 100-Pin PQFP

Commerical Temperature: 0°C ambient to +70°C case

QB1: 100-Pin PQFP

Extended Temperature: 0°C to +85°C ambient (equivalent

to 0°C ambient to +115°C case)

QB2: 100-Pin PQFP

Industrial Temperature: -40°C ambient to +85°C case

#### **Notice**

Vitesse Semiconductor Corporation ("Vitesse") provides this document for informational purposes only. This document contains pre-production information about Vitesse products in their concept, development and/or testing phase. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. Nothing contained in this document shall be construed as extending any warranty or promise, express or implied, that any Vitesse product will be available as described or will be suitable for or will accomplish any particular task.

#### Warning

Vitesse Semiconductor Corporation's products are not intended for use in life support appliances, devices or systems. Use of a Vitesse product in such applications without written consent is prohibited.

Data Sheet VSC8113

### **Application Notes**

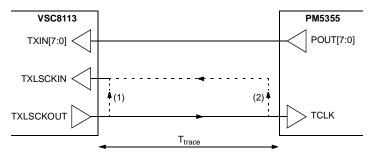

#### Interconnecting the Byte Clocks (TXLSCKOUT and TXLSCKIN)

The byte clock (TXLSCKOUT and TXLSCKIN) on the VSC8113 has been brought off-chip to allow as much flexibility in system-level clocking schemes as possible. Since the byte clock (TXLSCKOUT) clocks both the VSC8113 and the UNI devices, it is important to pay close attention to the routing of this signal. The UNI device in general is a CMOS part which can have very wide spreads in timing (1-11ns clock in to parallel data out for the PM5355), which utilizes most of the 12.86ns period (at 78MHz), leaving little for the trace delays and set-up times required to interconnect the 2 devices.

The VSC8113 and the UNI device should be placed as close to each other as possible to provide maximum setup and hold time margin at the inputs of the VSC8113. Figure 13 suggests two different ways of routing the TXLSCKOUT-to-TXLSCKIN clock trace when used in a 622MHz mode. Whichever method is used, the transmission line trace impedance should be no lower than  $75\Omega$ .

Figure 13: Interconnecting the Byte Clocks

Option (1): TXLSCKOUT and TXLSCKIN are tied together at the pins of the VSC8113. This provides a setup and hold time margin for the TXIN input of:

$$\begin{split} T_{su,margin} &= T_{clk} - T_{TCLK\text{-}POUT,max}(PM5355) - T_{su,min}(VSC8113) - 2xT_{trace} = 0.86ns - 2xT_{trace} \\ T_{hold,margin} &= T_{TCLK\text{-}POUT,min}(PM5355) - T_{hold,min}(VSC8113) + 2xT_{trace} = 2xT_{trace} \end{split}$$

Option (2): TXLSCKOUT is daisy chained to the UNI device and then routed back to the VSC8113 along with the byte data. This interface provides a setup and hold time margin for the TXIN input of:

$$\begin{split} T_{su,margin} &= T_{clk} \text{ - } T_{TCLK\text{-}POUT,max}(PM5355) \text{ - } T_{su,min}(VSC8113) = 0.86ns \\ T_{hold,margin} &= T_{TCLK\text{-}POUT,min}(PM5355) \text{ - } T_{hold,min}(VSC8113) = 0ns \end{split}$$

Option (2) does not provide any hold time margin, while option (1) requires the one-way trace delay ( $T_{trace}$ ) to be less than 0.43ns (~3 inches).

The general recommendation is to apply option (1) and place the VSC8113 and PM5355 as close to each other as possible. If the one-way trace delay cannot be kept less than 0.43ns with a 50pf load, daisy-chaining (option 2) should be applied; close attention must be paid to signal routing in this case because of the lack of hold time margin.

NOTE: The 11ns max Tpd on the PM5355 assumes a 50pF load at 60ps/pF, therefore 3ns of the max delay is due to loading. The VSC8113 input (TXLSCKIN) plus package is about 6pF. Assuming about 1pF per inch of 75 $\Omega$  trace on FR4 plus the VSC8113 6pF load, the user would, in most cases, choose option (1).

### ATM/SONET/SDH 622/155Mb/s Transceiver MUX/DEMUX with Integrated Clock Generation and Clock Recovery

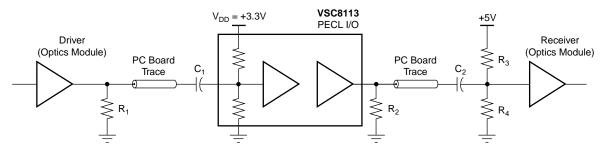

#### DC-Coupling and Terminating High-speed PECL I/Os

The high-speed signals on the VSC8113 (RXDATAIN, RXCLKIN, TXDATAOUT, TXCLKOUT, REFCLKP, LOSPECL) use 3.3/5V programmable PECL I/Os which can be direct coupled to either +3.3V PECL or +5V PECL signals from the optics. These PECL levels are essentially ECL levels shifted positive by 3.3V or 5V. These PECL I/Os are referenced to the  $V_{DDP}$  supply (VDDP) and are terminated to ground. To program these I/Os for either 3.3V or 5V interface, the three  $V_{DDP}$  pins (pin 9, 15, 21) are required to connect to 3.3V or 5V supplies accordingly.

#### AC-Coupling and Terminating High-speed PECL I/Os

If the optics modules provide ECL-level interface, the high-speed signals can be AC-coupled to the VSC8113 as well. The PECL receiver inputs of the VSC8113 are internally biased at  $V_{DD}/2$ . Therefore, AC-coupling to the VSC8113 inputs is accomplished by providing the pull-down resistor for the open-source PECL output and an AC-coupling capacitor used to eliminate the DC component of the output signal. This capacitor allows the PECL receivers of the VSC8113 to self-bias via its internal resistor divider network (see Figure 14). The PECL output drivers are capable of sourcing current but not sinking it. To establish a LOW output level, a pull-down resistor, traditionally connected to  $V_{DD}$  - 2.0V, is needed when the output FET is turned off. Since  $V_{DD}$  - 2.0V is usually not present in the system, the resistor could be terminated to ground for convenience. The VSC8113 output drivers should be either AC-coupled to the 5.0V PECL inputs of the optics module, or translated (DC-level shift). Appropriate biasing techniques for setting the DC-level of these inputs should be employed.

The DC biasing and  $50\Omega$  termination requirements can easily be integrated together using a Thevenin equivalent circuit as shown in Figure 14. Figure 14 shows the appropriate termination values when interfacing 3.3V PECL to 5.0V PECL. This network provides the equivalent  $50\Omega$  termination for the high-speed I/Os and also provides the required DC biasing for the receivers of the optics module. Table 18 shows recommended values for each of the components.

Figure 14: AC-Coupled High-Speed I/O

NOTE: Only one state of a differential signal is shown.

**Table 19: AC-Coupling Component Values**

| Component            | Value                 | Tolerance |

|----------------------|-----------------------|-----------|

| R <sub>1</sub>       | 270Ω                  | 5%        |

| R <sub>2</sub>       | 75Ω                   | 5%        |

| R <sub>3</sub>       | $68\Omega$            | 1%        |

| R <sub>4</sub>       | 190Ω                  | 1%        |

| $C_1, C_2, C_3, C_4$ | 0.01μF High Frequency | _         |

Data Sheet VSC8113

#### **TTL Input Structure**

The TTL inputs of the VSC8113 are 3.3V TTL which can accept 5.0V TTL levels within a given set of tolerances (see Table 5). The input structure, shown in Figure 15, uses a current limiter to avoid overdriving the input FETs.

#### **Layout of the High-Speed Signals**

The routing of the high-speed signals should be done using good high-speed design practices. This would include using controlled impedance lines and keeping the distance between components to an absolute minimum. In addition, stubs should be kept at a minimum as well as any routing discontinuities. This will help minimize reflections and ringing on the high-speed lines and insure the maximum eye opening. In addition, the output pull-down resistor should be placed as close to the VSC8113 pin as possible while the AC-coupling capacitor and the biasing resistors should be placed as close as possible to the optics input pin. The same is true on the receive circuit side. Using small outline components and minimum pad sizes also helps in reducing discontinuities.

#### **Ground Planes**

The ground plane for the components used in the high-speed interface should be continuous and not sectioned in an attempt to provide isolation to various components. Sectioning of the ground planes tends to interfere with the ground return currents on the signal lines. In addition, the smaller the ground planes, the less effective they are in reducing ground bounce noise and the more difficult to decouple. Sectioning of the positive supplies can provide some isolation benefits.

$V_{DDP} +3.3/+5V$  $V_{DD}$ +3.3V+3.3V INPUT Current **INPUT** Limit R **INPUT** All Resistors  $3.3k\Omega$ GND **GND** High-Speed Differential Input **REFCLK** and TTL Inputs (RXDATAIN+/RXDATAIN-) (RXCLKIN+/RXCLKIN-)

Figure 15: Input Structures

(REFCLKP+/REFCLKP-)