Quad Transceiver for Gigabit Ethernet and Fibre Channel

### **Features**

G52348-0, Rev 2.2

10/10/00

- Four Complete Transceiver Functions in One IC

- Full Gigabit Ethernet (IEEE 802.3z) Compliance

- Pin-Compatible With Agilent's HDMP-1686A

- 5V Tolerant TTL Inputs

- Utilizes Reference Clock to Latch Tx Data

- Receiver Squelch Circuit

- Common Local Loopback Control

- Single Comma Detect Enable

- Cable Equalization in Receivers

- Automatic Lock-to-Reference

- TAG Access Port

- 2kV ESD Protection on All Pins

- 3.3V Power Supply, 2.67 W Max Dissipation

Page 1

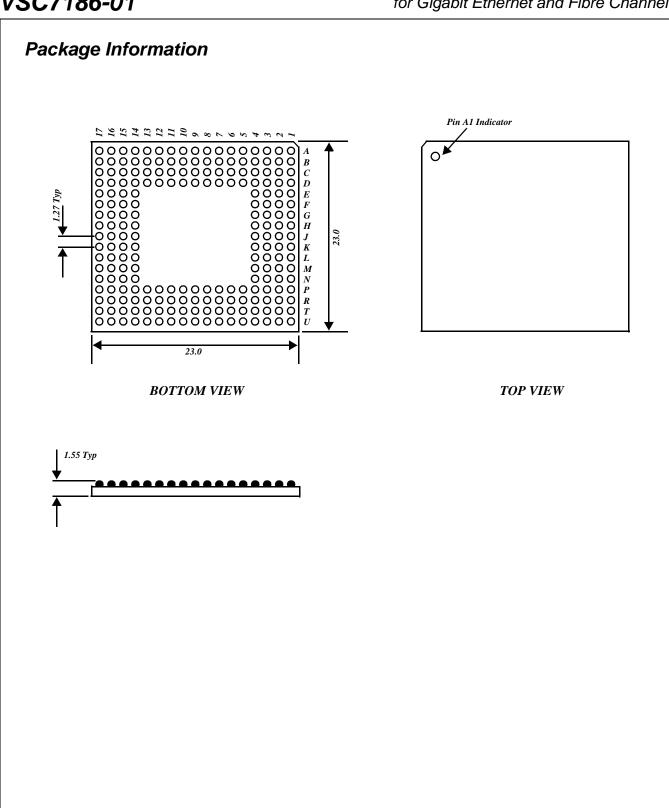

• 208-Pin, 23mm BGA Packaging

### General Description

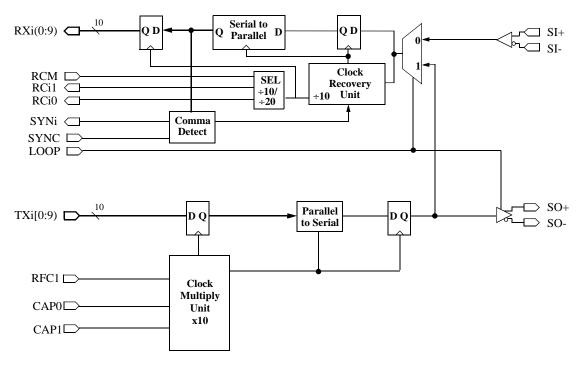

The VSC7186-01 is a quad Gigabit Ethernet transceiver IC. Each of the four transmitters has a 10-bit wide bus, running at 125MHz, which accepts 8B/10B encoded transmit characters and serializes the data onto high-speed differential outputs at rates between 1.05Gb/s and 1.36Gb/s. The transmit data must be synchronous to the reference clock. Each receiver samples serial receive data, recovers the clock and data, deserializes it into 10-bit receive characters, outputs a recovered clock and detects "Comma" characters. The VSC7186-01 contains on-chip (Phase-Lock Loop) PLL circuitry for synthesis of the baud-rate transmit clock and extraction of the clocks from the received serial streams. The VSC7186-01 also includes a receiver squelch circuit to control the parallel data bus in the absence of serial input.

### VSC7186-01 Block Diagram (1 of 4 Channels)

### Advance Product Information VSC7186-01

### Functional Description

#### **Notation**

In this document, each of the four channels are identified as Channel 0, 1, 2 or 3. When discussing a signal on any specific channel, the signal will have the channel number embedded in the name, for example, "T3[0:9]." When referring to the common behavior of a signal which is used on each of the four channels, the notation "i" is used. Differential signals, such as SOi+ and SOi-, may be referred to as a single signal (e. g., SOi) by dropping reference to the "+" and "-."

### **Clock Synthesizer**

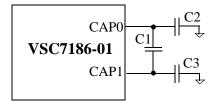

The VSC7186-01 Clock Multiplier Unit (CMU) multiplies the reference frequency provided on the RFC1 input by 10 to achieve a baud rate clock between 1.05GHz and 1.36GHz. The RFC1 input is TTL. The on-chip PLL uses a single external 0.1µF capacitor, connected between CAP0 and CAP1, to control the Loop Filter. This capacitor should be a multilayer ceramic dielectric, or better, with at least a 5V working voltage rating and a good temperature coefficient (NPO is preferred but X7R may be acceptable). These capacitors are used to minimize the impact of common-mode noise on the CMU, especially power supply noise. Higher value capacitors provide better robustness in systems. NPO is preferred because if an X7R capacitor is used, the power supply noise sensitivity will vary with temperature.

For best noise immunity, the designer may use a three capacitor circuit with one differential capacitor between CAP0 and CAP1, C1, a capacitor from CAP0 to ground, C2, and a capacitor from CAP1 to ground, C3. Larger values are better but  $0.1\mu F$  is adequate. However, if a three capacitor circuit cannot be used, a single differential capacitor, C1, is adequate. These components should be isolated from noisy traces.

Figure 1: Loop Filter Capacitors (Best Circuit)

C1=C2=C3=>0.1µF MultiLayer Ceramic Surface Mount NPO (preferred) or X7R 5V Working Voltage Rating

#### Serializer

The VSC7186-01 accepts TTL input data as four parallel 10-bit characters on the Ti[0:9] buses which are latched into the input registers on the rising edge of RFC1. The 10-bit parallel transmission character will be serialized and transmitted on the SOi+/- PECL differential outputs at the baud rate with bit Ti0 (bit A) transmitted first. User data should be encoded using 8B/10B or an equivalent code. The mapping to 10B encoded bit nomenclature and transmission order is shown in Table 1, along with the recognized comma pattern.

Table 1: Transmission Order and Mapping of a 10b Character

| Data Bit         | T9 | T8 | <i>T7</i> | T6 | T5 | T4 | <i>T3</i> | T2 | T1 | T0 |

|------------------|----|----|-----------|----|----|----|-----------|----|----|----|

| 10B Bit Position | j  | h  | g         | f  | i  | e  | d         | С  | b  | a  |

| Comma Character  | X  | X  | X         | 1  | 1  | 1  | 1         | 1  | 0  | 0  |

Quad Transceiver for Gigabit Ethernet and Fibre Channel

#### **Clock Recovery**

The VSC7186-01 accepts differential high-speed serial input from the selected source (either the PECL SIi+/- pins or the internal SOi+/- data), extracts the clock and retimes the data. Equalizers are included in the receiver to open the data eye and compensate for Intersymbol Interference (ISI) which may be present in the incoming data. The serial bit stream should be encoded so as to provide DC balance and limited run length by an 8B/10B encoding scheme. The digital Clock Recovery Unit (CRU) is completely monolithic and requires no external components. For proper operation, the baud rate of the data stream to be recovered should be within  $\pm 200$ ppm of ten times the REF frequency. For example, Gigabit Ethernet systems use 125MHz oscillators with a +/-100ppm accuracy resulting in +/-200ppm between VSC7186-01 pairs.

#### Deserializer

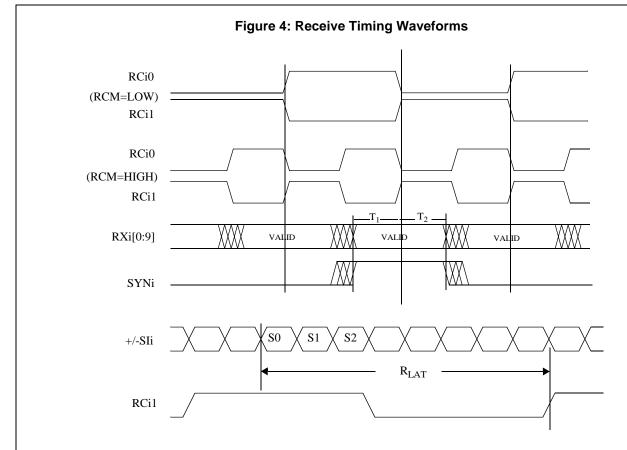

The recovered serial bit stream is converted into a 10-bit parallel output character. The VSC7186-01 provides complementary TTL recovered clocks, RCi0 and RCi1, at 1/20th of the serial baud rate if RCM=LOW, or a single clock at 1/10th the serial baud rate (on RCi1 only) if RCM=HIGH. The clocks are generated by dividing down the high-speed recovered clock which is phase-locked to the serial data. The serial data is retimed, deserialized and output on Ri[0:9].

If serial input data is not present, or does not meet the required baud rate, the VSC7186-01 will continue to produce a recovered clock so that downstream logic may continue to function. The RCi0/RCi1 output frequency under these circumstances will differ from its expected frequency by no more than  $\pm 1\%$ .

#### **Word Alignment**

The VSC7186-01 provides 7-bit comma character recognition and data word alignment. Word synchronization is enabled on all channels by asserting SYNC HIGH. When synchronization is enabled, the receiver examines the recovered serial data for the presence of the "Comma" pattern. This pattern is "0011111XXX", where the leading zero corresponds to the first bit received. The comma sequence is not contained in any normal 8B/10B coded data character or pair of adjacent characters. It occurs only within special characters, known as K28.1, K28.5 and K28.7, which are defined for synchronization purposes. Improper comma alignment is defined as any of the following conditions:

- 1) The comma is not aligned within the 10-bit transmission character such that Ri[0...6) = "0011111."

- 2) The comma straddles the boundary between two 10-bit transmission characters.

- 3) The comma is properly aligned but occurs in the received character presented during the rising edge of RCi0 rather than RCi1.

When an improperly aligned comma is encountered, the recovered clock is stretched, never slivered, so that the comma character and recovered clocks are aligned properly to Ri[0:9]. This results in proper character and word alignment. When the parallel data alignment changes in response to a improperly aligned comma pattern, data which would have been presented on the parallel output port prior to the comma character, and possibly the comma character itself, may be lost. Possible loss of the comma character is data dependent, according to the relative change in alignment. Data subsequent to the comma character will always be output correctly and properly aligned.

## Advance Product Information VSC7186-01

On encountering a comma character, SYNi is driven HIGH. The SYNi pulse is presented simultaneously with the comma character and has a duration equal to the data. The SYNi signal is timed such that it can be captured by the adjoining protocol logic on the rising edge of RCi1. Functional waveforms for synchronization are given in Figure 2. The first K28.5 shows the case where the comma is detected, but it is misaligned so a change in the output data alignment is required. Note that up to three characters prior to the comma character may be corrupted by the realignment process. The second K28.5 shows the case when a comma is detected and no phase adjustment is necessary. It illustrates the position of the SYNi pulse in relation to the comma character on Ri[0:9].

RCi0 (RCM LOW) RCi1 RCi0 ([RCM HIGH) RCi1 **SYNi** RXi[0:9] Data Corrupt Corrupt Corrupt Data1 Data2 K28.5 Data3 K28.5 Misaligned Comma: Stretched Aligned Comma

Figure 2: Misaligned and Aligned K28.5 Characters

#### **Loopback Operation**

Loopback operation is controlled by the LOOP line. When this line is HIGH, the outgoing high-speed serial data on each of the four channels is internally looped back into that channel's high-speed serial receiver section. This provides for in-circuit testing capability independent of the transmission medium.

### **JTAG Access Port**

A JTAG access port is provided to assist in board-level testing. Through this port most pins can be accessed or controlled and all TTL outputs can be tri-stated. A full description of the JTAG functions on this device is available in "VSC7186-01 JTAG Access Port Functionality." Circuits designed exclusively for the HDMP-1686A will automatically disable the JTAG port. Refer to Table 5 for proper connections for either HDMP-1686A emulation or for JTAG functionality (in parentheses).

Quad Transceiver for Gigabit Ethernet and Fibre Channel

### **AC Characteristics**

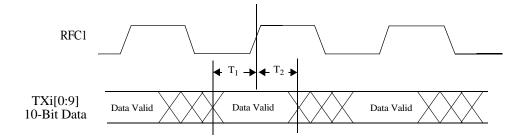

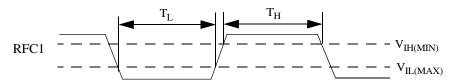

**Figure 3: Transmit Timing Waveforms**

**Table 2: Transmitter AC Characteristics**

| Parameter             | Description                                                          | Min          | Тур        | Max             | Units | Conditions                                                                 |

|-----------------------|----------------------------------------------------------------------|--------------|------------|-----------------|-------|----------------------------------------------------------------------------|

| T <sub>1</sub>        | Ti[0:9] setup time to the rising edge of RFC1                        | 1.5          |            |                 | ns    | Measured between the valid data level of Ti[0:9] to the 1.4V point of RFC1 |

| $T_2$                 | Ti[0:9] hold time after the rising edge of RFC1                      | 1.0          |            |                 | ns    |                                                                            |

| $T_{SDR}$ , $T_{SDF}$ | Ti+/Ti- rise and fall time                                           |              |            | 300             | ps    | 20% to 80%, 75 $\Omega$ load to $V_{DD}/2$ , tested on a sample basis      |

| $T_{LAT}$             | Latency from rising edge of<br>RFC1 to Ti0 appearing on SO<br>bit 0i | 7bc + 0.66ns |            | 7bc +<br>1.46ns |       | bc = bit clocks<br>ns = nanoseconds                                        |

|                       |                                                                      | Transmi      | tter Outpu | t Jitter        |       |                                                                            |

| RJ                    | Random jitter (rms)                                                  |              | 5          | 8               | ps    | Measured at SO+/-, 1 sigma<br>deviation of 50% crossing point              |

| DJ                    | Serial data output deterministic jitter (pk-pk)                      | _            | 35         | 80              | ps    | IEEE 802.3Z Clause 38.68, tested on a sample basis                         |

# Advance Product Information VSC7186-01

**Table 3: Receive AC Characteristics**

| Parameters       | Description                                                       | Min                          | Тур | Max                          | Units        | Conditions                                                    |

|------------------|-------------------------------------------------------------------|------------------------------|-----|------------------------------|--------------|---------------------------------------------------------------|

| T <sub>1</sub>   | TTL outputs valid prior to RCi1/RCi0 rise                         | 3.0                          |     | _                            | ns           | At 1.25Gb/s                                                   |

| T <sub>2</sub>   | TTL outputs valid after RCi1 or RCi0 rise                         | 2.0                          |     | _                            | ns           | At 1.25Gb/s                                                   |

| Т3               | Delay between rising edge of RCi1 to rising edge of RCi0          | 10 x T <sub>Ri</sub><br>-500 |     | 10 x T <sub>Ri</sub><br>+500 | ps           | T <sub>Ri</sub> is the bit period of the incoming data on Ri. |

| T <sub>4</sub>   | Period of RCi1 and RCi0                                           | 1.98 x<br>T <sub>REF</sub>   |     | 2.02 x<br>T <sub>REF</sub>   | ps           | Whether or not locked to serial data.                         |

| $T_R, T_F$       | TTL output rise and fall time                                     | _                            |     | 2.4                          | ns           | Between $V_{IL(MAX)}$ and $V_{IH(MIN)}$ , into 10pF load.     |

| $T_{LOCK}$       | Data acquisition lock time <sup>(1)</sup>                         | _                            |     | 1400                         | bit<br>times | 8B/10B IDLE pattern.<br>Tested on a sample basis.             |

| R <sub>LAT</sub> | Latency from bit 0 of RXi0 appearing on SI to rising edge of RCi1 | 12bc +<br>2.77ns             |     | 13bc +<br>7.28ns             |              | bc = bit clocks<br>ns = nanoseconds                           |

NOTE: (1) Probability of recovery for data acquisition is 95% per Section 5.3 of FC-PH rev. 4.3.

Quad Transceiver for Gigabit Ethernet and Fibre Channel

### Figure 5: RFC1 Waveform

**Table 4: Reference Clock Requirements**

| Parameters            | Description             | Min  | Тур | Max | Units | Conditions                                                                                     |

|-----------------------|-------------------------|------|-----|-----|-------|------------------------------------------------------------------------------------------------|

| FR                    | Frequency range         | 105  |     | 136 | MHz   | Range over which both transmit<br>and receive reference clocks on<br>any link may be centered. |

| FO                    | Frequency offset        | -200 |     | 200 | ppm   | Maximum frequency offset<br>between transmit and receive<br>reference clocks on one link.      |

| DC                    | RFC1 duty cycle         | 35   |     | 65  | %     | Measured at 1.4V                                                                               |

| $T_{RCR}$ , $T_{RCF}$ | RFC1 rise and fall time | _    |     | 1.5 | ns    | Between V <sub>IL(MAX)</sub> and V <sub>IH(MIN)</sub>                                          |

# Advance Product Information VSC7186-01

### **DC Characteristics**

| Parameters                     | Description                                        | Min  | Тур | Max  | Units | Conditions                                                      |  |  |  |  |  |  |

|--------------------------------|----------------------------------------------------|------|-----|------|-------|-----------------------------------------------------------------|--|--|--|--|--|--|

| TTL Outputs                    |                                                    |      |     |      |       |                                                                 |  |  |  |  |  |  |

| V <sub>OH</sub>                | TTL output HIGH voltage                            | 2.4  | _   | _    | V     | I <sub>OH</sub> = -1.0mA                                        |  |  |  |  |  |  |

| V <sub>OL</sub>                | TTL output LOW voltage                             | _    | _   | 0.5  | V     | $I_{OL} = +1.0 \text{mA}$                                       |  |  |  |  |  |  |

| $I_{OZ}$                       | TTL output Leakage current                         | _    | _   | 50   | μΑ    | When set to high-impedance state through JTAG.                  |  |  |  |  |  |  |

| TTL Inputs                     |                                                    |      | I.  | •    | •     |                                                                 |  |  |  |  |  |  |

| V <sub>IH</sub>                | TTL input HIGH voltage                             | 2.0  |     | 5.5  | V     | 5V tolerant inputs                                              |  |  |  |  |  |  |

| $V_{\mathrm{IL}}$              | TTL input LOW voltage                              | 0    | _   | 0.8  | V     |                                                                 |  |  |  |  |  |  |

| $I_{\mathrm{IH}}$              | TTL input HIGH current                             | _    | 50  | 500  | μΑ    | V <sub>IN</sub> =2.4V                                           |  |  |  |  |  |  |

| $I_{ m IL}$                    | TTL input LOW current                              | _    | _   | -500 | μΑ    | V <sub>IN</sub> =0.5V                                           |  |  |  |  |  |  |

| High-Speed Ou                  | itputs                                             |      |     |      |       |                                                                 |  |  |  |  |  |  |

| $\Delta V_{OUT75}^{(1)}$       | TX output differential peak-to-peak voltage swing  | 1200 |     | 2200 | mVp-p | $75\Omega$ to $V_{DD}$ – 2.0V $(Ti+)$ - $(Ti-)$                 |  |  |  |  |  |  |

| $\Delta V_{OUT50}^{(1)}$       | Ti output differential peak-to-peak voltage swing  | 1000 | _   | 2200 | mVp-p | $50\Omega$ to $V_{DD}$ – 2.0V $(Ti+)$ - $(Ti-)$                 |  |  |  |  |  |  |

| High-Speed In                  | puts                                               |      | I.  | •    | •     |                                                                 |  |  |  |  |  |  |

| $\Delta V_{\mathrm{IN}}^{(1)}$ | PECL differential peak-to-peak input voltage swing | 200  |     | 2600 | mV    | Ri+ - Ri-                                                       |  |  |  |  |  |  |

| Miscellaneous                  |                                                    |      |     |      |       |                                                                 |  |  |  |  |  |  |

| $V_{\mathrm{DD}}$              | Power supply voltage                               | 3.14 | _   | 3.47 | V     | 3.3V <u>+</u> 5%                                                |  |  |  |  |  |  |

| $P_{D}$                        | Power dissipation                                  | _    | 2.2 | 2.67 | W     | Maximum at 3.47V, outputs open,                                 |  |  |  |  |  |  |

| $I_{DD}$                       | Supply current (all supplies)                      | _    | _   | 770  | mA    | 25°C, 136MHz clk, PRBS 2 <sup>7</sup> -1 parallel input pattern |  |  |  |  |  |  |

| $I_{\mathrm{DDA}}$             | Supply current on V <sub>DDA</sub>                 | _    | 100 | _    | mA    |                                                                 |  |  |  |  |  |  |

NOTE: (1) Refer to Application Note, AN-37, for differential measurement techniques.

Quad Transceiver for Gigabit Ethernet and Fibre Channel

| Absolute Maximum Ratings (1)                                                                                                                                                              |                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Power Supply Voltage (V <sub>DD</sub> )                                                                                                                                                   | 0.5V to +4V                   |

| DC Input Voltage (PECL inputs)                                                                                                                                                            | 0.5V to V <sub>DD</sub> +0.5V |

| DC Input Voltage (TTL inputs)                                                                                                                                                             | 0.5V to 5.5V                  |

| DC Output Voltage (TTL outputs)                                                                                                                                                           | 0.5V to $V_{DD} + 0.5V$       |

| Output Current (TTL outputs)                                                                                                                                                              | +/-50mA                       |

| Output Current (PECL outputs)                                                                                                                                                             | +/-50mA                       |

| Case Temperature Under Bias                                                                                                                                                               |                               |

| Storage Temperature                                                                                                                                                                       | 65°C to +150°C                |

| Maximum Input ESD (human body model)                                                                                                                                                      | 2000V                         |

| NOTE: (1) CAUTION: Stresses listed under "Absolute Maximum Ratings" recausing permanent damage. Functionality at or above the values list extended periods may affect device reliability. | 2 11                          |

| Recommended Operating Conditions                                                                                                                                                          |                               |

| Power Supply Voltage (V <sub>DD</sub> )                                                                                                                                                   | +3.3V <u>+</u> 5%             |

| Operating Temperature Range                                                                                                                                                               |                               |

# Advance Product Information VSC7186-01

#### Table 5: Pin Table

| 17           | GNDT | RC31 | RX30 | RX34        | RX36 | GND  | VCCT | TX23 | TX27          | NC          | TX30 | TX34 | TX38  | NC          | SYNC           | NC<br>(TCK) | GND          |

|--------------|------|------|------|-------------|------|------|------|------|---------------|-------------|------|------|-------|-------------|----------------|-------------|--------------|

| 16           | VCCT | RC30 | GNDT | RX33        | RX35 | RX39 | TX20 | TX24 | TX28          | ACC         | TX31 | TX35 | TX39  | NC          | VCCTR          | GNDTR       | GND          |

| 15           | GNDT | SYN3 | VCCT | RX32        | GNDT | RX38 | TX21 | TX25 | TX29          | GND         | TX32 | TX36 | VCC   | NC<br>(TDI) | GND<br>(TRSTN) | GND         | GND          |

| 14           | RX28 | RX29 | NCC  | RX31        | VCCT | RX37 | TX22 | TX26 | NCC           | GND         | TX33 | TX37 | LOOP  | GND         | NCC            | VCC         | SI3+         |

| 13           | VCCT | RX25 | RX26 | RX27        |      |      |      |      |               |             |      |      |       | SO3+        | SO3-           | VCCP3       | SI3-         |

| 12           | RX21 | RX22 | RX23 | RX24        |      |      |      |      |               |             |      |      |       | GND         | GND            | GND         | GND          |

| 11           | GNDT | RX20 | VCCT | GNDT        |      |      |      |      |               |             |      |      |       | SO2+        | SO2-           | VCCP2       | SI2+         |

| 10           | NCC  | SYN2 | RC20 | RC21        |      |      |      |      | ATED          |             |      |      |       | GND         | GND            | GND         | SI2-         |

| 6            | VCCT | GND  | NC   | NC<br>(TMS) |      |      |      |      | NOT POPULATED |             |      |      |       | CAP0        | CAPI           | VCCA        | GND          |

| <b>&amp;</b> | RX16 | RX17 | RX18 | RX19        |      |      |      |      | NOT P         |             |      |      |       | GND         | GNDA           | GND         | GND          |

| 7            | RX14 | VCCT | GNDT | RX15        |      |      |      |      |               |             | SO1- | SOI+ | VCCPI | SI1+        |                |             |              |

| 9            | RX10 | RX11 | RX12 | RX13        |      |      |      |      |               |             |      |      |       | GND         | GND            | GND         | SII-         |

| S            | RC10 | RC11 | VCCT | GND         |      |      |      |      |               |             |      |      |       | SO0-        | **SOO+         | VCCP0       | VCC          |

| 4            | SYN1 | GNDT | VCCT | GNDT        | RX03 | GNDT | VCC  | TX17 | TX13          | GND         | VCC  | TX07 | TX03  | GND         | vcc            | vcc         | SIO+         |

| 3            | GNDT | RX09 | RX06 | VCCT        | RX02 | VCCT | GND  | TX16 | TX12          | GND         | GND  | TX06 | TX02  | NC          | GND            | ACC         | SIO-         |

| 2            | ACC  | RX08 | RX05 | RX01        | RC01 | SYN0 | 61XT | TX15 | TXII          | NC<br>(TDO) | 60XL | TX05 | TX01  | NC          | NC             | GND         | GND          |

| 1            | GNDT | RX07 | RX04 | RX00        | RC00 | NC   | TX18 | TX14 | TX10          | NC          | TX08 | TX04 | 1X00  | NC          | RFC1           | RCM0        | GND          |

|              | A    | В    | ၁    | D           | Ħ    | 1    | G    | Н    | ſ             | K           | T    | M    | Z     | Ь           | R              | T           | $\mathbf{u}$ |

Quad Transceiver for Gigabit Ethernet and Fibre Channel

### **Table 6: Pin Description**

| Pin                                                   | Name                                                                             | Description                                                                                                                                                                                                        |

|-------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N1, N2, N3<br>N4, M1, M2, M3,<br>M4, L1, L2           | TX0-0, TX0-1,<br>TX0-2 TX0-3,<br>TX0-4, TX0-5,<br>TX0-6, TX0-7,<br>TX0-8 TX0-9   | INPUT - TTL: 10-Bit Transmit Bus for Channel 0. Parallel data on this bus is latched on the rising edge of REF. TX0-0 is transmitted first.                                                                        |

| J1, J2, J3<br>J4, H1, H2<br>H3, H4, G1, G2            | TX1-0, TX1-1,<br>TX1-2 TX1-3,<br>TX1-4, TX1-5,<br>TX1-6, TX1-7,<br>TX1-8, TX1-9  | INPUT - TTL: 10-Bit Transmit Bus for Channel 1. Parallel data on this bus is latched on the rising edge of REF. TX1-0 is transmitted first.                                                                        |

| G16, G15, G14 H17,<br>H16, H15<br>H14, J17, J16 J15   | TX2-0, TX2-1,<br>TX2-2 TX2-3,<br>TX2-4, TX2-5,<br>TX2-6, TX2-7,<br>TX2-8, TX2-9  | INPUT - TTL: 10-Bit Transmit Bus for Channel 2. Parallel data on this bus is latched on the rising edge of REF. TX2-0 is transmitted first.                                                                        |

| L17, L16, L15 L14,<br>M17, M16, M15,<br>M14, N17, N16 | TX3-0, TX3-1,<br>TX3-2, TX3-3,<br>TX3-4, TX3-5,<br>TX3-6, TX3-7,<br>TX3-8, TX3-9 | INPUT - TTL: 10-Bit Transmit Bus for Channel 3. Parallel data on this bus is latched on the rising edge of REF. TX3-0 is transmitted first.                                                                        |

| R1                                                    | RFC1                                                                             | INPUT - TTL: TTL Reference Clock. This rising edge of RFC1 provides the reference clock, at 1/10th of the baud rate to the Clock Multiplying PLL. The rising edge of RFC1 will latch TXi[0:9] on all four channels |

| R5, P5<br>R7, P7<br>P11, R11<br>P13, R13              | SO0+, SO0-<br>SO1+, SO1-<br>SO2+, SO2-<br>SO3+, SO3-                             | OUTPUT - Differential PECL (AC-coupling recommended): These pins output the serialized transmit data for Channels 0-3 when LOOP is LOW. When LOOP is HIGH, SOi+ is HIGH and SOi- is LOW.                           |

| D1, D2, E3<br>E4, C1, C2<br>C3, B1, B2, B3            | RX0-0, RX0-1,<br>RX0-2, RX0-3,<br>RX0-4, RX0-5,<br>RX0-6, RX0-7,<br>RX0-8, RX0-9 | OUTPUT - TTL: 10-Bit Receive Bus for Channel 0. Parallel data on this bus is synchronous to RC0-0 and RC0-1. RX0-0 is the first bit received.                                                                      |

| A6, B6, C6<br>D6, A7, D7<br>A8, B8, C8, D8            | RX1-0, RX1-1,<br>RX1-2, RX1-3,<br>RX1-4, RX1-5,<br>RX1-6, RX1-7,<br>RX1-8, RX1-9 | OUTPUT - TTL: 10-Bit Receive Bus for Channel 1. Parallel data on this bus is synchronous to RC1-0 and RC1-1. RX1-0 is the first bit received.                                                                      |

| B11, A12, B12 C12,<br>D12, B13<br>C13, D13, A14 B14   | RX2-0, RX2-1,<br>RX2-2, RX2-3,<br>RX2-4, RX2-5,<br>RX2-6, RX2-7,<br>RX2-8, RX2-9 | OUTPUT - TTL: 10-Bit Receive Bus for Channel 2. Parallel data on this bus is synchronous to RC2-0 and RC2-1. RX2-0 is the first bit received.                                                                      |

# Advance Product Information VSC7186-01

| Pin                                                  | Name                                                                             | Description                                                                                                                                                                                                                                                     |

|------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C17, D14, D15 D16,<br>D17, E16, E17, F14,<br>F15 F16 | RX3-0, RX3-1,<br>RX3-2, RX3-3,<br>RX3-4, RX3-5,<br>RX3-6, RX3-7,<br>RX3-8, RX3-9 | OUTPUT - TTL: 10-Bit Receive Bus for Channel 3. Parallel data on this bus is synchronous to RC3-0 and RC3-1. RX3-0 is the first bit received.                                                                                                                   |

| T1                                                   | RCM0                                                                             | INPUT - TTL: Recovered Clock Mode Control. When LOW, RCi0/RCi1 is 1/20 <sup>th</sup> of the incoming baud rate. When HIGH, RCi0/RCi1 is 1/10 <sup>th</sup> the incoming baud rate.                                                                              |

| E1<br>E2                                             | RC00<br>RC01                                                                     | OUTPUT - Complementary TTL: Recovered complementary clocks for Channel 0 at 1/10 <sup>th</sup> the incoming baud rate (RCM=HIGH) or 1/20 <sup>th</sup> (RCM=LOW). Synchronous to the RX0[0:9] bus and SYN0.                                                     |

| A5<br>B5                                             | RC10<br>RC11                                                                     | OUTPUT - Complementary TTL: Recovered complementary clocks for Channel 1. At 1/10 <sup>th</sup> the incoming baud rate (RCM=HIGH) or 1/20 <sup>th</sup> (RCM=LOW). Synchronous to the RX1[0:9] bus and SYN1.                                                    |

| C10<br>D10                                           | RC20<br>RC21                                                                     | OUTPUT - Complementary TTL: Recovered complementary clocks for Channel 2 at 1/10 <sup>th</sup> the incoming baud rate (RCM=HIGH) or 1/20 <sup>th</sup> (RCM=LOW). Synchronous to the RX2[0:9] bus and SYN2.                                                     |

| B16<br>B17                                           | RC30<br>RC31                                                                     | OUTPUT - Complementary TTL: Recovered complementary clocks for Channel 3 at 1/10 <sup>th</sup> the incoming baud rate (RCM=HIGH) or 1/20 <sup>th</sup> (RCM=LOW). Synchronous to the RX3[0:9] bus and SYN3.                                                     |

| U4, U3<br>U7, U6<br>U11, U10<br>U14, U13             | SI0+, SI0-<br>SI1+, SI1-<br>SI2+, SI2-<br>SI3+, SI3-                             | $\label{eq:local_potential} INPUT - Differential PECL (AC-coupling recommended): Serial Receive Data Inputs for Channels 0-3. These are selected when LOOP is LOW. (internally biased to V_{DD}/2).$                                                            |

| N14                                                  | LOOP                                                                             | INPUT - TTL: Parallel Loopback Enable Input. SIi is input to the CRU for Channel i (normal operation) when LOOP is LOW. When HIGH, internal loopback paths from SOi to SIi are enabled.                                                                         |

| R17                                                  | SYNC                                                                             | INPUT - TTL: Enables SYNi and Word Alignment When HIGH. When LOW, keeps current word alignment and disables SYNi (always LOW).                                                                                                                                  |

| F2<br>A4<br>B10<br>B15                               | SYN0<br>SYN1<br>SYN2<br>SYN3                                                     | OUTPUT - TTL: Comma Detect for Channel i. This output goes HIGH for half of an RCi1 period to indicate that RXi[0:9] contains a "comma" character ('0011111XXX'). SYNi will go HIGH only during a cycle when RCi0 is rising. SYNi is enabled when SYNC is HIGH. |

| P9<br>R9                                             | CAP0<br>CAP1                                                                     | ANALOG: Loop Filter Capacitor for the Clock Multiplier Unit. Typically 0.1µF connected between CAP0 and CAP1. Amplitude is less than 3.3V.                                                                                                                      |

| T17                                                  | NC (TCK)                                                                         | INPUT - TTL: JTAG Test Clock                                                                                                                                                                                                                                    |

| D9                                                   | NC (TMS)                                                                         | INPUT - TTL: JTAG Test Mode Select                                                                                                                                                                                                                              |

| R15                                                  | GND (TRSTN)                                                                      | INPUT - TTL: JTAG Test Reset, Active LOW                                                                                                                                                                                                                        |

| P15                                                  | NC (TDI)                                                                         | INPUT - TTL: JTAG Test Data Input                                                                                                                                                                                                                               |

### Quad Transceiver for Gigabit Ethernet and Fibre Channel

| Pin                                                                                                                                | Name                             | Description                                         |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------|

| K2                                                                                                                                 | NC (TDO)                         | OUTPUT - TTL: JTAG Test Data Output                 |

| Т9                                                                                                                                 | VCCA                             | Analog Power Supply                                 |

| R8                                                                                                                                 | GNDA                             | Analog Ground. Tie to common ground plane with GND. |

| A2,A10,C14<br>G4,J14,K16<br>L4,N15,R4<br>R14,R16,T3<br>T4,T14,U5                                                                   | VCC                              | Digital Logic Power Supply                          |

| C4, D3,F3<br>A9, B7, C5<br>A13, A16, C11<br>C15, E14, G17                                                                          | VCCT                             | TTL Output Power Supply                             |

| T5<br>T7<br>T11<br>T13                                                                                                             | VCCP0<br>VCCP1<br>VCCP2<br>VCCP3 | PECL I/O Power Supply for Channel i                 |

| A1,A3,A11,A15A17<br>,B4,C7<br>C16,D4,D11<br>E15,F4                                                                                 | GNDT                             | Ground for TTL Outputs                              |

| B9,F17,G3,K3,<br>K14,K15,L3,P6,P8,P<br>10,P12,P14<br>R6,R10,R12,T2T6,T<br>8,T10,T12T15,T16,<br>U1,U2,U8,U9,U12,<br>U15<br>U16, U17 | GND                              | Ground                                              |

## Advance Product Information VSC7186-01

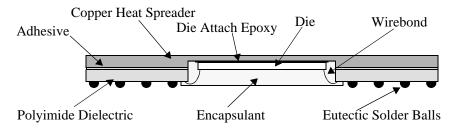

### Package Thermal Characteristics

The VSC7186-01 is packaged in a 23mm BGA package with 1.27mm eutectic ball spacing. The construction of the package is shown in Figure 6.

Figure 6: Package Cross Section

The VSC7186-01 is designed to operate with a case temperature up to  $100^{\circ}$ C. In order to comply with this target, the user must guarantee that the case temperature specification of  $100^{\circ}$ C is not violated. With the thermal resistances shown in Table 7, the VSC7186-01 can operate in still air ambient temperatures of  $40^{\circ}$ C [  $40^{\circ}$ C =  $100^{\circ}$ C - 2.5W \*  $24^{\circ}$ C/W ]. If the ambient air temperature exceeds these limits then some form of cooling through a heatsink or an increase in airflow must be provided.

**Table 7: Thermal Resistance**

| Symbol                   | Description                                                                                  | Value | Units |

|--------------------------|----------------------------------------------------------------------------------------------|-------|-------|

| $\theta_{ m jc}$         | Thermal resistance from junction-to-case                                                     | 4.3   | °C/W  |

| $\theta_{\mathrm{ca}}$   | Thermal resistance from case-to-ambient in still air including conduction through the leads. | 24    | °C/W  |

| $\theta_{\text{ca-100}}$ | Thermal resistance from case-to-ambient with 100 LFM airflow                                 | 21    | °C/W  |

| $\theta_{\text{ca-200}}$ | Thermal resistance from case-to-ambient with 200 LFM airflow                                 | 18.5  | °C/W  |

| $\theta_{\text{ca-400}}$ | Thermal resistance from case-to-ambient with 400 LFM airflow                                 | 17    | °C/W  |

| $\theta_{\text{ca-600}}$ | Thermal resistance from case-to-ambient with 600 LFM airflow                                 | 15    | °C/W  |

### Moisture Sensitivity Level

This device is rated at with a Moisture Sensitivity Level 3 rating. Refer to Application Note AN-20 for appropriate handling procedures.

Quad Transceiver for Gigabit Ethernet and Fibre Channel

### Advance Product Information VSC7186-01

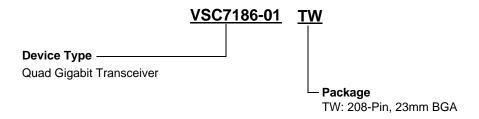

### **Ordering Information**

The order number for this product is formed by a combination of the device type and package type.

#### **Notice**

This document contains information about a new product during its fabrication or early sampling phase of development. The information in this document is based on design targets, simulation results or early prototype test results. Characteristic data and other specifications are subject to change without notice. Therefore the reader is cautioned to confirm that this data sheet is current prior to design or order placement.

#### Warning

Vitesse Semiconductor Corporation's products are not intended for use in life support appliances, devices or systems. Use of a Vitesse product in such applications without written consent is prohibited.