# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

## 8-BIT, 25MHz, VIDEO FLASH ADC (SINGLE + 5V SUPPLY)

The VP1058 is a low power analog-to-digital flash converter which requires no preceding sample and hold stage. Operating from a single +5V supply, it is capable of digitising analog signals with frequencies up to the Nyquist

Output data is available in four possible 8-bit formats, selectable via two digital control inputs, giving either true or inverted code in binary or offset twos' complement.

#### **FEATURES**

- 8-Bit Resolution

- 25MHz Conversion Rate

- 60MHz 3dB Analog Input Bandwidth

- Single +5V Supply Operation

- Low Power Consumption (Typically 670mW)

- +3V to +5V Analog Input Range

- Selectable Data Format

- TTL Compatible

- Direct Replacement for TDC 1058 or CXA 1096P

- Low Cost

- No Missing Codes Guaranteed

#### **APPLICATIONS**

- Digital Television

- Computing

- Radar

- Medical Imaging

- **Nucleonics**

- Low-Cost, High-Speed Data Conversion

#### **OPERATING TEMPERATURE RANGE**

Commercial 0°C to 70°C (Still - Air ambient)

## ORDERING INFORMATION

VP1058 F CG DPAS (Commercial - Plastic DIL Package, DP28) VP1058 F CG HPAS (Commercial - Quad Plastic J Lead Package,

VP1058 F CG DGAS (Commercial - Ceramic DIL Package, DG28)

#### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage +7V Analog input, AIN Vcc +0.5 Reference voltage VRT, VRB Vcc +0.5 Reference voltage VRT, VRB 2.5V Digital inputs Vcc Mid-ref input current -50mA to +50mA Digital output current -20mA to +20mA Voltage between AGND and DGND -0.5V to +0.5V Voltage between AVcc and DVcc -0.5V to +0.5V

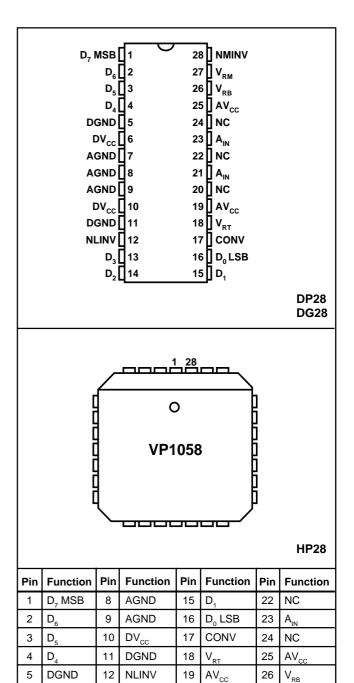

Fig.1 Pin Connections (Top View)

20

21

$DV_{CC}$

**AGND**

6

13  $D_{3}$

14 D, NC

27

28

$V_{RM}$

**NMINV**

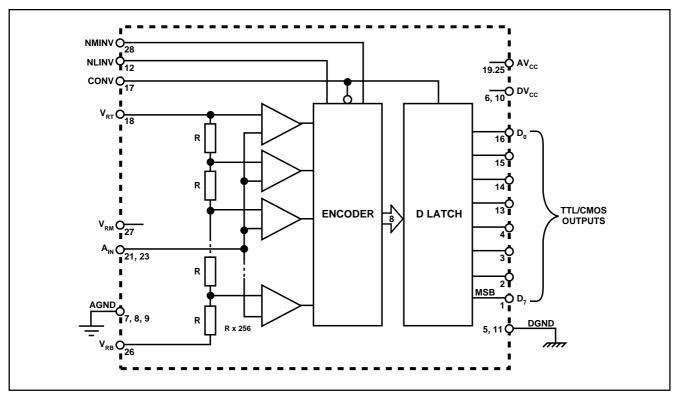

Fig.2 Internal block diagram

## **PIN DESCRIPTIONS**

| Pin No.    | Function                        | Description                                                                                      |

|------------|---------------------------------|--------------------------------------------------------------------------------------------------|

| 1          | D <sub>7</sub>                  | Most significant bit (output data bit 7)                                                         |

| 2 - 4      | D <sub>6</sub> - D <sub>4</sub> | Output data bits 6 to 4                                                                          |

| 5, 11      | DGND                            | Digital ground                                                                                   |

| 6, 10      | $DV_cc$                         | Digital supply pin (+5V)                                                                         |

| 7 - 9      | AGND                            | Analog ground                                                                                    |

| 12         | NLINV                           | Not Least significant bits INvert - inverts data D <sub>0</sub> to D <sub>6</sub> when taken low |

| 13 - 15    | D <sub>3</sub> - D <sub>1</sub> | Output data bits 3 to 1                                                                          |

| 16         | $D_{o}$                         | Least significant bit (output data bit 0)                                                        |

| 17         | CONV                            | Clock input - the rate of input (CONVert) clock signal determines the ADC sampling rate          |

| 18         | $V_{RT}$                        | Top of reference resistor chain                                                                  |

| 19, 25     | $AV_cc$                         | Analog supply pin                                                                                |

| 20, 22, 24 | NC                              | Not connected                                                                                    |

| 21, 23     | $A_{IN}$                        | Analog input pin                                                                                 |

| 26         | $V_{RB}$                        | Bottom of reference resistor chain                                                               |

| 27         | $V_{_{RM}}$                     | Midpoint of reference resistor - can be used for linearity adjustment                            |

| 28         | NMINV                           | Not Most significant bit INvert - inverts data bit D <sub>7</sub> when taken low                 |

## THERMAL CHARACTERISTICS

| Storage Temperature Rai | o +150°C |        |    |      |

|-------------------------|----------|--------|----|------|

| Maximum Junction Opera  | ire      | +175°C |    |      |

| Lead Temperature (solde | s)       | 300°C  |    |      |

|                         | DP       | HP     | DG |      |

| Junction to Ambient θjA | 55       | 57     | 44 | °C/W |

| Junction to Case θjc    | 14       | 15     | 9  | °C/W |

|                         |          |        |    |      |

## RECOMMENDED OPERATING CONDITIONS

| Supply Voltage                       | $5V \pm 0.25V$ |

|--------------------------------------|----------------|

| Reference V <sub>RT</sub>            | $5V \pm 0.1V$  |

| Reference V <sub>RB</sub>            | $3V \pm 0.1V$  |

| AV <sub>cc</sub> to DV <sub>cc</sub> | $0V \pm 50 mV$ |

| Analog Input                         | $4V \pm 1V$    |

## **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions conditions (unless otherwise stated):

$V_{CC} = +5V \pm 0.25V$ ,  $T_{amb} = 25^{\circ}C$  **DC CHARACTERISTICS**

| Characteristic                                                                                                                     | Symbol                                                                    | Temp                                           | Test level                 | Value.                |                                            |                                      | Units                                                  | Conditions                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|----------------------------|-----------------------|--------------------------------------------|--------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                                                                                                    | Cymbol                                                                    |                                                |                            | Min.                  | Тур.                                       | Max.                                 | Office                                                 | Conditions                                                                             |

| Power Supply                                                                                                                       |                                                                           |                                                |                            |                       |                                            |                                      |                                                        |                                                                                        |

| Supply voltage                                                                                                                     | AV <sub>cc</sub> /DV <sub>cc</sub>                                        | Full                                           | 4                          | 4.75                  |                                            | 5.25                                 | V                                                      | AGND/DGND = 0V                                                                         |

| Supply current                                                                                                                     | I <sub>cc</sub>                                                           | Full<br>25                                     | 4<br>1                     | 95<br>105             | 125<br>125                                 | 165                                  | mA<br>mA                                               |                                                                                        |

| Power dissipation                                                                                                                  | Р                                                                         | Full<br>25                                     | 4                          | 500<br>540            | 670                                        | 150<br>900                           | mW<br>mW                                               |                                                                                        |

| Analog Input                                                                                                                       |                                                                           | 25                                             | ı                          | 540                   | 670                                        | 830                                  | IIIVV                                                  |                                                                                        |

| Input range Input bias current 3dB bandwidth Input capacitance Reference Ladder                                                    | A <sub>IN</sub><br>I <sub>IN</sub><br>f <sub>3dB</sub><br>C <sub>IN</sub> | Full<br>Full<br>25<br>25                       | 4<br>4<br>4<br>4           | V <sub>RB</sub><br>60 | 150<br>60<br>30                            | V <sub>RT</sub><br>500               | V<br>μA<br>MHz<br>pF                                   |                                                                                        |

| Ladder resistance  Ladder voltage (top)  Ladder voltage (bottom)  Ladder offset (top)  Ladder offset (bottom)  Ladder temp. coeff. | R <sub>D</sub> VRT VRB VRTO VRBO P                                        | Full<br>25<br>Full<br>Full<br>25<br>25<br>Full | 4<br>1<br>4<br>4<br>5<br>5 | 50<br>75<br>2.5       | 90<br>100<br>5.0<br>3.0<br>15<br>5<br>0.33 | 145<br>125<br>AV <sub>cc</sub> + 0.1 | $\Omega$ $\Omega$ $V$ $W$ $mV$ $mV$ $\Omega/^{\circ}C$ |                                                                                        |

| Digital Inputs  Logic '1' voltage  Logic '0' voltage  Logic '1' current  Logic '1' current  Logic '0' current  Digital Outputs     | R to V H H H H H                                                          | Full<br>Full<br>Full<br>Full<br>Full           | 4<br>4<br>4<br>4<br>4      | 2.0                   | 0.00                                       | 0.8<br>350<br>75<br>-150             | V<br>V<br>μΑ<br>μΑ<br>μΑ                               | $V_{i} = V_{CC} = MAX$<br>$V_{i} = 2.4V, V_{CC} = MAX$<br>$V_{i} = 0.4V, V_{CC} = MAX$ |

| Logic '1' voltage  Logic '0' voltage                                                                                               | V <sub>OH</sub><br>V <sub>OL</sub>                                        | Full<br>25<br>Full<br>25                       | 4<br>1<br>4<br>1           | 2.4<br>2.4            |                                            | 0.4<br>0.4                           | V<br>V<br>V                                            | Into a standard<br>LSTTL load                                                          |

| Static performance Differential non-linearity                                                                                      | DNL                                                                       | Full                                           | 4                          |                       | ±0.5                                       |                                      | LSB                                                    |                                                                                        |

| Integral non-linearity                                                                                                             | INL                                                                       | 25<br>Full<br>25                               | 4<br>4<br>4                |                       | ±0.5<br>±0.5<br>±0.5                       |                                      | LSB<br>LSB<br>LSB                                      |                                                                                        |

### **AC CHARACTERISTICS**

| Characteristic             | Symbol           | Temp | Test level | Value.      |      |      | Units | Conditions                         |  |

|----------------------------|------------------|------|------------|-------------|------|------|-------|------------------------------------|--|

|                            | - Cymbol         | Tomp |            | Min. Typ. I |      | Max. |       | Conditions                         |  |

| Clock min.high             | t <sub>PW1</sub> | Full | 4          | 15          |      |      | ns    |                                    |  |

| Clock min.low              | t FWO            | Full | 4          | 15          |      |      | ns    |                                    |  |

| Max. conversion rate       | f MAX            | Full | 4          | 25          |      |      | MHz   | A <sub>IN</sub> at FS & 12.5MHz    |  |

| Aperture delay             | t <sub>AD</sub>  | 25   | 5          |             | 3    |      | l ns  | IN                                 |  |

| Output data delay          | t <sub>D</sub>   | 25   | 4          |             |      | 25   | ns    | <u></u>                            |  |

| Calpar data dota)          | U U              | Full | 4          |             |      | 30   | ns    | With standard                      |  |

| Output hold time           | t <sub>HO</sub>  | 25   | 4          | 5           |      |      | ns    | LSTLL load                         |  |

|                            | НО               | Full | 4          | 5           |      |      | ns    |                                    |  |

| Aperture Jitter            |                  | 25   | 5          | _           | 50   |      | ps    |                                    |  |

| Dynamic Performance        |                  |      |            |             |      |      |       | f <sub>CLK</sub> = 25MHz           |  |

| Differential non-linearity | DNL              | 25   | 1 1        | -0.85       | ±0.5 | +1   | LSB   |                                    |  |

| Integral non-linearity     | INL              | 25   | 1          |             | ±1   | ±2   | LSB   | } A <sub>IN</sub> at FS & 1.019MHz |  |

| S/N ratio                  | SNR              | 25   | 1          |             | 45   |      | dB    | $A_{IN} = 1.019MHz$                |  |

| 5,11,10,1110               |                  | Full | 4          |             | 44.5 |      | dB    | $A_{IN}^{IN} = 1.019MHz$           |  |

|                            |                  | 25   | 4          |             | 44.0 |      | dB    | $A_{} = 2.438MHz$                  |  |

|                            |                  | Full | 4          |             | 43.5 |      | dB    | $A_{} = 2.438MHz$                  |  |

|                            |                  | 25   | 4          |             | 43.5 |      | dB    | $A_{IN}^{IN} = 4.388MHz$           |  |

|                            |                  | Full | 4          |             | 43.0 |      | dB    | $A_{in} = 4.388MHz$                |  |

| Effective No. of bits      | ENOB             | 25   | 1          |             | 7.2  |      | bits  | $A_{} = 1.019MHz$                  |  |

|                            |                  |      | 4          |             | 7.1  |      | bits  | $ A_{ij}  = 2.438MHz$              |  |

|                            |                  |      | 4          |             | 7.0  |      | bits  | $A_{IN}^{IN} = 4.388MHz$           |  |

#### **ELECTRICAL CHARACTERISTICS DEFINITIONS**

#### **Analog Bandwidth**

The analog input frequency, at which the spectral power of the fundamental frequency as determined by Fast Fourier Transform analysis, is 3dB down on the DC level.

#### **Aperture Delay**

The delay between the falling edge of the CONV signal and the instant at which the analog input is sampled.

#### **Aperture Jitter**

The variation between successive samples of the aperture delay.

#### **Conversion Rate**

The maximum rate at which the converter will run.

#### **Differential Non-Linearity (DNL)**

The deviation of any code width from an ideal LSB step.

### **Effective Number of Bits (ENOB)**

This is a measure of the dynamic performance which is calculated from the following expression.:

$$ENOB = \frac{SNR-1.76}{6.02}$$

SNR is the signal-to-noise ratio, in decibels, at the test frequency.

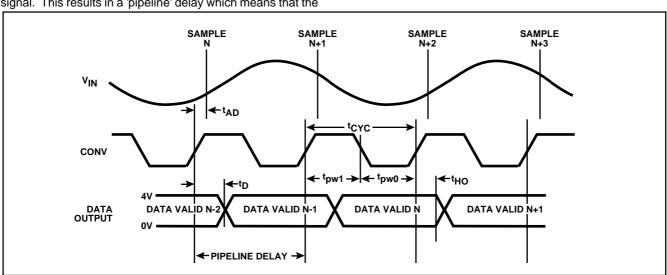

#### **CONVERSION TIMING**

Operation of the VP1058 requires that an external clock be applied to the CONV (convert) pin. This CONV signal synchronises the sampling, conversion, and output stages of the devices as shown in the timing diagram (Fig.3).

The analog input is sampled when the comparator array is latched after a rising edge on the CONV pin. This rising edge also causes the result of the previous sample to be transferred to the outputs. Data at the outputs is latched at the same time as the 255 to 8 encoding of the current sample. Both these operations are performed on the falling edge of the CONV signal. This results in a 'pipeline' delay which means that the

#### Integral Non-Linearity (INL)

The deviation of the centre of each code from a reference line which has been determined by a least squares curve fit.

#### **Output Data Delay**

The delay between the 50% point of the rising edge of the CONV signal and the 50% point of any data output change.

#### **Reference Ladder Offset**

The voltage error at the ends of the resistor chain caused by the lead frame and bond wire.

#### Signal-to-Noise Ratio (SNR)

The ratio of the RMS signal amplitude to the RMS value of 'noise' which is defined as the sum of all other spectral components including harmonics but excluding DC with a full scale analog input signal.

#### **Test Levels**

Level 1 - 100% production tested

**Level 2 -** 100% production tested at 25°C and sample tested at specified temperatures

Level 3 - Sample tested only

**Level 4 -** Parameter is guaranteed by design and characteristics testing

Level 5 - Parameter is a typical value only

digital result of sample 'N' is available for acquisition by external circuitry whilst sample 'N+2' is being taken.

The time interval between a rising edge on the CONV pin and the comparators latching is the aperture delay time ( $t_{AD}$ ). This time may be subject to small variations mainly due to temperature and component matching. The short term uncertainty in the aperture delay time is specified by the aperture jitter (or aperture error). Output data becomes valid after  $t_{D}$  (output data delay). Data remains valid for at least  $t_{HO}$  (output hold time) after the rising edge of the CONV pin.

Fig.3 Timing diagram

#### **GENERAL CIRCUIT DESCRIPTION**

The VP1058 employs a 'flash' architecture consisting of a reference resistor chain, an array of 256 comparators, encoding logic, and a full 8-bit D-type output latch. The 255 reference levels generated by the resistor chain are compared with the analog input signal by the comparator array. This produces a thermometer code which the encoding logic coverts into an 8-bit word. The D-type latch accepts this data and holds the outputs until the next conversion. The format of the output data is determined by the NLINV and NMINV control lines.

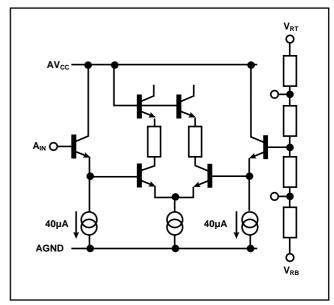

#### **Analog Input**

The maximum amplitude and offset of the input is defined by the setting of the two reference voltages  $V_{RB}$  and  $V_{RT}$ . A signal outside this range will cause the output to be either full-scale positive or full-scale negative, depending on whether the signal is off scale in the positive or negative direction.

For optimum performance, the input signal should be biased at +4.0V with a 2V peak-to-peak amplitude. The necessary gain, offset and low impedance drive required for the input signal can be provided by use of a high slew rate ADC driver.

#### **Reference Voltage**

The reference chain between pins  $V_{RB}$  and  $V_{RT}$  is formed of 256 series resistors and has a total resistance of approximately  $90\Omega$ . A mid-reference pin,  $V_{RM}$ , is provided for precise setting of the integral linearity, although adjustment is not necessary to meet the data sheet specification.

The VP1058 will convert analog signals in the range  $V_{RB} \le A_{IN} \le V_{RT}$ , where  $V_{RB}$  and  $V_{RT}$  are in the range +3V to +5V. (The design of the VP1058 has been optimised for VRB = 3V and VRT = 5V). All reference pins should be adequately decoupled close to the device.

## **Output Format**

The output data format is controlled by the logic levels at the NLINV and NMINV pins as shown on the output coding table. These inputs are active low and may be tied to  $\mathrm{DV}_\mathrm{CC}$  for logic '1' or DGND for logic '0'. Both inputs are considered DC controls and as such should only be altered while the converter is in the steady state.

Fig.4 Analog input

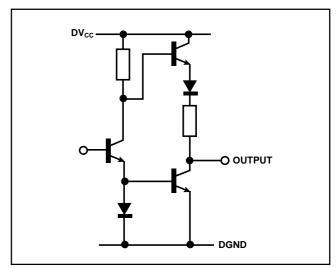

Fig.5 TTL output stage

|      | Input           | voltage           | Bin       | ary       | Offset 2s' complement |           |  |

|------|-----------------|-------------------|-----------|-----------|-----------------------|-----------|--|

| Code | pat             | vollago           | True      | Inverted  | True                  | Inverted  |  |

| Code | 20.V Full Scale | 2.048V Full Scale | NMINV = 1 | 0         | 0                     | 1         |  |

|      | 7.8431mV Step   | 8.0mV Step        | NLINV = 1 | 0         | 1                     | 0         |  |

| 000  | 5.0V            | 5.0V              | 0000 0000 | 1111 1111 | 1000 0000             | 0111 1111 |  |

| 001  | 4.9922V         | 4.9922V           | 0000 0001 | 1111 1110 | 1000 0001             | 0111 1110 |  |

| •    | •               | •                 | •         | •         | •                     | •         |  |

| 127  | 4.0039V         | 3.9840V           | 0111 1111 | 1000 0000 | 1111 1111             | 0000 0000 |  |

| 128  | 3.9961V         | 3.9760V           | 1000 0000 | 0111 1111 | 0000 0000             | 1111 1111 |  |

| 129  | 3.9882V         | 3.9680V           | 1000 0001 | 0111 1110 | 0000 0001             | 1111 1110 |  |

| •    | •               | •                 | •         | •         | •                     | •         |  |

| 254  | 3.0079V         | 2.9680V           | 1111 1110 | 0000 0001 | 0111 1110             | 1000 0001 |  |

| 255  | 3.0V            | 2.960V            | 1111 1111 | 0000 0000 | 0111 1111             | 1000 0000 |  |

Table 1 Output coding

#### **APPLICATION NOTES**

As with all high speed analog-to-digital converters, careful consideration must be given to circuit layout. The best performance from the VP1058 can be achieved by use of separate analog and digital ground planes. Ideally these should be connected at a point close to the device. This will reduce the amount of digital switching noise fed back into the analog section of the converter, so aiding device performance.

Supply line decoupling is important when dealing with mixed analog and digital signals, as they can provide a feedback path from the digital output currents. Therefore, the VP1058 should be decoupled close to the device supply pins with good quality high frequency, low inductance capacitors. Due to the high clock rates, long clock lines to the device should be avoided to reduce noise pick up.

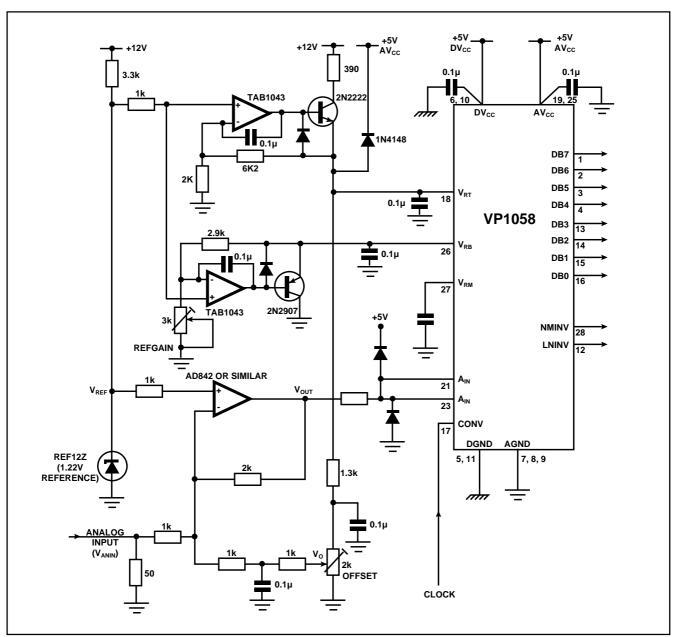

A typical applications circuit is shown below. The analog input amplifier should be a wideband, high slew rate op-amp used to drive the input directly. A stable reference is needed for both input offset and gain control (e.g. REF12Z micropower voltage reference as shown in Fig.6). Both analog input pins should be connected close to the device with the input amplifiers feedback loop closed at the point. The reference inputs should be adequately decoupled to ground so as to limit the effects of system noise on conversion accuracy. A capacitor at the mid-reference point (as shown) may be useful in correcting any inherent reference ladder skew.

The circuit will accept a 1V p-p video signal and level shift and multiply it to provide the recommended 2V p-p signal to drive the VP1058.

Fig.6 Typical applications circuit

# HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom.

Tel: (0793) 518000 Fax: (0793) 518411

#### **GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900

Tel: (408) 438 2900 Fax: (408) 438 5576

#### CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- **GERMANY** Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023.

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260. Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY

Swindon Tel: (0793) 518510 Fax: (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No. DS3003 Issue No. 3.0 June 1994

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any pound to reservice. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink s  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in and  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE