VC1021

**Preliminary**

# **Product Summary**

Quad 2.488 – 2.67 Gb/s SONET/SDH SERDES (Serializer/Deserializer) for OC-48, OC-192 Very-Short-Reach (VSR) Optics and Backplane Applications with Digital Wrapper data rate support

## **GENERAL DESCRIPTION**

The VC1021 is a versatile SERDES that provides an on-ramp to 2.488-2.67 Gb/s electrical or optical SONET/SDH aware backplanes, as well as driving Very-Short-Reach (VSR) optical interfaces. It provides four Serializer/Deserializer lanes, which run from 2.488–2.67 Gb/s, using CML differential I/Os.

The parallel side is an SFI-4 compliant (OIF99.102) 16 x 622MHz differential LVDS interface.

The VC1021 utilizes Velio's low-power GigaCore I/O technology, delivering unmatched signal integrity across both electrical and optical backplanes.

Table 1: VC1021 Features and Benefits

| FEATURES                                                                               | BENEFITS                                                                                                                                                  |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Four 2.488 – 2.67 Gb/s SerDes Lanes                                                    | Integration conserves board space, reduces power. Higher-speed option allows Forward Error Correction (FEC) and Digital Wrapper (g.709) data rate support |

| 16 bit, 622 – 669MHz LVDS Parallel-side Interface (SFI-4, XSBI compliant)              | Standard interface to ASICs, off-the-shelf Framers, and other components                                                                                  |

| 1.8 V Core, 2.5V LVDS I/O Voltage Supply                                               | Low Voltage Core reduces power consumption                                                                                                                |

| 2.2 W Typical Power                                                                    | Reduces overall system power requirements                                                                                                                 |

| OC-48, OC-192 modes                                                                    | Processes multiple line rates: 2.5 and 10 Gb/s data                                                                                                       |

| Adjustable Pre-Emphasis on Serial Outputs, including Programmable Output Voltage Swing | Reduces Inter-Symbol-Interference, enables serial transmission over longer distances                                                                      |

| Frame Alignment Flexible De-Skew Capability                                            | Aligns incoming SONET/SDH data via A1/A2 bytes; can de-skew up to 235 bytes; can be optionally disabled                                                   |

| Transparent Mode                                                                       | SONET/SDH Processing/Alignment can be disabled; enables support of FEC and Digital Wrapper traffic                                                        |

| SONET/SDH Processing, Byte Insertion/Monitor                                           | Allows performance monitoring, diagnostic modes                                                                                                           |

| IEEE 802.3ae compliant MDIO/MDC Interface                                              | Fast interface to configuration and status registers                                                                                                      |

| 27 mm x 27 mm BGA Package                                                              | Space-saving package                                                                                                                                      |

### **APPLICATIONS**

- SONET/SDH Backplane SerDes for OC-192 & OC-48 Applications

- FEC traffic, Digital Wrapper Support

- SONET/SDH Transceiver for OC-192 VSR (Very Short Reach) Optics

Figure 1: Pre-emphasis effects on Signal Integrity; a 2.488 Gb/s signal through 40" of FR4: disabled (left), and enabled (right)

PRELIMINARY

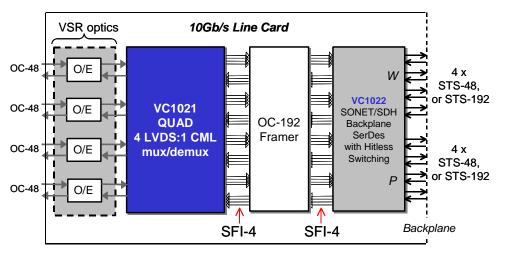

Figure 2: A line card with a VC1021 as an interface to VSR optics, connecting seamlessly to an OC-192 Framer device

#### **VSR APPLICATIONS**

The VC1021 functions as an interface to 4 x 2.488 Gb/s Very Short Reach (VSR) Optics. It converts 16 x 622MHz LVDS streams to four 2.488 Gb/s CML streams, for transmission across a VSR4-3 optical interface.

The 622MHz interface is industry standard OIF SFI-4 and **XSBI** compliant.

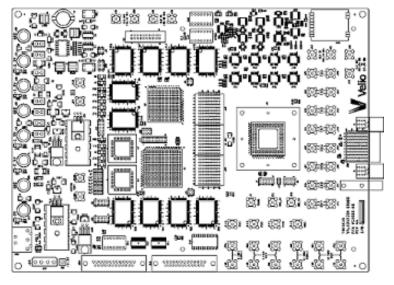

Figure 3: VC1021 Evaluation Platform

## VC1021 EVALUATION PLATFORM

The VC1021 Evaluation Platform is an extremely versatile tool for prototyping with the VC1021 SONET/SDH SerDes. It interfaces to existing systems, via both the LVDS Parallel interface and the CML Serial interface.

It contains an FPGA from each of the major suppliers, enabling flexible prototyping, and interoperability testing.

Velio reserves the right to change its products without notice. Velio advises its customers to obtain the latest version of all information prior to committing a device to an application.

Nothing herein grants any license to any intellectual property rights of Velio or any third party.

Velio is a trademark of Velio Communications, Incorporated. Copyright © 2002 Velio Communications, Incorporated.