# V23816-N1018-C322/L322<sup>(\*)</sup>

3.3 V, 4-Line LVDS Parallel 2.5 GBd Transponder OC-48 SONET/SDH Intermediate Reach (IR-1) up to 15 km

**Preliminary**

## **FEATURES**

- · Compliant with existing standards

- · Compact integrated transponder unit with

- DFB laser diode transmitter with optoisolator

- InGaAs PIN photodiode receiver

- Pigtailed optical connections

- Integrated Mux, Demux and Clock Recovery

- · Class 1 FDA and IEC laser safety compliant

- Single +3.3 V power supply

- OC-48 optical transmit and receive at 2488.32 Mbit/s

- · 4-line LVDS differential interface at 622.08 Mbit/s

- · External control for laser shutoff

- Loss of optical signal and Loss of synch indicators (RX)

- · Loss of lock indicator for TX high speed clock

- · Laser bias monitor

- · RX power monitor output

- · Loopback operating modes

- 155.520 MHz LVPECL input TX reference clock

- 2.8 W Typical Power Consumption

- · TX Fault output indicator

## **ABSOLUTE MAXIMUM RATINGS**

Operation beyond these ratings may cause permanent damage to the transponder.

| Supply Voltage (V <sub>CC</sub> )  | 0 to 4.0 V           |

|------------------------------------|----------------------|

| LVDS Input Levels                  | 0 to V <sub>CC</sub> |

| LVPECL Input Level                 | 0 to V <sub>CC</sub> |

| LVTTL Input Level                  | 0 to 5.5 V           |

| LVDS Output Source Current         | 5 mA                 |

| LVPECL Output Source Current       | 24 mA                |

| LVTTL Output Source Current        | 1 mA                 |

| Operating Ambient Temperature      | 0 to 70 °C           |

| Storage Ambient Temperature        | 40 to 85 °C          |

| Static Discharge Voltage, All Pins | 1000 V               |

## (\*) Ordering Information

| Connector type | Fiber length | Part number       |

|----------------|--------------|-------------------|

| SC             | 24.1 ±0.8 "  | V23816-N1018-C322 |

| LC             | 24.1 ±0.8 "  | V23816-N1018-L322 |

Fiber Optics OCTOBER 2001

### DESCRIPTION

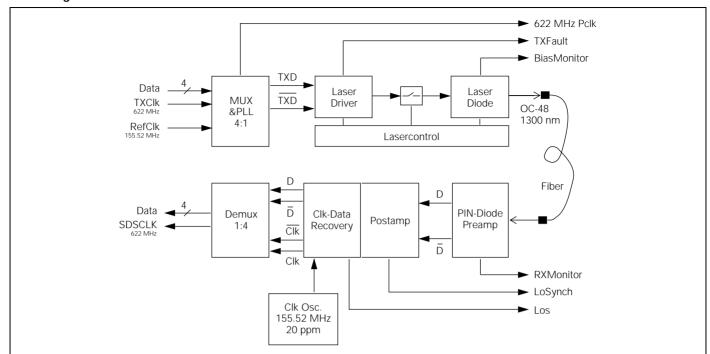

The Infineon single mode SONET/SDH transponder is compliant with the Bellcore GR-253, ITU-T G.957, and ITU-T G.958 specifications. The transmitter section consists of a multiplexer (Mux), laser driver, Distributed Feed Back (DFB) laser diode and pigtail single mode fiber with LC/PC or SC/PC 0° termination. The receiver section consists of a multimode fiber pigtail with LC/PC or SC/PC termination, a packaged PIN photodiode and preamplifier, postamplifier, clock and data recovery (CDR), and a demultiplexer (Demux). The Mux and Demux functions are integrated together onto a single Transceiver IC. The 622.08 MHz parallel data interface frees the user from the concerns of pcb layout at 2.5 Gb/s. The pluggable connector blind mates easily to the customer pcb, and allows the transponder to be removed prior to any solder reflow or washing of the users pcb.

The transponder operates from a single +3.3 V power supply. The electrical interface is via a 60 pin pluggable connector. The transmit and receive electrical signals each consist of 4 parallel differential LVDS data, and a differential LVDS clock. The transmit input data and clock lines, and the receive output data and clock lines, are all internally biased and terminated. All lines are DC coupled to the interface connector.

The transponder is designed to transmit and receive serial OC-48 (2488.32 Mb/s) data over standard non-dispersion-shifted single mode fiber at a wavelength of 1310 nm.

## Transmitter (Mux Section)

Please refer to the transponder block diagram.

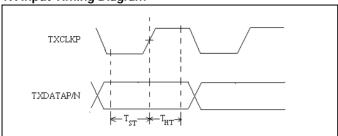

The transmitter accepts a 4 bit wide parallel input data word, TXDATAP/N[3:0], at a 622.08 Mb/s data rate. The TX input clock, TXCLKP/N, is synchronous with the incoming data, at a frequency of 622.08 MHz. This clock is used to load the data into a 4-bit latch. The data is read in on the rising edge of the positive input clock. (See TX Input Timing Diagram).

A reference input clock, REFCLKP/N, at 155.52 MHz, is supplied as a reference input to the high speed Clock Synthesizer. The high speed output of the clock synthesizer will clock the Timing Generator and the Parallel-to-Serial Converter. The Parallel-to-Serial Converter will output the retimed data as a serial bit stream, TSDP/N, at 2488.32 Mb/s data rate. Bit 3 of the TXDATAP/N parallel input word is the MSB, and is transmitted first in the data stream. Bit 0, the LSB, is transmitted last.

The output of the high speed Clock Synthesizer, which is internally set to 2488.32 MHz, is tapped off the Timing Generator, and is divided to 622.08 MHz. This output (PCLKP/N) is intended to be used as a reference clock for TX upstream logic.

The TX Clock Synthesizer section provides a lock alarm output signal, TXLOCK, which indicates if the clock synthesizer is properly phase locked.

## Transmitter (Electro-Optical Section)

The serial data output, TSDP/N, of the Transceiver IC is input to a laser driver IC. The laser driver provides both bias and modulation to a laser diode. The laser bias current is controlled by a closed-loop circuit, which regulates the output average power of the laser over conditions of temperature and aging. The Monitor PIN diode, which is mechanically built into the laser, provides a feedback signal to the laser driver, and prevents the laser power from exceeding the factory preset operating limits.

The laser driver includes an eye safety feature that will automatically shut off power to the laser if a fault condition occurs which causes excessively high laser bias current or excessively high average output power. Such a fault will be indicated on the TX\_FAULT output. The fault can be cleared by cycling DC power, or by strobing the RESET\_L input.

The Mux and Laser Driver can be reset with the RESET\_L input. During the time that RESET\_L is held active, there will be no optical output from the transmitter. The RESET\_L input will clear any fault indication that has occurred on the TX\_FAULT output.

The laser can be switched off at any time with the LASER\_DISABLE input.

The TX\_BIASMON output is provided as an alarm to indicate if the laser bias current is outside of the normal operating range. This output can be used to monitor the aging of the laser.

The laser diode is a DFB type, which will emit light in a single longitudinal mode centered at nominal wavelength of 1310 nm. This type of laser is suited for the intermediate reach transmission over single-mode fiber that this transponder is intended for. The laser has a built-in optoisolator, and a single-mode fiber pigtail which is terminated in an LC/PC or SC/PC 0° optical connector.

## **Receiver (Electro-Optical Section)**

The input light to the RX is coupled from the transmission fiber into a PIN/Preamp assembly on the transponder. The PIN/Preamp contains a multi-mode fiber pigtail, which is terminated in an LC/PC or SC/PC 0 ° optical connector. The multi-mode fiber pigtail has a larger core diameter (50  $\mu m$ ) than the single-mode transmission fiber (9  $\mu m$ ). Therefore, all the light from the single-mode fiber is coupled into the larger diameter core of the multi-mode pigtail.

The PIN/Preamp contains a PIN photodiode, trans-impedance amplifier and non-limiting post-amplifier in one package. The PIN diode produces a current output, which is directly proportional to the intensity of the incoming light. The trans-impedance amplifier performs current-to-voltage conversion, and the non-limiting post-amplifier quantizes the signal into a digital output.

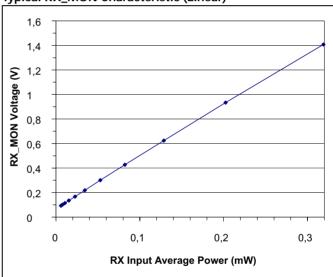

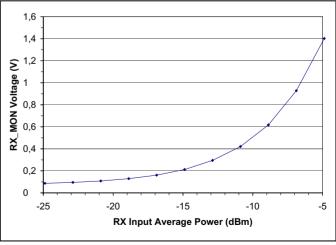

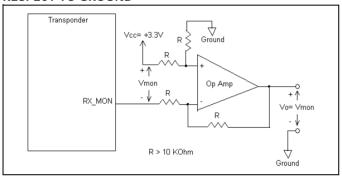

The receiver contains a RX power monitor output, which is a voltage output directly proportional to the average optical input power.

The Limiting Post-Amplifier provides additional voltage amplification, and also provides a Loss Of Signal (RX\_LOS) indicator. LOS will occur at a RX input power level less than the specified RX Sensitivity, and is an indication that the RX is taking bit errors.

The Clock and Data Recovery (CDR) uses a PLL based approach to recover the high speed clock from the incoming serial data stream. A lock alarm, RX\_LOSYNC, indicates if the CDR has lost synchronization. This will occur if the input RX power level is very low (below the LOS threshold level), or if the input data rate is outside the specified frequency tolerance. In these cases, the CDR will phase lock to a Crystal Oscillator so it can produce a valid clock output, with a frequency accuracy of  $\pm 20$  ppm. In both cases of Loss Of Signal or Loss Of Synchronization, the Transceiver IC will force all the RX output data bits, RXDATAP/N [3:0] to a constant zero state.

## Receiver (Demux section)

The incoming serial data is latched into the Transceiver IC by the recovered clock. The data and clock are applied to a 4 bit wide Serial-to-Parallel Converter (Demux), which demultiplexes the data into a parallel format. The first bit received, i.e. the MSB which is transmitted first in the serial data stream, is placed into the highest order bit of the parallel output word, i.e. Bit 3 = MSB. The Transceiver IC, however, does not perform a frame alignment function. This means that the parallel output word will contain the bits in the correct order, however, the position of the bits within the parallel output word may be shifted by an arbitrary amount between 0 and 4 bits. It is the function of downstream framer logic to realign the bits.

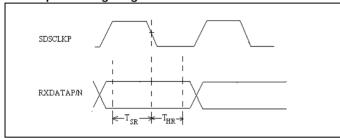

The retimed RX output data, RXDATAP/N[3:0], is output at a 622.08 Mb/s data rate. The output clock, SDSCLKP/N, is at 622.08 MHz. The RXDATAP/N[3:0] data is clocked out on the falling edge of SDSCLKP. (See RX Output Timing Diagram).

## **Loopback Operation**

Four loopback modes of operation are provided.

Line Loopback is enabled with the LLEB\_L input. In Line Loopback operation, the RX Serial Data and Clock inputs to the Transceiver IC (RSDP/N and RSCLKP/N) are routed directly to the TX Serial outputs of the IC (TSDP/N and TSCLKP/N). This effectively eliminates the Transceiver IC from the signal path.

Diagnostic Loopback is enabled with the DLEB\_L input. In Diagnostic Loopback operation, the TX output Serial Data and Clock of the Transceiver IC (TSDP/N and TSCLKP/N) are routed directly to the RX Serial Data and Clock inputs of the IC (RSDP/N and RSCLKP/N). This effectively eliminates the optical and electro-optical components from the signal path.

Reference Loop Time is enabled with the RLPTIME input. In Reference Loop Time operation, a divide-by-4 version of the POCLKP/N output of the RX is used as the reference clock input to the TX.

Serial Loop Time is enabled with the SLPTIME input. In Serial Loop Time operation, the recovered high-speed clock (RSCLKP/N) from the RX section is used in place of the synthesized transmit clock.

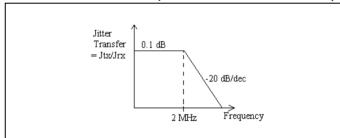

#### **Jitter**

The transponder is specified to meet the Sonet Jitter performance as outlined in ITU-T G.958 and Bellcore GR-253.

Jitter Generation is defined as the amount of jitter that is generated by the transponder. The Jitter Generation specifications are referenced to the optical OC-48 signals. If no or minimum jitter is applied to the electrical inputs of the transmitter, then Jitter Generation can simply be defined as the amount of jitter on the TX Optical output. The Sonet specifications for Jitter Generation are 0.01 UI rms, maximum and 0.1 UI p-p, maximum. Both are measured with a 12 KHz-20 MHz filter in line. A UI is a Unit Interval, which is equivalent to one bit slot. At OC-48, the bit slot is 400 ps, so the Jitter Generation specification translates to 4 ps rms, max. and 40 ps p-p, max.

Jitter Tolerance is defined as the amount of jitter applied to the RX Optical input that the receiver will tolerate while producing less than a 1 dB penalty in RX Sensitivity. The minimum Jitter Tolerance levels are normally expressed as a mask of jitter amplitude versus jitter frequency. Measured Jitter Tolerance levels must be greater than the mask limits. The Jitter Tolerance mask specified in the Bellcore GR-253 document covers jitter frequencies down to 10 Hz. The transponder is designed to meet this mask.

## Sonet Jitter Transfer Mask (ITU-T G.958 & Bellcore GR-253)

## Sonet Jitter Tolerance Mask (Bellcore GR-253)

Jitter Transfer is defined as the ratio of output jitter. Referenced to an optical transponder, it is defined as the ratio of TX Optical Output Jitter to RX Optical Input Jitter. To measure Jitter Transfer, the transponder must be operating in electrical loopback mode, with the RX electrical outputs looped back into the TX electrical inputs. Jitter Transfer is defined to be less than 0.1 dB up to 2 MHz, then dropping at –20 dB decade thereafter, per ITU-T G.958 and Bellcore GR-253. The Jitter Transfer must be less than the following mask limits.

## **Block Diagram**

## **Functional Signal Description**

## **Transmit Functions**

| Signal Name                                                             | Level  | I/O | Pin #                                    | Description                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------|--------|-----|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDATAPO TXDATANO TXDATAP1 TXDATAN1 TXDATAP2 TXDATAN2 TXDATAP3 TXDATAN3 | LVDS   | _   | 1<br>3<br>7<br>9<br>13<br>15<br>19<br>21 | Transmit Parallel input data at 622.08 Mb/s, aligned to the TXCLKP/N parallel input clock. TXDATAP/N[3] is the most significant bit (MSB), and is the first bit transmitted in the outgoing OC-48 serial data stream. TX-DATAP/N[3:0] is sampled on the rising edge of TX-CLKP. DC coupled and internally terminated. |

| TXCLKP<br>TXCLKN                                                        | LVDS   | _   | 27<br>25                                 | Transmit Parallel input clock, 622.08 MHz, to which TXDATAP/N[3:0] is aligned. TXCLK transfers the data on the TXDATAP/N inputs into a 4-bit wide latch in the Transceiver IC. Data is sampled on the rising edge of TXCLKP. DC coupled and internally terminated.                                                    |

| REFCLKP<br>REFCLKN                                                      | LVPECL |     | 31<br>33                                 | 155.52 MHz Transmit Reference Clock input to the bit clock frequency synthesizer of the Transceiver IC. DC coupled and internally biased.                                                                                                                                                                             |

| No connect                                                              |        |     | 37<br>39                                 | Do not connect.                                                                                                                                                                                                                                                                                                       |

| LASER_<br>DISABLE                                                       | LVTTL  | I   | 49                                       | Laser Disable. Control input to disable Transmit laser. High = Disable laser. Pulled low through 1 k $\Omega$ resistor.                                                                                                                                                                                               |

| Signal Name    | Level | I/O | Pin #    | Description                                                                                                                                                                                                                |

|----------------|-------|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXLOCK         | LVTTL | 0   | 51       | Loss Of Lock alarm for TX<br>PLL of the Transceiver IC.<br>High = Locked. Asynchro-<br>nous output.                                                                                                                        |

| No connect     |       |     | 45<br>43 | Do not connect.                                                                                                                                                                                                            |

| TX_FAULT       | LVTTL | 0   | 53       | Transmit Fault alarm output. Indicates that the laser has been automatically shut off due to a fault in the TX laser circuit. High = TX Fault. Fault may be cleared by cycling DC power, or by strobing the RESET_L input. |

| TX_BIASMON     | LVTTL | 0   | 59       | Transmit Bias Monitor<br>alarm output. Indicates that<br>the bias current of the TX<br>laser is currently outside<br>normal operating limits.<br>High = TX Bias outside lim-<br>its.                                       |

| PCLKP<br>PCLKN | LVDS  | 0   | 10<br>8  | 622.08 MHz Parallel Clock<br>output. Generated by divid-<br>ing the internal high-speed<br>TX clock by 4.                                                                                                                  |

| RESET_L        | LVTTL | I   | 56       | Master Reset input. A Low level resets the TX Mux and Laser Driver. RESET_L must be held low for at least 6 millisec. Pulled high through a 1 k $\Omega$ resistor.                                                         |

## **Receive Functions**

| Signal Name                                                                                  | Level  | I/O | Pin #                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------|--------|-----|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDATAPO<br>RXDATANO<br>RXDATAP1<br>RXDATAN1<br>RXDATAP2<br>RXDATAN2<br>RXDATAN3<br>RXDATAN3 | LVDS   | 0   | 44<br>42<br>34<br>32<br>28<br>26<br>22<br>20 | Parallel Output Data at 622.08 Mb/s from the Receiver, aligned to the Parallel Output Clock (RXCLKP/N). RXDATAP/N[3] is the Most Significant Bit, and is the first bit received in the incoming OC-48 serial data stream. RXDATAP/N[3:0] is clocked out on the falling edge of SDSCLKP. All data outputs are forced to zero level under Loss Of Signal or Loss Of Synchronization conditions. DC coupled outputs. Internally terminated. |

| SDSCLKN<br>SDSCLKP                                                                           | LVDS   | 0   | 16<br>14                                     | Parallel Output Clock from the Receiver at 622.08 MHz. This clock is aligned to the RXDATAP/N[3:0] parallel output data. RXDATAP/N[3:0] is clocked out on the falling edge of SDSCLKP. Clock output is continuous under Loss Of Signal or Loss Of Synchronization conditions. DC coupled output. Internally terminated.                                                                                                                  |

| RX_LOS                                                                                       | LVTTL  | Ο   | 55                                           | Receive Loss Of Signal alarm<br>output. A High output level<br>indicates RX input power is<br>below the sensitivity level of<br>the receiver (high BER condi-<br>tion).                                                                                                                                                                                                                                                                  |

| RX_LOSYNC                                                                                    | LVTTL  | O   | 57                                           | Receive Loss Of Synchronization alarm output. A High output level indicates that the receive Clock Recovery unit has lost synchronization, due to either very low RX input power level, or input data rate outside of frequency tolerance.                                                                                                                                                                                               |

| RX_MON                                                                                       | Analog | Ο   | 58                                           | Receive power monitor<br>output. A voltage output<br>which is directly proportional<br>to the optical RX input<br>power.                                                                                                                                                                                                                                                                                                                 |

## **Loopback Modes**

| Signal<br>Name | Level | I/O | Pin # | Description                                                                                                                                                                                                                                      |

|----------------|-------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LLEB_L         | LVTTL | I   | 38    | Line Loopback Enable input. A Low level enables Line Loopback mode. When active, the RX inputs to the Transceiver IC will be routed directly to the TX outputs. Pulled high through a 1 k $\Omega$ resistor.                                     |

| DLEB_L         | LVTTL | I   | 40    | Diagnostic Loopback Enable input. A Low level enables Diagnostic Loopback mode. When active, the TX outputs of the Transceiver IC are routed directly to the RX inputs. Pulled high through a 1 k $\Omega$ resistor.                             |

| RLP-<br>TIME   | LVTTL | I   | 4     | Reference Loop Time Enable input. A High level enables Reference Loop Time. When active, a divide-by-4 version of the PO-CLKP/N output of the RX is used as the reference clock input to the TX. Pulled low through a 1 k $\Omega$ resistor.     |

| SLP-<br>TIME   | LVTTL | I   | 2     | Serial Loop Time Enable input. A High level enables Serial Loop Time. When active, the recovered high-speed clock (RSCLKP/N) from the RX section is used in place of the synthesized transmit clock. Pulled low through a 1 k $\Omega$ resistor. |

## DC Power

| Signal<br>Name  | Level     | I/O | Pin #                                                           | Description                                                                                                                                                                                                                                                    |

|-----------------|-----------|-----|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GROUND          | 0 V DC    | _   | 5,6,<br>11,12,<br>17,18,<br>23,24,<br>29,30,<br>35,36,<br>Blade | Ground connection for both signal and chassis ground on the transponder. The blade contact of the 60 pin interface connector is tied to ground in the transponder. Therefore, the blade of the user's mating connector should be connected to ground, as well. |

| V <sub>CC</sub> | +3.3 V DC | -   | 41,47,<br>46,48,<br>50,52,<br>54                                | DC Power Input. +3.3 V DC, nominal.                                                                                                                                                                                                                            |

## **Functional Diagrams**

## **TX Input Timing Diagram**

## **RX Output Timing Diagram**

## **TECHNICAL DATA**

## **Recommended Operating Conditions**

| Parameter                                 | Symbol            | Min. | Тур. | Max. | Units     |

|-------------------------------------------|-------------------|------|------|------|-----------|

| Operating Case Temperature <sup>(1)</sup> | T <sub>C</sub>    | 0    |      | 70   | °C        |

| Transponder Total Power Consumption       | P <sub>TOT</sub>  |      | 2.8  | 3.46 | W         |

| 3.3 V Supply Voltage                      | V <sub>CC</sub>   | 3.13 | 3.3  | 3.46 | V         |

| 3.3 V Supply Current                      | I <sub>CC</sub>   |      | 0.85 | 1.0  | А         |

| Input Differential Noise,<br>All Pins     | N <sub>DIFF</sub> |      |      | 15   | mV<br>0-p |

## Note

1.  $T_{\mbox{CASE}}$  is measured on top of the transponder (see details on page 1, outline dimensions)

## **DC Electrical Characteristics**

| Parameter                             | Symbol                               | Min.                    | Тур. | Max.                     | Units |

|---------------------------------------|--------------------------------------|-------------------------|------|--------------------------|-------|

| LVDS Input High Voltage               | LVDS V <sub>IH</sub>                 | 1.1                     |      | 1.9                      | V     |

| LVDS Input Low Voltage                | LVDS V <sub>IL</sub>                 | 0.6                     |      | 1.5                      |       |

| LVDS Input Voltage<br>Differential    | LVDS<br>V <sub>INDIFF</sub>          | 200                     |      | 1200                     | mV    |

| LVDS Input Single<br>Ended Voltage    | LVDS<br>V <sub>INSING</sub>          | 100                     |      | 600                      |       |

| LVDS Differential Input Resistance    | LVDS R <sub>DIFF</sub>               | 80                      | 100  | 120                      | Ω     |

| LVDS Output High<br>Voltage           | LVDS V <sub>OH</sub>                 | 1.13                    |      | 1.8                      | V     |

| LVDS Output Low<br>Voltage            | LVDS V <sub>OL</sub>                 | 0.7                     |      | 1.4                      |       |

| LVDS Output Differ-<br>ential Voltage | LVDS<br>V <sub>OUTDIFF</sub>         | 440                     | 740  | 1100                     | mV    |

| LVDS Output Single<br>Ended Voltage   | LVDS<br>V <sub>OUTSIN</sub> -<br>GLE | 220                     | 370  | 550                      |       |

| LVPECL Input Low<br>Voltage           | LVPECL V <sub>IL</sub>               | V <sub>CC</sub><br>-1.9 |      | V <sub>CC</sub><br>-1.4  | V     |

| LVPECL Input High<br>Voltage          | LVPECL<br>V <sub>IH</sub>            | V <sub>CC</sub><br>-1.1 |      | V <sub>CC</sub><br>-0.55 |       |

| LVPECL Input Single<br>Ended Swing    | LVPECL<br>V <sub>INSINGLE</sub>      | 200                     |      | 1200                     | mV    |

| LVPECL Input Differential Swing       | LVPECL<br>V <sub>INDIFF</sub>        | 400                     |      | 2400                     |       |

| LVPECL Input DC<br>Bias               | LVPECL<br>V <sub>BIAS</sub>          | V <sub>CC</sub><br>-0.5 |      | V <sub>CC</sub><br>-0.3  | V     |

| LVTTL Input High<br>Voltage           | LVTTL V <sub>IH</sub>                | 2.0                     |      | V <sub>CC</sub>          |       |

| LVTTL Input Low<br>Voltage            | LVTTL V <sub>IL</sub>                | 0                       |      | 0.8                      |       |

| LVTTL Input High<br>Current           | LVTTL I <sub>IH</sub>                |                         |      | 50                       | μΑ    |

| LVTTL Output<br>Current               | LVTTL I <sub>O</sub>                 | -500                    |      |                          |       |

| LVTTL Output High<br>Voltage          | LVTTL V <sub>OH</sub>                | 2.4                     |      |                          | V     |

| LVTTL Output Low<br>Voltage           | LVTTL V <sub>OL</sub>                |                         |      | 0.8                      |       |

## **AC Electrical Characteristics**

| Parameter                                                                   | Sym-<br>bol     | Condi-<br>tions                  | Min. | Тур.    | Max. | Units      |

|-----------------------------------------------------------------------------|-----------------|----------------------------------|------|---------|------|------------|

| Transmitter                                                                 | DOI             | tions                            |      |         |      |            |

|                                                                             |                 |                                  |      | (22.22  |      | NAL /      |

| TXDATAP/N[3:0]<br>Input Bit Rate                                            |                 |                                  |      | 622.08  |      | Mb/s       |

| TXCLKP/N Input Frequency                                                    |                 |                                  |      | 622.08  |      | MHz        |

| TXCLKP/N Input<br>Duty Cycle                                                |                 |                                  | 40   |         | 60   | %          |

| TXCLKP/N Input<br>Rise/Fall Time                                            |                 | 20-80%                           | 100  |         | 300  | ps         |

| TXDATA Setup<br>Time with re-<br>spect to the Ris-<br>ing edge of<br>TXCLKP | T <sub>ST</sub> | See TX<br>Timing<br>Dia-<br>gram |      |         | 200  |            |

| TXDATA Hold<br>Time with re-<br>spect to the Ris-<br>ing edge of<br>TXCLKP  | T <sub>HT</sub> | See TX<br>Timing<br>Dia-<br>gram |      |         | 200  |            |

| REFCLKP/N In-<br>put Frequency                                              |                 |                                  |      | 155.520 |      | MHz        |

| REFCLKP/N Input Frequency Tolerance <sup>(3)</sup>                          |                 |                                  |      |         | ±20  | ppm        |

| REFCLKP/N Input Duty Cycle                                                  |                 |                                  | 45   |         | 55   | %          |

| REFCLKP/N In-<br>put Rise/Fall<br>Time                                      |                 | 10-90%                           |      |         | 500  | ps         |

| REFCLKP/N Input Jitter <sup>(2)</sup>                                       |                 |                                  |      |         | 1    | ps,<br>rms |

| PHASE_INITP/N<br>Input Min. Pulse<br>Width                                  |                 |                                  | 3.2  |         |      | ns         |

| PCLKP/N Out-<br>put Frequency                                               |                 |                                  |      | 622.08  |      | MHz        |

| PCLKP/N Out-<br>put Duty Cycle                                              |                 |                                  | 45   |         | 55   | %          |

| Return Loss, All<br>AC Inputs & Out-<br>puts                                |                 | 10 MHz<br>- 1 GHz                | 15   |         |      | dB         |

| RESET_L Input<br>Min. Pulse Width                                           |                 |                                  | 30   |         |      | ms         |

| Parameter                                                                     | Sym-<br>bol     | Condi-<br>tions                         | Min. | Тур.   | Max. | Units |

|-------------------------------------------------------------------------------|-----------------|-----------------------------------------|------|--------|------|-------|

| Receiver                                                                      |                 | I                                       |      | 1      | 1    | ı     |

| RXDATAP/N[3:0]<br>Output Bit Rate                                             |                 |                                         |      | 622.08 |      | Mb/s  |

| SDSCLKP/N Output Frequency                                                    |                 |                                         |      | 622.08 |      | MHz   |

| SDSCLKP/N Output Duty Cycle                                                   |                 |                                         | 40   |        | 60   | %     |

| SDSCLKP/N Output Rise/Fall Time                                               |                 | 20-80%                                  | 100  |        | 300  | ps    |

| RXDATA Setup<br>Time with re-<br>spect to the Fall-<br>ing edge of<br>SDSCLKP | T <sub>SR</sub> | See RX<br>Timing<br>Dia-<br>gram        |      |        | 600  |       |

| RXDATA Hold<br>Time with re-<br>spect to the Fall-<br>ing edge of<br>SDSCLKP  | T <sub>HR</sub> | See RX<br>Timing<br>Dia-<br>gram        |      |        | 600  |       |

| Return Loss, all<br>AC Inputs & Out-<br>puts                                  |                 | 10 MHz<br>- 1 GHz                       | 15   |        |      | dB    |

| SDSCLKP/N Output Frequency Accuracy during LOS or LO- SYNC <sup>(1)</sup>     |                 | Over<br>operat-<br>ing<br>Temp<br>Range |      |        | ±20  | ppm   |

## Notes

- 1. T<sub>CASE</sub> is measured on top of the transponder (see details on page 1, outline dimensions)

- Maximum allowable jitter on the reference clock input (REFCLKP/N) such that the transmitter will meet ITU-T G.958 and Bellcore GR-253 Jitter Generation requirements. Measured with a 12 KHz - 20 MHz filter

- 3. The REFCLK input must be connected and not left open-circuit.

### **Transmitter Electro-Optical Characteristics**

| nansmitter Liectro-Opi                   | Denomination Complete Miles Time Many Herita |      |       |      |           |  |  |  |  |

|------------------------------------------|----------------------------------------------|------|-------|------|-----------|--|--|--|--|

| Parameter                                | Symbol                                       | Min. | Тур.  | Max. | Units     |  |  |  |  |

| Nominal Center Wave-<br>length           | TX λ <sub>NOM</sub>                          | 1310 |       |      | nm        |  |  |  |  |

| Range Of Center Wavelengths              | $\lambda_{MAX}$                              | 1260 |       | 1360 |           |  |  |  |  |

| Spectral Bandwidth (–20 dB)              | $\Delta\lambda_{20}$                         |      |       | 1    |           |  |  |  |  |

| Sidemode Suppression<br>Ratio            | SSR                                          | 30   |       |      | dB        |  |  |  |  |

| Average Output<br>Power <sup>(1)</sup>   | TX P <sub>AVG</sub>                          | -5   |       | 0    | dBm       |  |  |  |  |

| Extinction Ratio                         | TX ER                                        | 8.2  | 14    |      | dB        |  |  |  |  |

| Output Rise Time<br>20%-80%              | TXT <sub>R</sub>                             |      | 100   | 200  | ps        |  |  |  |  |

| Output Fall Time<br>80%-20%              | TX T <sub>F</sub>                            |      | 175   | 250  |           |  |  |  |  |

| Eye Diagram <sup>(2)</sup>               | TX ED                                        |      |       |      |           |  |  |  |  |

| TX Jitter Generation, rms <sup>(3)</sup> | TX<br>J <sub>GEN rms</sub>                   |      | 0.007 | 0.01 | UI<br>rms |  |  |  |  |

| TX Jitter Generation, p-p <sup>(3)</sup> | TX<br>J <sub>GEN p-p</sub>                   |      | 0.075 | 0.1  | UI p-p    |  |  |  |  |

| Reset Threshold for $V_{CC}^{(4)}$       | TX V <sub>TH</sub>                           | 2.2  |       | 2.95 | V         |  |  |  |  |

| Power On Delay for $V_{CC}^{(4)}$        | TX T <sub>POD</sub>                          | 8    | 11    | 14   | ms        |  |  |  |  |

| Fault Delay <sup>(5)</sup>               | TX<br>T <sub>FAULT</sub>                     | 15   | 22    | 29   |           |  |  |  |  |

| TX Bias Monitor switching threshold      | TX I <sub>BIAS</sub>                         |      |       | 60   | mA        |  |  |  |  |

#### Notes

- The laser driver contains a control circuit, which regulates the average optical output power. Nominal output power is factory set to be within the specified range.

- The Eye Diagram is compliant with Bellcore GR-253 and ITU-T G.957 Eye Mask specifications.

- 3. Jitter Generation is defined as the amount of jitter on the TX Optical Output, when there is no or minimum jitter on the TX electrical inputs. Jitter Generation is compliant with GR-253 and ITU-T G.958 specifications, when measured using a 12 KHz - 20 MHz filter, and with a jitter level on the REFCLKP/N input which is less than the level specified in "AC Electrical Characteristics - Transmitter".

- 4. If the +3.3 V power supply drops below the specified level, the laser bias and modulation currents will be held disabled until the supply voltage rises above threshold and after the Power On Delay Time period.

- A fault, such as high laser bias current or high average power, which lasts longer than the specified Fault Delay time, will cause the transmitter to be disabled. The fault can be cleared by cycling of DC power, or by strobing the RESET\_L input.

## **Receiver Electro-Optical Characteristics**

| Parameter                                                                      | Symbol                                | Min. | Тур. | Max. | Units     |

|--------------------------------------------------------------------------------|---------------------------------------|------|------|------|-----------|

| Nominal Center<br>Wavelength                                                   | RX λ <sub>NOM</sub>                   |      | 1310 |      | nm        |

| Sensitivity (Average Power) <sup>(1)</sup>                                     | RX P <sub>SENS</sub>                  |      | -25  | -18  | dBm       |

| Overload (Average<br>Power) <sup>(1)</sup>                                     | RX P <sub>OL</sub>                    | 0    |      |      |           |

| Optical Return Loss                                                            | RX RL                                 | 27   |      |      | dB        |

| RX Jitter Tolerance <sup>(2)</sup>                                             | $RX J_{TOL}$                          |      |      |      |           |

| RX-to-TX Jitter Transfer <sup>(3)</sup>                                        | RX-TX J <sub>XFR</sub>                |      |      |      |           |

| Optical Path Penalty                                                           | RX P <sub>PEN</sub>                   |      |      | 1.0  | dB        |

| Clock Recovery Capture Frequency Range <sup>(5)</sup>                          | RX F <sub>CAPT</sub>                  |      | ±200 |      | ppm       |

| Clock Recovery Acquisition Lock Time                                           | RX T <sub>LOCK</sub>                  |      | 32   | 250  | μs        |

| RX_LOS Output As-<br>sert relative To RX<br>Optical Input Power <sup>(4)</sup> | RX_<br>LOS <sub>ASSERT</sub>          | -30  |      | -25  | dBm       |

| RX_LOSYNC Output<br>Assert relative to RX<br>input frequency <sup>(5)</sup>    | RX_<br>LOSYNC <sub>AS</sub> .<br>SERT | ±450 | ±600 | ±770 | ppm       |

| RX_LOS Output Hys-<br>teresis <sup>(4)</sup>                                   | RX_<br>LOS <sub>HYST</sub>            |      |      | 3    | dB        |

| RX_LOS &<br>RX_LOSYNC Output<br>Assert Time <sup>(4, 5)</sup>                  | RX<br>T <sub>ASSERT</sub>             |      | 100  |      | μS        |

| RX_LOS &<br>RX_LOSYNC Output<br>Deassert Time <sup>(4, 5)</sup>                | RX<br>T <sub>DEASSERT</sub>           |      | 100  |      |           |

| RX_MON Transfer<br>Slope <sup>(6)</sup>                                        |                                       |      | 4.4  |      | mV/<br>μW |

| RX_MON Dark Offset<br>Voltage <sup>(6)</sup>                                   |                                       |      | 53   |      | mV        |

| RX_MON Output<br>Voltage at<br>P <sub>IN</sub> = -17 dBm <sup>(6)</sup>        |                                       |      | 142  |      |           |

| RX_MON Output<br>Voltage at<br>P <sub>IN</sub> = -7 dBm <sup>(6)</sup>         |                                       |      | 900  |      |           |

## Notes

- 1. Average RX power for a  $1\times10^{-10}$  BER, and using a PRBS pattern of  $2^{23}$ –1 length with 72 zeros and 72 ones inserted, as per ITU-T G 958

- Jitter Tolerance is defined as the amount of jitter applied to the RX optical input that the receiver will tolerate without producing bit errors. The minimum required Jitter Tolerance for a 1 dB power penalty is defined to be 15 UI from 10 Hz to 600 Hz, 1.5 UI from 6 KHz to 100 KHz, and 0.15 UI from 1 MHz onwards, per Bellcore GR-253.

- Jitter Transfer is defined as the ratio of TX Output Jitter to RX Input Jitter, when the transponder is operated in electrical loopback mode (RX electrical outputs looped back into TX electrical inputs). Jitter Transfer is specified to be less than 0.1 dB up to 2 MHz, and dropping at -20 dB/Decade after that point, per ITU-T G.958 and Bellcore GR-253.

- 4. The RX\_LOS output is an active high LVTTL output, which is set HIGH if there is a loss of RX optical signal input (LOS), A decrease in optical input power below the assert level will cause the RX\_LOS

- output to switch HIGH (ON). Hysteresis occurs when the optical input power is raised back above the threshold switching level. The RX\_LOSYNC output is an active high LVTTL output, which is set HIGH if the Clock Data Recovery PLL becomes unlocked. Loss Of Sync will occur at a lower optical input power level than LOS, but still within the specified input power range.

- 5. The receiver lock range is typically ±300 ppm from nominal OC-48 data rate. When the data rate of the RX signal deviates by more than ±600 ppm (typically) from nominal, or if the RX is in a Loss Of Signal (LOS) condition, then the Clock Recovery module will lock to an internal 155.52 MHz crystal oscillator. Under this condition: The appropriate fault output (RX\_LOS or RX\_LOSYNC) switches active; The RXDATAP/N[3:0] output data is forced to all zeros; and, the switching of the SDSCLKP/N output is done so that the clock is continuous, and there are no violations of the minimum pulse width and period.

- RX\_MON ouput voltage is measured between V<sub>CC</sub> (+) and RX\_MON (-). RX\_MON is specified up to a maximum optical input average power of –5 dBm (316.2 μW).

## **Connector Pin Assignments**

| Pin # | Signal Name   | Pin # | Signal Name |

|-------|---------------|-------|-------------|

| 1     | TXDATAP0      | 2     | SLPTIME     |

| 3     | TXDATAN0      | 4     | RLPTIME     |

| 5     | GND           | 6     | GND         |

| 7     | TXDATAP1      | 8     | PCLKN       |

| 9     | TXDATAN1      | 10    | PCLKP       |

| 11    | GND           | 12    | GND         |

| 13    | TXDATAP2      | 14    | SDSCLKP     |

| 15    | TXDATAN2      | 16    | SDSCLKN     |

| 17    | GND           | 18    | GND         |

| 19    | TXDATAP3      | 20    | RXDATAN3    |

| 21    | TXDATAN3      | 22    | RXDATAP3    |

| 23    | GND           | 24    | GND         |

| 25    | TXCLKN        | 26    | RXDATAN2    |

| 27    | TXCLKP        | 28    | RXDATAP2    |

| 29    | GND           | 30    | GND         |

| 31    | REFCLKP       | 32    | RXDATAN1    |

| 33    | REFCLKN       | 34    | RXDATAP1    |

| 35    | GND           | 36    | GND         |

| 37    | No connect    | 38    | LLEB_L      |

| 39    | No connect    | 40    | DLEB_L      |

| 41    | VCC           | 42    | RXDATAN0    |

| 43    | No connect    | 44    | RXDATAP0    |

| 45    | No connect    | 46    | VCC         |

| 47    | VCC           | 48    | VCC         |

| 49    | LASER_DISABLE | 50    | VCC         |

| 51    | TXLOCK        | 52    | VCC         |

| 53    | TX_FAULT      | 54    | VCC         |

| 55    | RX_LOS        | 56    | RESET_L     |

| 57    | RX_LOSYNC     | 58    | RX_MON      |

| 59    | TX_BIASMON    | 60    | SPARE       |

| BLADE | GND           |       |             |

## **Agency Certifications**

| Feature                                                              | Standard                                             | Comments                                                                                                                                                                   |

|----------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic Discharge (ESD) to the Electrical Pins                 | EIA/JESD22-A114-A<br>(MIL-STD 883D<br>Method 3015.7) | Class 1 (2000 V)                                                                                                                                                           |

| Immunity:<br>Electrostatic<br>Discharge (ESD)<br>to Housing/Pigtails | EN 61000-4-2<br>IEC 61000-4-2                        | Discharges ranging from ±2 kV to ±15 kV on housing/pigtails cause no damage to transponder (under recommended conditions).                                                 |

| Immunity:<br>Radio Frequency<br>Electromagnetic<br>Field             | EN 61000-4-3<br>IEC 61000-4-3                        | With a field strength of<br>10 V/m rms, noise<br>frequency ranges from<br>10 MHz to 2 GHz. No<br>effect on transponder<br>performance between<br>the specification limits. |

| Emission:<br>Electromagnetic<br>Interference (EMI)                   | FCC Part 15, Class B<br>EN 55022 Class B<br>CISPR 22 | Noise frequency range:<br>250 MHz to 18 GHz                                                                                                                                |

## Typical RX\_MON Characteristic (Linear)

## Typical RX\_MON Characteristic (Logarithmic)

#### **EYE SAFETY**

This laser based single mode transponder is a Class 1 product. It complies with IEC 60825-1 and FDA 21 CFR 1040.10 and 1040.11.

The transponder has been certified with FDA under accession number 9911449-04.

To meet laser safety requirements the transponder shall be operated within the Absolute Maximum Ratings.

#### Caution

All adjustments have been made at the factory prior to shipment of the devices. No maintenance or alteration to the device is required.

Tampering with or modifying the performance of the device will result in voided product warranty.

#### Note

Failure to adhere to the above restrictions could result in a modification that is considered an act of "manufacturing", and will require, under law, recertification of the modified product with the U.S. Food and Drug Administration (ref. 21 CFR 1040.10 (i)).

#### Laser Data

| Wavelength                                                              | 1310 nm |

|-------------------------------------------------------------------------|---------|

| Total output power (as defined by IEC: 7 mm aperture at 14 mm distance) | 2 mW    |

| Total output power (as defined by FDA: 7 mm aperture at 20 cm distance) | 180 μW  |

| Beam divergence                                                         | 5°      |

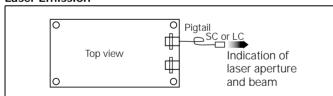

## **Required Labels**

## Laser Emission

#### APPLICATION NOTES

## INTERFACING THE 4-LINE TRANSPONDER

## Scope

This Application Note is meant to define the interfacing between the Infineon 4-Line OC-48 Transponder, and the customer equipment.

#### Introduction

The signals which interface to the OC-48 Transponder can be grouped into Transmit (TX) and Receive (RX) functions.

The TX signals are:

TXDATAP/N[0..3]: 4 differential LVDS inputs for TX Data. TXCLKP/N: A differential LVDS input for TX Clock. REFCLKP/N: A differential LVPECL input for TX Reference Clock

PCLKP/N: A differential LVDS output which is a divide-by-4 version of the TX high speed clock.

The RX signals are:

RXDATAP/N[0..3]: 4 differential LVDS outputs for RX Data. SDSCLKP/N: A differential LVDS output for RX Clock.

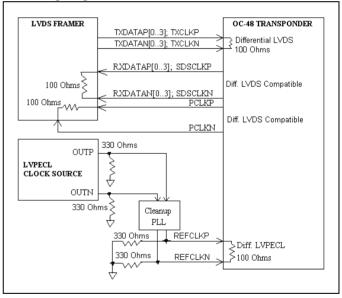

## Interfacing

## Interfacing Diagram

## TX Signals

The customer OC-48 framer drives the TXDATA and TXCLK inputs. In order to use DC Coupling, the framer should be a +3.3 V LVDS device. Each of the inputs is terminated with 100  $\Omega$  differential between lines in the transponder.

The REFCLK input is a LVPECL input, which is driven by the customer Clock Source, which should be an LVPECL device. DC coupling is acceptable if the clock source is a +3.3 V LVPECL. The REFCLK input is terminated with 100  $\Omega$  differential between lines in the transponder. It is necessary for the customer to provide the external 330  $\Omega$  resistors to ground for the source termination.

## **RX Signals**

The customer framer accepts as input the RXDATA and SDSCLK outputs of the transponder. In order to use DC Coupling, the framer should be a +3.3 V LVDS device. The RXDATA and SDSCLK outputs of the transponder are not true LVDS, but are LVDS level compatible, which use a 330  $\Omega$  to ground termination in the transponder. If the framer does not have a 100  $\Omega$  differential termination between lines, then the customer will have to supply the terminations on their board.

## Line Impedance

For proper impedance matching, all LVDS traces should be constructed as a differential trace pair, with 100  $\Omega$  characteristic impedance between the lines of each pair, and 50  $\Omega$  characteristic impedance per line. The LVPECL traces should be constructed as 50  $\Omega$  per line.

## CONVERSION OF RX\_MON OUTPUT TO A VOLTAGE WITH RESPECT TO GROUND

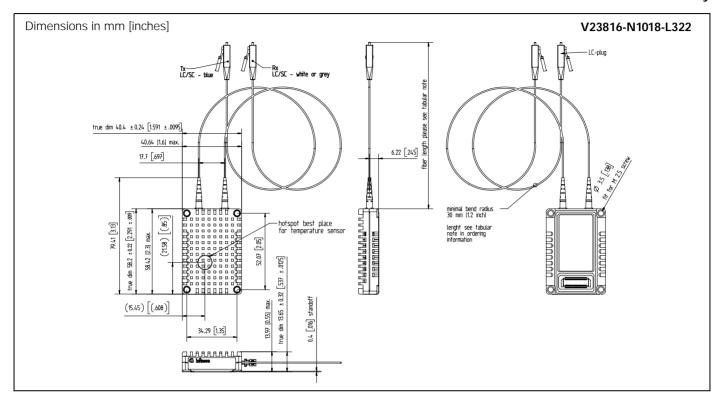

## **MECHANICAL**

#### Size

The outline size for the transponder housing is 2.3 in x 1.6 in x 0.54 inches. Please refer to the outline drawing.

## Fiber & Connectors

The transponder has fiber pigtails for both TX and RX. The TX pigtail is Single Mode Fiber, 9  $\mu$ m/125  $\mu$ m. The RX pigtail is Multi Mode Fiber, 50  $\mu$ m/125  $\mu$ m, allowing a highly tolerant coupling with a Single Mode Fiber. Each pigtail is terminated with a LC/PC or SC/PC optical connector with 0 ° polish. The minimum bend radius of the fiber pigtails is 30 mm (1.18 inches), typical. The fiber length see Ordering Information on page 1, as measured from the transponder housing to the tip of the connector.

#### Interface Connector

The transponder interface connector is a 60 pin SMT, dual row, header, 0.5 mm pitch, with ground blade, Samtec part number QTH-030-01-L-D-A. The appropriate mating connector for the customer pcb is a 60 pin SMT, dual row, socket, 0.5 mm pitch, with mating alignment pins, Samtec part number QSH-030-01-L-D-A. The internal blade of the connector should be connected to signal ground on the user's pcb. Contact Samtec for recommended pcb layout pattern for QSH connector.

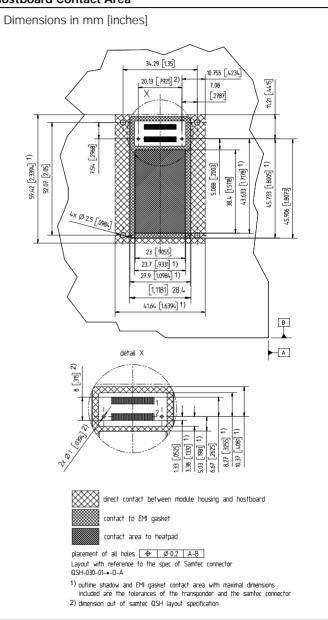

#### **Hostboard Contact Area**

For detailed connector layout information, check http://www.samtec.com, and go to "QSH" connector.

For the guaranteed EMI-performance an optimal electrical contact between the transponder housing and the user's pcb signal ground is necessary. For the user's pcb (hostboard) we recommend a full signal ground plane underneath the entire transponder housing (including the standoff area, the EMI gasket area and the optional heatsink area).

The transponder is equipped with an attached EMI gasket. According to the drawing "Hostboard Contact Area" the contact surface of the entire EMI gasket should be connected to signal ground on the user's pcb. The area under the EMI gaskets (EMI gasket area) should be gold flash or tin plated copper with no solder mask or other nonconductive coatings.

The four mounting screws of the housing also must be connected to signal ground on the user's pcb. Therefore the mounting screw areas should have square pads of gold flash or tin plated copper, that are connected to signal ground. These pads are located on the pcb opposite side to the transponder. Use a torque wrench to tighten the mounting screws. The recommended torque value is  $10 \pm 2 \text{ Ncm} = 0.1 \pm 0.02 \text{ Nm} = 14.16 \pm 2.83 \text{ oz-in}$ . With a higher or lower value, the EMI-performance will deteriorate.

The heatsink area under the center of the transponder is optional and could be used for critical ambient temperature or critical airflow. Currently it is not a complete replacement for the regular heatsink. The contact area should be connected to signal ground. Gold (Au), Tin or other metal platings are recommended for good heat transfer. Any polymer coating will decrease the heatsinking performance. Special heat transfer pads are in progress. For reliable heatsinking to the hostboard, the max. hostboard temperature must be lower or equal to the specified ambient air temperature.

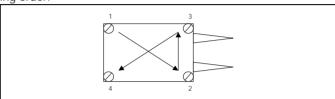

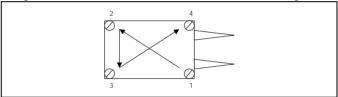

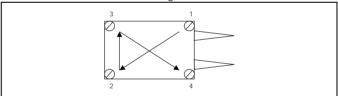

## Scheme of tightening mounting screws

It is recommended to use a torque wrench to tighten the mounting screws. Tightening torque value is:  $10 \pm 2 \text{ Ncm} = 0.1 \pm 0.02 \text{ Nm} = 14.16 \pm 2.83 \text{ oz-in}$ . With a higher or lower value, the EMI-performance will deteriorate

In order to avoid a mechanical stress of the users PCB and to reduce the impacting forces (twisting or wresting of the PCB) we recommend a crosswise tightening of the 4 mounting screws.

#### Scheme

Please tighten the screws according to the following scheme:

1. Insert four screws and tighten them very loose in the following order:

2. Tighten the four screws hand-screwed in the following order:

3. Tighten the four screws with a torque wrench 10  $\pm 2$  Ncm = 0.1  $\pm 0.02$  Nm

14.16 ±2.83 oz-in in the following order:

## Published by Infineon Technologies AG

#### © Infineon Technologies AG 2001 All Rights Reserved

## Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein. Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact the Infineon Technologies offices or our Infineon Technologies Representatives worldwide - see our webpage at

## www.infineon.com/fiberoptics

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your Infineon Technologies offices

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.