#### features

12-Bit, 21-MSPS, Analog-to-Digital Converter

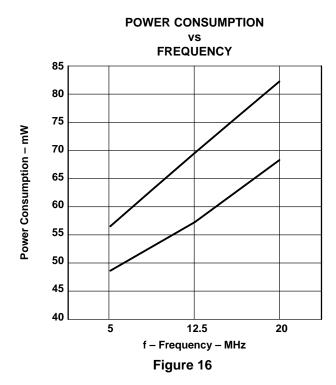

Very-Low Power: 70 mW Minimum Power-Down Mode: 4 mW

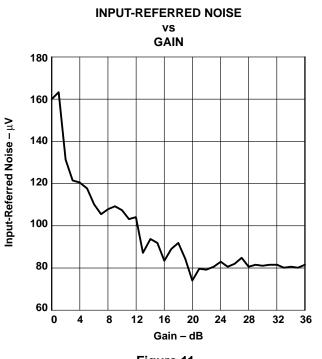

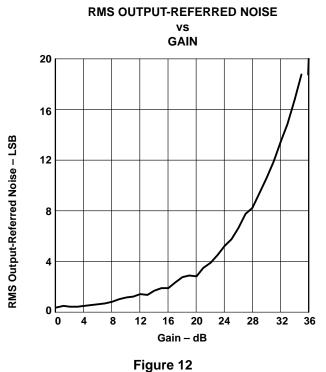

Very-Low Input-Referred Noise: 75-dB SNR Typical at 0-dB Gain

Novel Optical-Black (OB) Calibration

Low-Aperture Delay

Single 3-V Supply Operation

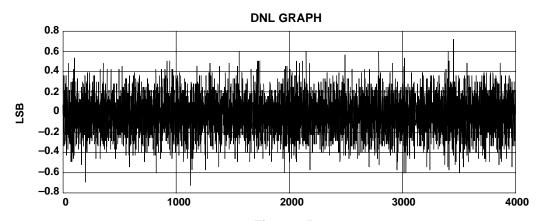

DNL: <±0.5 LSB and</li>

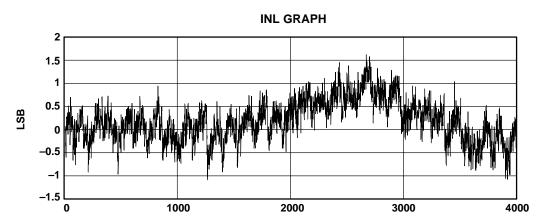

INL: <±1.5 LSB Typical at 0-dB Gain</li>

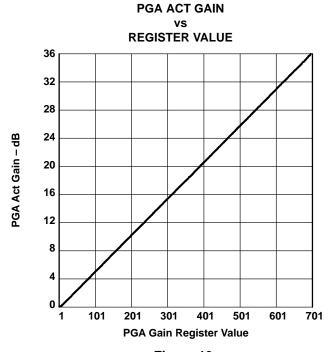

Programmable-Gain Range: 0 dB to 36 dB, Gain Resolution of 0.05 dB/Step

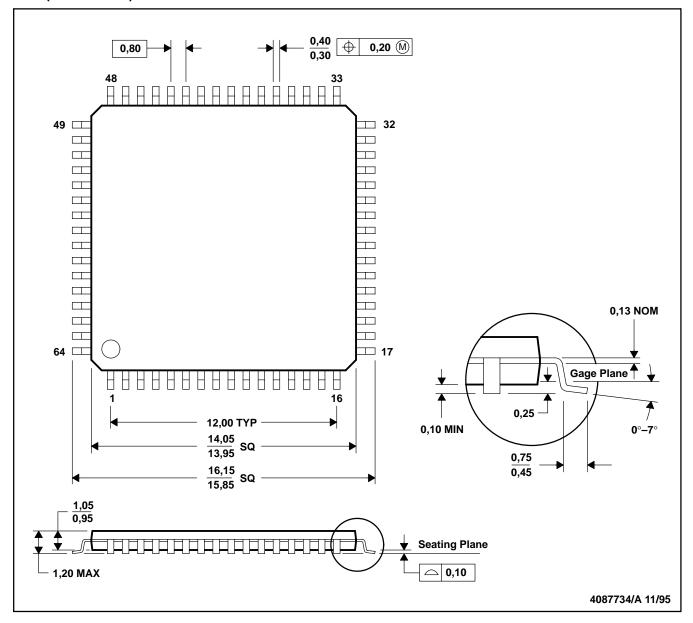

• 48-Pin TQFP Package

## applications

Digital Still Camera, Digital Video Camera

### description

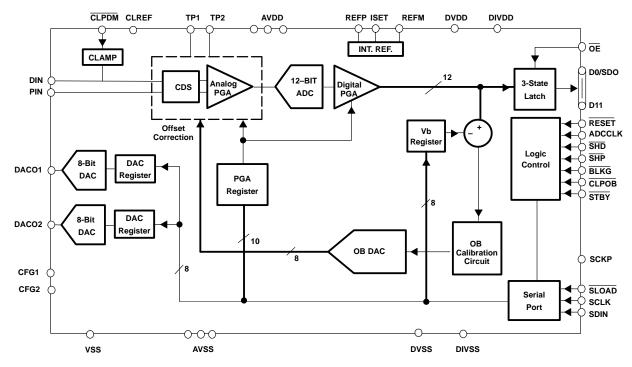

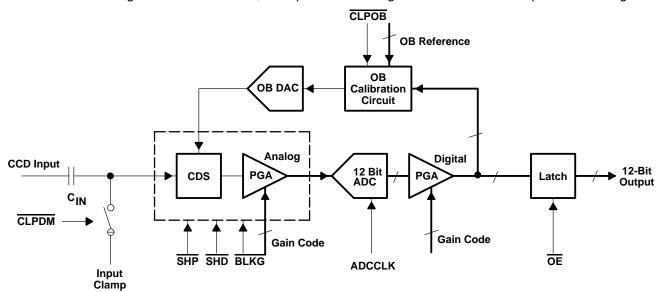

The VSP1221 is a highly-integrated mixed-signal IC used for signal conditioning and analog-to-digital conversion at the output of a CCD array. The IC has a correlated double sampler (CDS) and an analog programmable-gain amplifier (PGA) stage followed by an analog-to-digital converter (ADC) and a digital PGA stage. The CDS is used to sample the CCD signal and is followed by the analog PGA stage. The ADC is a12-bit, 21-MSPS pipelined ADC. The digital PGA provides further amplification.

Additionally, there is an offset calibration loop for optical-black correction. The optical-black reference level is user-programmable. The chip also has two eight-bit digital-to-analog converters (DAC) for external analog setting.

The chip has a serial port for configuring internal control registers.

The VSP1221 is available in a 48-pin TQFP package and operates from a single 3-V power supply.

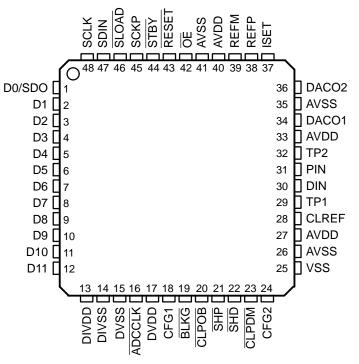

## pin assignments

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **Terminal Functions**

| TERM   | IINAI         | T   |                                                                                                                                           |  |  |  |  |

|--------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME   | PIN           |     |                                                                                                                                           |  |  |  |  |

| D0     | 1             | DO  | D0 = Bit 0 ADC output, least-significant bit (LSB)                                                                                        |  |  |  |  |

| SDO    | ·             |     | SDO = Serial data output (used for register read back)                                                                                    |  |  |  |  |

| D1     | 2             | DO  | Bit 1 ADC output                                                                                                                          |  |  |  |  |

| D2     | 3             | DO  | Bit 2 ADC output                                                                                                                          |  |  |  |  |

| D3     | 4             | DO  | Bit 3 ADC output                                                                                                                          |  |  |  |  |

| D4     | 5             | DO  | Bit 4 ADC output                                                                                                                          |  |  |  |  |

| D5     | 6             | DO  | Bit 5 ADC output                                                                                                                          |  |  |  |  |

| D6     | 7             | DO  | Bit 6 ADC output                                                                                                                          |  |  |  |  |

| D7     | 8             | DO  | Bit 7 ADC output                                                                                                                          |  |  |  |  |

| D8     | 9             | DO  | Bit 8 ADC output                                                                                                                          |  |  |  |  |

| D9     | 10            | DO  | Bit 9 ADC output                                                                                                                          |  |  |  |  |

| D10    | 11            | DO  | Bit 10 ADC output                                                                                                                         |  |  |  |  |

| D11    | 12            | DO  | Bit 11 ADC output, most-significant bit (MSB)                                                                                             |  |  |  |  |

| DIVDD  | 13            | Р   | Power supply for digital I/O                                                                                                              |  |  |  |  |

| DIVSS  | 14            | Р   | Digital ground for digital I/O                                                                                                            |  |  |  |  |

| DVSS   | 15            | Р   | Digital ground                                                                                                                            |  |  |  |  |

| ADCCLK | 16            | DI  | ADC clock                                                                                                                                 |  |  |  |  |

| DVDD   | 17            | Р   | Digital power supply                                                                                                                      |  |  |  |  |

| CFG1   | 18            | DI  | Configuration pin1                                                                                                                        |  |  |  |  |

| BLKG   | 19            | DI  | Blanking pulse:  High = Normal operation  Low = Digital output as programmed in the blanking register (see the blanking register section) |  |  |  |  |

| CLPOB  | 20            | DI  | Optical-black clamping pulse (default = active low)                                                                                       |  |  |  |  |

| SHP    | 21            | DI  | CDS reference sampling pulse (default = active low)                                                                                       |  |  |  |  |

| SHD    | 22            | DI  | CDS data sampling pulse (default = active low)                                                                                            |  |  |  |  |

| CLPDM  | 23            | DI  | Dummy clamping pulse (default = active low)                                                                                               |  |  |  |  |

| CFG2   | 24            | DI  | Configuration pin 2                                                                                                                       |  |  |  |  |

| VSS    | 25            | Р   | Substrate ground                                                                                                                          |  |  |  |  |

| AVSS   | 26, 35,<br>41 | Р   | Analog ground                                                                                                                             |  |  |  |  |

| AVDD   | 27, 33,<br>40 | Р   | Analog power supply                                                                                                                       |  |  |  |  |

| CLREF  | 28            | AO  | External decoupling for clamp voltage                                                                                                     |  |  |  |  |

| TP1    | 29            | AIO | Test point                                                                                                                                |  |  |  |  |

| DIN    | 30            | Al  | CCD signal input                                                                                                                          |  |  |  |  |

| PIN    | 31            | Al  | Input ground                                                                                                                              |  |  |  |  |

| TP2    | 32            | AIO | Test point                                                                                                                                |  |  |  |  |

| DAC01  | 34            | AO  | General-purpose eight-bit DAC output voltage                                                                                              |  |  |  |  |

| DAC02  | 36            | A0  | General-purpose eight-bit DAC output voltage                                                                                              |  |  |  |  |

| ISET   | 37            | AO  | Internal bias-current setting                                                                                                             |  |  |  |  |

NOTE: P: Power Supply, AI: Analog input, AO: Analog output, AIO: Analog input/output, DI: Digital input, DO: Digital output

# **Terminal Functions (Continued)**

| TERMINAL |     |      | DECODINE                                                                                                                                                            |

|----------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | PIN | TYPE | DESCRIPTION                                                                                                                                                         |

| REFP     | 38  | AO   | External decoupling for internal positive reference                                                                                                                 |

| REFM     | 39  | AO   | External decoupling for internal negative reference                                                                                                                 |

| ŌĒ       | 42  | DI   | Output data enable: High = Normal operation Low = Digital output high-impedance state                                                                               |

| RESET    | 43  | DI   | Hardware reset (active low)                                                                                                                                         |

| STBY     | 44  | DI   | Hardware power down (active low)                                                                                                                                    |

| SCKP     | 45  | DI   | SCKP – Serial clock polarity:  High = Sample serial data on rising edge of serial clock (pin 48)  Low = Sample serial data on falling edge of serial clock (pin 48) |

| SLOAD    | 46  | DI   | Serial data latch                                                                                                                                                   |

| SDIN     | 47  | DI   | Serial data input                                                                                                                                                   |

| SCLK     | 48  | DI   | Serial clock input                                                                                                                                                  |

NOTE: P: Power supply, AI: Analog input, AO: Analog output, AIO: Analog input/output, DI: Digital input, DO: Digital output

# functional block diagram

Figure 1. Internal Block Diagram of the VSP1221

DATE AND TRACKING INFORMATION

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage, AV <sub>DD</sub> , DV <sub>DD</sub> , DIV <sub>DD</sub> | 0.3 V to 6.5 V        |

|-------------------------------------------------------------------------|-----------------------|

| Analog input voltage                                                    | 0.3 V to AVDD + 0.3 V |

| Digital input voltage                                                   | 0.3 V to DVDD + 0.3 V |

| Junction temperature, T <sub>J</sub>                                    | 0°C to 150°C          |

| Storage temperature, T <sub>sta</sub>                                   |                       |

| Storage temperature, T <sub>stg</sub>                                   | 260°C                 |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## electrical characteristics

#### general specifications

All typical specifications are at  $T_A = 25^{\circ}C$ , all power supply voltages = 3 V, and conversion rate = 21 MHz, unless otherwise stated. All maximum specifications are assured across operating temperature and voltage ranges.

|                   | PARAMETERS                          | TEST CONDITIONS                                  | MIN      | TYP  | MAX      | UNIT   |

|-------------------|-------------------------------------|--------------------------------------------------|----------|------|----------|--------|

| Power S           | Supply                              | •                                                |          |      |          |        |

| $AV_{DD}$         | Analog supply voltage               |                                                  | 2.7      | 3.0  | 3.3      |        |

| $DV_{DD}$         | Digital supply voltage              |                                                  | 2.7      | 3.0  | 3.3      | V      |

| $DIV_{DD}$        | Digital I/O supply voltage          |                                                  | 1.8      |      | 3.3      |        |

| $AV_{DD}$         |                                     |                                                  | 20       | 24   | 29       |        |

| $DV_DD$           | Operating current                   |                                                  | 2        | 4    | 6        | mA     |

| DIV <sub>DD</sub> |                                     |                                                  | 0.5      | 1    | 4        |        |

|                   | B                                   | Normal mode                                      | 80       | 90   | 100      | 347    |

|                   | Power dissipation                   | Power-down mode                                  | 1        | 2    | 4        | mW     |

| Referen           | ice                                 | •                                                |          |      |          |        |

|                   | Positive reference voltage          | 1 μF to ground (pin 38)                          | 1.95     | 2.05 | 2.2      | V      |

|                   | Negative reference voltage          | 1 μF to ground (pin 39)                          | 0.7      | 0.75 | 0.9      | V      |

|                   | External bandgap voltage reference  | 100 kΩ to ground (pin 37)                        |          | 1.00 |          | V      |

|                   | Bandgap temperature coefficient     |                                                  |          | 100  |          | PPM/°C |

| Tempera           | ature Range                         | •                                                |          |      |          |        |

| T <sub>A</sub>    | Operating temperature               |                                                  | -20      |      | 75       | °C     |

| Digital I         | nput                                | •                                                | •        |      |          |        |

| VIH               | Logic-high input voltage            |                                                  | 0.8DIVDD |      |          | .,     |

| $\vee_{IL}$       | Logic-low input voltage             |                                                  |          |      | 0.2DIVDD | V      |

| lн                | Logic-high input current            | DIV <sub>DD</sub> = 3 V                          | -10      |      | 10       |        |

| I <sub>IL</sub>   | Logic-low input current             | DIV <sub>DD</sub> = 3 V                          | -10      |      | 10       | μΑ     |

| Cl                | Input capacitance                   |                                                  |          | 5    |          | pF     |

| Digital C         | Output                              | •                                                | •        |      |          | •      |

| Vон               | Logic-high output voltage           | I <sub>OH</sub> = 50 μA, DIV <sub>DD</sub> = 3 V | 0.8DIVDD |      |          |        |

| VOL               | Logic-low output voltage            | I <sub>OL</sub> = 50 μA, DIV <sub>DD</sub> = 3 V |          |      | 0.2DIVDD | V      |

| loz               | High-impedance-state output current |                                                  | -10      |      | 10       | μΑ     |

| CO                | Output capacitance                  | CO                                               |          | 5    | 15       | pF     |

# electrical characteristics (continued)

# device specifications

All typical specifications are at  $T_A = 25$ °C, all power supply voltages = 3 V, and conversion rate = 21 MHz. unless otherwise stated. All maximum specifications are assured across operating temperature and voltage ranges.

| PARAMETERS                               | TEST CONDITIONS                                            | MIN   | TYP            | MAX     | UNIT   |

|------------------------------------------|------------------------------------------------------------|-------|----------------|---------|--------|

| Full Channel                             |                                                            |       |                |         |        |

| Input signal level for full-scale output | Single ended, gain= 0 dB                                   |       | 1000           |         | mV     |

| Input capacitance                        |                                                            |       | 8              |         | pF     |

| Input referred noise                     | Gain = 0 dB                                                |       | 130            | 360     | μV     |

| Integral nonlinearity                    | Gain = 0 dB                                                | ±1.5  | ±2             | ±5      | LSB    |

| Differential nonlinearity                | Gain = 0 dB                                                | ±0.5  | ±0.75          | +1.5/–1 | LSB    |

| Data latency                             |                                                            |       | 10             |         | Clocks |

| Conversion rate                          |                                                            |       |                | 21      | MHz    |

| PGA                                      |                                                            |       |                |         |        |

| Gain control code                        |                                                            |       | 10             |         | Bits   |

| Maximum gain                             | Gain code = 1011010000 (720 Decimal)                       |       | 36             |         | dB     |

| Minimum gain                             | Gain code = 0000000000                                     |       | 0              |         | dB     |

| Gain resolution                          |                                                            |       | 0.05           |         | dB     |

| Integral nonlinearity                    |                                                            | ±0.02 | ±0.05          | ±0.4    | dB     |

| Differential nonlinearity                |                                                            | ±0.02 | ±0.05          | ±0.3    | dB     |

| Analog-to-Digital Converter (ADC)        |                                                            | •     |                |         |        |

| Resolution                               |                                                            |       | 12             |         | Bits   |

| Conversion rate                          |                                                            |       |                | 21      | MHz    |

| No missing codes                         |                                                            |       |                |         |        |

| Integral nonlinearity                    |                                                            |       | ±1             |         | LSB    |

| Differential nonlinearity                |                                                            |       | ±0.50          |         | LSB    |

| Data latency                             |                                                            |       | 3.5<br>(fixed) |         | Clocks |

| General-Purpose Digital-to-Analog C      | onverter (DAC)                                             |       |                |         | L      |

| Resolution                               |                                                            |       | 8              |         | Bits   |

| Integral nonlinearity                    |                                                            |       | ±0.1           | ±1      | LSB    |

| Differential nonlinearity                |                                                            |       | ±0.1           | ±1      | LSB    |

| Output voltage range                     |                                                            | 0     |                | AVDD    | V      |

| Output settling time                     | 10-pF external load. Settle to 1 mV                        |       | 4              |         | μs     |

| Serial Interface                         |                                                            |       |                |         | L      |

| Clock frequency                          | DIV <sub>DD</sub> = 3 V                                    |       |                | 40      | MHz    |

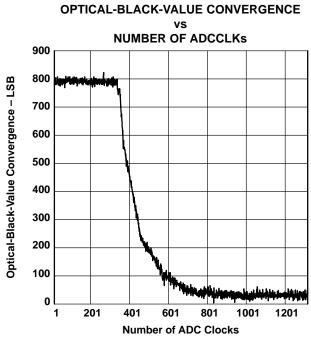

| Optical-Black Calibration                |                                                            | •     |                |         |        |

| Maximum correctable CCD black level      |                                                            |       |                | 100     | mV     |

| Convergence time                         | Black level = 100 mV, gain = 12 dB, OB reference level = 0 | 440   |                | 550     | Clocks |

|                                          | Gain = 0-20dB                                              |       | ±1             | ±2      |        |

|                                          | Gain = 20–26 dB                                            |       | ±1             | ±4      |        |

| Calibration error                        | Gain = 26–32 dB                                            |       | ±2             | ±4      | LSB    |

|                                          | Gain = 32–36 dB                                            |       | ±4             | ±8      |        |

# timing requirements

DATE AND TRACKING INFORMATION

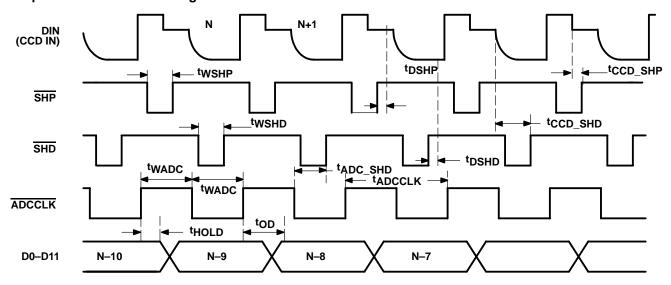

## sample and conversion timing

|                     | PARAMETERS                          | MIN | TYP  | MAX | UNIT |  |  |

|---------------------|-------------------------------------|-----|------|-----|------|--|--|

| <sup>t</sup> ADCCLK | ADC clock period                    | 46  |      |     | ns   |  |  |

| tWADC               | ADC high or low width               | 23  |      |     | ns   |  |  |

| tWSHP               | SHP pulse width                     |     |      | ns  |      |  |  |

| tWSHD               | SHD pulse width                     | 5   |      |     |      |  |  |

| tCCE_SHP            | CCD reset start to SHP rising edge  | S   |      |     |      |  |  |

| tCCD_SHD            | CCD data start to SHD rising edge   | S   |      |     |      |  |  |

| tADC_SHD            | ADC falling edge to SHD rising edge | 15  |      | 35  | ns   |  |  |

| <sup>t</sup> DSHP   | Sampling delay, reset               | 1.0 | 1.75 | 3.0 | ns   |  |  |

| <sup>t</sup> DSHD   | Sampling delay, data                | 4.0 | 5.0  | 7.0 | ns   |  |  |

| tHOLD               | Output hold time                    | 4   |      |     | ns   |  |  |

| t <sub>OD</sub>     | Output delay                        | 4   |      | 15  | ns   |  |  |

NOTES: 1. Best performance if t<sub>CCD\_SHP</sub> > 15 ns

Good performance if 10 ns < t<sub>CCD\_SHP</sub> < 15 ns

Poor performance if t<sub>CCD\_SHP</sub> < 10 ns

Best performance if tCCD\_SHD > 19 ns

Good performance if 10 ns < tCCD\_SHD < 19 ns

Poor performance if  $t_{CCD\_SHD} < \overline{15}$  ns

Figure 2. Sample and Conversion Timing

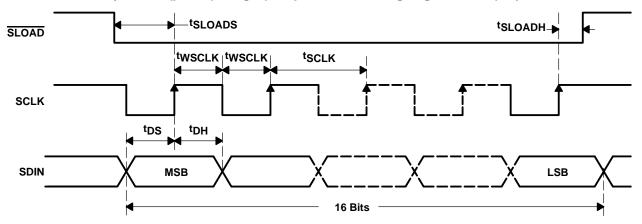

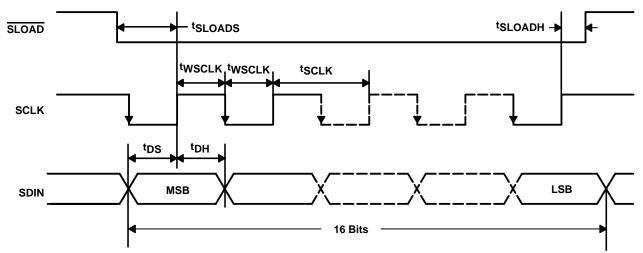

## serial interface timing

standard functionality, SCKP (pin 45) = high (sample data on rising edge of SCLK), operation = write

Figure 3. Serial Interface Timing for Write, SCKP = High

standard functionality, SCKP (pin 45) = low (sample data on falling edge of SCLK), operation = write

|                     | PARAMETERS               | MIN  | TYP | MAX | UNIT |

|---------------------|--------------------------|------|-----|-----|------|

| tSCLK               | SCLK period              | 25   |     |     | ns   |

| tWSCLK              | SCLK high or low width   | 12.5 |     |     | ns   |

| tSLOADS             | SLOAD to SCLK setup time | 5    |     |     | ns   |

| <sup>t</sup> SLOADH | SCLK to SLOAD hold time  | 2    |     |     | ns   |

| t <sub>DS</sub>     | Data setup time          | 5    |     |     | ns   |

| t <sub>DH</sub>     | Data hold time           | 2    |     |     | ns   |

NOTE: Serial data is in MSB first order.

For write operation, MSB = 0 (see the serial data format section)

Figure 4. Serial Interface Timing for Write, SCKP = Low

DATE AND TRACKING INFORMATION

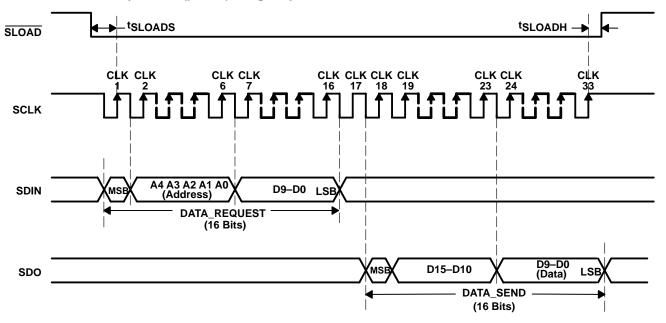

#### serial interface timing (continued)

standard functionality, SCKP (pin 45) = high, operation = read

Figure 5. Serial Interface Timing for Read, SCKP = High

Device register values can be read back serially from the SDO pin (pin 1). For serial data read, user first sends a 16 bit DATA\_REQUEST on the SDIN pin (pin 47). The format is as follows:

#### **DATA\_REQUEST on SDIN**

| SD15 | SD14-SD10                 | SD9-SD0    |  |  |

|------|---------------------------|------------|--|--|

| 1    | Required register address | Don't Care |  |  |

Although the length of DATA\_REQUEST is 16 bits, the ten LSBs are don't cares. Also, note that SD15 (RD/WR) should be 1 for register read (see the *serial data format* section). The register address portion of DATA\_REQUEST is decoded and the register data value (DATA\_SEND) is available on the SDO pin at the rising edge of CLK18 (see Figure 5) if SLOAD is low at that time. If SLOAD is high at that time, then DATA\_SEND is available when SLOAD goes low again. The format of DATA\_SEND is as follows:

#### DATA\_SEND on SDO

| SD15-SD10  | SD9-SD0                   |

|------------|---------------------------|

| Don't Care | Required register address |

Although the length of DATA SEND is 16 bits, the six MSBs are don't cares.

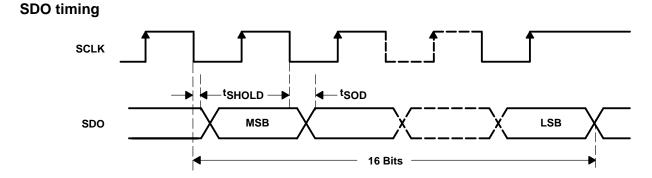

|        | PARAMETERS            | MIN | TYP | MAX | UNIT |

|--------|-----------------------|-----|-----|-----|------|

| tSHOLD | Data output hold time | 5   |     |     | ns   |

| tSOD   | Data output delay     |     |     | 13  | ns   |

NOTE: Data output transition occurs at the falling edge of SCLK; so data should be sampled at the rising edge of SCLK. Since the SDO pin is multiplexed with the D0 pin,  $\overline{\text{OE}}$  (pin 42) should be low.

Figure 6. Serial Interface Timing Between SCLK and SDO

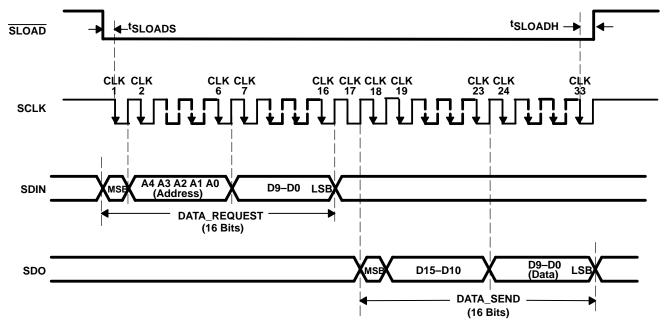

# standard functionality, SCKP (pin 45) = low, operation = read

Figure 7. Serial Interface Timing for Read, SCKP = Low

The SDO timing is the same as before, except that data should be sampled at the falling edge of SCLK.

# DATE AND TRACKING INFORMATION

## serial data format

## standard functionality

The serial data is always grouped in 16-bit blocks with the following format. Multiple 16-bit blocks can be send through the SDIN pin (pin 47) keeping SLOAD (pin 46) low.

| SD15<br>MSB | SD14                  | SD13 | SD12 | SD11 | SD10 | SD9               | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0<br>LSB |

|-------------|-----------------------|------|------|------|------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|------------|

| RD/WR       | A4                    | А3   | A2   | A1   | A0   | D9                | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0         |

|             | ←—Register Address——→ |      |      |      |      | ← Register Data → |     |     |     |     |     |     |     |     |            |

$RD/\overline{WR} = 0$ , Write into registers  $RD/\overline{WR} = 1$ , Read from registers

## register description (see Note 3)

|    | REGIS | TER ADI | DRESS |    | DEGIGTED MANE            |                               |  |  |  |  |

|----|-------|---------|-------|----|--------------------------|-------------------------------|--|--|--|--|

| A4 | А3    | A2      | A1    | Α0 | REGISTER NAME            | REGISTER FUNCTION             |  |  |  |  |

| 0  | 0     | 0       | 0     | 0  | Control register         | Mode control                  |  |  |  |  |

| 0  | 0     | 0       | 0     | 1  | PGA register             | Gain control                  |  |  |  |  |

| 0  | 0     | 0       | 1     | 0  | User DAC1 register       | User DAC1 control             |  |  |  |  |

| 0  | 0     | 0       | 1     | 1  | User DAC2 register       | User DAC2 control             |  |  |  |  |

| 0  | 0     | 1       | 0     | 0  | Reserved                 | Reserved                      |  |  |  |  |

| 0  | 0     | 1       | 0     | 1  | Reserved                 | Reserved                      |  |  |  |  |

| 0  | 0     | 1       | 1     | 0  | OB register              | OB level control              |  |  |  |  |

| 0  | 0     | 1       | 1     | 1  | Blanking register        | Blanking output control       |  |  |  |  |

| 0  | 1     | 0       | 0     | 0  | Signal polarity register | Clock signal polarity control |  |  |  |  |

| 0  | 1     | 0       | 0     | 1  | Timing register 1        | ADCCLK                        |  |  |  |  |

| 0  | 1     | 0       | 1     | 0  | Timing register 2        | SHP                           |  |  |  |  |

NOTE 3: The register values are updated as soon as the register is written. It may take 0 to 9 ADCCLK cycles for it to have effect on the device.

# control register

| SD15<br>MSB | SD14        | SD13 | SD12    | SD11 | SD10 | SD9         | SD8      | SD7 | SD6           | SD5   | SD4    | SD3 | SD2           | SD1           | SD0<br>LSB |

|-------------|-------------|------|---------|------|------|-------------|----------|-----|---------------|-------|--------|-----|---------------|---------------|------------|

| RD/WR       | 0           | 0    | 0       | 0    | 0    | STBYZ       | CLAMPPIN | ОВ  | RE-<br>SERVED | RI    | ESERVE | D   | RE-<br>SERVED | RE-<br>SERVED | RTSY       |

|             | <del></del> |      | Address |      |      | <del></del> |          |     |               | —Data | a      |     |               |               |            |

| BIT     | NAME                  | DEFAULT VALUE | DESCRIPTION                                                                                                                                                     |

|---------|-----------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD0     | RTSY                  | 0             | RTSY=0, no change<br>RTSY=1, reset all register bits to their default settings                                                                                  |

| SD1     | RESERVED              | 0             | Reserved                                                                                                                                                        |

| SD2     | RESERVED              | 0             | Reserved                                                                                                                                                        |

| SD3-SD5 | RESERVED              | All 0         | Reserved                                                                                                                                                        |

| SD6     | RESERVED              | Х             | Reserved                                                                                                                                                        |

| SD7     | ОВ                    | 1             | OB=0, optical-black calibration disable <sup>†</sup> OB=1, optical-black calibration enable                                                                     |

| SD8     | CLAMPPIN <sup>‡</sup> | 1             | CLAMPPIN=1, disable clamping on PIN (pin 31), connect PIN directly to ground. CLAMPPIN=0, enable clamping on PIN (pin 31), connect PIN to ground via capacitor. |

| SD9     | STBYZ                 | 1             | STBYZ=0, device in power-down mode (software power down) STBYZ=1, no change                                                                                     |

<sup>†</sup> Under this condition, previous value of black level remains unchanged. ‡ See the *CCD input* section

# programmable-gain amplifier (PGA) register

| SD15<br>MSB | SD14 | SD13 | SD12    | SD11 | SD10              | SD9      | SD8 | SD7 | SD6 | SD5  | SD4 | SD3 | SD2 | SD1 | SD0<br>LSB    |

|-------------|------|------|---------|------|-------------------|----------|-----|-----|-----|------|-----|-----|-----|-----|---------------|

| RD/WR       | 0    | 0    | 0       | 0    | 1                 | MSB      |     |     |     | GA   | AIN |     |     |     | LSB           |

|             | ←    |      | -Addres | s    | $\longrightarrow$ | <b>←</b> |     |     |     | ——Да | ta  |     |     |     | $\rightarrow$ |

| BIT     | NAME | DEFAULT VALUE |                                                                                | DESCRIPTION          |  |  |  |

|---------|------|---------------|--------------------------------------------------------------------------------|----------------------|--|--|--|

| SD0-DS9 | GAIN | All 0         | Programmable-gai<br>Gain step = 0.05 d<br>Minimum gain = 0<br>Maximum gain = 3 | B<br>dB              |  |  |  |

|         |      |               | Code                                                                           | Gain                 |  |  |  |

|         |      |               | 000000000<br>000000001                                                         | 0 dB<br>0.05 dB      |  |  |  |

|         |      |               |                                                                                |                      |  |  |  |

|         |      |               | 1011001111 35.95 dB                                                            |                      |  |  |  |

|         |      |               | 1011010000<br>Higher codes                                                     | 36.00 dB<br>36.00 dB |  |  |  |

# user DAC1 register

| SD15<br>MSB | SD14     | SD13 | SD12    | SD11 | SD10      | SD9         | SD8  | SD7        | SD6 | SD5 | SD4 | SD3    | SD2 | SD1 | SD0<br>LSB        |

|-------------|----------|------|---------|------|-----------|-------------|------|------------|-----|-----|-----|--------|-----|-----|-------------------|

| RD/WR       | 0        | 0    | 0       | 1    | 0         | Reserved    | PDZ1 | MSB<br>LSB |     |     |     | DACIN1 | 1   |     |                   |

|             | <b>←</b> |      | -Addres | s    | <b></b> → | <del></del> |      |            | D;  | ata |     |        |     |     | $\longrightarrow$ |

| BIT     | NAME     | DEFAULT VALUE | DESCRIPTION                                                            |

|---------|----------|---------------|------------------------------------------------------------------------|

| SD0-DS7 | DACIN1   | All 0         | Eight-bit digital input to DAC1                                        |

| SD8     | PDZ1     | 0             | PDZ1 = 0, DAC1 in power-down mode<br>PDZ1 = 1, DAC1 in functional mode |

| SD9     | Reserved | 0             | Reserved                                                               |

# user DAC2 register

| SD15<br>MSB | SD14 | SD13 | SD12    | SD11 | SD10 | SD9         | SD8  | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0<br>LSB        |

|-------------|------|------|---------|------|------|-------------|------|-----|-----|-----|-----|-----|-----|-----|-------------------|

| RD/WR       | 0    | 0    | 0       | 1    | 1    | Reserved    | PDZ2 | MSB |     |     | DAC | IN2 |     |     | LSB               |

|             | ←    |      | -Addres | s    |      | <del></del> |      |     | D   | ata |     |     |     |     | $\longrightarrow$ |

| BIT     | NAME     | DEFAULT VALUE | DESCRIPTION                                                            |

|---------|----------|---------------|------------------------------------------------------------------------|

| SD0-DS7 | DACIN2   | All 0         | Eight-bit digital input to DAC2                                        |

| SD8     | PDZ2     | 0             | PDZ1 = 0, DAC2 in power-down mode<br>PDZ1 = 1, DAC2 in functional mode |

| SD9     | Reserved | 0             | Reserved                                                               |

# **OB** register

| SD15<br>MSB | SD14        | SD13 | SD12    | SD11 | SD10              | SD9         | SD8  | SD7 | SD6 | SD5   | SD4  | SD3 | SD2 | SD1 | SD0<br>LSB        |

|-------------|-------------|------|---------|------|-------------------|-------------|------|-----|-----|-------|------|-----|-----|-----|-------------------|

| RD/WR       | 0           | 0    | 1       | 1    | 0                 | Rese        | rved | MSB |     |       | OBLE | VEL |     |     | LSB               |

|             | <del></del> |      | -Addres | s    | $\longrightarrow$ | <del></del> |      |     |     | —Data |      |     |     |     | $\longrightarrow$ |

| BIT     | NAME     | DEFAULT VALUE          |                      |        |            | DESCRIPTION | N |  |

|---------|----------|------------------------|----------------------|--------|------------|-------------|---|--|

| SD0-DS9 | OBLEVEL  | 01000000J (64<br>LSBs) | OB reference leve    | el     |            |             |   |  |

|         |          |                        | Code                 | OB I   | _evel      |             |   |  |

|         |          |                        | 00000000<br>00000001 | 0<br>1 | LSB<br>LSB |             |   |  |

|         |          |                        | 11111111             |        | LSBs       |             |   |  |

| SD8-SD9 | Reserved | All 0                  | Reserved             |        |            |             |   |  |

# blanking register

| SD15<br>MSB | SD14        | SD13 | SD12    | SD11 | SD10              | SD9         | SD8 | SD7 | SD6 | SD5  | SD4    | SD3 | SD2 | SD1 | SD0<br>LSB        |

|-------------|-------------|------|---------|------|-------------------|-------------|-----|-----|-----|------|--------|-----|-----|-----|-------------------|

| RD/WR       | 0           | 0    | 1       | 1    | 1                 | MSB         |     |     |     | В    | BLKGVA | L   |     |     | LSB               |

|             | <del></del> |      | -Addres | s    | $\longrightarrow$ | <del></del> |     |     |     | Data | 1      |     |     |     | $\longrightarrow$ |

| BIT     | NAME     | DEFAULT VALUE |                          | DESCRIPTION                              |

|---------|----------|---------------|--------------------------|------------------------------------------|

| SD0-DS9 | BLKGVAL  | All 0         | Output data whe          | n BLKG (pin 19) is low                   |

|         |          |               | Code                     | Output data (blanking level)             |

|         |          |               | 0000000000<br>0000000001 | 0 LSB<br>1 LSB<br>1022 LSBs<br>1023 LSBs |

| SD8-SD9 | Reserved | All 0         | Reserved                 |                                          |

# signal polarity register (see Note 4)

| SD15<br>MSB | SD14        | SD13 | SD12 | SD11 | SD10 | SD9      | SD8 | SD7 | SD6 | SD5 | SD4  | SD3  | SD2 | SD1 | SD0<br>LSB |

|-------------|-------------|------|------|------|------|----------|-----|-----|-----|-----|------|------|-----|-----|------------|

| RD/WR       | 0           | 1    | 0    | 0    | 0    | Reserved |     |     |     |     | SPDZ | ADCZ | OBZ | BLZ | CLZ        |

|             | ← Address → |      |      |      |      | ←Data    |     |     |     |     |      |      |     |     |            |

| BIT     | NAME     | DEFAULT VALUE | DESCRIPTION                                                                                                                                      |

|---------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| SD0     | CLZ      | 0             | $CLZ = 0$ , $\overline{CLPDM}$ (pin 23) = active low $CLZ = 1$ , $\overline{CLPDM}$ (pin 23) = active high                                       |

| SD1     | BLZ      | 0             | $BLZ = 0$ , $\overline{BLKG}$ (pin 19) = active low $BLZ = 1$ , $\overline{BLKG}$ (pin 19) = active high                                         |

| SD2     | OBZ      | 0             | OBZ = 0, CLPOB (pin 20) = active low OBZ = 1, CLPOB (pin 20) = active high                                                                       |

| SD3     | ADCZ     | 0             | ADCZ = 0, ADCCLK (pin 16) = active low<br>ADCZ = 1, ADCCLK (pin 16) = active high                                                                |

| SD4     | SPDZ     | 0             | SPDZ = 0, <u>SHP</u> (pin 21) = active low, <u>SHD</u> (pin 22) = active low<br>SPDZ = 1, SHP (pin 21) = active high, SHD (pin 22) = active high |

| SD5-SD9 | Reserved | All 0         | Reserved                                                                                                                                         |

NOTE 4: For this register to take effect, bit SD4 of timing register 1 must be 0.

DATE AND TRACKING INFORMATION

# timing register 1

| SD15<br>MSB | SD14        | SD13 | SD12 | SD11 | SD10 | SD9   | SD8 | SD7 | SD6  | SD5 | SD4  | SD3  | SD2 | SD1 | SD0<br>LSB |

|-------------|-------------|------|------|------|------|-------|-----|-----|------|-----|------|------|-----|-----|------------|

| RD/WR       | 0           | 1    | 0    | 0    | 1    |       | Re  |     | BYPZ | MSB | ADCD | ELAY | LSB |     |            |

|             | ← Address → |      |      |      |      | ←Data |     |     |      |     |      |      |     |     |            |

| BIT     | NAME     | DEFAULT VALUE | DESCRIPTION                                                                                                                   |  |  |  |  |  |  |

|---------|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SD0-SD3 | ADCDELAY | All 0         | Delay ADC clock by programmed value Delay step = 0.8 ns                                                                       |  |  |  |  |  |  |

|         |          |               | Code Delay                                                                                                                    |  |  |  |  |  |  |

|         |          |               | 0000 0<br>0001 0.8 ns<br>                                                                                                     |  |  |  |  |  |  |

| SD4     | BYPZ     | 1             | BYPZ = 0, signal polarity and programmable delay enable (see Note 5) BYPZ = 1, signal polarity and programmable delay disable |  |  |  |  |  |  |

| SD5-SD9 | Reserved | All 0         | Reserved                                                                                                                      |  |  |  |  |  |  |

NOTE 5: When BYPZ = 0, the internal delays of SHP and SHD will increase approximately by 3 ns

# timing register 2 (see Note 6)

| SD15<br>MSB | SD14        | SD13 | SD12 | SD11 | SD10 | SD9      | SD8 | SD7 | SD6          | SD5 | SD4 | SD3 | SD2         | SD1 | SD0<br>LSB |

|-------------|-------------|------|------|------|------|----------|-----|-----|--------------|-----|-----|-----|-------------|-----|------------|

| RD/WR       | 0           | 1    | 0    | 1    | 0    | Reserved |     | MSB | SHDDELAY LSB |     | LSB | MSB | SB SHPDELAY |     | LSB        |

|             | ← Address → |      |      |      |      | ←Data    |     |     |              |     |     |     |             |     |            |

| BIT     | NAME     | DEFAULT VALUE | DESCRIPTION                                                |

|---------|----------|---------------|------------------------------------------------------------|

| SD0-SD3 | SHPDELAY | All 0         | Delay SHP clock by programmed value Delay step = 0.8 ns    |

|         |          |               | Code Delay                                                 |

|         |          |               | 0000 0<br>0001 0.8 ns<br>1110 11.2 ns<br>1111 12.0 ns      |

| SD4-SD7 | SHDDELAY | All 0         | Delay SHD clock by programmed value<br>Delay step = 0.8 ns |

|         |          |               | Code Delay                                                 |

|         |          |               | 0000 0<br>0001 0.8 ns                                      |

|         |          |               | 1110 11.2 ns<br>1111 12.0 ns                               |

| SD8-SD9 | Reserved | All 0         | Reserved                                                   |

NOTE 6: For this register to take effect, bit SD4 of timing register 1 must be 0 (see the timing register 1 section.

#### PRINCIPLES OF OPERATION

#### introduction

The principle functions of the VSP1221 are described below. The sections discussed are:

- CDS

- ADC

- PGA

- Voltage and current reference

- Serial interface

- Timing

- SHP, SHD AND ADCCLK

- CLPDM

- BLKG

- CLPOB

- <del>OE</del>

- RESET

- Optical-black calibration

- Standby mode

- General-purpose DAC

Before describing the individual blocks, a simplified block diagram of the VSP1221 is presented in Figure 8.

Figure 8. Simplified Block Diagram of the VSP1221

#### PRINCIPLES OF OPERATION

#### **CDS**

The output signal from the CCD is fed to the correlated double sampler (CDS) through off-chip coupling capacitor  $C_{in}$  (a 0.22- $\mu F$  capacitor is recommended for  $C_{in}$ ). The CCD signal is sampled twice during one pixel period: at the reference level ( $\overline{SHP}$ ) and at the data level ( $\overline{SHD}$ ). Subtracting these two samples extracts the pixel value and reduces the reset noise and other low-frequency noises that are present at the output of the CCD signal.

#### **ADC**

The output analog signal from the analog PGA stage is passed to the 12-bit analog-to-digital converter (ADC). The ADC employs a three-stage pipelined architecture to achieve high-throughput and low-power consumption. Fully-differential implementation and digital-error correction ensures 12-bit resolution.

#### **PGA**

VSP1221 has a programmable gain amplifier (PGA) which is composed of analog and digital stages. The total gain range is 0 dB–36 dB in 0.05-dB steps. The gain can be adjusted by programming the PGA register through the serial port, see the *programmable gain amplifier (PGA) register* section.

#### voltage reference

All the reference voltages and the bias currents used by the device are created by an internal bandgap circuit. Connecting an external 100-k $\Omega$  resistor from ISET (pin 37) to ground provides the bias current. The voltage at the ISET pin is 1 V and the reference current is 10  $\mu$ A (1 V/100 k $\Omega$ ). The reference voltages for the ADC are REFP (2.05 V) and REFM (0.75 V). They are available on pins 38 and 39, respectively. The full-scale range of the ADC is twice the difference between REFP and REFM. Pins REFP and REFM should be heavily decoupled with appropriate capacitors (1  $\mu$ F recommended).

#### serial interface

#### standard functionality

A simple three-wire (SCLK, SDIN, and \$\overline{SLOAD}\$) serial interface is provided to allow writing/reading the internal registers of the VSP1221. The serial data SDIN (pin 47) is 16 bits long. The MSB (most significant bit) is set to 0 for writing to and to 1 for reading from the internal registers. Following this, there are five address bits for accessing and ten data bits for writing to the particular registers. During a read operation, data from the particular register is available on SDO (pin 1). To enable serial read/write, \$\overline{SLOAD}\$ (pin 46) should be pulled low. Sending blocks of 16-bit data to SDIN can program multiple registers. The polarity of the serial clock (SCLK, pin 48) can be controlled by SCKP (pin 45). For serial interface timing see the *serial data format* section; for serial data format and description of the internal registers see the *register description* section.

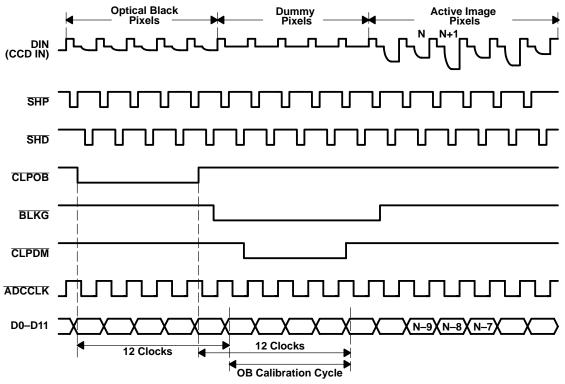

### timing

A description of the different timing signals of the VSP1221 follows. The timing diagram in *sample and conversion timing* section has additional information. Note that the polarity of SHP/SHD, ADCCLK, CLPDM, BLKG, and CLPOB can be programmed to be active low or active high (see the *signal polarity register* section). The timing diagram in the *timing specifications* section is based on active-low polarity.

#### PRINCIPLES OF OPERATION

## SHP, SHD, and ADCCLK

SHP/SHD are used for correlated double sampling of the CCD signal. Sample reference (SHP) is used to sample the reference level of the CCD signal, and sample data (SHD) is used to sample the data level. The ADC clock (ADCCLK) is used to latch the output of the ADC to the external pins. SHP, SHD, and ADCCLK are used to generate internal timing signals using the on-chip timing generator for proper synchronization of different blocks. SHP, SHD, and ADCCLK can be internally delayed by programming the timing registers through the serial port (see the *timing register 1* and *timing register 2* sections.

The following is recommended to get the best performance:

SHP and SHD must first be aligned based on the CCD signal and timing shown in Figure 2 ( $t_{DSHP}$  and  $t_{DSHD}$ ). It is observed that if output data switches at the instant of sampling ( $t_{DSHP}$ ), the device noise performance degrades. The data switches a few ns after the rising edge of ADCCLK ( $t_{OD}$ ). To improve performance, ADCCLK can be varied within the  $t_{ADC}$  SHD range.

#### **CLPDM**

The CCD signal is capacitively coupled to the VSP1221 because the dc level of the CCD signal is usually too high and might damage the chip. The purpose of the  $\overline{\text{CLPDM}}$  signal is to clamp the ac-coupling capacitor  $C_{in}$  to establish the proper dc bias for the CDS. The dc bias for the CDS is set to the clamp voltage, which is around 800 mV below the supply voltage. The clamp voltage can be decoupled with an external capacitor at CLREF (pin 28). This helps in charging the ac-coupling capacitor  $C_{in}$  faster, since the charge will be provided by the decoupling capacitor. Recommended value for the decoupling capacitor is 1  $\mu$ F. The dummy pixel clamp  $(\overline{\text{CLPDM}})$  signal is usually available during the dummy pixels of the CCD and is applied at the line rate of the CCD sensor.

#### BLK

Some CCDs have large transient output signals during blanking intervals. Such signals might drive the VSP1221 into saturation and can cause long recovery times. To prevent this, the VSP1221 has an input-blanking function which disconnects the CCD input from the CDS when it receives the blanking (BLKG) signal. Additionally, the output from the VSP1221 during blanking will be equal to the value programmed in the blanking register. The blanking level can be adjusted by programming the blanking register through the serial port (see the *blanking register* section).

#### **CLPOB**

The optical-black clamp (CLPOB) pulse is used for optical-black calibration (explained in the *optical-black calibration* section). The CLPOB pulse is given to the device during optical-black pixels of the CCD.

#### OE

Output enable  $(\overline{OE})$  is used to latch the output data to the output pins. When  $\overline{OE}$  is low, data is latched to the output pins (D0–D11); when it is high, the output is 3-state.

#### **RESET**

When the reset (RESET) signal is pulled low (hardware reset), all the internal registers are reset to their default values. In addition, The device also has a software-reset option that allows setting the RTSY bit in the control register through the serial port (see the *control register* section). See the *control register* section for the default values of the internal registers. In addition to resetting the registers, hardware reset also resets the output of the OB DAC to zero. However, to exactly reset the OB DAC to zero, RESET must be kept low for approximately 600 ns.

#### PRINCIPLES OF OPERATION

### optical-black calibration

Optical-black calibration (OB) is used to clamp the CCD *black* level to the user-defined OB reference level. In CCDs, thermally generated electrons produce a significant amount of charge even at room temperature. So, even in the absence of light (*black* level), thermal electrons generate a considerable amount of current in CCDs. Thus, the CCD black level will carry a residual signal, also known as the CCD offset, which is typically of the order of 50 mV. This residual signal will reduce the effective dynamic range of the CCD input, resulting in a degradation of image quality. An offset voltage must be subtracted from the CCD black level so that the difference between the CCD black level and the offset voltage is equal to the reference OB level programmed by the user. The reference OB level is much lower than the CCD black level, so that the effective dynamic range of the CCD input increases and the image quality improves. The offset voltage has to be determined based on the CCD black level. There are certain CCD pixels which are not exposed to light (optical-black pixels) and the CCD signal corresponding to these pixels represent the CCD black level. Thus, the offset voltage is determined during the optical-black pixels, and the offset voltage is kept constant and is subtracted from the CCD input to cancel the CCD offset during normal image pixels.

OB calibration in the VSP1221 is done in a closed feedback loop. The difference between the CCD black level and the offset voltage is compared with the user-defined OB reference level at the output of the digital PGA stage. The error is fed to an OB calibration circuit which generates a step proportional to the error and a sign based on the sign of the error. The step and the sign are then given to the OB DAC, which generates an analog voltage that updates the offset voltage at the input of the CDS. If the error is positive, the offset voltage is increased; if the error is negative, the offset voltage is decreased. This continues in a closed feedback loop until the difference between the CCD black level and the offset voltage converges to the OB reference level. The OB calibration circuit has been designed so that a 100-mV CCD black level converges to zero reference OB level within 500–750 pixel clocks. Convergence time increases with an increase in gain. Convergence is faster if the CCD black level is smaller than 100 mV. A plot of the convergence time as a function of the PGA gain is shown in the performance plots section. Since the feedback loop includes the CDS, the PGA, and the ADC, it also cancels any offset introduced by these blocks. The OB reference level can be adjusted by programming the OB register through the serial port (see the *OB register* section)

## standby mode (power-down mode)

To save power, the VSP1221 can be put into standby mode (power-down mode) both through hardware and software. Pulling the STBY signal low puts the device into standby mode (hardware power-down). In this mode, the reference is pulled down, all the functional blocks are disabled, the output is *all zero*, and the power dissipation is zero. The power-up time is of the order of 10 ms. Software power down can be exercised by resetting the STBYZ bit in the control register through the serial port (see the *control register* section). This is similar to hardware power down, except that the reference is not pulled down. Hence, the power dissipation is around 4 mW and the power-up time is of the order of 10 μs. The user can still program all the internal registers during both hardware and software power down.

### general purpose DAC

The VSP1221 has two eight-bit general-purpose digital-to-analog converters (DACs) that can be used for external analog settings. The output voltage of each DAC can be independently set and has a range of 0 V to the supply voltage with eight-bit resolution. The digital input to the DACs can be set by programming the user DAC1 and User DAC2 registers through the serial port (see the *user DAC1 register* and *user DAC2 register* sections). When not used in the system, the DACs can be put in standby mode by programming the above-mentioned registers. The DACs are, by default, in standby mode. The average power consumed by each DAC is approximately 1 mW.

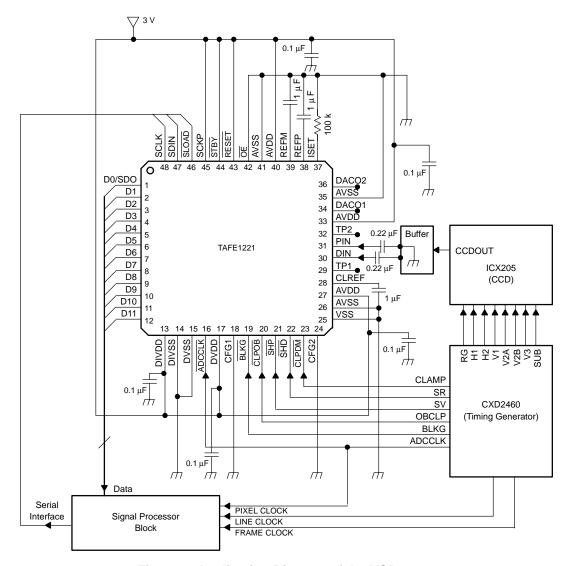

## **APPLICATION INFORMATION**

Figure 9. Application Diagram of the VSP1221

#### NOTE:

The application circuits shown are typical examples of the operation of the devices. Texas Instruments cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third-party patents and other rights due to the same.

## **CCD** input

The CCD output may need an off-chip external buffer in order to drive the input capacitive load of the VSP1221. The buffer output is applied to DIN (pin 30) through an ac-coupling capacitor. It is advisable to connect PIN (pin 31) to the buffer ground through a similar ac-coupling capacitor for the following reason: since the input stage of the VSP1221 is differential, the input to the CDS is the voltage difference between DIN and PIN. Hence, if the noise path for DIN and PIN are similar, the noise can be effectively cancelled. This is not the case if the noise paths are different. However, PIN can also be connected directly to ground. In this case, bit SD8 (CLAMPPIN) of the control register should be 1 (see the *control register* section). If PIN is connected to an ac-coupling capacitor, it is recommended to set bit SD8 (CLAMPPIN) of the control register to 0 so that the ac-coupling capacitor is charged to a fixed clamp voltage. The recommended value for the ac coupling capacitor is  $0.22 \, \mu F$ .

### reference decoupling

Pins REFP (pin 38) and REFM (pin 39) should be connected to ground by means of decoupling capacitors. A 1- $\mu$ F ceramic capacitor is recommended for reference decoupling. For better high-frequency decoupling, 0.1  $\mu$ F ceramic capacitors may be used in parallel. The decoupling capacitors should be placed as close as possible to the reference pins.

### clamp decoupling

To decouple the clamp voltage, a 1- $\mu$ F ceramic capacitor may be connected to CLREF (pin 28). See the  $\overline{CLPDM}$  section for further details.

## internal bias current setting

To set the internal bias current, ISET (pin 37) should be connected to ground through a 100-k $\Omega$  resistor. However, no capacitor should be connected to the ISET pin.

#### power supply, grounding, and device decoupling

The VSP1221 has several power-supply pins. Each major internal analog block has a dedicated AVDD supply pin (pins 27, 33, and 40). The DVDD supply pin (pin 17) powers all internal digital circuitry. Both AVDD and DVDD work with 3-V power supplies. DIVDD and DIGND (pins 13 and 14) supply power to the output digital driver (D0–D11). DIVDD is independent of DVDD and can be operated from 1.8 V to 3.3 V. This allows the outputs to interface with digital ASICs requiring different supply voltages

General design practices should apply to the PCB to limit high-frequency transients and noise that are fed back into the supply lines. This requires adequate bypassing of the supply pins. In the case of power supply decoupling, 0.1- $\mu$ F ceramic capacitors are sufficient to keep the impedance low over a wide frequency range. Since their effectiveness depends largely on the proximity to the individual supply pin, all decoupling capacitors should be placed as close as possible to the supply pins.

To reduce high-frequency and noise coupling, it is highly recommended to short the digital and analog grounds immediately outside the package. This can be accomplished by running a low-impedance line under the package between pins DVSS and AVSS.

#### **APPLICATION INFORMATION**

### data output

It is recommended to keep the capacitive loading on the output data lines as low as possible (typically less than 15 pF). Larger capacitive loads demand higher charging-current surges which can feed back into the analog portion of the VSP1221 and affect its performance. If the data lines are long, it is advisable to use external buffers or latches, which will also provide the added benefit of isolating the VSP1221 from any digital noise that may couple back. In addition, resistors in series with each data line will help in minimizing the surge current. Typical resistor values are  $40-50~\Omega$ .

NOTES: A. OB Calibration latency is 12 clocks. So, OB update starts 12 clocks after CLPOB is pulled low and stops 12 clocks after CLPOB is pulled high.

- B. If active image pixels are located immediately after CLPOB goes high, the OB update will affect the adjacent 12 pixels.

- C. The device clocks are stopped during BLKG and CLPDM. Therefore, if these signals appear immediately after CLPOB goes high, the OB calibration update for the subsequent 12 clocks will stop. So, its recommended to delay BLKG and CLPDM by at least 12 pixels after CLPOB goes high.

Figure 10. System Timing Diagram Example

# performance plots

Figure 11

Figure 13

Figure 14

Figure 15

Figure 17

## **MECHANICAL DATA**

# PBR (S-PQFP-G64)

## **PLASTIC QUAD FLATPACK**

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265