NEC

## VRC4372 I/O Controller with PCI Interface

Data Sheet February 2000

### **Description**

The VRC4372™ is a PCI-based I/O controller for high-performance, low-cost system implementation. Connected to the PCI bus, it is designed to support NEC's VR43xx CPU, interfacing between the VRC4373™ or VRC4375™ system controller and peripherals for tethered applications such as set-top boxes, printers, network computers and consumer electronics.

#### **Features**

- Compatible with NEC VR43xx CPUs and VRc4373 and VRc4375 system controllers

- PCI Bus Interface Controller

- Compliant with the 3.3-volt PCI interface specification (version 2.1)

- 5-volt PCI signaling in a controlled environment (with voltage spikes less than 7.6 volts and DC levels less than 6.6 volts)

- PCI bus arbitration for one internal and six external PCI masters

- □ I/O Controller

- ISA-like, 16-bit I/O bus and four independent direct memory access (DMA) channels

- Ten chip selects and control signals for interfacing to external peripheral chips

- N-to-3 interrupt controller to regulate interrupts from 14 input pins, two internal timers, the keyboard, the mouse, and four DMA channels can be encoded onto one of three outgoing interrupt lines

- □ Four programmable DMA channels

- Unique TC, EOP, DREQ, and DACK signals on each channel

- Block or single transfers

- Read or write requests

- I/O device-demanded service requests via DREQx

- Software-initiated requests

- Channel suspend via the MASK register bit

- I/O device transfer termination via EOP

- · Channel reload notification and termination notification via an interrupt

- Efficient PCI bus data packing mode

- Byte/short scattering/gathering capabilities (one per PCI word)

- □ Miscellaneous I/O

- Timer and a beeper source

- General-purpose control/status I/O pins

- □ Test Port

- TESTOE signal that can be used to tristate all outputs

- SCAN pin to place the chip in scan mode

- Data buffers for direct memory access channels and the I/O bus

- 33-MHz bus frequency

NEC VRc chipsets are designed for use with NEC VR Series microprocessors. NEC makes no claim as to the suitability of VRc chipsets for use with non-NEC microprocessors and does not warrant their performance, suitability or use in such applications.

## Ordering Information

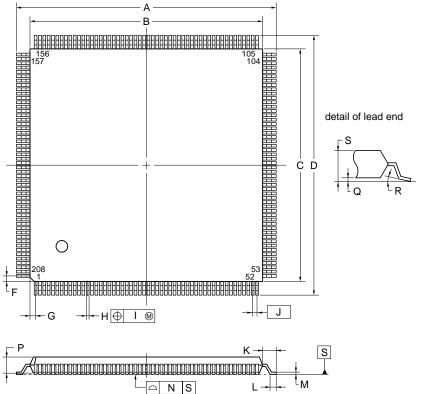

| Part Number | Package      |  |  |

|-------------|--------------|--|--|

| Vrc4372-1   | 208-pin PQFP |  |  |

## System Configuration

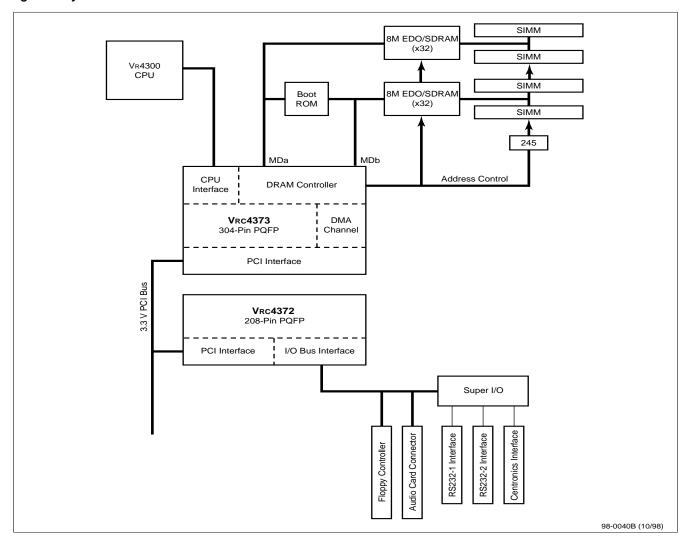

Figure 1 provides an example of a system that uses the VRC4372 controller.

Figure 1. System Connection

### **Reference Documents**

- □ *PCI Local Bus Specification* Revision 2.1 and *PCI System Design Guide* Revision 1.0 (available from the Peripheral Component Interconnect Special Interest Group)

- □ NEC VR4300™ Microprocessor Data Sheet (document number U10116EJ4V0DS00)

- □ IC Package Manual (document number C10943XJ7V0IF00)

## **Contents**

|        | Description                  | 1   |

|--------|------------------------------|-----|

|        | -eatures                     |     |

| (      | Ordering Information         | 2   |

| 5      | System Configuration         | 2   |

| F      | Reference Documents          | . 2 |

| 1.0 F  | Pin Configuration            | . 4 |

| 2.0 E  | Block Diagram                | . 7 |

| 3.0 F  | PCI Bus Interface Controller | . 8 |

| 4.0 C  | Control Registers            | 12  |

| 5.0 F  | PCI Interface                | 12  |

| 6.0 l/ | O Controller                 | 14  |

| 7.0 E  | Buffers                      | 55  |

| 8.0 E  | Frror Handling               | 58  |

| 9.0 E  | Electrical Specifications    | 59  |

| 10.0   | Package Description          | 33  |

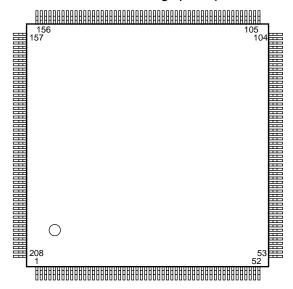

## 1.0 Pin Configuration

### 208-Pin Plastic Quad Flat Package (PQFP)

Table 1. Pin Assignments

| Pin     | Name                     | Pin | Name             | Pin | Name             | Pin | Name             | Pin | Name             |

|---------|--------------------------|-----|------------------|-----|------------------|-----|------------------|-----|------------------|

| 1       | GND0                     | 43  | AD7              | 85  | IOA1             | 127 | IOD15            | 169 | ĪNT4             |

| 2       | GND1                     | 44  | AD6              | 86  | IOA2             | 128 | SCAN             | 170 | ĪNT5             |

| 3       | CBE3                     | 45  | AD5              | 87  | IOA3             | 129 | ARB              | 171 | ĪNT6             |

| 4       | IDSEL                    | 46  | GND10            | 88  | IOA4             | 130 | V <sub>DD7</sub> | 172 | ĪNT7             |

| 5       | AD23                     | 47  | V <sub>DD3</sub> | 89  | IOA5             | 131 | GND20            | 173 | ĪNT8             |

| 6       | AD22                     | 48  | AD4              | 90  | EOP_TC1          | 132 | GPIO0            | 174 | ĪNT9             |

| 7       | GND2                     | 49  | AD3              | 91  | GND15            | 133 | GPIO1            | 175 | ĪNT10            |

| 8       | AD21                     | 50  | AD2              | 92  | IOD0             | 134 | GPIO2            | 176 | IPL2             |

| 9       | AD20                     | 51  | GND11            | 93  | IOA6             | 135 | GPIO3            | 177 | IPL1             |

| 10      | AD19                     | 52  | GND12            | 94  | IOA7             | 136 | GPIO4            | 178 | IPL0             |

| 11      | AD18                     | 53  | V <sub>DD4</sub> | 95  | CS7              | 137 | GPIO5            | 179 | GNT5             |

| 12      | GND3                     | 54  | AD1              | 96  | IOD1             | 138 | GPIO6            | 180 | GNT4             |

| 13      | V <sub>DD0</sub>         | 55  | AD0              | 97  | IOD2             | 139 | GPIO7            | 181 | GNT3             |

| 14      | AD17                     | 56  | IOREADY          | 98  | GND16            | 140 | GPIO8            | 182 | GND25            |

| 15      | AD16                     | 57  | ĪNT0             | 99  | IOD3             | 141 | GPIO9            | 183 | V <sub>DD9</sub> |

| 16      | CBE2                     | 58  | ĪNT1             | 100 | IOD4             | 142 | GND21            | 184 | GNT2             |

| 17      | FRAME                    | 59  | ĪNT2             | 101 | IOD5             | 143 | GPIO10           | 185 | GNT1             |

| 18      | GND4                     | 60  | ĪNT3             | 102 | IOD6             | 144 | IOBEEP           | 186 | REQ5             |

| 19      | ĪRDY                     | 61  | NC               | 103 | IOD7             | 145 | ĪNT12            | 187 | REQ4             |

| 20      | TRDY                     | 62  | EOP_TC3          | 104 | V <sub>DD6</sub> | 146 | ĪNT13            | 188 | GND26            |

| 21      | DEVSEL                   | 63  | EOP_TC2          | 105 | GND17            | 147 | NC               | 189 | REQ3             |

| 22      | GND5                     | 64  | IOFRAME          | 106 | GND18            | 148 | EOP_TC0          | 190 | REQ2             |

| 23      | STOP                     | 65  | GND13            | 107 | NC               | 149 | DREQ1            | 191 | REQ1             |

| 24      | PERR                     | 66  | NC               | 108 | NC               | 150 | DACK1            | 192 | RST              |

| Note: N | Note: NC = no connection |     |                  |     |                  |     |                  |     |                  |

Table 1. Pin Assignments (continued)

| Pin   | Name                     | Pin | Name             | Pin | Name   | Pin | Name             | Pin | Name              |

|-------|--------------------------|-----|------------------|-----|--------|-----|------------------|-----|-------------------|

| 25    | SERR                     | 67  | DREQ3            | 109 | NC     | 151 | DREQ0            | 193 | GND27             |

| 26    | GND6                     | 68  | DREQ2            | 110 | NC     | 152 | DACK0            | 194 | CLK               |

| 27    | V <sub>DD1</sub>         | 69  | DACK3            | 111 | INT11  | 153 | WR0              | 195 | GNT0              |

| 28    | PAR                      | 70  | DACK2            | 112 | NC     | 154 | RD0              | 196 | REQ0              |

| 29    | CBE1                     | 71  | CS0              | 113 | NC     | 155 | GND22            | 197 | V <sub>DD10</sub> |

| 30    | AD15                     | 72  | CS1              | 114 | NC     | 156 | GND23            | 198 | GND28             |

| 31    | AD14                     | 73  | CS2              | 115 | NC     | 157 | V <sub>DD8</sub> | 199 | AD31              |

| 32    | GND7                     | 74  | CS3              | 116 | GND19  | 158 | CPRD0            | 200 | AD30              |

| 33    | AD13                     | 75  | CS4              | 117 | TESTOE | 159 | CPRD1            | 201 | AD29              |

| 34    | AD12                     | 76  | CS5              | 118 | HBE    | 160 | CPWR0            | 202 | AD28              |

| 35    | AD11                     | 77  | RD1              | 119 | LBE    | 161 | CPWR1            | 203 | GND29             |

| 36    | AD10                     | 78  | V <sub>DD5</sub> | 120 | IOD8   | 162 | CPRD2            | 204 | AD27              |

| 37    | GND8                     | 79  | GND14            | 121 | IOD9   | 163 | CPWR2            | 205 | AD26              |

| 38    | V <sub>DD2</sub>         | 80  | WR1              | 122 | IOD10  | 164 | CS6              | 206 | AD25              |

| 39    | AD9                      | 81  | W_R              | 123 | IOD11  | 165 | NC               | 207 | AD24              |

| 40    | AD8                      | 82  | ALE              | 124 | IOD12  | 166 | CS8              | 208 | V <sub>DD11</sub> |

| 41    | CBE0                     | 83  | BUFOE            | 125 | IOD13  | 167 | CS9              | _   | _                 |

| 42    | GND9                     | 84  | IOA0             | 126 | IOD14  | 168 | GND4             | _   |                   |

| Note: | Note: NC = no connection |     |                  |     |        |     |                  |     |                   |

### 1.0.1 Pin Functions

Table 2. PCI Interface Pins

| Pin(s)   | I/O    | Reset Value  | Pull-up/<br>Pull-down | Description                                          |

|----------|--------|--------------|-----------------------|------------------------------------------------------|

| AD[31:0] | I/O    | Hi-Z         | _                     | Multiplexed address/data bus                         |

| CBE[3:0] | I/O    | Hi-Z         | _                     | PCI command/byte enable                              |

| PAR      | I/O    | Hi-Z         | _                     | Parity of AD and CBE                                 |

| FRAME    | I/O    | Hi-Z         | _                     | PCI FRAME                                            |

| TRDY     | I/O    | Hi-Z         | _                     | PCI TRDY                                             |

| ĪRDY     | I/O    | Hi-Z         | _                     | PCI IRDY                                             |

| STOP     | I/O    | Hi-Z         | _                     | PCI STOP                                             |

| DEVSEL   | I/O    | Hi-Z         | _                     | PCI DEVSEL                                           |

| IDSEL    | I      | Hi-Z         | _                     | PCI IDSEL                                            |

| REQ0     | I/O    | Hi-Z         | _                     | PCI REQ input (ARB = Vcc) PCI REQ output (ARB = GND) |

| REQ[5:1] | I      |              | _                     | PCI REQ input                                        |

| GNT0     | I/O    | High<br>Hi-Z | _                     | PCI GNT output (ARB = Vcc) PCI GNT input (ARB = GND) |

| GNT[5:1] | 0      | High         | _                     | PCI GNT output                                       |

| CLK      | I      |              | _                     | PCI CLK input                                        |

| RST      | I      |              | _                     | Reset                                                |

| PERR     | I/O    | Hi-Z         | _                     | Parity error                                         |

| SERR     | I/O-oc | Hi-Z         | _                     | System error                                         |

Table 3. I/O Bus Bidirectional/Output Pins

| Pin(s)                | 1/0 | Reset<br>Value | Pull-up/<br>Pull-down    | Max. DC Load (mA) | AC Load<br>(pF) | Description                                                                   |

|-----------------------|-----|----------------|--------------------------|-------------------|-----------------|-------------------------------------------------------------------------------|

| IOA[7:0]              | 0   | Low            | _                        | 1                 | 10–100          | I/O address bus (eight LSB)                                                   |

| IOD[15:8]<br>IOD[7:0] | I/O | Hi-Z           | Pull-down, 50 KΩ         | 3                 | 0–50<br>10–100  | Multiplexed I/O address/data bus                                              |

| HBE                   | 0   | High           | _                        | 1                 | 0–30            | I/O bus high-byte enable                                                      |

| LBE                   | 0   | High           | _                        | 1                 | 0–30            | I/O bus low-byte enable                                                       |

| ALE                   | 0   | High           | _                        | 2                 | 0–30            | Latches IOA[23:8] from the IOD bus                                            |

| IOFRAME               | 0   | High           | _                        | 1                 | 0–30            | Controls the I/O transfer                                                     |

| W_R                   | 0   | High           | _                        | 1                 | 0–50            | I/O write/read status                                                         |

| RD1<br>RD0            | 0   | High           | _                        | 1                 | 0–70<br>0–30    | General I/O read strobes                                                      |

| WR1<br>WR0            | 0   | High<br>—      | _                        | 1                 | 0-70<br>0-30    | General I/O write strobes                                                     |

| BUFOE                 | 0   | High           | _                        | 3                 | 0–30            | I/O data bus buffer enable                                                    |

| CPRD2<br>CPRD[1:0]    | 0   | High           | _                        | 3<br>1            | 0-30<br>0-30    | Decoded I/O read strobe, 2x F245 load<br>Decoded I/O read strobes, CMOS load  |

| CPWR2<br>CPWR[1:0]    | 0   | High           | _                        | 2                 | 0–30            | Decoded I/O write strobe, 3x F373 load<br>Decoded I/O write strobe, CMOS load |

| CS[9:8]<br>CS[7:0]    | 0   | High           | _                        | 3<br>1            | 0–30            | Decoded chip selects, 2x F245 load<br>Decoded chip selects, CMOS load         |

| IPL[2:0]              | 0   | High           | _                        | 1                 | 0–15            | CPU interrupts                                                                |

| DACK[2:0]             | 0   | High           | _                        | 1                 | 0–30            | DMA acknowledge                                                               |

| DACK3                 | 0   | Low            | _                        | 1                 | 0–30            | DMA acknowledge                                                               |

| EOP_TC[3:0]           | I/O | Hi-Z           | Pull-down, 50 K $\Omega$ | 1                 | 0–30            | DMA terminal count and EOP                                                    |

### Table 4. I/O Bus Input Pins

| Pin(s)    | 1/0              | Reset Value | Pull-up/Pull-down | Description                                                                                                                         |

|-----------|------------------|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| IOREADY   | I                |             | Pull-down, 50 KΩ  | Ready indicates I/O bus cycle complete                                                                                              |

| DREQ[3:0] | I                |             | Pull-down, 50 KΩ  | DMA request                                                                                                                         |

| ĪNT[13:0] | I/O<br>(Schmitt) | Hi–Z        |                   | Interrupt request when \$\overline{SCAN}\$ = Vcc (input only); scan signals when \$\overline{SCAN}\$ = GND (may be input or output) |

### Table 5. Miscellaneous I/O Pins

| Pin(s)     | I/O | Reset<br>Value | Pull-up/<br>Pull-down | DC<br>Load<br>(mA) | AC<br>Load<br>(pF) | Description                                                   |

|------------|-----|----------------|-----------------------|--------------------|--------------------|---------------------------------------------------------------|

| GPIO[10:0] | I/O | Hi–Z           | Pull-down, 50 KB      | 2<br>(Note)        | 0–30               | General-purpose status/control signals                        |

| IOBEEP     | 0   | Low            | _                     | 1                  | 30                 | Beeper output                                                 |

| SCAN       | 1   | _              | _                     | _                  | _                  | Enables scan test mode when low                               |

| TESTOE     | 1   | _              | _                     | 1                  | 0                  | Tristates all outputs when low                                |

| ARB        | I   | _              | _                     | 1                  | 0                  | Internal arbitration when high; external arbitration when low |

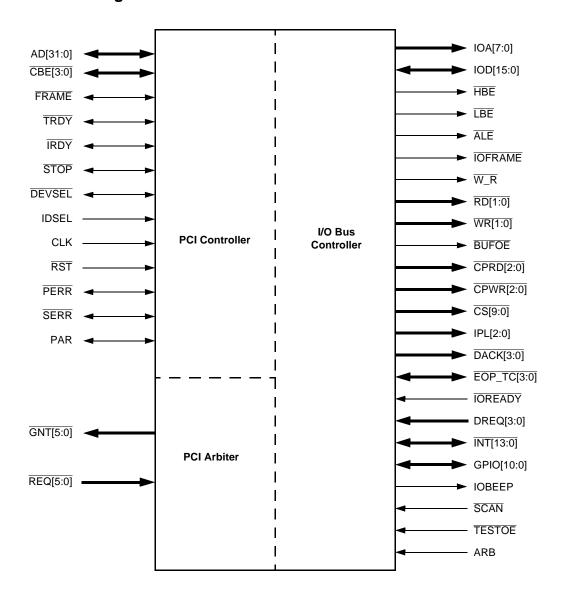

## 2.0 Block Diagram

### 3.0

### 3.1

# PCI Configuration Space Registers

### **PCI Bus Interface Controller**

The VRC4372 controller implements the 256-byte configuration space defined by the PCI bus specification (Table 6). Access to these registers is accomplished by read and write accesses in the PCI configuration space. In these modes, onboard logic asserts the IDSEL signal pin, thus selecting the VRC4372 configuration registers. Read accesses from undefined and reserved locations complete normally and return a logic 0. Undefined or reserved bits also read as logic 0, but the PCI specification requires that the software not rely on reserved bits having any particular value. Write accesses to undefined and reserved locations complete normally and the data is discarded.

Table 6. PCI Configuration Registers

| Register<br>Name             | Symbol   | Configuration<br>Offset | R/W | Description                                                              |

|------------------------------|----------|-------------------------|-----|--------------------------------------------------------------------------|

| Vendor ID                    | VID      | 0x01-0x00               | R   | Manufacturer name                                                        |

| Device ID                    | DID      | 0x03-0x02               | R   | Device name                                                              |

| Command                      | PCICMD   | 0x05-0x04               | R/W | Coarse control of PCI interface                                          |

| Status                       | PCISTS   | 0x07-0x06               | R/W | Status information for PCI-related events                                |

| Revision ID                  | RID      | 0x08                    | R   | Device revision                                                          |

| Class code                   | CLASS    | 0x0b-0x09               | R   | Device type                                                              |

| Cache line size              | CLSIZ    | 0x0c                    | R/W | System cache line size (words)                                           |

| Master latency timer         | MLTIM    | 0x0d                    | R/W | Value of latency timer for this master, in PCI clocks                    |

| Header type                  | HTYPE    | 0x0e                    | R   | Layout for registers in the range 0x10–0xff                              |

| Register base address        | REGADD   | 0x13-0x10               | R/W | Start and size of register's region                                      |

| I/O bus base<br>address      | IObusADD | 0x17-0x14               | R/W | Start and size of I/O memory space                                       |

| Reserved                     | _        | 0x3b-0x18               | _   | _                                                                        |

| Interrupt line               | INTLIN   | 0x3c                    | R/W | Interrupt line routing information                                       |

| Interrupt pin                | INTPIN   | 0x3d                    | R   | Interrupt pin name                                                       |

| Undefined                    | _        | 0x3f-0x3e               | _   | _                                                                        |

| Disconnect timer             | DSCTIM   | 0x40                    | R   | Not implemented                                                          |

| Retry timer                  | RTYTIM   | 0x41                    | R/W | Maximum number of tries before terminating transaction. Reset value = 00 |

| Trdy timer                   | TDYTIM   | 0x42                    | R/W | Not implemented                                                          |

| PCI arbiter priority control | PAPC     | 0x43                    | R/W | Priority scheme for granting the PCI bus                                 |

### Table 7. Device and Vendor Identification

| Bit(s) | Symbol | Name      | Functional Description                  |

|--------|--------|-----------|-----------------------------------------|

| 15:0   | VID    | Vendor ID | Hardwired to 0x1033 for NEC PCI devices |

| 31:16  | DID    | Device ID | Hardwired to 0x001A                     |

### Table 8. Command Register (PCICMD)

| Bit(s) | Symbol   | Name                               | Functional Description                                                                           |

|--------|----------|------------------------------------|--------------------------------------------------------------------------------------------------|

| 0      | IOEN     | I/O space enable                   | Hardwired to 0; ignored                                                                          |

| 1      | MEMEN    | Memory space enable                | Reset to 0; must set to 1 via software to enable the VRC4372 to respond to memory space accesses |

| 2      | BMAS     | Bus master enable                  | Reset to 0; must be set to 1 to enable the VRC4372 to generate PCI accesses                      |

| 3      | SPC      | Special cycles enable              | Hardwired to 0; ignored                                                                          |

| 4      | MWI      | Memory write and invalidate enable | Hardwired to 0; ignored                                                                          |

| 5      | VGA      | Video Graphics Array               | Hardwired to 0; ignored because the VRC4372 is not a VGA device                                  |

| 6      | PER      | PERR enable                        | Reset to 0                                                                                       |

| 7      | WAIT_CTL | Wait cycle control                 | Hardwired to 0; ignored                                                                          |

| 8      | SERR_EN  | SERR enable                        | Reset to 0                                                                                       |

| 9      | FBBE     | Fast back-to-back enable           | Hardwired to 0; ignored                                                                          |

| 15:10  | Reserved | _                                  | Read as 0                                                                                        |

### Table 9. Status Register (PCISTS)

| Bit(s) | Symbol                                                           | Name                      | Functional Description                                   |  |

|--------|------------------------------------------------------------------|---------------------------|----------------------------------------------------------|--|

| 22:16  | Reserved                                                         | _                         | Read as 0                                                |  |

| 23     | FBBC                                                             | Fast back-to-back capable | Hardwired to 1; fast back-to-back enabled                |  |

| 24     | DPR                                                              | Data parity reported      | Data parity reported                                     |  |

| 26:25  | DEVSEL                                                           | DEVSEL timing             | Hardwired to 01 (medium response)                        |  |

| 27     | STA Signaled target abort Set whenever the VRC4372 signals abort |                           | Set whenever the VRC4372 signals a target abort          |  |

| 28     | RTA                                                              | Received target abort     | Set whenever the VRC4372 master receives a target abort  |  |

| 29     | RMA                                                              | Received master abort     | Set whenever the VRc4372 master generates a master abort |  |

| 30     | SSE                                                              | Signaled system error     | Set whenever the VRc4372 detects a system error          |  |

| 31     | DPE                                                              | Detected parity error     | Set whenever the VRC4372 detects a pari error            |  |

Table 10. Revision Identification (RID) and Class Codes

| Bit(s) | Symbol | Name                  | Functional Description |

|--------|--------|-----------------------|------------------------|

| 7:0    | RID    | Revision ID           | Hardwired to 0x00      |

| 15:8   | Prog   | Programming interface | Hardwired to 0x00      |

| 23:16  | SubCl  | Subclass              | Hardwired to 0x80      |

| 31:24  | BaseCl | Base class            | Hardwired to 0x06      |

### Table 11. Built-In Self Test, Header Type, Master Latency Timer, and Cache Line Size

| Bits(s) | Symbol   | Functional Description                                                                   |

|---------|----------|------------------------------------------------------------------------------------------|

| 7:0     | CLSIZ    | Hardwired to 0x00. The VRC4372 rejects cache line fills/spills (unnatural order bursts). |

| 10:8    | MLTIM    | Hardwired to 000                                                                         |

| 15:11   | MLTIM    | Master Latency Timer. See the PCI specification (Sections 3.4.4.1 and 6.2.4).            |

| 23:16   | HTYPE    | Hardwired to 0x00                                                                        |

| 31:24   | Reserved | -                                                                                        |

### Table 12. Register Base Address (REGADD)

| Bits(s) | Symbol   | Functional Description                                                                                                                            |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0    | Reserved | Hardwired to 0x0000; indicates that the VRc4372 registers should be located in a 32-bit memory space on a 64 KB boundary and are not prefetchable |

| 31:16   | REGADD   | Maps the VRC4372 registers in memory on a 64 KB boundary                                                                                          |

### Table 13. I/O Memory Base Address (IOADD)

| Bits(s) | Symbol   | Functional Description                                                                                                                                    |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27:0    | Reserved | Hardwired to 0x000000 to indicate that the VRc4372 I/O memory should be located in a 32-bit PCI memory space on a 256-MB boundary and is not prefetchable |

| 31:28   | IOADD    | The higher four bits of IOADD are used to map the VRC4372 system memory on a 256-MB boundary.                                                             |

### Table 14. Interrupt Pin (INTPIN) and Interrupt Line (INTLIN)

| Bit(s) | Symbol    | Functional Description                                                                                                                                                                                                                                                  |

|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | INTLIN    | Provides interrupt line routing information as required by the PCI specification (Section 6.2.4); can be used as a scratch pad in motherboard implementations                                                                                                           |

| 15:8   | INTPIN    | Hardwired to 0x01 to indicate that the VRc4372 uses INTA. When the VRc4372 is used with add-in cards, this bit indicates that the VRc4372 is connected only to INTA. When used in a motherboard implementation, the VRc4372 may drive as many as three interrupt lines. |

| 31:16  | Undefined | Read as 0                                                                                                                                                                                                                                                               |

## Table 15. DSCTIM, RTYTIM, TDYTIM, PAPC

| Bit(s) | Symbol    | Functional Description                                                                                                                                                 |

|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | DSCTIM    | Disconnect timer (not implemented); read as 0                                                                                                                          |

| 15:8   | RTYTIM    | Retry timer; reset value is 00                                                                                                                                         |

| 23:16  | TDYTIM    | TRDY timer (not implemented); read as 0                                                                                                                                |

| 25:24  | PAPC      | PCI arbiter priority control register; reset value is 00                                                                                                               |

|        |           | Rotating fair (00); REQ0 owns the bus during Idle mode                                                                                                                 |

|        |           | Rotating alternate 0 (01); REQ0 owns the bus during Idle mode                                                                                                          |

|        |           | Rotating alternate I (10); the VRc4372 owns the bus during Idle mode                                                                                                   |

|        |           | Not used (11)                                                                                                                                                          |

| 26     | TKYGNT    | Take away grant; reset value is 00                                                                                                                                     |

|        |           | When 0, REQx is granted and continues until the request is removed.                                                                                                    |

|        |           | When 1, REQx is granted, but the bus loses the GNTx to higher priority requests. Since only rotating priority schemes are used, all requests are at a higher priority. |

|        |           | MLTIM determines the minimum bus tenure for a master.                                                                                                                  |

| 31:27  | Undefined | Read as 0                                                                                                                                                              |

### 4.0 Control Registers

The VRC4372 I/O controller implements 64 KB of control register space (16 KB words). Beginning at the address specified by the REGADD register in the PCI header and occupying the lower 64 KB of that address space, the register space is divided into 16 regions of 4096 bytes each and selected by A[15:12]. Each register region is dedicated to one particular function.

Table 16. Register Allocation

| Number | Address Offset | Description       |

|--------|----------------|-------------------|

| 0      | 0x0000-0x0fff  | Control registers |

| _      | 0x1000-0xffff  | Undefined         |

### 5.0 PCI Interface

The PCI interface performs the following functions:

- PCI master

- PCI target

- Register access

As a PCI master, the PCI interface used by the DMA controller performs memory read and write cycles on the PCI bus. Burst transfers are executed if the byte count requested by the DMA channel is greater than four (in multiples of four). Byte alignment is accomplished in the DMA data buffer section.

As a PCI target, the PCI interface is used for CPU accesses to the I/O bus and should enforce nonburst accesses by performing a target disconnect on the first word. The PCI target contains a posted write buffer that allows write cycles to complete with no PCI bus wait states. When write cycles are executed, data is captured by the posted write buffer and split into one to four I/O bus accesses, according to the byte enables and the device data size communicated by the I/O bus controller and as specified by the profile register for that device. The data is split according to little-endian ordering and correctly aligned. During splitting of the write data (emptying the I/O bus-posted write buffer), the target subsection causes the PCI interface to generate a target retry for all subsequent read or write accesses to the I/O bus.

Register access is also provided by the PCI interface. All VRc4372 registers are accessed as byte-writable 32-bit words directly through this subsection. Register accesses continue during PCI target-posted, write buffer emptying.

5.1

#### **PCI** Arbitration

The VRC4372 I/O controller features an internal PCI arbiter that can be configured by pulling the ARB pin high to arbitrate among six requestors (five external and one internal), as specified by the bits programmed in the PAPC register. A reset selects a rotating fair scheme. If the ARB pin is tied low, the VRC4372 does not perform arbitration for the PCI bus and uses a logic 0 request grant pair to request the PCI bus for internal requirements.

### 5.1.1 Rotating Fair

In this scheme, the priority of each requestor changes after every request, in roundrobin fashion, to give every request a fair chance to get on the bus. The rotation sequence is as follows:

- 1. Internal request

- 2. Requestors 0, 1, 2, 3, 4, 5

- 3. Internal request

If any of the requestors is not on, then the next requestor in the sequence becomes the highest priority. After a requestor is granted the bus, it remains granted, depending upon the setting of the TKYGNT bit.

### 5.1.2 Rotating Alternate 0

In this scheme,  $\overline{REQ0}$ , if asserted, is granted the bus after every other transaction, as follows:

0, 1, 0, 2, 0, 3, 0, 4, 0, 5, 0, i (internal), and then repeat

After a requestor is granted the bus, it remains granted, depending upon the setting of the TKYGNT bit.

### 5.1.3 Rotating Alternate I

This scheme is identical to rotating alternate 0, except that the internal request is given the advantage, as follows:

i, 0, i, 1, i, 2, i, 3, i, 4, i, 5, and then repeat

After a requestor is granted the bus, it remains granted, depending on the setting of the TKYGNT bit.

When a PCI-to-I/O bus request cannot be granted immediately by the I/O bus arbiter,

PCI-to-I/O Bus

Arbitration Control

the VRc4372 I/O controller can wait up to four clock cycles before generating a PCI bus retry. Refer to Section 6.5.3 for additional information.

5.3

5.2

## PCI Interface Timer (DSCTIM, RTYTIM)

### 5.3.1 Disconnect Timer (DSCTIM)

The DDCTIM times out a burst operation when the bridge is a target. Because the VRC4372 cannot take a burst operation as a target, this timer is not necessary.

### 5.3.2 Retry Timer (RTYTIM)

This timer programs the maximum number of tries that a master performs before terminating a transaction. On a reset, the value 0x00 is loaded into the timer to disable the feature. To enable the timer, a nonzero value is loaded. When the timer expires, SERR is asserted (if enabled) and a bit is set in the Status register of the affected DMA channel.

### 6.0 I/O Controller

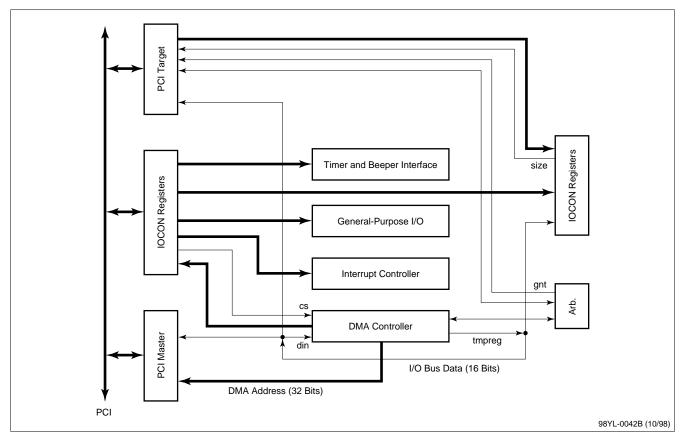

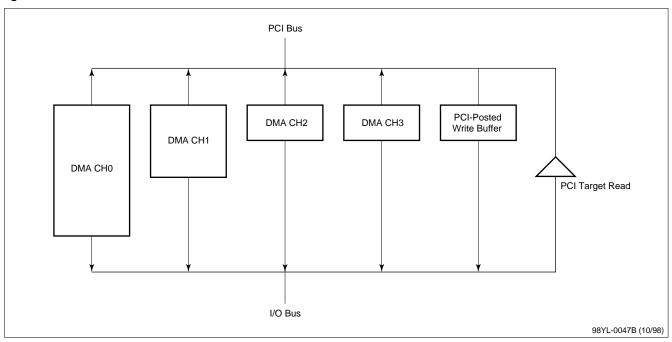

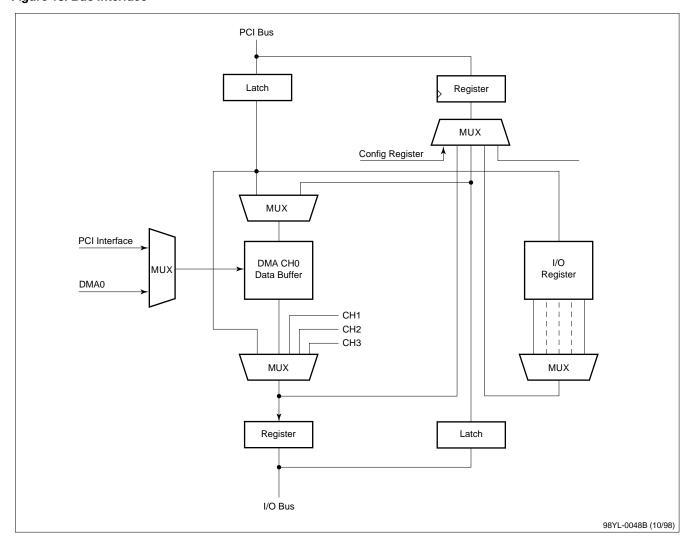

The I/O controller (IOCON) block contains the following subblocks (Figure 2):

### Overview

- Interface controller

- DMA controller

- Timer and beeper interface

- General-purpose I/O

- Interrupt controller

Figure 2. I/O Controller Block Diagram

### 6.1.1 I/O Register Memory Map

The I/O registers are grouped by function (Table 17):

Table 17. Control Register Memory Map

| Offset Value  | Register Name        | Reference/Description    |

|---------------|----------------------|--------------------------|

| 0x01ff-0x0100 | General-Purpose I/O  | Section 6.2.2 on page 15 |

| 0x02ff-0x0200 | Interrupt Controller | Section 6.3.2 on page 17 |

| 0x03ff-0x0300 | Timer and Beeper     | Section 6.4.2 on page 22 |

| 0x04ff-0x0400 | I/O Bus Interface    | Section 6.5.2 on page 25 |

| 0x06ff-0x0500 | DMA Controller       | Section 6.6.2 on page 43 |

| 0xffff-0x0700 | Undefined            | Read as 0                |

#### 6.2

## General-Purpose I/O Pins

### 6.2.1 Overview

Eleven general-purpose I/O pins provide glueless access to system status and control information. All pins can be individually defined as either input or output via the GPDIR register. Pins configured as outputs receive output data from the GPOUT register. Pins configured as inputs or outputs can be read back via the GPIN register.

### 6.2.2 Signal and Pin Descriptions

The general-purpose I/O block consists of 11 bidirectional pins. When configured as outputs, these pins are clocked directly from the rising edge of the PCI CLK signal and do not float. When configured as inputs, these pins are considered static inputs and are not sampled.

| Bit(s) | Symbol     | Description                                                    |

|--------|------------|----------------------------------------------------------------|

| 10:0   | GPIO[10:0] | Default direction is input. No inversion occurs on these pins. |

### 6.2.3 General-Purpose I/O Registers

Table 18. General-Purpose I/O Registers

| Symbol | Offset Value  | Reset Value     | R/W | Description                     |

|--------|---------------|-----------------|-----|---------------------------------|

| GPDIR  | 0x0103-0x0100 | Input direction | R/W | Sets the direction for each pin |

| GPOUT  | 0x0107-0x0104 | 0x0000 0000     | R/W | Output value to each pin        |

| GPIN   | 0x010b-0x0108 | N/A             | R   | Input value from each pin       |

| _      | 0x01ff-0x010c | N/A             | R   | Read as 0                       |

### 6.2.4 General-Purpose Direction Register (GPDIR)

This register selects the GPIO pins to perform as either inputs or outputs.

| Bit(s) | Symbol      | Description                                                                                                                                                                   |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:0   | GPDIR[10:0] | Each bit controls the direction of the GPIO pin of the same number. At power-up, all bits are reset to 0 (input). When a bit is set to 1, the appropriate GPIO pin is output. |

| 31:11  | Unused      | Read back as zero                                                                                                                                                             |

### 6.2.5 General-Purpose Output Register (GPOUT)

This register contains the data to be placed on GPIO pins configured as outputs. Data written to input pins is ignored.

| Bit(s) | Symbol      | Description                                               |

|--------|-------------|-----------------------------------------------------------|

| 10:0   | GPOUT[10:0] | Each bit sends data onto the GPIO pin of the same number. |

| 31:11  | Unused      | Read back as zero                                         |

### 6.2.6 General-Purpose Input Register (GPIN)

This register provides the capability to read the state of the GPIO pins at the pad. All pins, whether configured as input or output, can be read.

| Bit(s) | Symbol     | Description                                                    |

|--------|------------|----------------------------------------------------------------|

| 10:0   | GPIN[10:0] | Each bit reads data back from the GPIO pin of the same number. |

| 31:11  | Unused     | Read back as zero                                              |

#### 6.3.1 Overview

### **Interrupt Controller**

6.3

The interrupt controller block controls the 14 external interrupt pins and internal interrupt sources (two timer ticks, four DMA channel interrupts, one watchdog timer, and a host of PCI error sources) coded onto three output interrupt pins. This interrupt controller implements a very simple scheme that does not perform interrupt encoding.

Each of the 14 external interrupt lines (INT[13:0]) can be programmed separately to falling edge, rising edge, active low, or active high; triggering occurs via the INTPOL and INTTRIG registers. Additionally, each of the 14 raw interrupt lines may be read using the INTPINS register.

Each of the three IPL[2:0] interrupt output pins has an associated Interrupt Source Mask register (INTMSK[2:0]) and Interrupt Status register (INTSTAT[2:0]).

## 6.3.2 Signal and Pin Descriptions

| Symbol       | Description                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPL[2:0]     | These three, twice-clocked, active-low outputs are the concentrated interrupt lines to the CPU.                                                                                                                                                                                                                                                                                         |

| ĪNT[13:0]    | These 14 inputs serve as external interrupts to the IPL interrupt pins. Each input can be programmed to perform as a rising-edge, falling-edge, active-low, or active-high interrupt.                                                                                                                                                                                                   |

| DMA_INT[3:0] | These four signals originate internally, one from each of the four DMA channels. They are active low when asserted and are cleared at the DMA channel source.                                                                                                                                                                                                                           |

| TICK[1:0]    | These two signals originate internally, one from each of the two timer channels. They are rising-edge when triggered and require clearing within the interrupt controller, using the INTSTAT write operation.                                                                                                                                                                           |

| TOUT_INT     | This signal originates internally from the I/O bus time-out block. This signal is active low when asserted and cleared using the IOTOUT register clearing mechanism described in Section 6.5.                                                                                                                                                                                           |

| PERR_INT     | This signal originates internally from the PCI bus interface. It is triggered at the falling edge and requires clearing within the interrupt controller using the INSTAT write operation. This interrupt source signals that the VRC4372 has sensed that the PCI PERR signal is asserted during a valid PCI transaction originating from any device on the PCI bus (including VRC4372). |

| SERR_INT     | This signal originates internally from the PCI bus interface. It is triggered at the falling edge and requires clearing within the interrupt controller using the INSTAT write operation. This interrupt source signals that the VRC4372 has sensed that the PCI SERR signal is asserted during a valid PCI transaction originating from any device on the PCI bus (including VRC4372). |

| SIG_TA       | This signal originates internally from the PCI bus interface. It is triggered at the falling edge and requires clearing within the interrupt controller using the INSTAT write operation. This interrupt source signals that the VRC4372 has signalled a PCI "Target Abort" during a valid PCI target access to VRC4372.                                                                |

| REC_TA       | This signal originates internally from the PCI bus interface. It is triggered at the falling edge and requires clearing within the interrupt controller using the INSTAT write operation. This interrupt source signals that the VRC4372 has received a PCI "Target Abort" during a valid PCI target access from a DMA channel.                                                         |

| SIG_MA       | This signal originates internally from the PCI bus interface. It is triggered at the falling edge and requires clearing within the interrupt controller using the INSTAT write operation. This interrupt source signals that the VRC4372 has signalled a PCI "Master Abort" during a valid PCI master access from a DMA channel.                                                        |

| PCI_ADD      | This signal originates internally from the PCI bus interface. It is triggered at the falling edge and requires clearing within the interrupt controller using the INSTAT write operation. This interrupt source signals that the VRC4372 has detected a parity error on the PCI address bus.                                                                                            |

| RET_ERR      | This signal originates internally from the PCI bus interface. It is triggered at the falling edge and requires clearing within the interrupt controller using the INSTAT write operation. This interrupt source signals that the retry counter limit is reached on a PCI bus cycle originating from a DMA channel.                                                                      |

### 6.3.3 Interrupt Controller Registers

Table 19. Interrupt Controller Registers

| Symbol   | Offset Value  | Reset Value | R/W | Description                            |

|----------|---------------|-------------|-----|----------------------------------------|

| INTPOL   | 0x0203-0x0200 | 0x0000 0000 | R/W | INT[13:0] input inversion control      |

| INTTRIG  | 0x0207-0x0204 | 0x0000 0000 | R/W | INT[13:0] level/edge selection control |

| INTPINS  | 0x020b-0x0208 | N/A         | R   | Raw input value from each INT pin      |

| INTMSK0  | 0x020f-0x020c | 0x0000 0000 | R/W | IPL0 mask register                     |

| INTSTAT0 | 0x0213-0x0210 | 0x0000 0000 | R/W | IPL0 status register                   |

| INTMSK1  | 0x0217-0x0214 | 0x0000 0000 | R/W | IPL1 mask register                     |

| INTSTAT1 | 0x021b-0x0218 | 0x0000 0000 | R/W | IPL1 status register                   |

| INTMSK2  | 0x021f-0x021c | 0x0000 0000 | R/W | IPL2 mask register                     |

| INTSTAT2 | 0x0223-0x0220 | 0x0000 0000 | R/W | IPL2 status register                   |

| Unused   | 0x02ff-0x0224 | N/A         | R   | Read as 0                              |

### **Interrupt Polarity Control Register (INTPOL)**

This register provides the ability to selectively invert each of the 14 interrupt input pins (INT[13:0]) before they enter the interrupt controller. The register also provides the ability to deal with any active polarity or edge type that might be required by an external peripheral.

| Bit(s) | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:0   | INTPOL[13:0] | Each bit corresponds to the $\overline{\text{INT}}$ input pin of the same number. When a bit is clear, the corresponding $\overline{\text{INT}}$ interrupt input pin is brought into the controller without inversion to provide the capability to trigger on either a low level or a rising edge. When a bit is set, the corresponding input pin is brought into the controller inverted to provide the ability to trigger on either a high level or a falling edge. |

| 31:14  | Unused       | Read back as zero                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### **Interrupt Trigger Control Register (INTTRIG)**

This register provides the ability to selectively trigger on either edge- or level-triggered interrupts for each of the incoming  $\overline{\text{INT}}$  interrupt lines that have passed through the INTPOL block.

| Bit(s)     | Symbol        | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits 13:0  | INTTRIG[13:0] | Each bit corresponds to the $\overline{\text{INT}}$ input pin of the same number. When a bit is clear, the corresponding $\overline{\text{INT}}$ interrupt input pin is level-triggered (active low when the INTPOL bit is set to 0, and active high when INTPOL is set to 1). When a bit is set, the corresponding input pin is edge-triggered (rising edge when INTPOL is set to 0; falling edge when INTPOL is set to 1). |

| Bits 31:14 | Unused        | Read back as zero                                                                                                                                                                                                                                                                                                                                                                                                            |

### **Interrupt Pin Read Register (INTPINS)**

This register provides the ability to read the raw interrupt pins. It does not latch the input pin states and it contains static inputs for unused interrupt input lines.

| Bit(s) | Symbol        | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:0   | INTPINS[13:0] | Each bit corresponds to the $\overline{\text{INT}}$ input pin of the same number. When a bit is clear, the corresponding $\overline{\text{INT}}$ interrupt input pin is low; when a bit is set, the corresponding $\overline{\text{INT}}$ pin is high. If dynamic input sources are used, then the buffer should be read repeatedly until two consecutive read cycles return the same value. |

| 31:14  | Unused        | Read back as zero                                                                                                                                                                                                                                                                                                                                                                            |

### Interrupt MASK Registers (INTMSK[2:0])

Each of these registers corresponds to the output interrupt pin IPL[2:0] of the same number. These three registers provide a means for selecting the interrupt input sources that are assigned to a particular IPL output pin. It is recommended that an interrupt source only be assigned to zero or to one IPL output and not all. Every possible interrupt source has a corresponding bit in each of these registers. When this bit is set, the interrupt source is enabled to the IPL output pin. When this bit is clear, the interrupt source is masked on that IPL output pin.

| Bit( | s) | Symbol       | Description                                                                            |

|------|----|--------------|----------------------------------------------------------------------------------------|

| 13:0 | )  | INT[13:0]    | Each bit corresponds to an external qualified interrupt input line of the same number. |

| 17:1 | 14 | DMA_INT[3:0] | Interrupt mask bit for DMA channels 3 to 0                                             |

| 19:1 | 18 | TICK[1:0]    | Interrupt mask bit for timer TICK1 and TICK0                                           |

| 21:2 | 20 | Unused       | Undefined                                                                              |

| 22   |    | TOUT_INT     | Interrupt mask bit for an I/O bus timeout interrupt                                    |

| 23   |    | PERR_INT     | Interrupt mask bit for the PCI PERR_INT signal                                         |

| 24   |    | SERR_INT     | Interrupt mask bit for the PCI SERR_INT signal                                         |

| 25   |    | SIG_TA       | Interrupt mask bit for the PCI SIG_TA signal                                           |

| 26   |    | REC_TA       | Interrupt mask bit for the PCI REC_TA signal                                           |

| 27   |    | SIG_MA       | Interrupt mask bit for the PCI SIG_MA signal                                           |

| 28   |    | PCI_ADD      | Interrupt mask bit for the PCI PCI_ADD signal                                          |

| 29   |    | RET_ERR      | Interrupt mask bit for the PCI RET_ERR signal                                          |

| 30   |    | Unused       | Read back as zero                                                                      |

| 31   |    | Unused       | Read back as zero                                                                      |

### Interrupt Status Registers (INTSTAT[2:0])

Each of these registers corresponds to the output interrupt pin IPL[2:0] of the same number. These three registers provide a snapshot of the source of an IPL interrupt taken on one clock edge during the read cycle (synchronized). This register also provides a means for clearing edge-triggered interrupt sources. To clear an edge-triggered interrupt, a zero is written to this register in the bit position of the interrupt. And, since common edge-detection logic is used for an interrupt source to both IPL outputs, clearing a bit in one INTSTAT register clears the bit in all registers. Zeros written to level-triggered interrupt sources have no effect. Every possible interrupt source has a corresponding bit in each of these registers. When this bit is set, the interrupt source is driving the IPL pin. When this bit is clear, the interrupt source is not the cause of the IPL output assertion. Note that because level-triggered sources are not clocked, it is possible (but unlikely) that an interrupt could be generated and disappear before this register is read.

| Bit(s) | Symbol       | Description                                                                            |

|--------|--------------|----------------------------------------------------------------------------------------|

| 13:0   | INT[13:0]    | Each bit corresponds to an external qualified interrupt input line of the same number. |

| 17:14  | DMA_INT[3:0] | Interrupt status bit for DMA channels 3 to 0                                           |

| 19:18  | TICK[1:0]    | Interrupt status bit for timer TICK1 and TICK0                                         |

| 21:20  | Unused       | Undefined                                                                              |

| 22     | TOUT_INT     | Interrupt status bit for an I/O bus timeout interrupt                                  |

| 23     | PERR_INT     | Interrupt status bit for the PCI PERR_INT signal                                       |

| 24     | SERR_INT     | Interrupt status bit for the PCI SERR_INT signal                                       |

| 25     | SIG_TA       | Interrupt status bit for the PCI SIG_TA signal                                         |

| 26     | REC_TA       | Interrupt status bit for the PCI REC_TA signal                                         |

| 27     | SIG_MA       | Interrupt status bit for the PCI SIG_MA signal                                         |

| 28     | PCI_ADD      | Interrupt status bit for the PCI PCI_ADD signal                                        |

| 29     | RET_ERR      | Interrupt status bit for the PCI RET_ERR signal                                        |

| 30     | Unused       | Read back as zero                                                                      |

| 31     | Unused       | Read back as zero                                                                      |

### 6.4

## Timer and Beeper Interface

### 6.4.1 Overview

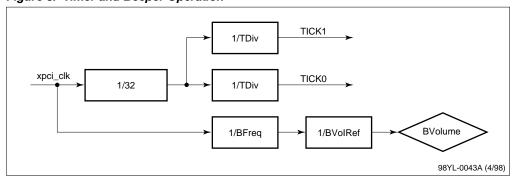

The timer section generates a system tick with a programmable frequency that can be used to issue a periodic interrupt. The beeper section generates the pulse-width-modulated waveform required for activating the speaker driver.

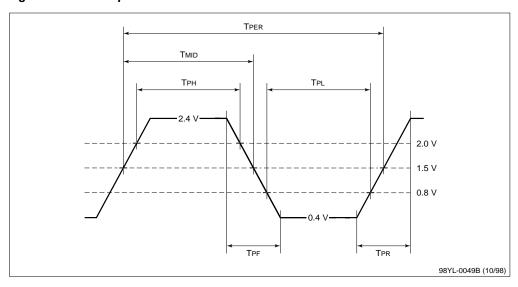

Figure 3. Timer and Beeper Operation

### 6.4.2 Signal and Pin Descriptions

The timer and beeper block consists of two internal signals and one output pin.

| Symbol    | Description                                                                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOBEEP    | This signal drives an operational amplifier (op-amp) that activates an external beeper. An internal version of this signal is also used by the DMA channels as a method to request DMA channel service.                            |

| TICK[1:0] | These two internal signals are used by the interrupt controller block to generate periodic interrupts to the CPU. The interrupt controller block is responsible for capturing, clearing, and masking these signals as appropriate. |

### 6.4.3 Timer and Beeper Registers

Table 20. Timer/Beeper Registers

| Symbol  | Offset Value  | Reset Value | R/W | Description                               |

|---------|---------------|-------------|-----|-------------------------------------------|

| IOTIME0 | 0x0303-0x0300 | 0x0000 0000 | R/W | Controls timer 0                          |

| IOTVAL0 | 0x0307-0x0304 | 0x0000 0000 | R   | Contains running value for timer 0        |

| IOTIME1 | 0x030b-0x0308 | 0x0000 0000 | R/W | Controls timer 1                          |

| IOTVAL1 | 0x030f-0x030c | 0x0000 0000 | R   | Contains running value for timer 1        |

| IOBEEP  | 0x0313-0x0310 | 0x0000 0000 | R/W | Controls the pitch and volume of the beep |

| _       | 0x03ff-0x0314 | _           | R   | Read as 0                                 |

### 6.4.4 Timer Control Register (IOTIMEx)

This register controls the timer "x." Any write cycle to this register resets the counter to its initial value.

| Bit(s) | Symbol   | Description                                                                                                                                                                                                  |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0   | TDiv     | Tick generator divider. Sets the system tick between 16 Hz and 1 MHz. 0 disables the timer.                                                                                                                  |

| 29:16  | Unused   | Read as 0                                                                                                                                                                                                    |

| 30     | TIntEN   | Timer interrupt enable (1)                                                                                                                                                                                   |

| 31     | Terminal | Timer terminal value reached (1). Set by the hardware when the timer reaches its terminal count. Reset by the hardware when the IOTIME register is read. This bit is updated regardless of the TIntEN value. |

### 6.4.5 Timer Value Register (IOTVALx)

This register contains the running value for timer "x."

| Bit(s) | Symbol | Description          |

|--------|--------|----------------------|

| 15:0   | Count  | Tick generator count |

| 31:16  | Unused | Read as 0            |

### 6.4.6 Beeper Control Register (IOBEEP)

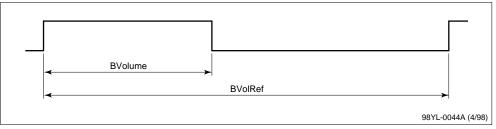

The beeper section generates a sound by dividing the system clock by BFreq, which sets the pitch. The period of the generated sound is subsequently divided into a high period and a low period, thus providing a variable volume through pulsewidth modulation (PWM).

| Bit(s) | Symbol  | Description                                                                                                                                                                                                                                                         |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:0   | BVolRef | Sets the reference count width for the PWM output. When set to 0, disables the beeper. When set to a value of 2047 (for a 33-MHz system clock), provides pulse-width modulation with 11 bits of resolution and an output frequency in the range of 16 Hz to 16 kHz. |

| 20:11  | BVolume | Beeper volume control. Sets the pulse width (and therefore volume). BVolume has a valid range between 0 and BVolRef/2, for minimum to maximum volume, respectively.                                                                                                 |

| 21     | Unused  | Read as 0                                                                                                                                                                                                                                                           |

| 31:22  | BFreq   | Beeper frequency divisor. Sets the pitch of the beeper to CLK/(BFreq x BVolRef).                                                                                                                                                                                    |

Figure 4. Pulse Width Modulation

6.5

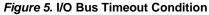

### I/O Bus Interface Controller

#### 6.5.1 Overview

The I/O bus within the VRc4372 controller is a mostly demultiplexed ISA-like bus that controls devices with up to 24 bits of address and up to 16 bits of data. The timing for I/O bus cycles is provided by the PCI CLK.

The I/O devices controlled by the VRc4372 controller are assigned a 256-MB memory region, located at the address specified by the IOADD register in the PCI header. This region is further divided into 16 subregions of 16 MB each. The first 10 subregions are assigned to the chip-select signals CS[9:0]. The next three subregions are assigned to read and write chip-select pairs CPRD[2:0] and CPWR[2:0]. The remaining three subregions are reserved for future use. Each subregion can host several external devices by decoding the lower address bits (starting with A23). To facilitate this additional decoding, the software should enforce fixed addresses on these lower bits. Along with these 16 addressable subregions, the I/O bus is also used for DMA transfers under the control of four DMA channels.

Table 21. Chip-Select Memory Map and Profile Register Assignment

| A[27:0]                                                   | Chip-Select or DMA Channel | Profile Register |  |

|-----------------------------------------------------------|----------------------------|------------------|--|

| 000 0000–0FF FFFF                                         | CS0                        | IOPROF_00        |  |

| 100 0000–1FF FFFF                                         | CS1                        | IOPROF_01        |  |

| 200 0000–2FF FFFF                                         | CS2                        | IOPROF_02        |  |

| 300 0000–3FF FFFF                                         | CS3                        | IOPROF_03        |  |

| 400 0000–4FF FFFF                                         | CS4                        | IOPROF_04        |  |

| 500 0000–5FF FFFF                                         | CS5                        | IOPROF_05        |  |

| 600 0000–6FF FFFF                                         | CS6                        | IOPROF_06        |  |

| 700 0000–7FF FFFF                                         | CS7                        | IOPROF_07        |  |

| 800 0000–8FF FFFF                                         | CS8                        | IOPROF_08        |  |

| 900 0000–9FF FFFF                                         | CS9                        | IOPROF_09        |  |

| A00 0000–AFF FFFF                                         | CP0                        | IOPROF_0A        |  |

| B00 0000-BFF FFFF                                         | CP1                        | IOPROF_0B        |  |

| C00 0000-CFF FFFF                                         | CP2                        | IOPROF_0C        |  |

| D00 0000-FFF FFFF                                         | _                          | Reserved         |  |

| _                                                         | DMA0                       | IOPROF_10        |  |

| _                                                         | DMA1                       | IOPROF_11        |  |

| _                                                         | DMA2                       | IOPROF_12        |  |

| _                                                         | DMA3                       | IOPROF_13        |  |

| _                                                         | _                          | Reserved         |  |

| Note: No addresses are assigned to the four DMA channels. |                            |                  |  |

### 6.5.2 Signal and Pin Descriptions

The general interface of the I/O bus consists of output, input, and bidirectional pins. Unless otherwise specified, all outputs are clocked directly from the rising edge of the PCI CLK signal and do not float between valid accesses. Some outputs have programmable inversion capabilities controllable through the IOPOL register.

| Signal Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOA[7:0]    | These eight output pins drive the least-significant eight bits of the byte address during 8- and 16-bit-wide I/O bus accesses. These lines are driven valid during the first CLK cycle of a valid I/O bus access and remain valid until the completion of the same I/O bus access. Between valid I/O bus accesses, the last address on the bus is held.                                                                                                                                                                                                                                                                                                                                                   |

| IOD[15:0]   | These 16 bidirectional pins implement a multiplexed address and data bus. During the first CLK cycle of a valid I/O bus access, the IOD bus (bit A[23:8] in the IOPROF_xx register of a region) can be configured to output the most significant 16 address bits (IOA[23:8]). During all subsequent CLK cycles of a valid I/O bus access, this bus is used for data transfers. Turnaround cycles are enforced between the address phase and the first data read phase in systems that use the $\overline{\text{BUFOE}}$ pin. To avoid contention in other systems with fast devices, either disable the address phase (bit A[23:8] in the IOPROF_xx register) or program the $\overline{\text{RD}}$ line. |

| НВЕ         | This output pin acts as a high-byte enable during accesses to 16-bit devices. It remains deasserted 1) during accesses to 8-bit devices and 2) during accesses to 16-bit devices that do not access the most-significant IOD bus byte. This signal is asserted during most-significant bit (MSB) access to 16-bit devices, has the same timing as the IOA[7:0] bus, and is held in its last state between valid I/O bus accesses.                                                                                                                                                                                                                                                                         |

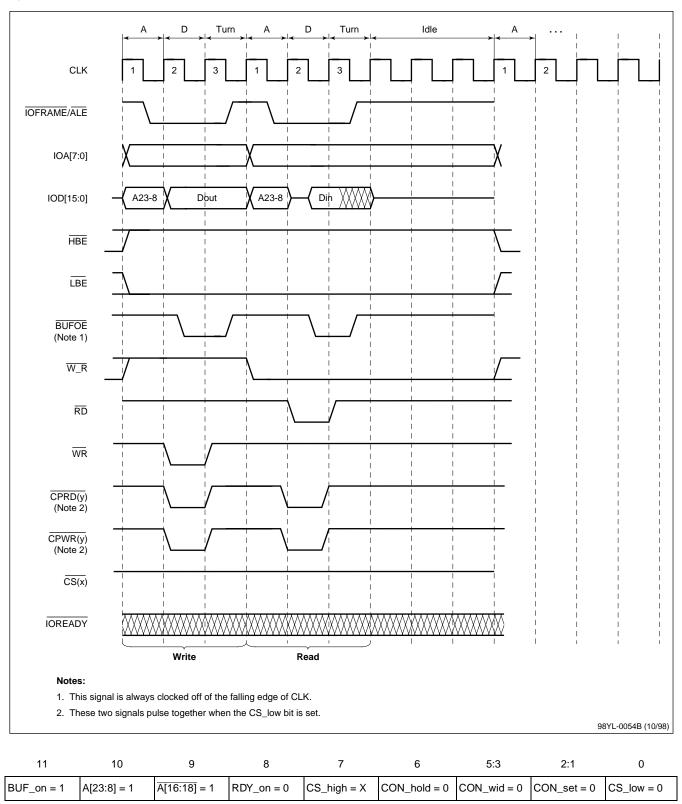

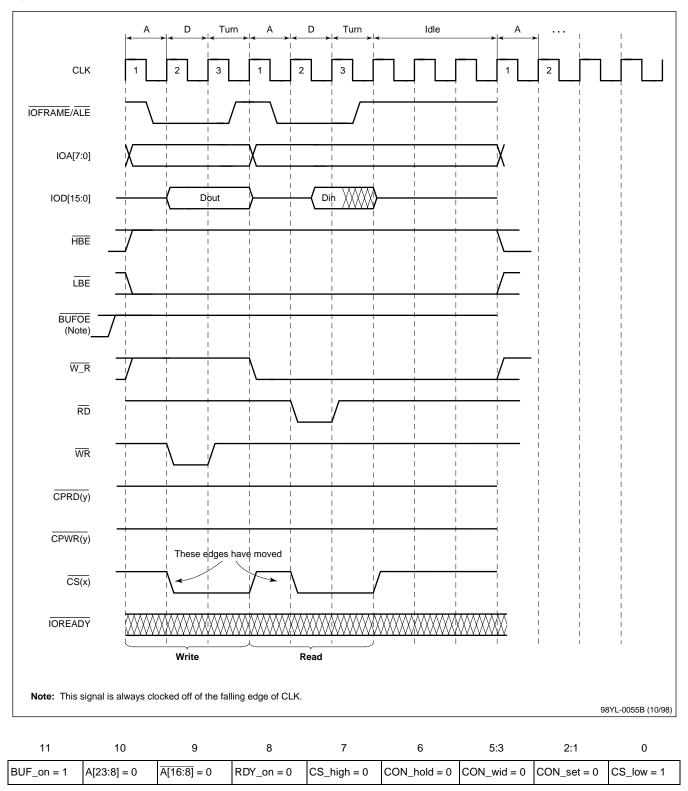

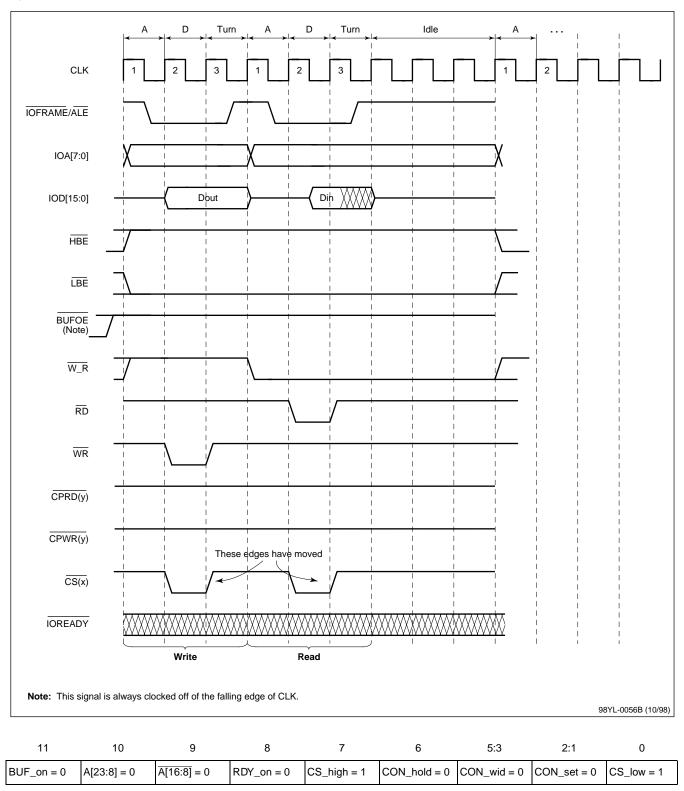

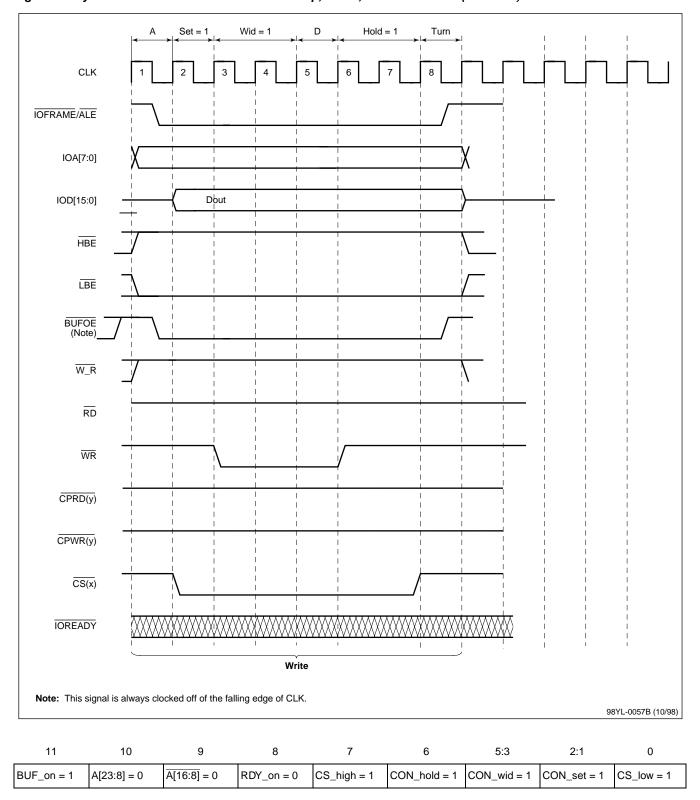

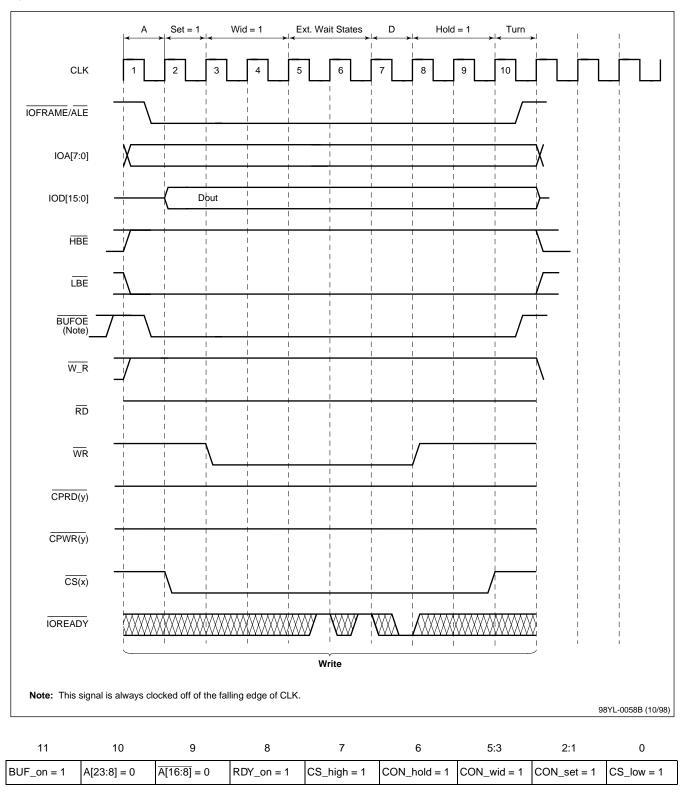

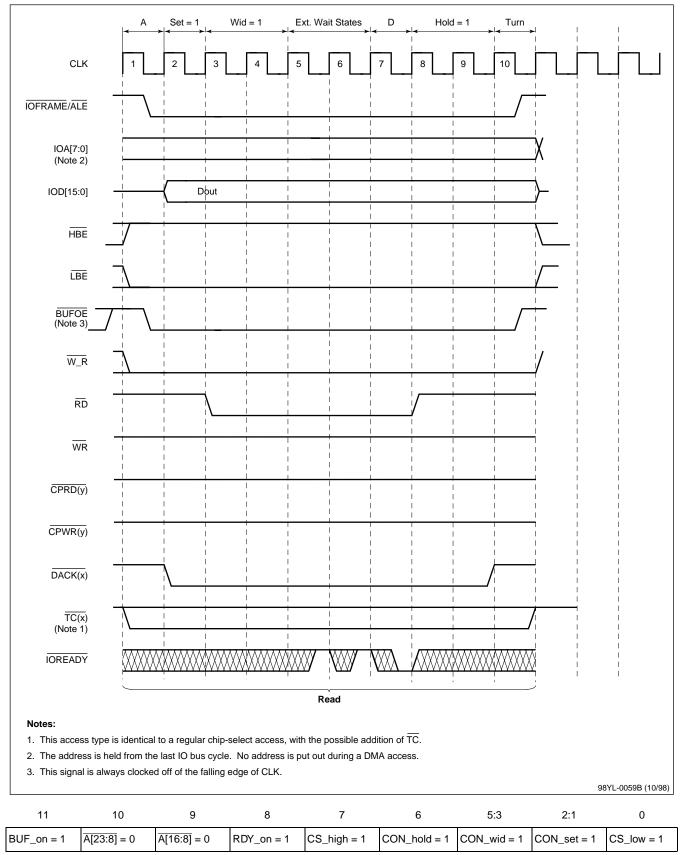

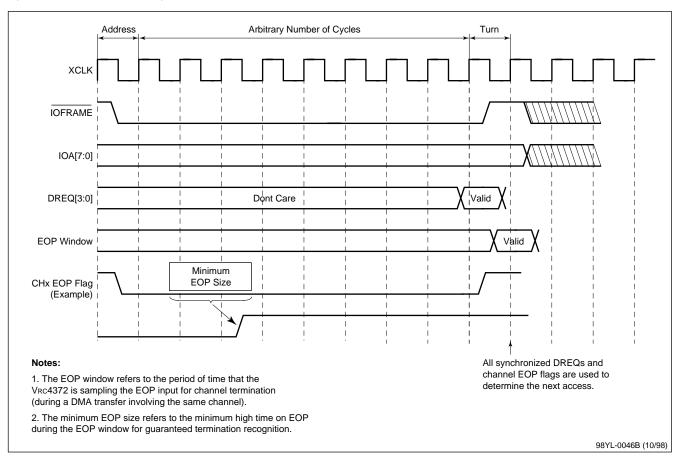

| <u>LBE</u>  | This output pin acts as a low-byte enable during accesses to 8- and 16-bit devices. It is asserted during any valid I/O bus access that requires data from the least-significant IOD bus byte (IOD[7:0]). This signal has the same timing as the IOA[7:0] bus and is held in its last state between valid I/O bus accesses.                                                                                                                                                                                                                                                                                                                                                                               |