# VISIA VES96( Single Chip Channel Decoder

# **DVB-T Single-Chip Solution**

#### O V E R V I E W

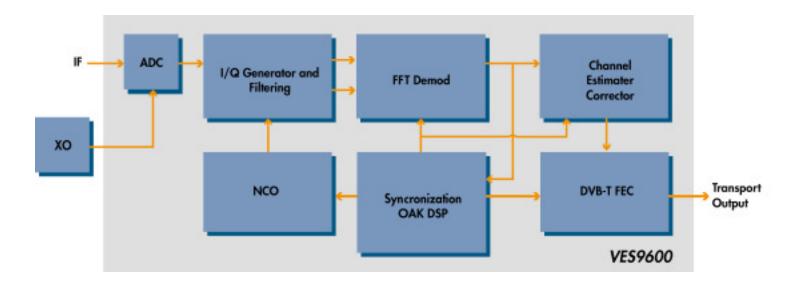

The ViSTA VES9600 digital terrestrial television decoder chip is designed to demodulate 2K and 8K OFDM broadcast transmissions based on the ETSI 300 744 specification.

The VES9600 contains all the functionality required to demodulate an COFDM signal in the UHF/VHF band, perform necessary channel and bit stream decoding, including forward error correction, and generate an MPEG2 transport stream output.

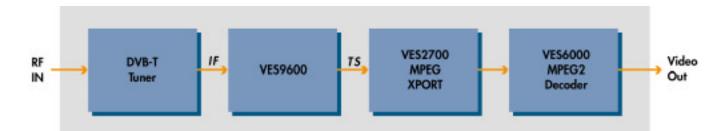

The VES9600 integrates seamlessly with other components of the ViSTA solution for Set-Top Box products and integrated digital television designs including the VES2700 MPEG Transport Demux and the VES6100 MPEG2 Decoder.

The VES9600 implements algorithms which enhance stability and performance in environments with strong co-channel and adjacent channel interference as well as other severe terrestrial channel characteristics.

Also, a common phase estimator (CPE) is implemented to reduce the effects of tuner phase noise.

The VES9600 integrates a digital clock recovery circuit eliminating the need for an external VCXO. Also the device integrates an analog-to-digital converter, simplifying external logic requirements.

Validated API firmware is also available with the VES9600. API firmware greatly reduces the need for system software development and allows for system design flexibility and softwaretransparent product upgrades.

### <u>Block Diagram</u>

#### FEATURES

- Bandwidth variable 8MHz/7MHz/ 6MHz

- Supports both 2K FFT and 8K FFT

- Supports QPSK, 16-QAM and 64-QAM

- Hierarchical and not-hierarchical modes

- Implements all required Guard Intervals (1/32, 1/16, 1/8, 1/4)

- Implements an embedded OAK DSP for synchronization

- Channel response estimation and correction

- Enhanced features implemented to handle CCI/ACI

- Provides complete DVB-T FEC

- Embedded API firmware

- I<sup>2</sup>C serial bus interface

- OFDM de-interleaving

- QPSK/QAM demapping; symbol and bit de-interleaving

- Viterbi decoder

- Constraint length K=7 with G1=171 base 8, G2=133 base 8

- BER monitor

- Forney convolutional deinterleaving of depth 12

- Reed Solomon decoder (204,188)

## <u>Typical Application</u>

All brands, product names, and company names are trademarks or registered trademarks of their respective owners.

With respect to the information in this document, VLSI Technology, Inc. (VLSI) makes no guarantee or warranty of its accuracy or that the use of such information will not infringe upon the intellectual rights of third parties. VLSI shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it and no patent or other license is implied hereby. This document does not in any way extend or modify VLSI's warranty on any product beyond that set forth in its standard terms and conditions of sale. VLSI reserves the right to make changes in its products and specifications at any time and without notice.

LIFE SUPPORT APPLICATIONS:

VLSI's products are not intended for use as critical components in life support appliances, devices, or systems, in which the failure of a VLSI product to perform could be expected to result in personal injury. For update information, please visit our Web site at

http://www.vlsi.com or call the Worldwide Headquarters at +1-408-434-3100 or the European Headquarters at +49/89/627 06-0

VLSI Technology, Inc. 1109 McKay Drive San Jose, CA 95131 USA