# Single-Chip MPEG2 Audio/Video Decoder Subsystem

### OVERVIEW

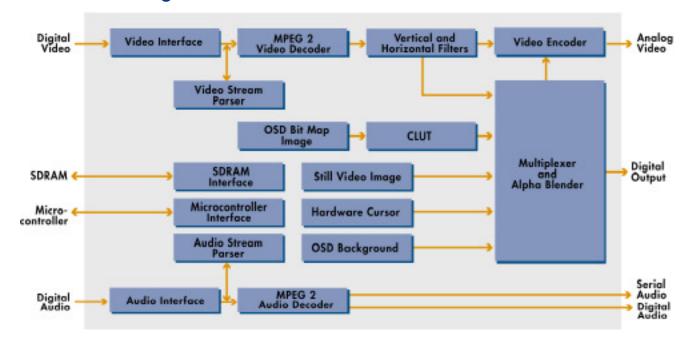

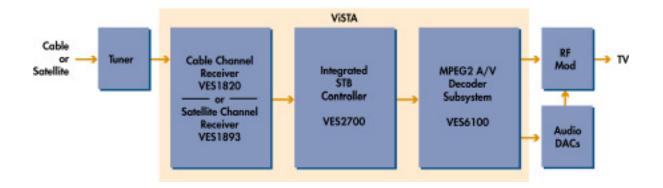

As part of VLSI's industry leading integrated Set-Top Architecture (ViSTA), the ViSTA VES6100 integrates all functions of a high performance, real-time MPEG2 Audio/Video Decoder Subsystem on a single chip. The VES6100 combines the features of the ViSTA VES6000 (MPEG2 Audio/Video Decoder), the ViSTA VES7000 (NTSC/PAL Encoder), and additional new feautres such as enhanced onscreen display (OSD) engine and SDRAM support. The VES6100 enables state-of-the-art system design solutions for direct broadcast satellite (DBS) receivers, digital TV, DVD (Digital Versatile Disk) and digital systems.

On the MPEG2 decoding side, the VES6100 offers SDRAM support and an enhanced OSD engine. On the digital encoder side, the VES6100 adds both the ability of decoding SECAM, and supporting closed captioning, teletext, and Macrovision 7.0 anti-copy protection.

The VES6100 provides a high performance interface to stereo audio DAC's and industry-standard 8-bit and 16-bit microcontrollers. It supports full NTSC, PAL, or SECAM decoding with full-screen 4-bit per pixel OSD with 16 MB DRAM, and supports up to 32 MB DRAM depending upon required resolution and modes.

The MPEG2 decoder incorporates an integrated clock-synthesizer, a microprogrammable RISC architecture,

true-color OSD, and Synchronous DRAM support, in addition to the ability to decode full MPEG2 with fullscreen OSD easily within 16 Mbits of DRAM.

An integrated clock synthesizer eliminates the need for an external clock chip. The micro-programmable RISC architecture allows for customization and flexibility within the design itself while the 256-color and true-color OSD features provide enhanced visuals.

The video interface performs horizontal resampling of both luminance and chrominance data, provides vertical filtering to construct 4:2:2 CCIR 656 formatted video data, and interfaces

## <u>Block Diagram</u>

with the on-screen display unit, providing a display bitmap for super-imposing onto display video. It supports two modes, base mode (1 bit/pixel, 2 bits/pixel, 4 bits/pixel, 8 bits/pixel, support for transparencies, and 256-level Alpha-blending) and true color mode.

The video encoder supports NTSC, PAL, and SECAM standards. It has been designed to accept input video data that is compliant with CCIR-601/656, supporting both 8-bit 4:2:2 and 24-bit 4:4:4 formats for RGB and YCrCb.

The color matrix is designed to support a wide variety of modes and provides the highest quality composite output signal. Two-times oversampling of the output signals is accomplished by filtering the input signal and reconstructing extra samples in between the existing ones. Three 9-bit resolution output DACs have also been integrated.

### FEATURES

- Fully compliant to MPEG1 (ISO 11172-2) and MPEG2 (ISO/IEC 13818-2) video standards

- Fully compliant to MPEG1 (ISO 11172-3) Layer 1 and Layer 2, and two-channel MPEG2 (ISO/IEC 13818-3) audio standards

- Provides the ability to fully decode **MPEG2 Packetized Elementary** Streams (PES)

- Enhanced on-screen display (OSD) for high-quality graphics

- Has both auto synchronization and manual synchronization modes for design flexibility

- Supports Macrovision 7.0 for anti-copy protection

- Teletext insertion support

- Closed caption insertion support

- Vertical chroma filtering (2-tap) for 4:2:0 to 4:2:2 conversion

- High-level commands and trick modes supported

- · Play, Pause, Freeze, NewChannel, Slow Motion, Scan, Fast Forward, Single Step

- Skip, repeat frame for audio/video synchronization

- Supports NTSC, PAL, and SECAM standards for worldwide application ·50 and 60 Hz NTSC and (M) NTSC ·Versions B, D, G, H, and I of PAL, and (N) PAL

- Internal digital subcarrier synthesizer

- System clock frequency can be set from 24 MHz to 30 Mhz to support slight clock variations

- Three independent video outputs

- Integrated 9-bit resolution low-power output DACs

- x2 oversampling of the output signals

- 160 MOFP package

- 0.35 µm CMOS technology

# <u>Typical Application</u>

All brands, product names, and company names are trademarks or registered trademarks of their respective owners.

With respect to the information in this document, VLSI Technology, Inc. (VLSI) makes no guarantee or warranty of its accuracy or that the use of such information will not infringe upon the intellectual rights of third parties. VLSI shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it and no patent or other license is implied hereby. This document does not in any way extend or modify VLSI's warranty on any product beyond that set forth in its standard terms and conditions of sale. VLSI reserves the right to make changes in its products and specifications at any time and without notice.

LIFE SUPPORT APPLICATIONS:

VLSI's products are not intended for use as critical components in life support appliances, devices, or systems, in which the failure of a VLSI product to perform could be expected to result in personal injury. For update information, please visit our Web site at

or call the Worldwide Headquarters at +1-408-434-3100 or the European Headquarters at +49/89/627 06-0

© 1998 VLSI Technology, Inc. Printed in USA. Document Control: PB-V/iSTA-6100 V1.3 Mai 98

VLSI Technology, Inc. 1109 McKay Drive San Jose, CA 95131 USA