# VISTA VES2030

# MPEG 2 Transport Demultiplexer Subsystem

#### OVERVIEW

The VES2030 MPEG 2 Transport

Demultiplexer Subsystem is part of the VISTA™ family, (VISI Integrated Set-Top Architecture). The VES2030 handles MPEG 2 transport streams and Packetized Elementary Streams (PES) of up to 60 Mbps, parses the streams to frame the MPEG 2 packets, and then routes the extracted packets to either an MPEG 2 video decoder, MPEG audio decoder, or to a host microcontroller for downstream processing. The

VES2030 integrates the functionality of the VES0010 DVB descrambler supporting descrambling at both the transport level and the PES level. The device can descramble data on the fly and provides an 8 bit input and output bus between the RISC core and the descrambler block. The VES2030 also performs Program Clock Reference (PCR) recovery to maintain audio and video synchronization, acts as the DRAM controller for not only itself, but also for the host microcontroller and

MPEG decoder, thus reducing overall system DRAM requirements and cost. The VES2030 comes with necessary firmware, and is packaged in a 208-lead MQFP package. Features also include a 32-bit Cyclical Redundancy Check (CRC) engine together with robust error handling with error source for interrupt status and interrupt mask. The VES2030 also provides direct teletext output.

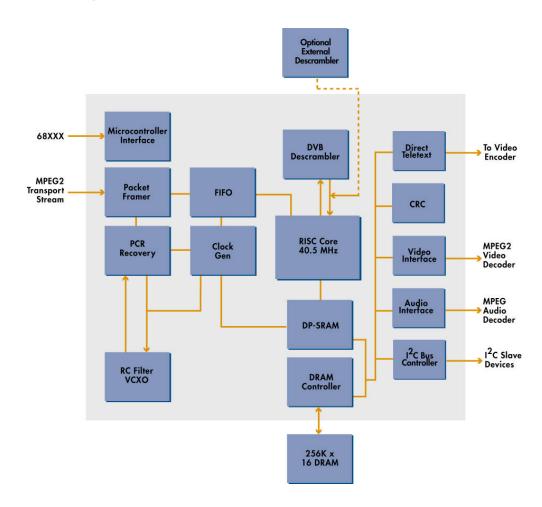

### Block Diagram

#### FEATURES

- Accepts MPEG 2 system transport streams up to 60 Mbps

- Handles MPEG 2 transport and Packetized Elementary Stream (PES)

- Support for up to 32 PIDs

- Integrated high performance microprogrammable 40.5 MHz RISC

- Glueless interface to VES6100 and industry standard MPEG decoders

- Support for Motorola 68XXX microcontrollers

- Direct interface to VES1893 and VES1820 channel decoders

- Integrated Program Clock Reference (PCR) recovery

- Integrated DRAM controller

- · Functions as the memory controller for the host microcontroller

- Channel rate and extended channel rate buffering

- CRC Engine

- Direct Teletext Output

- DVB-complaint Descrambler

- · Compliance to DVB Common **Scrambling Specifications**

- · Handles transport level or PES level descrambling

- · New Common Key for each transport packet

- Lost packet detection and handling

- PTS, PSI, and CAS management

- EMM and ECM filtering

- I<sup>2</sup>C Bus support

- 208 MQFP

- 0.5 µm CMOS

## <u>Typical Application</u>

All brands, product names, and company names are trademarks or registered trademarks of their respective owners.

With respect to the information in this document, VLSI With respect to the information in this document, VISI Technology, Inc. (VISI) makes no guarantee or warranty of its accuracy or that the use of such information will not infringe upon the intellectual rights of third parties. VISI shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it and no patent or other license is implied hereby. This document does not in any way extend or modify VISI's warranty on any product beyond that set forth in its standard terms and conditions of sale. VISI reserves the right to make changes in its products and specifications at any time and without notice. LIFE SUPPORT APPLICATIONS:

VISI's products are not intended for use as critical components in life support appliances, devices, or systems, in which the failure of a VISI product to perform could be expected to result in personal injury.

For update information, please visit our Web site: http://www.vlsi.com

© 1998 VLSI Technology, Inc. Printed in USA Document Control: PB-ViSTA2030 V1.1

January 98

VLSI Technology, Inc. 1109 McKay Drive San Jose, CA 95131