# V54C365804VD(L) HIGH PERFORMANCE 143/133/125 MHz 3.3 VOLT 8M X 8 SYNCHRONOUS DRAM 4 BANKS X 2Mbit X 8

### **PRELIMINARY**

|                                                                    | 7      | 75     | 8PC     | 8       |

|--------------------------------------------------------------------|--------|--------|---------|---------|

| System Frequency (f <sub>CK</sub> )                                | 143MHz | 133MHz | 125 MHz | 125 MHz |

| Clock Cycle Time (t <sub>CK3</sub> )                               | 7 ns   | 7.5 ns | 8 ns    | 8 ns    |

| Clock Access Time (t <sub>AC3</sub> ) $\overline{CAS}$ Latency = 3 | 5.4 ns | 5.4 ns | 6 ns    | 7 ns    |

| Clock Access Time (t <sub>AC2</sub> ) CAS Latency = 2              | 5.5 ns | 6 ns   | 6 ns    | 7 ns    |

#### Features

- 4 banks x 2Mbit x 8 organization

- High speed data transfer rates up to 143 MHz

- Full Synchronous Dynamic RAM, with all signals referenced to clock rising edge

- Single Pulsed RAS Interface

- Data Mask for Read/Write Control

- Four Banks controlled by BA0 & BA1

- Programmable CAS Latency: 2, 3

- Programmable Wrap Sequence: Sequential or Interleave

- Programmable Burst Length:

- 1, 2, 4, 8 and full page for Sequential Type

- 1, 2, 4, 8 for Interleave Type

- Multiple Burst Read with Single Write Operation

- Automatic and Controlled Precharge Command

- Random Column Address every CLK (1-N Rule)

- Suspend Mode and Power Down Mode

- Auto Refresh and Self Refresh

- Refresh Interval: 4096 cycles/64 ms

- Available in 54 Pin 400 mil TSOP-II

- LVTTL Interface

- Single +3.3 V ±0.3 V Power Supply

### Description

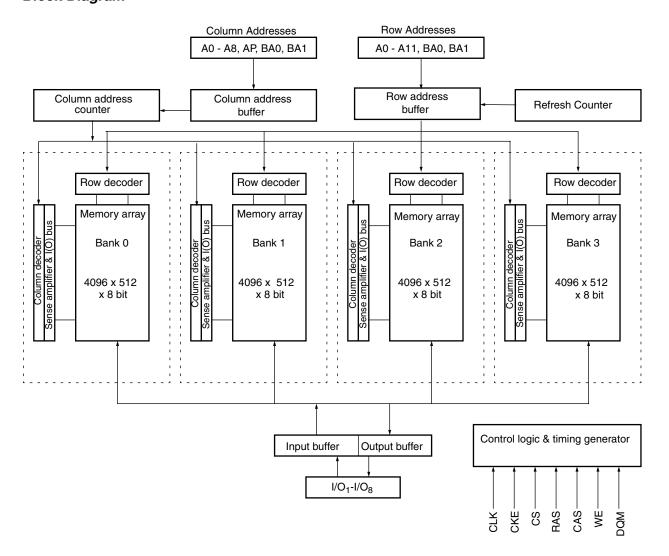

The V54C365804VD(L) is a four bank Synchronous DRAM organized as 4 banks x 2Mbit x 8. The V54C365804VD(L) achieves high speed data transfer rates up to 143 MHz by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock

All of the control, address, data input and output circuits are synchronized with the positive edge of an externally supplied clock.

Operating the four memory banks in an interleaved fashion allows random access operation to occur at higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 143 MHz is possible depending on burst length,  $\overline{\text{CAS}}$  latency and speed grade of the device.

### **Device Usage Chart**

| Operating            | Package Outline | Access Time (ns) Power |   |   |   |   |   | Temperature<br>Mark |  |

|----------------------|-----------------|------------------------|---|---|---|---|---|---------------------|--|

| Temperature<br>Range | Т               | 7 75 8PC 8 Std.        |   |   |   |   |   |                     |  |

| 0°C to 70°C          | •               | •                      | • | • | • | • | • | Blank               |  |

| Description | Pkg. | Pin Count |

|-------------|------|-----------|

| TSOP-II     | Т    | 54        |

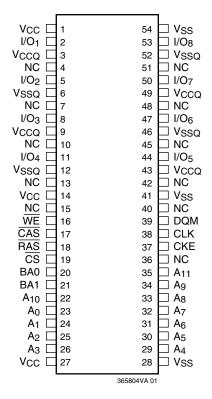

## 54 Pin Plastic TSOP-II PIN CONFIGURATION Top View

### Pin Names

| CLK                                | Clock Input             |

|------------------------------------|-------------------------|

| CKE                                | Clock Enable            |

| CS                                 | Chip Select             |

| RAS                                | Row Address Strobe      |

| CAS                                | Column Address Strobe   |

| WE                                 | Write Enable            |

| A <sub>0</sub> -A <sub>11</sub>    | Address Inputs          |

| BA0, BA1                           | Bank Select             |

| I/O <sub>1</sub> –I/O <sub>8</sub> | Data Input/Output       |

| DQM                                | Data Mask               |

| V <sub>CC</sub>                    | Power (+3.3V)           |

| V <sub>SS</sub>                    | Ground                  |

| V <sub>CCQ</sub>                   | Power for I/O's (+3.3V) |

| V <sub>SSQ</sub>                   | Ground for I/O's        |

| NC                                 | Not connected           |

# Capacitance\*

$T_A = 0$  to  $70^{\circ}C,~V_{CC} = 3.3~V \pm 0.3~V,~f = 1~Mhz$

| Symbol           | Parameter                                         | Max. | Unit |

|------------------|---------------------------------------------------|------|------|

| C <sub>I1</sub>  | Input Capacitance (A0 to A11)                     | 5    | pF   |

| C <sub>I2</sub>  | Input Capacitance RAS, CAS, WE, CS, CLK, CKE, DQM | 5    | pF   |

| C <sub>IO</sub>  | Output Capacitance (I/O)                          | 6.5  | pF   |

| C <sub>CLK</sub> | Input Capacitance (CLK)                           | 4    | pF   |

<sup>\*</sup>Note:Capacitance is sampled and not 100% tested.

## **Block Diagram**

# Signal Pin Description

| Pin            | Type            | Signal | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-----------------|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK            | Input           | Pulse  | Positive<br>Edge | The system clock input. All of the SDRAM inputs are sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CKE            | Input           | Level  | Active High      | Activates the CLK signal when high and deactivates the CLK signal when low, thereby initiates either the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CS             | Input           | Pulse  | Active Low       | $\overline{\text{CS}}$ enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RAS, CAS<br>WE | Input           | Pulse  | Active Low       | When sampled at the positive rising edge of the clock, $\overline{\text{CAS}}$ , $\overline{\text{RAS}}$ , and $\overline{\text{WE}}$ define the command to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A0 - A11       | Input           | Level  |                  | During a Bank Activate command cycle, A0-A11 defines the row address (RA0-RA11) when sampled at the rising clock edge.  During a Read or Write command cycle, A0-An defines the column address (CA0-CAn) when sampled at the rising clock edge.CAn depends from the SDRAM organization:  8M x 8 SDRAM CA0-CA8 (Page Length = 512 bits)  In addition to the column address, A10(=AP) is used to invoke autoprecharge operation at the end of the burst read or write cycle. If A10 is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If A10 is low, autoprecharge is disabled. During a Precharge command cycle, A10(=AP) is used in conjunction with BA0 and BA1 to control which bank(s) to precharge. If A10 is high, all four banks will BA0 and BA1 are used to define which bank to precharge. |

| BA0,<br>BA1    | Input           | Level  | _                | Selects which bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DQx            | Input<br>Output | Level  | _                | Data Input/Output pins operate in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DQM            | Input           | Pulse  | Active High      | The Data Input/Output mask places the DQ buffers in a high impedance state when sampled high. In Read mode, DQM has a latency of two clock cycles and controls the output buffers like an output enable. In Write mode, DQM has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the write operation if DQM is high.  One DQM input is present in x4 and x8 DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                         |

| VCC, VSS       | Supply          |        |                  | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VCCQ<br>VSSQ   | Supply          | _      | _                | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### **Operation Definition**

All of SDRAM operations are defined by states of control signals  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , and DQM at the positive edge of the clock. The following list shows the thruth table for the operation commands.

| Operation                 | Device<br>State     | CKE<br>n-1 | CKE<br>n | cs | RAS | CAS | WE | DQM | A0-9,<br>A11 | A10 | BS0<br>BS1 |

|---------------------------|---------------------|------------|----------|----|-----|-----|----|-----|--------------|-----|------------|

| Row Activate              | Idle <sup>3</sup>   | Н          | Х        | L  | L   | Н   | Н  | Х   | ٧            | ٧   | V          |

| Read                      | Active <sup>3</sup> | Н          | Х        | L  | Н   | L   | Н  | Х   | V            | L   | V          |

| Read w/Autoprecharge      | Active <sup>3</sup> | Н          | Х        | L  | Н   | L   | Н  | Х   | V            | Н   | V          |

| Write                     | Active <sup>3</sup> | Н          | Х        | L  | Н   | L   | L  | Х   | V            | L   | V          |

| Write with Autoprecharge  | Active <sup>3</sup> | Н          | Х        | L  | Н   | L   | L  | Х   | ٧            | Н   | V          |

| Row Precharge             | Any                 | Н          | Х        | L  | L   | Н   | L  | Х   | Х            | L   | ٧          |

| Precharge All             | Any                 | Н          | Х        | L  | L   | Н   | L  | Х   | Х            | Н   | Х          |

| Mode Register Set         | Idle                | Н          | Х        | L  | L   | L   | L  | Х   | ٧            | ٧   | V          |

| No Operation              | Any                 | Н          | Х        | L  | Н   | Н   | Н  | Х   | Х            | Х   | Х          |

| Device Deselect           | Any                 | Н          | Х        | Н  | Х   | Х   | Х  | Х   | Х            | Х   | Х          |

| Auto Refresh              | Idle                | Н          | Н        | L  | L   | L   | Н  | Х   | Х            | Х   | Х          |

| Self Refresh Entry        | Idle                | Н          | L        | L  | L   | L   | Н  | Х   | Х            | Х   | Х          |

| Self Refresh Exit         | Idle                |            |          | Н  | Х   | Х   | Х  |     |              |     |            |

|                           | (Self Refr.)        | L          | Н        | L  | Н   | Н   | Х  | X   | X            | Х   | X          |

| Power Down Entry          | Idle _              |            |          | Н  | Х   | Х   | Х  |     |              |     |            |

|                           | Active <sup>5</sup> | H          | L        | L  | Н   | Н   | Х  | X   | X            | Х   | X          |

| Power Down Exit           | Any                 |            |          | Н  | Х   | Х   | Х  |     |              |     |            |

|                           | (Power<br>Down)     | L          | Н        | L  | Н   | Н   | L  | Х   | X            | X   | X          |

| Data Write/Output Enable  | Active              | Н          | Х        | Х  | Х   | Х   | Х  | L   | Х            | Х   | Х          |

| Data Write/Output Disable | Active              | Н          | Х        | Х  | Х   | Х   | Х  | Н   | Х            | Х   | Х          |

#### Notes:

- V = Valid , x = Don't Care, L = Low Level, H = High Level

CKEn signal is input level when commands are provided, CKEn-1 signal is input level one clock before the commands are provided.

- These are state of bank designated by BS0, BS1 signals.

- Device state is Full Page Burst operation

- 5. Power Down Mode can not entry in the burst cycle. When this command assert in the burst mode cycle device is clock suspend mode.

#### Power On and Initialization

The default power on state of the mode register is supplier specific and may be undefined. The following power on and initialization sequence guarantees the device is preconditioned to each users specific needs. Like a conventional DRAM, the Synchronous DRAM must be powered up and initialized in a predefined manner. During power on, all VCC and VCCQ pins must be built up simultaneously to the specified voltage when the input signals are held in the "NOP" state. The power on voltage must not exceed VCC+0.3V on any of the input pins or VCC supplies. The CLK signal must be started at the same time. After power on, an initial pause of 200 µs is required followed by a precharge of both banks using the precharge command. To prevent data contention on the DQ bus during power on, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. A minimum of eight Auto Refresh cycles (CBR) are also required. These may be done before or after programming the Mode Register. Failure to follow these steps may lead to unpredictable start-up modes.

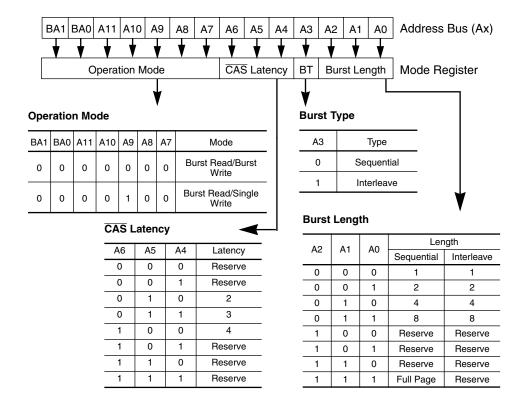

#### Programming the Mode Register

The Mode register designates the operation mode at the read or write cycle. This register is divided into 4 fields. A Burst Length Field to set the length of the burst, an Addressing Selection bit to program the column access sequence in a burst cycle (interleaved or sequential), a CAS Latency Field to set the access time at clock cycle and a Operation mode field to differentiate between normal operation (Burst read and burst Write) and a special Burst Read and Single Write mode. The mode set operation must be done before any activate command after the initial power up. Any content of the mode register can be altered by re-executing the mode set command. All banks must be in precharged state and CKE must be high at least one clock before the mode set operation. After the mode

register is set, a Standby or NOP command is required. Low signals of  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  at the positive edge of the clock activate the mode set operation. Address input data at this timing defines parameters to be set as shown in the previous table.

### Read and Write Operation

When  $\overline{RAS}$  is low and both  $\overline{CAS}$  and  $\overline{WE}$  are high at the positive edge of the clock, a RAS cycle starts. According to address data, a word line of the selected bank is activated and all of sense amplifiers associated to the wordline are set. A  $\overline{CAS}$  cycle is triggered by setting  $\overline{RAS}$  high and  $\overline{CAS}$  low at a clock timing after a necessary delay,  $t_{RCD}$ , from the  $\overline{RAS}$  timing.  $\overline{WE}$  is used to define either a read  $\overline{WE} = H$ ) or a write  $\overline{WE} = L$ ) at this stage.

SDRAM provides a wide variety of fast access modes. In a single CAS cycle, serial data read or write operations are allowed at up to a 143 MHz data rate. The numbers of serial data bits are the burst length programmed at the mode set operation, i.e., one of 1, 2, 4, 8 and full page. Column addresses are segmented by the burst length and serial data accesses are done within this boundary. The first column address to be accessed is supplied at the CAS timing and the subsequent addresses are generated automatically by the programmed burst length and its sequence. For example, in a burst length of 8 with interleave sequence, if the first address is '2', then the rest of the burst sequence is 3, 0, 1, 6, 7, 4, and 5.

Full page burst operation is only possible using the sequential burst type and page length is a function of the I/O organisation and column addressing. Full page burst operation do not self terminate once the burst length has been reached. In other words, unlike burst length of 2, 3 or 8, full page burst continues until it is terminated using another command.

### Address Input for Mode Set (Mode Register Operation)

Similar to the page mode of conventional DRAM's, burst read or write accesses on any column address are possible once the RAS cycle latches the sense amplifiers. The maximum t<sub>RAS</sub> or the refresh interval time limits the number of random column accesses. A new burst access can be done even before the previous burst ends. The interrupt operation at every clock cycles is supported. When the previous burst is interrupted, the remaining addresses are overridden by the new address with the full burst length. An interrupt which accompanies

with an operation change from a read to a write is possible by exploiting DQM to avoid bus contention.

When two or more banks are activated sequentially, interleaved bank read or write operations are possible. With the programmed burst length, alternate access and precharge operations on two or more banks can realize fast serial data access modes among many different pages. Once two or more banks are activated, column to column interleave operation can be done between different pages.

### Burst Length and Sequence:

| Burst<br>Length | Starting Address<br>(A2 A1 A0)                | Seque                                | Sequential Burst Addressing (decimal)                |                                      |                                      |                                      |                                      | lı                                   | Interleave Burst Addressing (decimal) |     |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |

|-----------------|-----------------------------------------------|--------------------------------------|------------------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------------------------|-----|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| 2               | xx0<br>xx1                                    |                                      |                                                      |                                      | 0,<br>1,                             |                                      |                                      |                                      |                                       |     | 0, 1<br>1, 0                         |                                      |                                      |                                      |                                      |                                      |                                      |                                      |

| 4               | x00<br>x01<br>x10<br>x11                      |                                      | 0, 1, 2, 3<br>1, 2, 3, 0<br>2, 3, 0, 1<br>3, 0, 1, 2 |                                      |                                      |                                      |                                      |                                      |                                       |     |                                      | 1                                    | ), 1,<br>, 0,<br>2, 3,<br>3, 2,      | 2, 3<br>3, 2<br>0, 1                 | •                                    |                                      |                                      |                                      |

| 8               | 000<br>001<br>010<br>011<br>100<br>101<br>110 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>0                 | 2<br>3<br>4<br>5<br>6<br>7<br>0<br>1 | 3<br>4<br>5<br>6<br>7<br>0<br>1<br>2 | 4<br>5<br>6<br>7<br>0<br>1<br>2<br>3 | 5<br>6<br>7<br>0<br>1<br>2<br>3<br>4 | 6<br>7<br>0<br>1<br>2<br>3<br>4<br>5 | 7<br>0<br>1<br>2<br>3<br>4<br>5<br>6  |     | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 1<br>0<br>3<br>2<br>5<br>4<br>7<br>6 | 2<br>3<br>0<br>1<br>6<br>7<br>4<br>5 | 3<br>2<br>1<br>0<br>7<br>6<br>5<br>4 | 4<br>5<br>6<br>7<br>0<br>1<br>2<br>3 | 5<br>4<br>7<br>6<br>1<br>0<br>3<br>2 | 6<br>7<br>4<br>5<br>2<br>3<br>0<br>1 | 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 |

| Full<br>Page    | nnn                                           | Cn, Cn+1, Cn+2,                      |                                                      |                                      |                                      |                                      |                                      |                                      | not                                   | sup | por                                  | ted                                  |                                      |                                      |                                      |                                      |                                      |                                      |

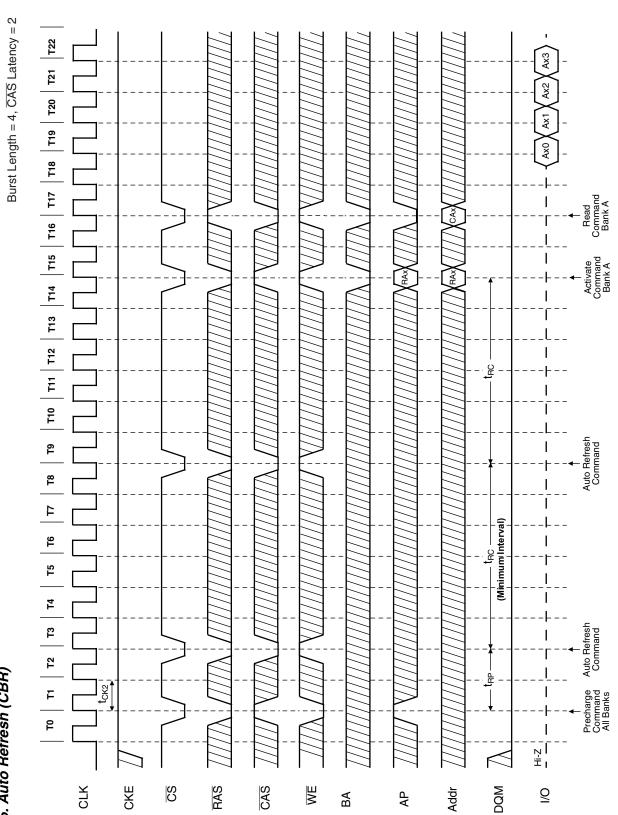

#### Refresh Mode

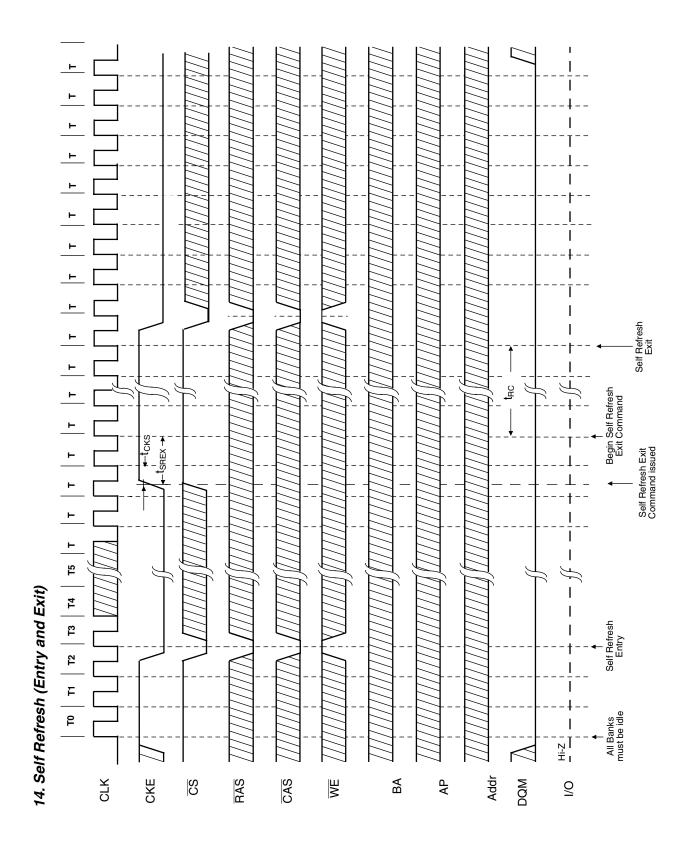

SDRAM has two refresh modes, Auto Refresh and Self Refresh. Auto Refresh is similar to the CAS-before-RAS refresh of conventional DRAMs. All of banks must be precharged before applying any refresh mode. An on-chip address counter increments the word and the bank addresses and no bank information is required for both refresh modes.

The chip enters the Auto Refresh mode, when RAS and CAS are held low and CKE and WE are held high at a clock timing. The mode restores word line after the refresh and no external precharge command is necessary. A minimum tRC time is required between two automatic refreshes in a burst refresh mode. The same rule applies to any access command after the automatic refresh operation.

The chip has an on-chip timer and the Self Refresh mode is available. It enters the mode when  $\overline{RAS}$ ,  $\overline{CAS}$ , and CKE are low and  $\overline{WE}$  is high at a clock timing. All of external control signals including the clock are disabled. Returning CKE to high enables the clock and initiates the refresh exit operation. After the exit command, at least one  $t_{RC}$  delay is required prior to any access command.

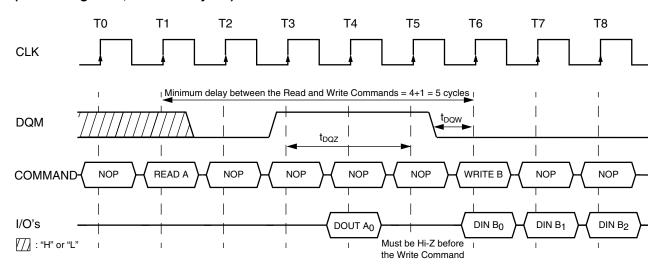

### **DQM Function**

DQM has two functions for data I/O read and write operations. During reads, when it turns to "high" at a clock timing, data outputs are disabled and become high impedance after two clock delay (DQM Data Disable Latency  $t_{DQZ}$ ). It also provides

a data mask function for writes. When DQM is activated, the write operation at the next clock is prohibited (DQM Write Mask Latency  $t_{DQW}$  = zero clocks).

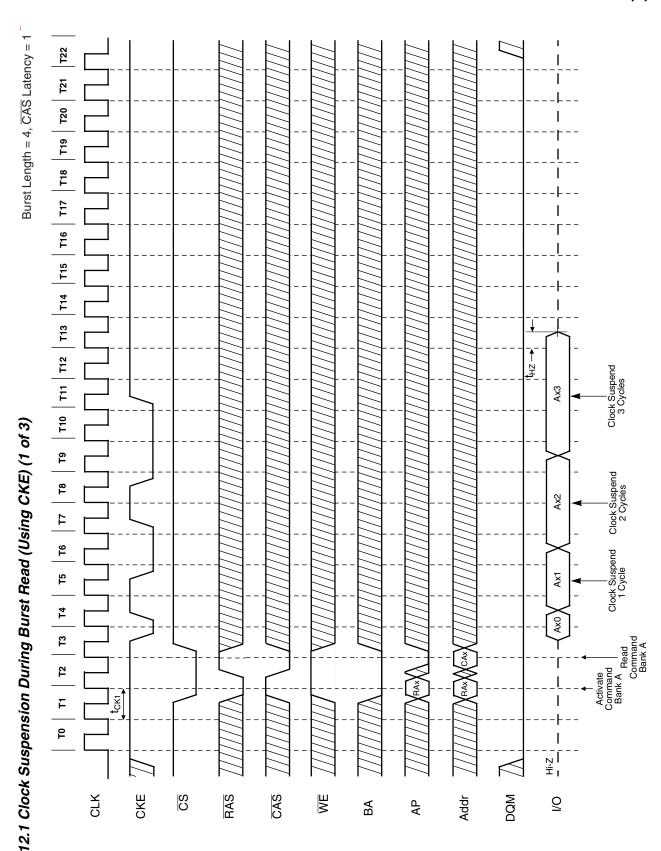

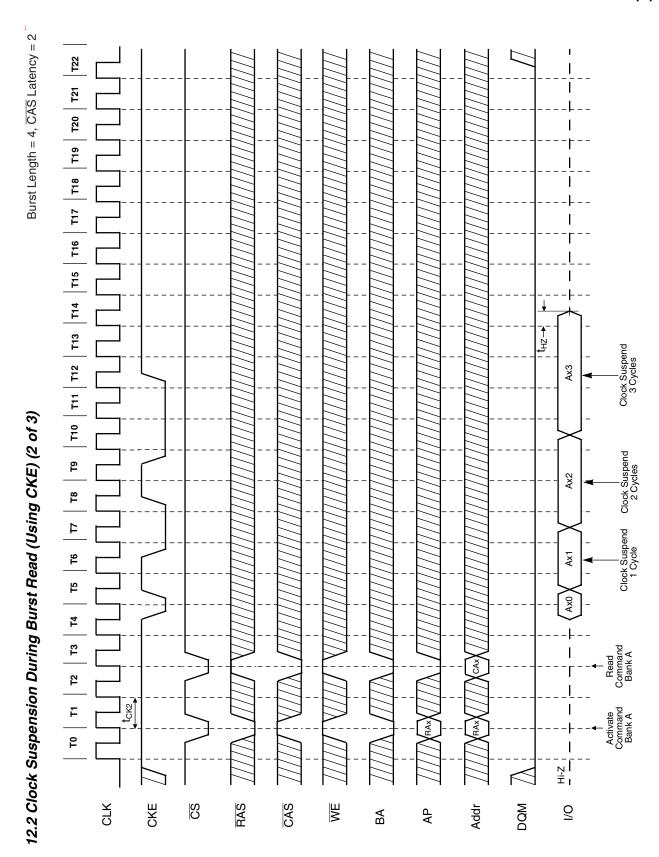

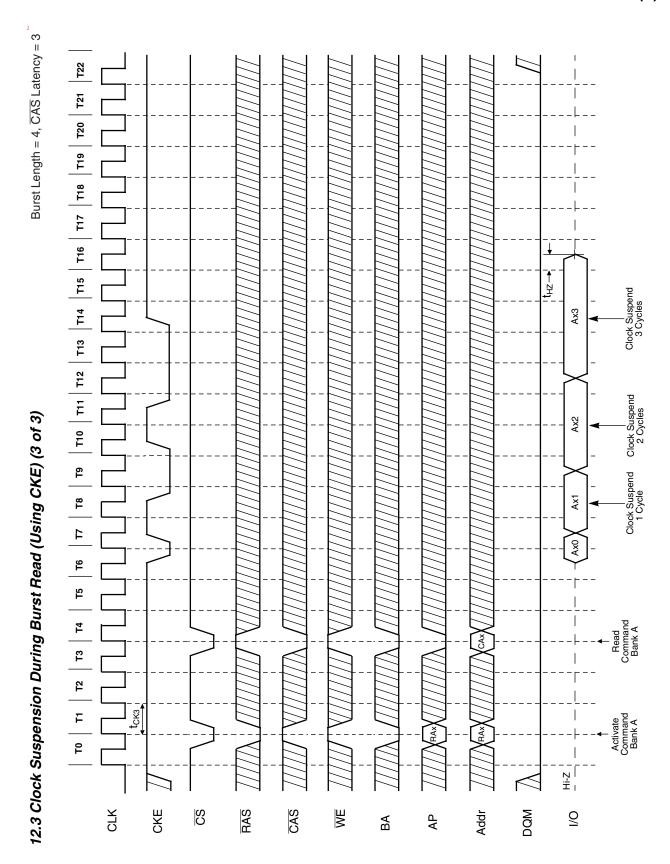

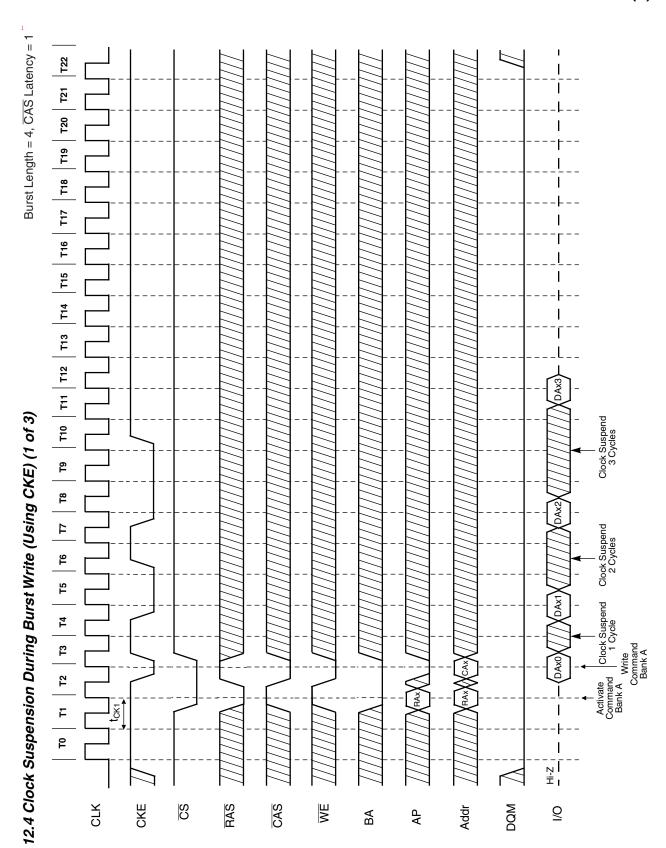

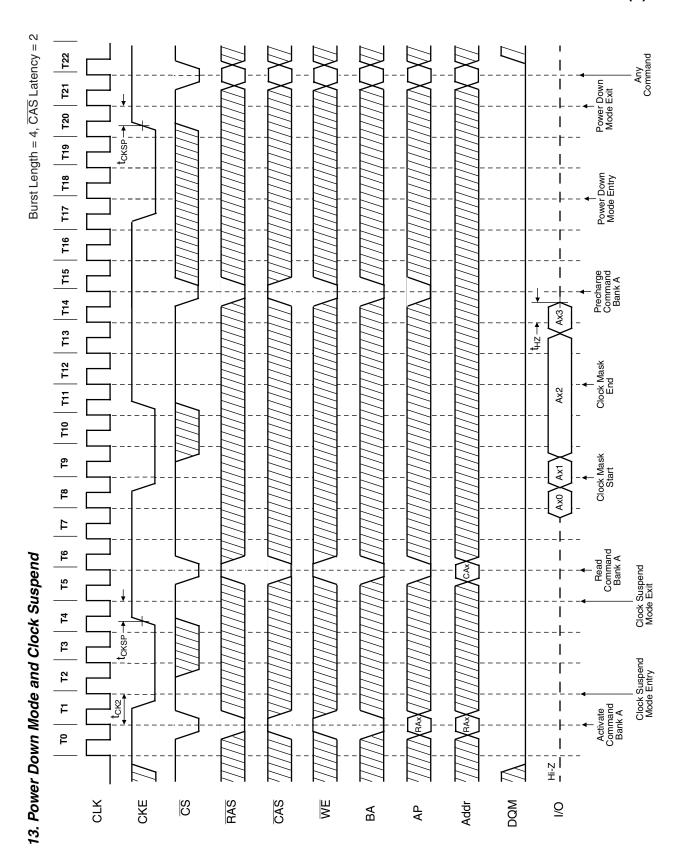

#### Suspend Mode

During normal access mode, CKE is held high enabling the clock. When CKE is low, it freezes the internal clock and extends data read and write operations. One clock delay is required for mode entry and exit (Clock Suspend Latency  $t_{CSL}$ ).

#### **Power Down**

In order to reduce standby power consumption, a power down mode is available. All banks must be precharged and the necessary Precharge delay (trp) must occur before the SDRAM can enter the Power Down mode. Once the Power Down mode is initiated by holding CKE low, all of the receiver circuits except CLK and CKE are gated off. The Power Down mode does not perform any refresh operations, therefore the device can't remain in Power Down mode longer than the Refresh period (tref) of the device. Exit from this mode is performed by taking CKE "high". One clock delay is required for mode entry and exit.

#### Auto Precharge

Two methods are available to precharge SDRAMs. In an automatic precharge mode, the CAS timing accepts one extra address, CA10, to determine whether the chip restores or not after the

operation. If CA10 is high when a Read Command is issued, the **Read with Auto-Precharge** function is initiated. The SDRAM automatically enters the precharge operation one clock before the last data out for  $\overline{\text{CAS}}$  latencies 2, two clocks for  $\overline{\text{CAS}}$  latencies 3 and three clocks for CAS latencies 4. If CAS10 is high when a Write Command is issued, the **Write with Auto-Precharge** function is initiated. The SDRAM automatically enters the precharge operation a time delay equal to  $t_{WR}$  (Write recovery time) after the last data in.

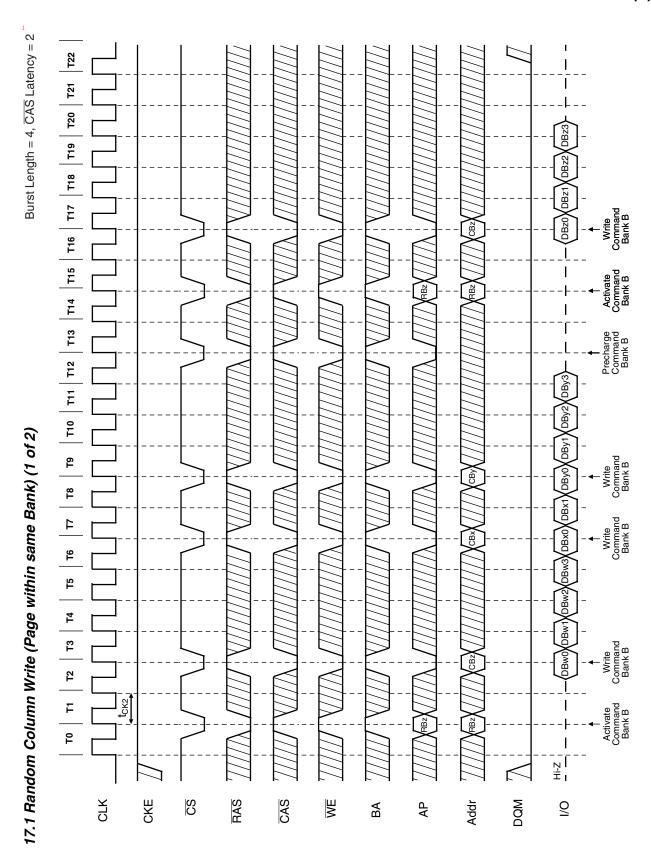

### Precharge Command

There is also a separate precharge command available. When  $\overline{\text{RAS}}$  and  $\overline{\text{WE}}$  are low and  $\overline{\text{CAS}}$  is high at a clock timing, it triggers the precharge operation. Three address bits, BA0, BA1 and A10 are used to define banks as shown in the following list. The precharge command can be imposed one clock before the last data out for CAS latency = 2, two clocks before the last data out for CAS latency = 3 and three clocks before the last data out for CAS latency= 4. Writes require a time delay twr from the last data out to apply the precharge command.

Bank Selection by Address Bits:

| A10 | BA0 | BA1 |           |

|-----|-----|-----|-----------|

| 0   | 0   | 0   | Bank 0    |

| 0   | 0   | 1   | Bank 1    |

| 0   | 1   | 0   | Bank 2    |

| 0   | 1   | 1   | Bank 3    |

| 1   | Х   | Х   | all Banks |

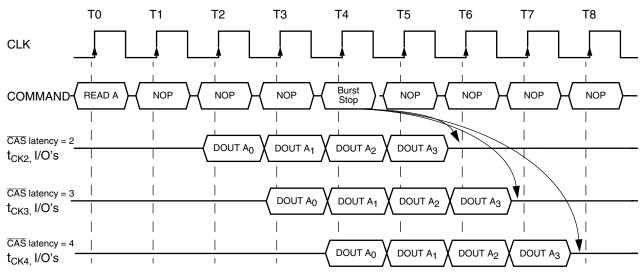

#### **Burst Termination**

Once a burst read or write operation has been initiated, there are several methods in which to terminate the burst operation prematurely. These methods include using another Read or Write Command to interrupt an existing burst operation, use a Precharge Command to interrupt a burst cycle and close the active bank, or using the Burst Stop Command to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank. When interrupting a burst with another Read or Write Command care must be taken to avoid I/O contention. The Burst Stop Command, however, has the fewest restrictions making it the easiest method to use when terminating a burst operation before it has been completed. If a Burst Stop command is issued during a burst write operation, then any residual data from the burst write cycle will be ignored. Data that is presented on the I/O pins before the Burst Stop Command is registered will be written to the memory.

# Absolute Maximum Ratings\*

| Operating temperature range                  | 0 to 70 °C                  |

|----------------------------------------------|-----------------------------|

| Storage temperature range                    | 55 to 150 °C                |

| Input/output voltage0.3                      | to (V <sub>CC</sub> +0.3) V |

| Power supply voltage                         | 0.3 to 4.6 V                |

| Power dissipation                            | 1 W                         |

| Data out current (short circuit)             | 50 mA                       |

| *Note: Stresses above those listed under "Al | solute Maximum              |

| Ratings" may cause permanent dama            |                             |

| Exposure to absolute maximum rating          | conditions for              |

extended periods may affect device reliability.

## Recommended Operation and Characteristics for LV-TTL

$T_A = 0$  to 70 °C;  $V_{SS} = 0$  V;  $V_{CC}$ ,  $V_{CCQ} = 3.3$  V  $\pm 0.3$  V

|                                                                                                                                 |                   | Limit \ |         |      |       |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|---------|------|-------|

| Parameter                                                                                                                       | Symbol            | min.    | max.    | Unit | Notes |

| Input high voltage                                                                                                              | V <sub>IH</sub>   | 2.0     | Vcc+0.3 | V    | 1, 2  |

| Input low voltage                                                                                                               | V <sub>IL</sub>   | - 0.3   | 0.8     | ٧    | 1, 2  |

| Output high voltage (I <sub>OUT</sub> = – 2.0 mA)                                                                               | V <sub>OH</sub>   | 2.4     | -       | ٧    |       |

| Output low voltage (I <sub>OUT</sub> = 2.0 mA)                                                                                  | V <sub>OL</sub>   | _       | 0.4     | V    |       |

| Input leakage current, any input $(0 \text{ V} < \text{V}_{\text{IN}} < 3.6 \text{ V}, \text{ all other inputs} = 0 \text{ V})$ | I <sub>I(L)</sub> | - 5     | 5       | μА   |       |

| Output leakage current (DQ is disabled, 0 V < V <sub>OUT</sub> < V <sub>CC</sub> )                                              | I <sub>O(L)</sub> | - 5     | 5       | μА   |       |

### Note:

All voltages are referenced to V<sub>SS</sub>.

V<sub>IH</sub> may overshoot to V<sub>CC</sub> + 2.0 V for pulse width of < 4ns with 3.3V. V<sub>IL</sub> may undershoot to -2.0 V for pulse width < 4.0 ns with 3.3V. Pulse width measured at 50% points with amplitude measured peak to DC reference.</li>

**Operating Currents** (T<sub>A</sub> = 0 to 70°C, V<sub>CC</sub> =  $3.3V \pm 0.3V$ ) (Recommended Operating Conditions unless otherwise noted)

|        |                                                                                                                                                            |                                                  |     | Ma  |      |     |      |      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----|-----|------|-----|------|------|

| Symbol | Parameter & Test Conditio                                                                                                                                  | n                                                | -7  | -75 | -8PC | -8  | Unit | Note |

| ICC1   | Operating Current  t <sub>RC</sub> = t <sub>RCMIN</sub> , t <sub>RC</sub> = t <sub>CKMIN</sub> . Active-precharge command cycling, without Burst Operation | 1 bank operation                                 | 150 | 140 | 130  | 130 | mA   | 7    |

| ICC2P  | Precharge Standby Current in Power Down Mode                                                                                                               | t <sub>CK</sub> = min.                           | 2   | 2   | 2    | 2   | mA   | 7    |

| ICC2PS | $\overline{CS} = V_{IH}, CKE \le V_{IL(max)}$                                                                                                              | t <sub>CK</sub> = Infinity                       | 1   | 1   | 1    | 1   | mA   | 7    |

| ICC2N  | Precharge Standby Current in Non-Power Down Mode                                                                                                           | t <sub>CK</sub> = min.                           | 45  | 40  | 35   | 35  | mA   |      |

| ICC2NS | CS =V <sub>IH</sub> , CKE≥ V <sub>IL(max)</sub>                                                                                                            | t <sub>CK</sub> = Infinity                       | 5   | 5   | 5    | 5   | mA   |      |

| ICC3   | No Operating Current $t_{CK} = min, \overline{CS} = V_{IH(min)}$                                                                                           | CKE ≥ V <sub>IH(MIN.)</sub>                      | 55  | 50  | 45   | 45  | mA   |      |

| ICC3P  | bank ; active state ( 4 banks)                                                                                                                             | CKE ≥ V <sub>IL(MAX.)</sub><br>(Power down mode) | 8   | 8   | 8    | 8   | mA   |      |

| ICC4   | Burst Operating Current  t <sub>CK</sub> = min  Read/Write command cycling                                                                                 |                                                  | 120 | 120 | 110  | 110 | mA   | 7,8  |

| ICC5   | Auto Refresh Current  t <sub>CK</sub> = min  Auto Refresh command cycling                                                                                  |                                                  | 150 | 140 | 130  | 130 | mA   | 7    |

| ICC6   | Self Refresh Current                                                                                                                                       |                                                  | 1   | 1   | 1    | 1   | mA   |      |

|        | Self Refresh Mode, CKE=0.2V                                                                                                                                | L-version                                        | 500 | 500 | 500  | 500 | μA   |      |

### Notes:

These parameters depend on the cycle rate and these values are measured by the cycle rate under the minimum value of t<sub>CK</sub> and t<sub>RC</sub>. Input signals are changed one time during t<sub>CK</sub>.

These parameter depend on output loading. Specified values are obtained with output open.

# V54C365804VD(L)

AC Characteristics 1,2,3

$T_A$  = 0 to 70 °C;  $V_{SS}$  = 0 V;  $V_{DD}$  = 3.3 V  $\pm$  0.3 V,  $t_T$  = 1 ns

|      |                   |                                                          | Limit Values |            |           |            |         |            |         |           |               |      |

|------|-------------------|----------------------------------------------------------|--------------|------------|-----------|------------|---------|------------|---------|-----------|---------------|------|

|      |                   |                                                          | -7           |            | -75       |            | -8PC    |            | -8      |           | 1             |      |

| #    | Symbol            | Parameter                                                | Min.         | Max.       | Min.      | Max.       | Min.    | Max.       | Min.    | Max.      | Unit          | Note |

| Cloc | k and Clo         | ck Enable                                                | ļ.           |            |           |            |         |            |         |           |               |      |

| 1    | t <sub>CK</sub>   | Clock Cycle Time CAS Latency = 3 CAS Latency = 2         | 7<br>10      | _<br>_     | 7.5<br>10 | _<br>_     | 8<br>10 | _<br>_     | 8<br>12 | _<br>_    | s<br>ns<br>ns |      |

| 2    | t <sub>CK</sub>   | Clock Frequency CAS Latency = 3 CAS Latency = 2          | _<br>_       | 143<br>100 | -<br>-    | 133<br>100 | _<br>_  | 125<br>100 | _<br>_  | 125<br>83 | MHz<br>MHz    |      |

| 3    | t <sub>AC</sub>   | Access Time from Clock  CAS Latency = 3  CAS Latency = 2 | _<br>_       | 5.4<br>5.5 | _<br>_    | 5.4<br>6   | _<br>_  | 6<br>6     | _<br>_  | 7<br>7    | ns<br>ns      | 2, 4 |

| 4    | t <sub>CH</sub>   | Clock High Pulse Width                                   | 2.5          | _          | 2.5       | _          | 3       | _          | 3       | _         | ns            |      |

| 5    | t <sub>CL</sub>   | Clock Low Pulse Width                                    | 2.5          | _          | 2.5       | _          | 3       | _          | 3       | _         | ns            |      |

| 6    | t <sub>T</sub>    | Transition Tim                                           | 0.3          | 1.2        | 0.3       | 1.2        | 0.5     | 10         | 0.5     | 10        | ns            |      |

| Setu | p and Hole        | d Times                                                  |              |            |           |            |         |            |         |           |               |      |

| 7    | t <sub>IS</sub>   | Input Setup Time                                         | 1.5          | _          | 1.5       | _          | 2       | _          | 2.5     | _         | ns            | 5    |

| 8    | t <sub>IH</sub>   | Input Hold Time                                          | 0.8          | _          | 0.8       | _          | 1       | _          | 1       | _         | ns            | 5    |

| 9    | t <sub>CKS</sub>  | CKE Setup Time                                           | 1.5          | _          | 1.5       | _          | 2       | _          | 2.5     | _         | ns            | 5    |

| 10   | t <sub>CKH</sub>  | CKE Hold Time                                            | 0.8          | _          | 0.8       | _          | 1       | _          | 1       | _         | ns            | 5    |

| 11   | t <sub>RSC</sub>  | Mode Register Set-up Time                                | 14           | _          | 15        | _          | 16      | _          | 16      | _         | ns            |      |

| 12   | t <sub>SB</sub>   | Power Down Mode Entry Time                               | 0            | 7          | 0         | 7.5        | 0       | 8          | 0       | 8         | ns            |      |

| Com  | mon Para          | meters                                                   |              |            |           |            |         |            |         |           |               |      |

| 13   | t <sub>RCD</sub>  | Row to Column Delay Time                                 | 20           | _          | 20        | _          | 20      | _          | 24      | _         | ns            | 6    |

| 14   | t <sub>RP</sub>   | Row Precharge Time                                       | 20           | _          | 20        | _          | 20      | _          | 24      | _         | ns            | 6    |

| 15   | t <sub>RAS</sub>  | Row Active Time                                          | 42           | 100K       | 45        | 100K       | 45      | 100k       | 48      | 100k      | ns            | 6    |

| 16   | t <sub>RC</sub>   | Row Cycle Time                                           | 60           | _          | 60        | _          | 60      | _          | 72      | _         | ns            | 6    |

| 17   | t <sub>RRD</sub>  | Activate(a) to Activate(b) Command Period                | 14           | -          | 15        | -          | 16      | -          | 20      | -         | ns            | 6    |

| 18   | t <sub>CCD</sub>  | CAS(a) to CAS(b) Command Period                          | 1            | _          | 1         | _          | 1       | _          | 1       | -         | CLK           |      |

| Refr | esh Cycle         |                                                          |              |            |           |            |         |            |         |           |               |      |

| 19   | t <sub>REF</sub>  | Refresh Period (4096 cycles)                             | _            | 64         | _         | 64         | _       | 64         | _       | 64        | ms            |      |

| 20   | t <sub>SREX</sub> | Self Refresh Exit Time                                   | 10           |            | 10        |            | 10      |            | 12      |           | ns            |      |

# V54C365804VD(L)

# AC Characteristics (Cont'd)

|             |                  |                                 | Limit Values |      |      |      |      |      |      |      |      |      |

|-------------|------------------|---------------------------------|--------------|------|------|------|------|------|------|------|------|------|

|             |                  |                                 | -7           |      | -75  |      | -8PC |      | -8   |      |      |      |

| #           | Symbol           | Parameter                       | Min.         | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Unit | Note |

| Read Cycle  |                  |                                 |              |      |      |      |      |      |      |      |      |      |

| 21          | t <sub>OH</sub>  | Data Out Hold Time              | 2.7          | -    | 2.7  | _    | 3    | _    | 3    | _    | ns   | 2    |

| 22          | t <sub>LZ</sub>  | Data Out to Low Impedance Time  | 1            | _    | 1    | _    | 0    | _    | 0    | _    | ns   |      |

| 23          | t <sub>HZ</sub>  | Data Out to High Impedance Time | _            | 5.4  | _    | 5.4  | 3    | 8    | 3    | 8    | ns   | 7    |

| 24          | t <sub>DQZ</sub> | DQM Data Out Disable Latency    | _            | 2    | _    | 2    | _    | 2    | _    | 2    | CLK  |      |

| Write Cycle |                  |                                 |              |      |      |      |      |      |      |      |      |      |

| 25          | t <sub>WR</sub>  | Write Recovery Time             | 2            | _    | 2    | _    | 2    | _    | 2    | _    | CLK  |      |

| 26          | t <sub>DQW</sub> | DQM Write Mask Latency          | 0            | _    | 0    | -    | 0    | -    | _    | _    | CLK  |      |

### Notes for AC Parameters:

- 1. For proper power-up see the operation section of this data sheet.

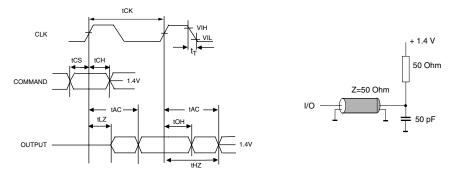

- 2. AC timing tests have  $V_{IL} = 0.8V$  and  $V_{IH} = 2.0V$  with the timing referenced to the 1.4 V crossover point. The transition time is measured between  $V_{IH}$  and  $V_{IL}$ . All AC measurements assume  $t_T = 1$ ns with the AC output load circuit shown in Figure 1.

Figure 1.

- 4. If clock rising time is longer than 1 ns, a time  $(t_T/2 0.5)$  ns has to be added to this parameter.

- 5. If  $t_T$  is longer than 1 ns, a time  $(t_T 1)$  ns has to be added to this parameter.

- 6. These parameter account for the number of clock cycle and depend on the operating frequency of the clock, as follows:

the number of clock cycle = specified value of timing period (counted in fractions as a whole number)

Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after CKE returns high. Self Refresh Exit is not complete until a time period equal to tRC is satisfied once the Self Refresh Exit command is registered.

7. Referenced to the time which the output achieves the open circuit condition, not to output voltage levels

## V54C365804VD(L)

### **Timing Diagrams**

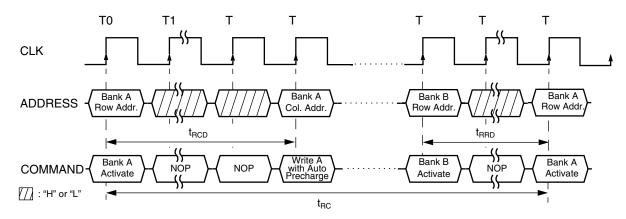

- 1. Bank Activate Command Cycle

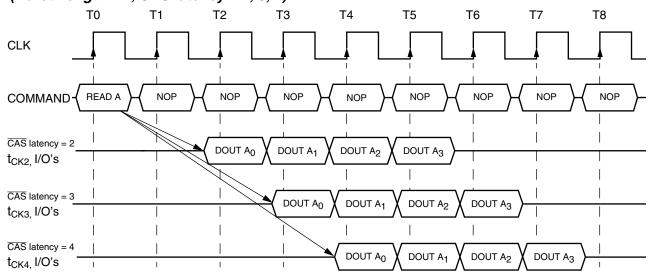

- 2. Burst Read Operation

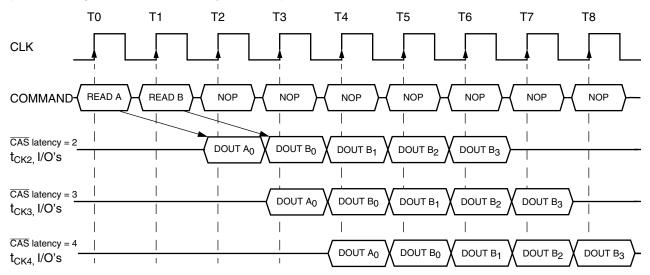

- 3. Read Interrupted by a Read

- 4. Read to Write Interval

- 4.1 Read to Write Interval

- 4.2 Minimum Read to Write Interval

- 4.3 Non-Minimum Read to Write Interval

- 5. Burst Write Operation

- 6. Write and Read Interrupt

- 6.1 Write Interrupted by a Write

- 6.2 Write Interrupted by Read

- 7. Burst Write & Read with Auto-Precharge

- 7.1 Burst Write with Auto-Precharge

- 7.2 Burst Read with Auto-Precharge

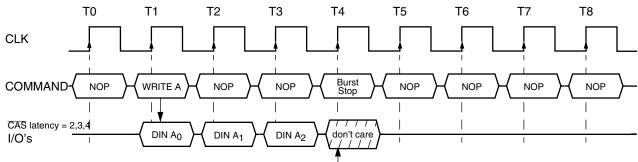

- 8. Burst Termination

- 8.1 Termination of a Full Page Burst Write Operation

- 8.2 Termination of a Full Page Burst Write Operation

- 9. AC- Parameters

- 9.1 AC Parameters for a Write Timing

- 9.2 AC Parameters for a Read Timing

- 10. Mode Register Set

- 11. Power on Sequence and Auto Refresh (CBR)

- 12. Clock Suspension (using CKE)

- 12.1 Clock Suspension During Burst Read CAS Latency = 2

- 12. 2 Clock Suspension During Burst Read CAS Latency = 3

- 12. 3 Clock Suspension During Burst Write CAS Latency = 2

- 12. 4 Clock Suspension During Burst Write CAS Latency = 3

- 13. Power Down Mode and Clock Suspend

- 14. Self Refresh (Entry and Exit)

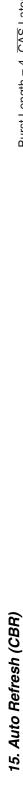

- 15. Auto Refresh (CBR)

## Timing Diagrams (Cont'd)

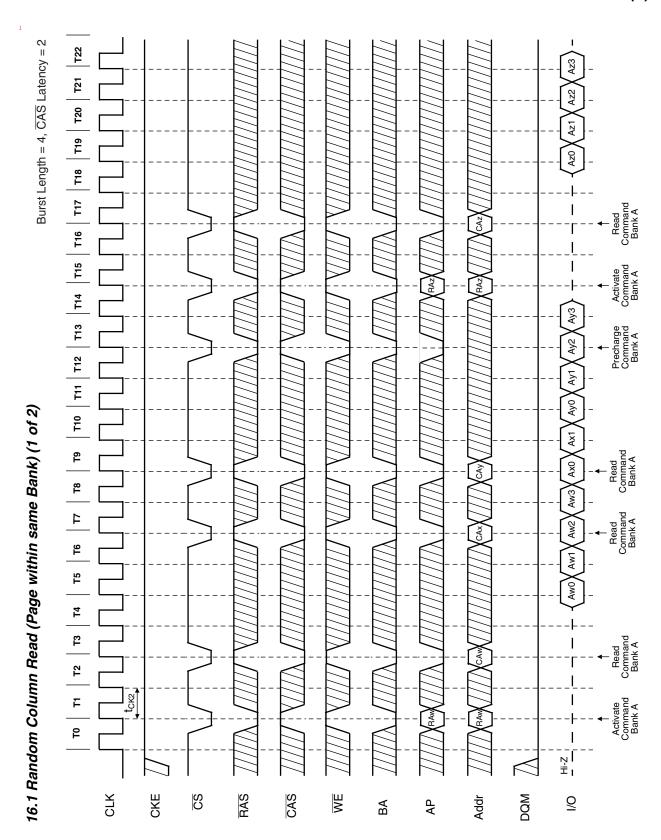

- 16. Random Column Read ( Page within same Bank)

- 16.1  $\overline{CAS}$  Latency = 2

- $16.2 \overline{CAS} Latency = 3$

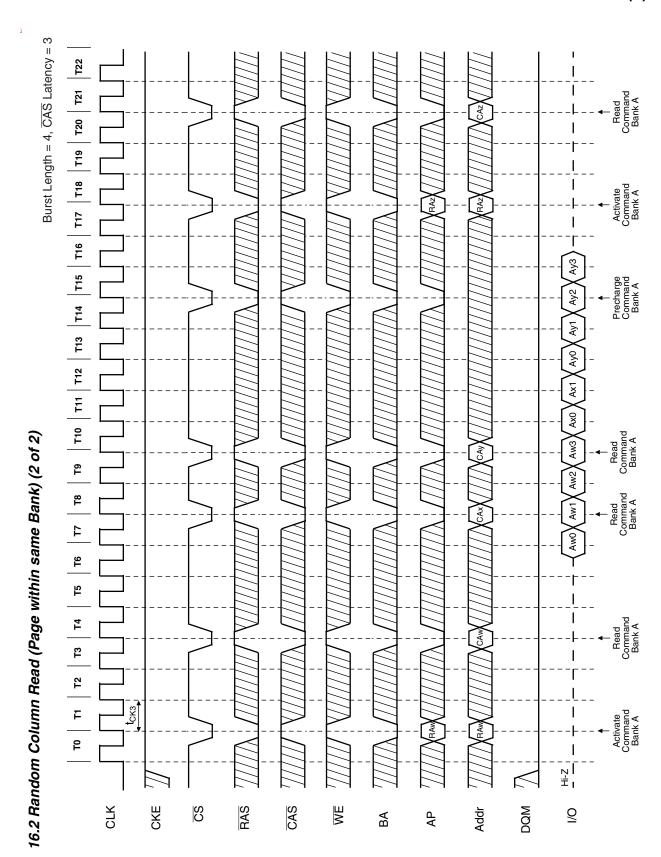

- 17. Random Column Write ( Page within same Bank)

- 17.1  $\overline{\text{CAS}}$  Latency = 2

- $17.2 \overline{CAS} Latency = 3$

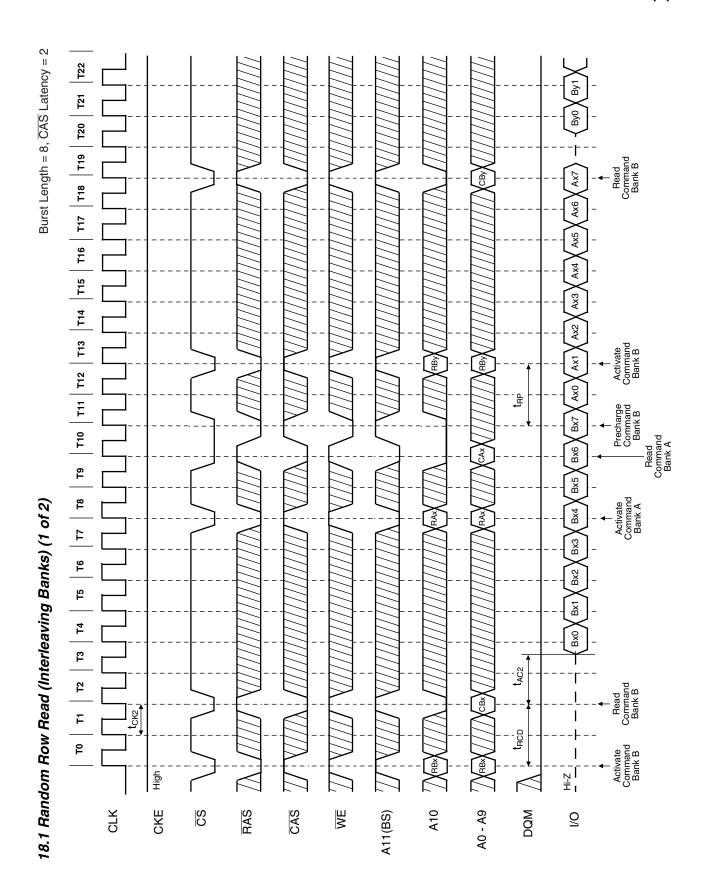

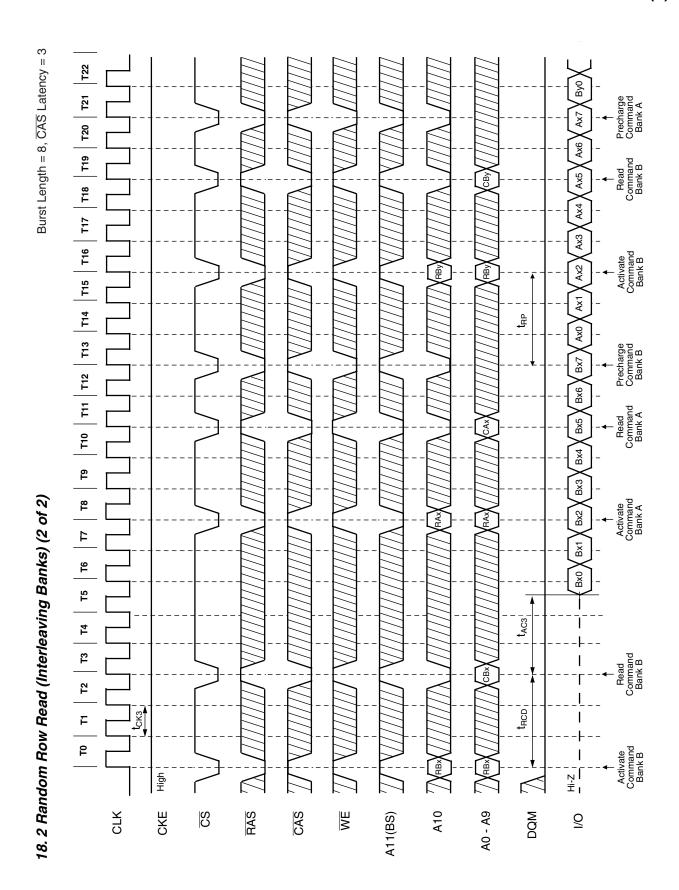

- 18. Random Row Read (Interleaving Banks) with Precharge

- 18.1  $\overline{CAS}$  Latency = 2

- 18.2  $\overline{CAS}$  Latency = 3

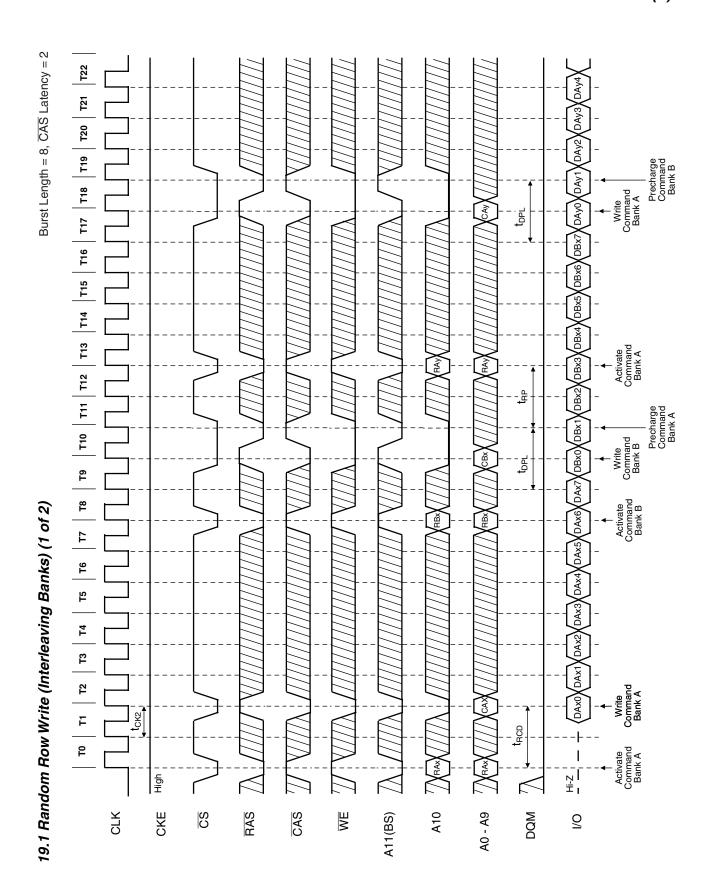

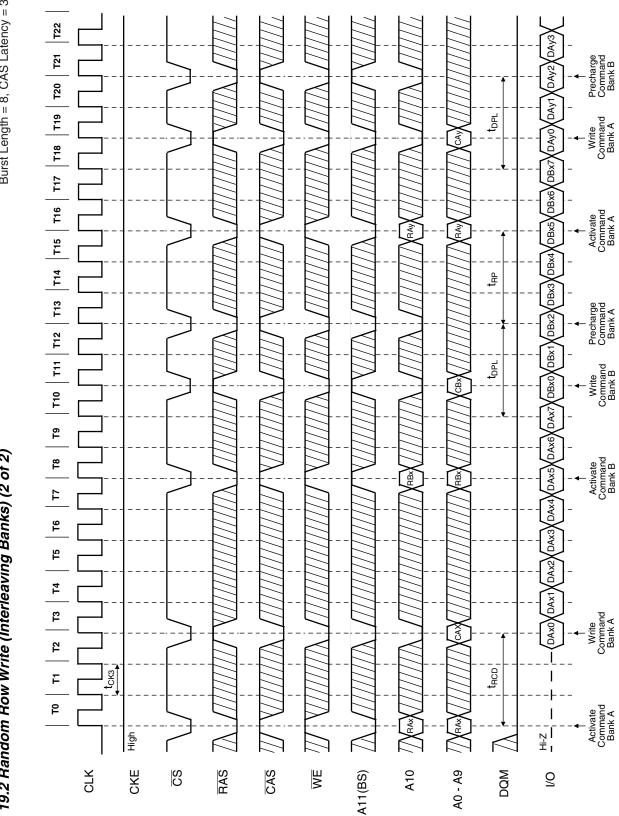

- 19. Random Row Write (Interleaving Banks) with Precharge

- 19.1  $\overline{CAS}$  Latency = 2

- 19.2  $\overline{CAS}$  Latency = 3

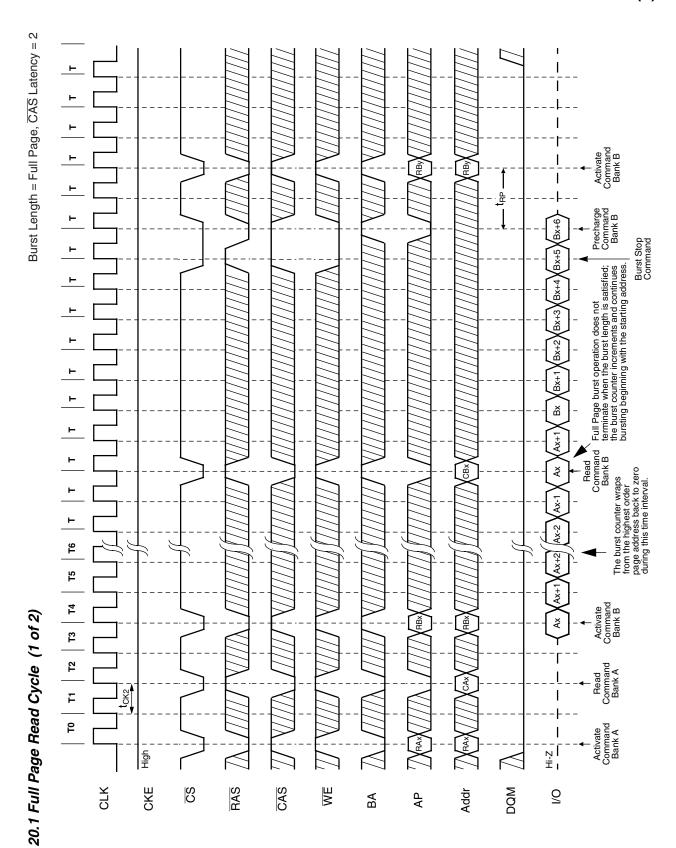

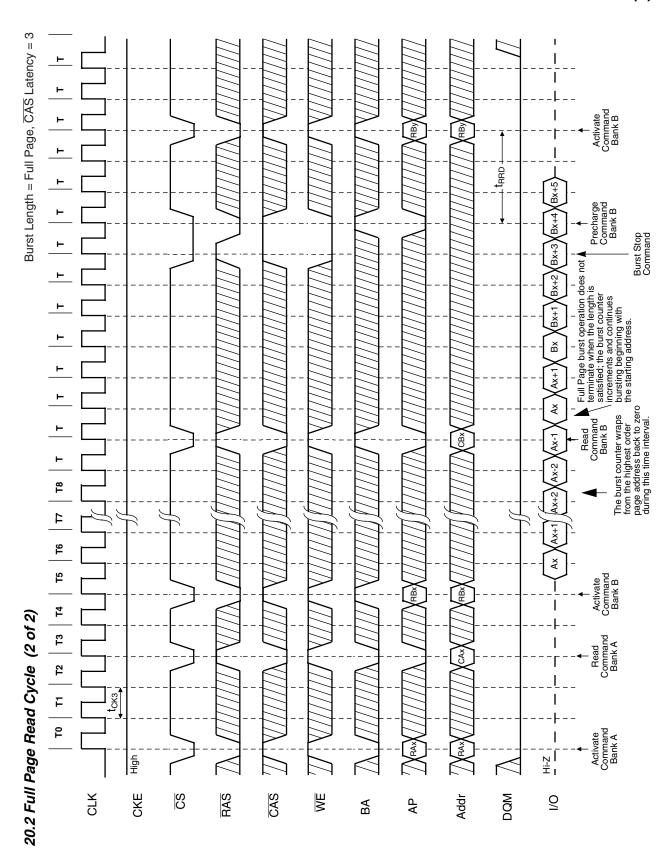

- 20. Full Page Read Cycle

- 20.1  $\overline{CAS}$  Latency = 2

- 20.2  $\overline{CAS}$  Latency = 3

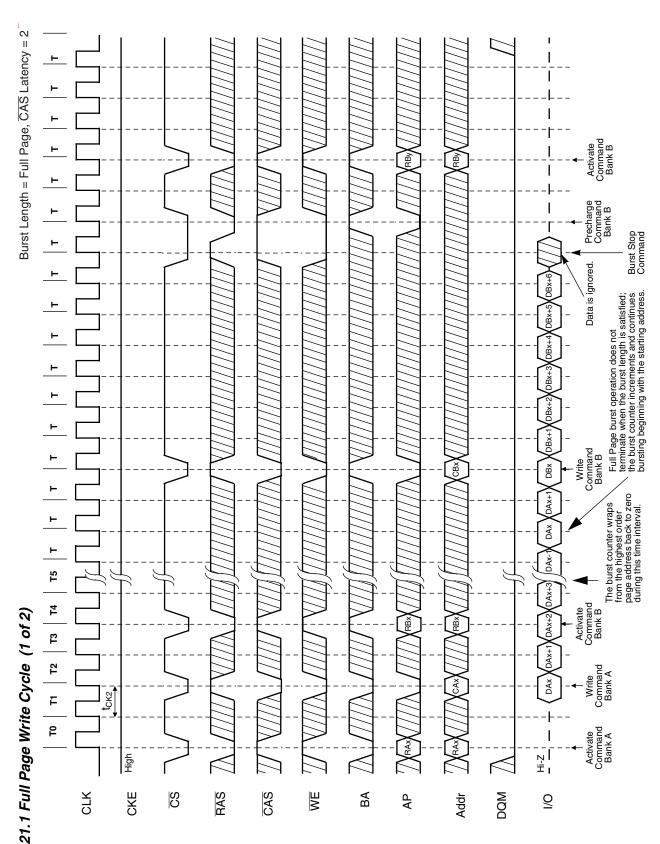

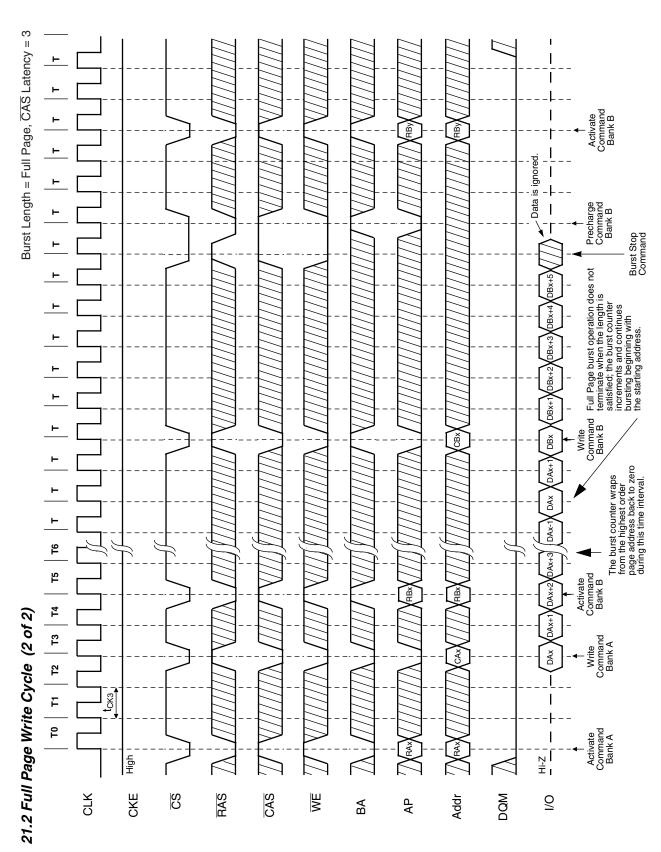

- 21. Full Page Write Cycle

- 21.1  $\overline{CAS}$  Latency = 2

- 21.2  $\overline{CAS}$  Latency = 3

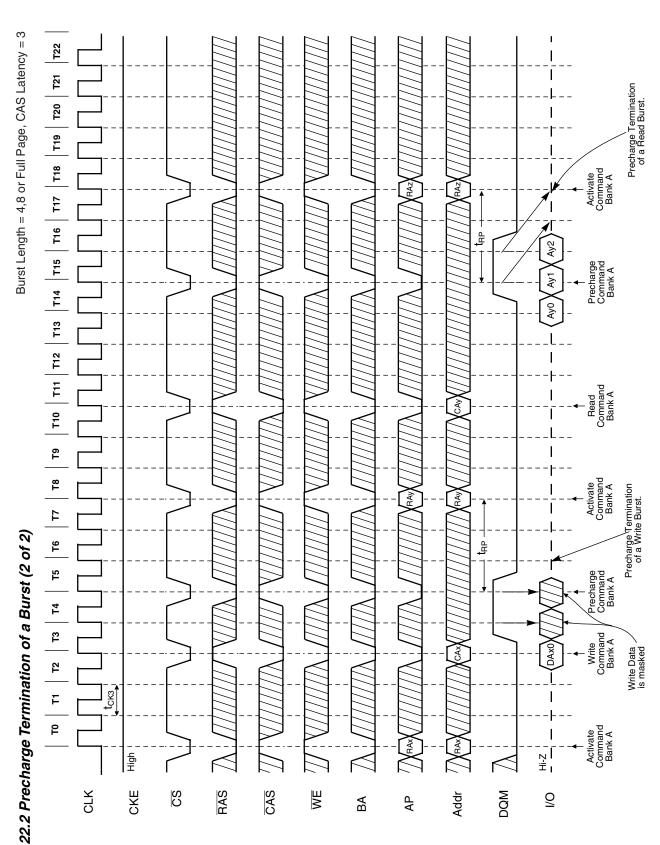

- 22. Precharge Termination of a Burst

- 22.1  $\overline{CAS}$  Latency = 2

- 22.2  $\overline{CAS}$  Latency = 3

# 1. Bank Activate Command Cycle

# (CAS latency = 3)

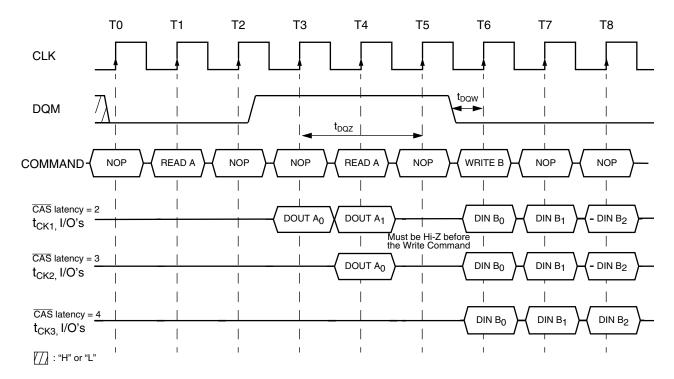

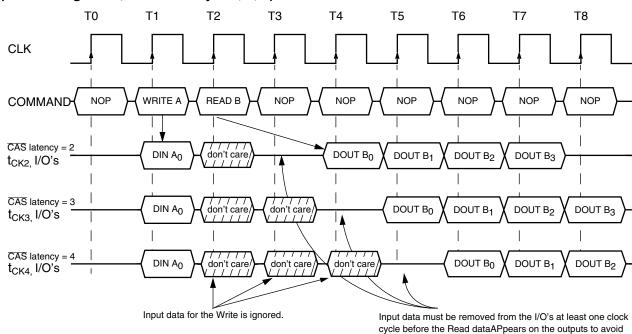

## 2. Burst Read Operation

## (Burst Length = 4, $\overline{CAS}$ latency = 2, 3, 4)

## 3. Read Interrupted by a Read

# (Burst Length = 4, $\overline{CAS}$ latency = 2, 3, 4)

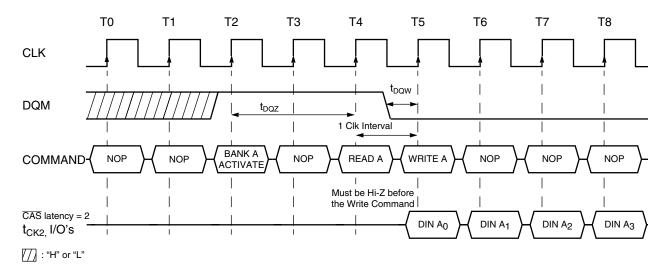

### 4.1 Read to Write Interval

### (Burst Length = 4, $\overline{CAS}$ latency = 3)

V54C365804VD(L)

### 4.2 Minimum Read to Write Interval

# (Burst Length = 4, $\overline{CAS}$ latency = 2)

### 4.3 Non-Minimum Read to Write Interval

## (Burst Length = 4, CAS latency = 2, 3, 4

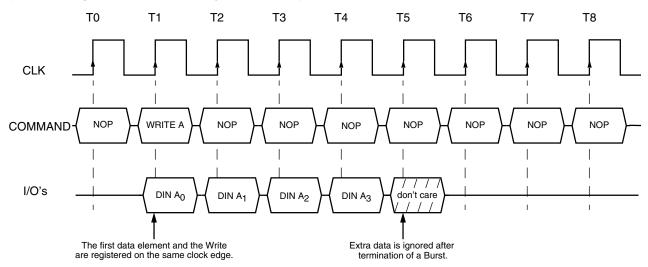

## 5. Burst Write Operation

# (Burst Length = 4, $\overline{CAS}$ latency = 2, 3, or 4)

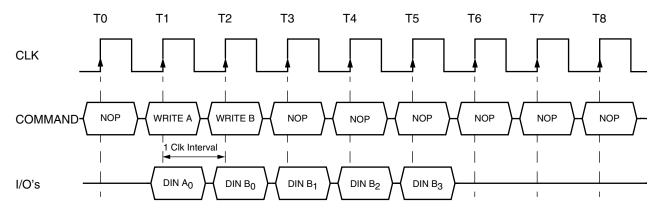

## 6.1 Write Interrupted by a Write

# (Burst Length = 4, $\overline{CAS}$ latency = 2, 3, or 4)

### 6.2 Write Interrupted by a Read

## (Burst Length = 4, $\overline{CAS}$ latency = 2, 3, 4)

data contention.

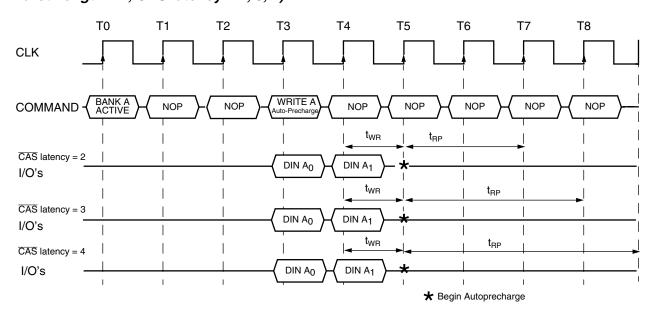

## 7. Burst Write with Auto-Precharge

# Burst Length = 2, CAS latency = 2, 3, 4)

Bank can be reactivated after trp

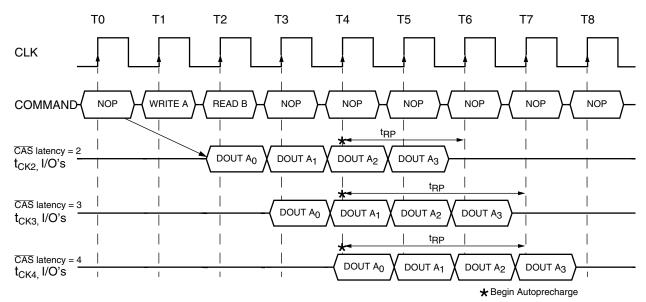

# 7.2 Burst Read with Auto-Precharge

# Burst Length = 4, $\overline{CAS}$ latency = 2, 3, 4)

Bank can be reactivated after tRP

22

# 8.1 Termination of a Full Page Burst Read Operation

# $(\overline{CAS} | latency = 2, 3, 4)$

The burst ends after a delay equal to the  $\overline{\text{CAS}}$  latency.

## 8.2 Termination of a Full Page Burst Write Operation

# $(\overline{CAS} | latency = 2, 3, 4)$

Input data for the Write is masked.

Burst Length = 4, CAS Latency = 2 T22 T21 T20 (RBy T19 t<sub>CKH</sub> T18 Activate Command Bank A T17 T16 Precharge Command Bank A T10 T11 T12 T13 T14 T15 **t**wn Ay3 Begin Auto Precharge Bank B ( Ay1 ) Ayo 🕽 tos → Bx3 Begin Auto Precharge Bank A Activate Command Bank A Bx2 RAY) 6 BX1 Write with Auto Precharge Command Bank B 8 Bx0 CBX 1 Ax3 **1**0 Ax2RBX RBX **T**2 Ax1 Write with Auto Precharge Command Bank A 9.1 AC Parameters for Write Timing 7 Axo tck2 2 trop. ←t<sub>AH</sub> Activate Command Bank A 72 RAX RAX ᅙ F . Y CKS ٤ Ν Ε Ι CLK CKE RAS CAS WE DOM SS Addr 9  $\mathsf{AP}$ ВА

Burst Length = 2, CAS Latency = 2 **T**13 T12 RAy RAy Ε t<sub>CKH</sub> **t**F BX1 110 Precharge Command Bank A Begin Auto Precharge Bank B <u>6</u> **2** RBX 1 2 **1**0 Activate Command Bank B X RBX /RBX t<sub>RAS</sub>-**1**2 7 × Ko **t**ro £ -RCD -t HH t<sub>CK2</sub> 72 v tcs RAX) RAx \ 9.2 AC Parameters for Read Timing F tAS → <del>ا</del>ت. tcks ᄋ to HO ЫН Н Н CLK RAS CAS WE DQM SS Addr 9  $\mathsf{AP}$ BA

T22 T18 T19 T20 T21 T14 T15 T16 T17 T13 T10 T11 T12 6 8 1 Any Command **9** 2 Clock min. **T**2 Mode Register Set Command Address Key 7 2 12 10. Mode Register Set <u></u> CKE CLK SS RAS CAS WE Addr ВА ЧΡ

Any Command 2 Clock min. Address Key t<sub>EC</sub> Minimum of 2 Refresh Cycles are required 2nd Auto Refresh Command F -11. Power on Sequence and Auto Refresh (CBR) Precharge 1st Auto Refresh Command Command All Banks ŧР High level is required Inputs hust be stable for 200μs 잍 ŅĮ. CLK RAS CAS WE SS Addr DQM 9 BA AP

Burst Length = 4, CAS Latency = 3 T22 Write Command Bank B T21 T20 T19 T17 T18 Activate Command Bank B RBz RBz T15 T16 Precharge Command Bank B T14 T13 (BBWOXDBW1XDBW2XDBXOXDBX1XDBY0XDBY1XDBY2XDBY3 T10 T11 T12 17.2 Random Column Write (Page within same Bank) (2 of 2) **6**L **8** œx) 4 **1**0 15 4 **T**3 2 tck3 F \_\_ 안 H.Y CLK CKE SS RAS CAS WE Addr DØM 9 ΑЬ ВА

Burst Length = 8 or Full Page, CAS Latency = 2 T22 T21 Az2 T19 T20 Az1 Precharge Termination of a Read Burst. Az0 118 T17 Read Command Bank A CAZ T16 T15 Activate Command Bank A RAZ X T10 T11 T12 T13 T14 Ay2 Precharge Command Bank A Ą Read Command Bank A <u>6</u> Activate Command Bank A 8 4 22.1 Precharge Termination of a Burst (1 of 2) Precharge Command Bank A <u>9</u> **T**2 4 13 12 CK2 F 욘 CKE RAS CAS WE DOM 유 SS Addr 0 ВА Αb

# V54C365804VD(L)

## **MOSEL VITELIC**

# **Complete List of Operation Commands**

# **SDRAM Function Truth Table**

| CURRENT<br>STATE <sup>1</sup> | cs | RAS | CAS | WE | BS  | Addr  | ACTION                                            |

|-------------------------------|----|-----|-----|----|-----|-------|---------------------------------------------------|

| Idle                          | Н  | Х   | Х   | Х  | Х   | Х     | NOP or Power Down                                 |

|                               | L  | Н   | Н   | Н  | X   | Х     | NOP                                               |

|                               | L  | Н   | Н   | L  | BS  | Х     | ILLEGAL <sup>2</sup>                              |

|                               | L  | Н   | L   | Х  | BS  | Х     | ILLEGAL <sup>2</sup>                              |

|                               | L  | L   | Н   | Н  | BS  | RA    | Row (&Bank) Active; Latch Row Address             |

|                               | L  | L   | Н   | L  | BS  | AP    | NOP <sup>4</sup>                                  |

|                               | L  | L   | L   | Н  | Х   | X     | Auto-Refresh or Self-Refresh <sup>5</sup>         |

|                               | L  | L   | L   | L  | Ор- | Code  | Mode reg. Access <sup>5</sup>                     |

| Row Active                    | Н  | x   | x   | x  | x   | х     | NOP                                               |

|                               | L  | Н   | Н   | Х  | X   | X     | NOP                                               |

|                               | L  | Н   | L   | Н  | BS  | CA,AP | Begin Read; Latch CA; DetermineAP                 |

|                               | L  | Н   | L   | L  | BS  | CA,AP | Begin Write; Latch CA; DetermineAP                |

|                               | L  | L   | Н   | Н  | BS  | X     | ILLEGAL <sup>2</sup>                              |

|                               | L  | L   | Н   | L  | BS  | AP    | Precharge                                         |

|                               | L  | L   | L   | Х  | Х   | Х     | ILLEGAL                                           |

| Read                          | Н  | X   | X   | X  | X   | X     | NOP (Continue Burst to End;>Row Active)           |

|                               | L  | H   | H   | Н  | X   | X     | NOP (Continue Burst to End;>Row Active)           |

|                               | L  | H   | H   | L  | BS  | X     | Burst Stop Command > Row Active                   |

|                               | L  | H   | L   | Н  | BS  | CA,AP | Term Burst, New Read, DetermineAP <sup>3</sup>    |

|                               | L  | H   | L   | L  | BS  | CA,AP | Term Burst, Start Write, DetermineAP <sup>3</sup> |

|                               | L  | L   | H   | H  | BS  | X     | ILLEGAL <sup>2</sup>                              |

|                               | L  | L   | H   | L  | BS  | AP    | Term Burst, Precharge                             |

|                               | L  | L   | L   | Х  | X   | Х     | ILLEGAL                                           |

| Write                         | Н  | X   | Х   | Х  | X   | Х     | NOP (Continue Burst to End;>Row Active)           |

|                               | L  | Н   | Н   | Н  | X   | X     | NOP (Continue Burst to End;>Row Active)           |

|                               | L  | Н   | Н   | L  | BS  | X     | Burst Stop Command > Row Active                   |

|                               | L  | Н   | L   | Н  | BS  | CA,AP | Term Burst, Start Read, DetermineAP3              |

|                               | L  | H   | L   | L  | BS  | CA,AP | Term Burst, New Write, DetermineAP <sup>3</sup>   |

|                               | L  | L   | Н   | H  | BS  | X     | ILLEGAL <sup>2</sup>                              |

|                               | L  | L   | Н   | L  | BS  | AP    | Term Burst, Precharge <sup>3</sup>                |

|                               | L  | L   | L   | Х  | Х   | Х     | ILLEGAL                                           |

| Read                          | Н  | X   | X   | X  | X   | Х     | NOP (Continue Burst to End;> Precharge)           |

| with                          | L  | Н   | Н   | Н  | X   | X     | NOP (Continue Burst to End;> Precharge)           |

| Auto                          | L  | Н   | Н   | L  | BS  | X     | ILLEGAL <sup>2</sup>                              |

| Precharge                     | L  | H   | L   | H  | BS  | X     | ILLEGAL <sup>2</sup>                              |

|                               | L  | Н   | L   | L  | X   | X     | ILLEGAL                                           |

|                               | L  | L   | H   | H  | BS  | X     | ILLEGAL <sup>2</sup>                              |

|                               | L  | L   | H   | L  | BS  | AP    | ILLEGAL <sup>2</sup>                              |

|                               | L  | L   | L   | X  | Х   | Х     | ILLEGAL                                           |

# V54C365804VD(L)

## **MOSEL VITELIC**

# **SDRAM FUNCTION TRUTH TABLE(continued)**

| CURRENT<br>STATE <sup>1</sup> | cs | RAS | CAS        | WE | BS | Addr | ACTION                                  |

|-------------------------------|----|-----|------------|----|----|------|-----------------------------------------|

| Write                         | Н  | Х   | Х          | Х  | Х  | Х    | NOP (Continue Burst to End;> Precharge) |

| with                          | L  | Н   | Н          | Н  | X  | Х    | NOP (Continue Burst to End;> Precharge) |

| Auto                          | L  | Н   | Н          | L  | BS | Х    | ILLEGAL <sup>2</sup>                    |

| Precharge                     | L  | H   | L          | H  | BS | X    | ILLEGAL <sup>2</sup>                    |

| coa. go                       | L  | H   | L          | L  | X  | X    | ILLEGAL                                 |

|                               | L  | L   | H          | H  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | ''<br>  H  | Ľ  | BS | AP   | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | ''         | X  | X  | X    | ILLEGAL                                 |

| Precharging                   | Н  | x   | Х          | Х  | Х  | Х    | NOP:> Idle after tRP                    |

|                               | L  | H   | Н          | Н  | X  | X    | NOP;> Idle after tRP                    |

|                               | L  | H   | H          | L  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | H   | L          | X  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | l H        | H  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | ''         | Ľ  | BS | AP   | NOP <sup>4</sup>                        |

|                               | L  | [   | <u>'</u> ' | X  | X  | X    | ILLEGAL                                 |

|                               |    |     |            |    |    |      |                                         |

| Row                           | H  | X   | X          | X  | X  | X    | NOP;> Row Active after tRCD             |

| Activating                    | L  | H   | Н          | Н  | X  | X    | NOP;> Row Active after tRCD             |

|                               | L  | H   | H          | L  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | Н   | L          | X  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | Н          | Н  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | H          | L  | BS | AP   | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | L          | Х  | Х  | Х    | ILLEGAL                                 |

| Write                         | Н  | x   | X          | X  | X  | X    | NOP                                     |

| Recovering                    | L  | H   | H          | Н  | X  | X    | NOP                                     |

|                               | L  | H   | H          | L  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | H   | L          | X  | BS | Х    | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | Н          | Н  | BS | X    | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | Н          | L  | BS | AP   | ILLEGAL <sup>2</sup>                    |

|                               | L  | L   | L          | X  | X  | X    | ILLEGAL                                 |

| Refreshing                    | Н  | Х   | Х          | Х  | Х  | Х    | NOP;> Idle after tRC                    |

|                               | L  | Н   | Н          | Н  | X  | Х    | NOP;> Idle after tRC                    |

|                               | L  | Н   | Н          | L  | X  | Х    | ILLEGAL                                 |

|                               | L  | Н   | L          | Х  | X  | Х    | ILLEGAL                                 |

|                               | L  | L   | H          | X  | X  | X    | ILLEGAL                                 |

|                               | L  | L   | L          | X  | X  | X    | ILLEGAL                                 |

| Mode                          | Н  | x   | Х          | Х  | Х  | Х    | NOP                                     |

| Register                      | L  | Н   | Н          | Н  | X  | Х    | NOP                                     |

| <b>5</b>                      | L  | H   | Н          | L  | X  | X    | ILLEGAL                                 |

| Accessing                     | L  | H   | L          | X  | X  | X    | ILLEGAL                                 |

| 9                             | L  | L   | X          | X  | X  | X    | ILLEGAL                                 |

|                               |    |     |            |    |    |      | TEECO LE                                |

## Clock Enable (CKE) Truth Table:

| STATE(n)                  | CKE<br>n-1 | CKE<br>n | cs | RAS | CAS | WE | Addr | ACTION                                       |

|---------------------------|------------|----------|----|-----|-----|----|------|----------------------------------------------|

| Self-Refresh <sup>6</sup> | Н          | Х        | Х  | Х   | Х   | Х  | Х    | INVALID                                      |

|                           | L          | Н        | Н  | Х   | X   | Х  | Х    | EXIT Self-Refresh, Idle after tRC            |

|                           | L          | Н        | L  | Н   | Н   | Н  | Х    | EXIT Self-Refresh, Idle after tRC            |

|                           | L          | Н        | L  | Н   | Н   | L  | Х    | ILLEGAL                                      |

|                           | L          | Н        | L  | Н   | L   | Х  | Х    | ILLEGAL                                      |

|                           | L          | Н        | L  | L   | X   | Х  | Х    | ILLEGAL                                      |

|                           | L          | L        | Х  | Х   | X   | X  | Х    | NOP (Maintain Self-Refresh)                  |

| Power-Down                | Н          | Х        | Х  | Х   | Х   | Х  | Х    | INVALID                                      |

|                           | L          | Н        | Н  | Х   | X   | Х  | Х    | EXIT Power-Down, > Idle.                     |

|                           | L          | Н        | L  | Н   | Н   | Н  | Х    | EXIT Power-Down, > Idle.                     |

|                           | L          | Н        | L  | Н   | Н   | L  | Х    | ILLEGAL                                      |

|                           | L          | Н        | L  | Н   | L   | Х  | Х    | ILLEGAL                                      |

|                           | L          | Н        | L  | L   | X   | Х  | Х    | ILLEGAL                                      |

|                           | L          | L        | Х  | X   | X   | Х  | Х    | NOP (Maintain Low-Power Mode)                |

| All. Banks                | Н          | Н        | Х  | Х   | Х   | Х  | Х    | Refer to the function truth table            |

| Idle <sup>7</sup>         | Н          | L        | Н  | X   | X   | Х  | Х    | Enter Power- Down                            |

|                           | Н          | L        | L  | Н   | Н   | Н  | Х    | Enter Power- Down                            |

|                           | Н          | L        | L  | Н   | Н   | L  | Х    | ILLEGAL                                      |

|                           | Н          | L        | L  | Н   | L   | Х  | Х    | ILLEGAL                                      |

|                           | Н          | L        | L  | L   | Н   | X  | Х    | ILLEGAL                                      |

|                           | Н          | L        | L  | L   | L   | Н  | Х    | Enter Self-Refresh                           |

|                           | Н          | L        | L  | L   | L   | L  | Х    | ILLEGAL                                      |

|                           | L          | L        | Х  | Х   | Х   | Х  | Х    | NOP                                          |

| Any State                 | Н          | Н        | Х  | Х   | х   | Х  | Х    | Refer to the function truth table            |

| other than                | Н          | L        | Х  | X   | X   | Х  | Х    | Begin Clock Suspend next cycle <sup>8</sup>  |

| listed above              | L          | Н        | Х  | X   | X   | Х  | X    | Exit Clock Suspend next cycle <sup>8</sup> . |

|                           | L          | L        | Х  | Х   | X   | X  | Х    | Maintain Clock Suspend.                      |

### Abbreviations:

RA = Row Address BS = Bank Address

CA = Column Address AP = Auto Precharge

## Notes for SDRAM function truth table:

- 1. Current State is state of the bank determined by BS. All entries assume that CKE was active (HIGH) during the preceding clock cycle.

- 2. Illegal to bank in specified state; Function may be legal in the bank indicated by BS, depending on the state of that bank.

- 3. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 4. NOP to bank precharging or in Idle state. May precharge bank(s) indicated by BS (andAP).

- 5. Illegal if any bank is not Idle.

- 6. CKE Low to High transition will re-enable CLK and other inputs asynchronously. A minimum setup time must be satisfied before any command other than EXIT.

- 7. Power-Down and Self-Refresh can be entered only from the All Banks Idle State.

- 8. Must be legal command as defined in the SDRAM function truth table.

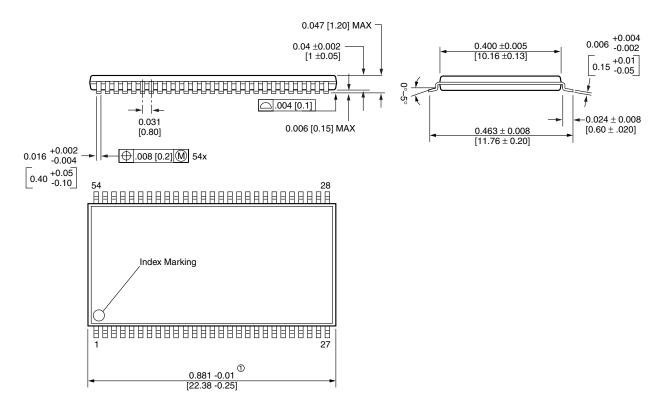

# Package Diagram

## 54-Pin Plastic TSOP-II (400 mil)

$\textcircled{\scriptsize 1}$  Does not include plastic or metal protrusion of 0.15 max. per side

Unit in inches [mm]

**MOSEL VITELIC**

V54C365804VD(L)

Notes

## **MOSEL VITELIC**

## **WORLDWIDE OFFICES**

#### U.S.A.

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0952

#### **TAIWAN**

7F, NO. 102 MIN-CHUAN E. ROAD, SEC. 3 TAIPEI PHONE: 886-2-2545-1213

FAX: 886-2-2545-1209

NO 19 LI HSIN ROAD SCIENCE BASED IND. PARK HSIN CHU, TAIWAN, R.O.C. PHONE: 886-3-579-5888 FAX: 886-3-566-5888

#### **SINGAPORE**

10 ANSON ROAD #23-13 INTERNATIONAL PLAZA SINGAPORE 079903 PHONE: 65-3231801 FAX: 65-3237013

### JAPAN

ONZE 1852 BUILDING 6F 2-14-6 SHINTOMI, CHUO-KU TOKYO 104-0041 PHONE: 03-3537-1400 FAX: 03-3537-1402

## V54C365804VD(L)

#### **UK & IRELAND**

SUITE 50, GROVEWOOD BUSINESS CENTRE STRATHCLYDE BUSINESS PARK BELLSHILL, LANARKSHIRE, SCOTLAND, ML4 3NQ PHONE: 44-1698-748515 FAX: 44-1698-748516

### GERMANY (CONTINENTAL EUROPE & ISRAEL)

BENZSTRASSE 32 71083 HERRENBERG GERMANY

PHONE: +49 7032 2796-0 FAX: +49 7032 2796 22

## U.S. SALES OFFICES

#### **NORTHWESTERN**

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0952

#### SOUTHWESTERN

302 N. EL CAMINO REAL #200 SAN CLEMENTE, CA 92672 PHONE: 949-361-7873 FAX: 949-361-7807

### CENTRAL, NORTHEASTERN & SOUTHEASTERN

604 FIELDWOOD CIRCLE RICHARDSON, TX 75081 PHONE: 214-826-6176 FAX: 214-828-9754

© Copyright 2001, MOSEL VITELIC Inc.

3/01 Printed in U.S.A.

The information in this document is subject to change without notice.

MOSEL VITELIC makes no commitment to update or keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of MOSEL-VITELIC.

MOSEL VITELIC subjects its products to normal quality control sampling techniques which are intended to provide an assurance of high quality products suitable for usual commercial applications. MOSEL VITELIC does not do testing appropriate to provide 100% product quality assurance and does not assume any liability for consequential or incidental arising from any use of its products. If such products are to be used in applications in which personal injury might occur from failure, purchaser must do its own quality assurance testing appropriate to such applications.