## MOS INTEGRATED CIRCUIT $\mu$ PD16837

#### MONOLITHIC QUAD H-BRIDGE DRIVER

#### **DESCRIPTION**

The  $\mu$ PD16837 is a monolithic quad H-bridge driver employing power MOS FETs in the output stage. The MOS FETs in the output stage lower the saturation voltage and power consumption as compared with conventional drivers using bipolar transistors.

In addition, a low-voltage malfunction prevention circuit is also provided that prevents the IC from malfunctioning when the supply voltage drops. A 30-pin plastic shrink SOP package is adopted to help create compact and slim application sets.

In the output stage H-bridge circuits, two low-ON resistance H-bridge circuits for driving actuators, and another two channels for driving sled motors and loading motors are provided, making the product ideal for applications in CD-ROM and DVD.

#### **FEATURES**

- · Four H-bridge circuits employing power MOS FETs

- · High-speed PWM drive: Operating frequency: 120 kHz MAX.

- Low-voltage malfunction prevention circuit: Operating voltage: 2.5 V (TYP.)

- 30-pin plastic SSOP (7.62 mm (300))

#### **ORDERING INFORMATION**

| Part Number | Package                             |

|-------------|-------------------------------------|

| μPD16837GS  | 30-pin plastic SSOP (7.62 mm (300)) |

#### ABSOLUTE MAXIMUM RATINGS ( $T_A = 25$ °C)

| Parameter                           | Symbol               | Conditions                   | Rating                        | Unit    |

|-------------------------------------|----------------------|------------------------------|-------------------------------|---------|

| Control block supply voltage        | V <sub>DD</sub>      |                              | -0.5 to +7.0                  | V       |

| Output block supply voltage         | Vм                   |                              | -0.5 to +15                   | V       |

| Input voltage                       | Vin                  |                              | -0.5 to V <sub>DD</sub> + 0.5 | V       |

| H-bridge drive currentNote 1        | IDR (pulse)          | PW ≤ 5 ms, Duty Cycle ≤ 30 % | ±1.0                          | A/phase |

| Power dissipation <sup>Note 2</sup> | Рт                   |                              | 1.25                          | W       |

| Operating temperature range         | TA                   |                              | 0 to 75                       | °C      |

| Peak junction temperature           | T <sub>j</sub> (MAX) |                              | 150                           | °C      |

| Storage temperature range           | T <sub>stg</sub>     |                              | -55 to +150                   | °C      |

Notes 1. When only one channel operates.

2. When mounted on a glass epoxy board (100 mm  $\times$  100 mm  $\times$  1 mm)

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

#### RECOMMENDED OPERATING RANGE

| Parameter                    | Symbol                         | MIN. | TYP. | MAX. | Unit |

|------------------------------|--------------------------------|------|------|------|------|

| Control block supply voltage | V <sub>DD</sub> Note 1         | 4.0  | 5.0  | 6.0  | ٧    |

| Output block supply voltage  | Vм                             | 10.8 | 12.0 | 13.2 | V    |

| H-bridge drive current       | I <sub>DR (pulse)</sub> Note 2 | -600 |      | 600  | mA   |

| Operating frequency          | fo                             |      |      | 120  | kHz  |

| Operating temperature range  | TA                             | 0    |      | 75   | °C   |

| Peak junction temperature    | Tj (MAX)                       |      |      | 125  | °C   |

**Notes 1.** The low-voltage malfunction prevention circuit operates when V<sub>DD</sub> is 1.5 V or higher but less than 4 V (2.5 V TYP.).

**2.** PW  $\leq$  5 ms, Duty Cycle  $\leq$  10%

#### ELECTRICAL CHARACTERISTICS (Unless otherwise specified, T<sub>A</sub> = 25 °C)

The low-voltage malfunction prevention circuit operates when VDD is 1.5 V to 4 V.

| Parameter                                  | Symbol    | Conditions                                   | MIN. | TYP. | MAX.                  | Unit |

|--------------------------------------------|-----------|----------------------------------------------|------|------|-----------------------|------|

| Vм pin current (leakage current)           | Ім        | V <sub>M</sub> = 13.2 V                      |      |      | 50                    | μΑ   |

| V <sub>DD</sub> pin current                | IDD       | VDD = 6 V                                    |      |      | 200                   | μΑ   |

| High-level input current                   | Іін       | VIN = VDD                                    |      |      | 0.25                  | mA   |

| Low-level input current                    | lı∟       | Vin = 0                                      | -2.0 |      |                       | μΑ   |

| High-level input voltage <sup>Note 1</sup> | Vıн       | V <sub>DD</sub> = 5 V, V <sub>M</sub> = 12 V | 3.0  |      | V <sub>DD</sub> + 0.3 | ٧    |

| Low-level input voltageNote 1              | VIL       | V <sub>DD</sub> = 5 V, V <sub>M</sub> = 12 V | -0.3 |      | 0.8                   | ٧    |

| H-bridge ON resistance (ch2, ch3)          | Rona      | V <sub>DD</sub> = 5 V, V <sub>M</sub> = 12 V |      | 3.0  | 4.0                   | Ω    |

| H-bridge ON resistance (ch1, ch4)          | Ronb      | V <sub>DD</sub> = 5 V, V <sub>M</sub> = 12 V |      | 1.5  | 2.0                   | Ω    |

| H-bridge switching current without         | Isa (AVE) | V <sub>DD</sub> = 5 V                        |      |      | 3.0                   | mA   |

| load (ch2, ch3)Note 2                      |           | V <sub>M</sub> = 12 V                        |      |      |                       |      |

| H-bridge switching current without         | Isb (AVE) | at 100 kHz                                   |      |      | 4.5                   | mA   |

| load (ch1, ch4)Note 2                      |           |                                              |      |      |                       |      |

#### ch2, ch3 2A, 3A, 2B, 3B Output

| Parameter                    | Symbol          | Conditions            | MIN. | TYP. | MAX. | Unit |

|------------------------------|-----------------|-----------------------|------|------|------|------|

| Rise time                    | <b>t</b> TLHa   | VDD = 5 V             |      |      | 200  | ns   |

| Rising delay time            | <b>t</b> PLHa   | V <sub>M</sub> = 12 V |      |      | 350  | ns   |

| Change in rising delay time  | $\Delta t$ PLHa | 20 Ω                  |      |      | 110  | ns   |

| Fall time                    | <b>t</b> THLa   | at 100 kHz            |      |      | 200  | ns   |

| Falling delay time           | <b>t</b> PHLa   |                       |      |      | 350  | ns   |

| Change in falling delay time | $\Delta t$ PHLa |                       |      |      | 130  | ns   |

#### ch2, ch3 2A-2B, 3A-3B

| Parameter                       | Symbol      | Conditions                                   | MIN. | TYP. | MAX. | Unit |

|---------------------------------|-------------|----------------------------------------------|------|------|------|------|

| Rising delay time differential  | tPLHa (A-B) | V <sub>DD</sub> = 5 V, V <sub>M</sub> = 12 V |      |      | 50   | ns   |

| Falling delay time differential | tPHLa (A-B) | 20 Ω at 100kHz                               |      |      | 50   | ns   |

Notes 1. The input pins are the IN and SEL pins.

2. Average value of the current consumed internally by an H-bridge circuit when the circuit is switched without load.

#### ELECTRICAL CHARACTERISTICS (Unless otherwise specified, $T_A = 25$ °C)

#### ch1, ch4 1A, 4A, 1B, 4B Output

| Parameter                    | Symbol                     | Conditions            | MIN. | TYP. | MAX. | Unit |

|------------------------------|----------------------------|-----------------------|------|------|------|------|

| Rise time                    | <b>t</b> тьнь              | V <sub>DD</sub> = 5 V |      |      | 200  | ns   |

| Rising delay time            | <b>t</b> PLHb              | V <sub>M</sub> = 12 V |      |      | 350  | ns   |

| Change in rising delay time  | $\Delta 	extstyle{t}$ PLHb | 10 Ω                  |      |      | 110  | ns   |

| Fall time                    | <b>t</b> тнь               | at 100 kHz            |      |      | 200  | ns   |

| Falling delay time           | <b>t</b> PHLb              |                       |      |      | 350  | ns   |

| Change in falling delay time | ∆tрны                      |                       |      |      | 130  | ns   |

#### ch1, ch4 1A-1B, 4A-4B

| Parameter                       | Symbol              | Conditions           | MIN. | TYP. | MAX. | Unit |

|---------------------------------|---------------------|----------------------|------|------|------|------|

| Rising delay time differential  | tPLHa (A-B)         | VDD = 5 V, VM = 12 V |      |      | 50   | ns   |

| Falling delay time differential | <b>t</b> PHLa (A-B) | 10 Ω at 100 kHz      |      |      | 50   | ns   |

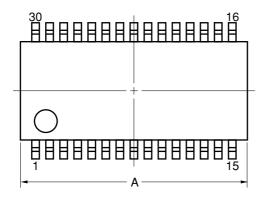

#### PIN CONFIGURATION

|                   |                   |    |    | i                |                   |

|-------------------|-------------------|----|----|------------------|-------------------|

|                   | IN <sub>1</sub>   | 1  | 30 | SEL <sub>4</sub> |                   |

|                   | IN <sub>2</sub>   | 2  | 29 | IN <sub>8</sub>  |                   |

|                   | SEL <sub>1</sub>  | 3  | 28 | IN <sub>7</sub>  |                   |

|                   | DGND              | 4  | 27 | V <sub>M4</sub>  |                   |

| Output block ch 1 | 1A                | 5  | 26 | 4B               | Output block ch 4 |

|                   | PGND <sub>1</sub> | 6  | 25 | PGND4            |                   |

|                   | 1B                | 7  | 24 | 4A               |                   |

|                   | V <sub>M1</sub>   | 8  | 23 | Vмз              |                   |

|                   | 2A                | 9  | 22 | 3B               |                   |

|                   | PGND <sub>2</sub> | 10 | 21 | PGND₃            |                   |

| Output block ch 2 | 2B                | 11 | 20 | 3A               | Output block ch 3 |

|                   | $V_{\text{M2}}$   | 12 | 19 | V <sub>DD</sub>  |                   |

|                   | INз               | 13 | 18 | SEL₃             |                   |

|                   | IN <sub>4</sub>   | 14 | 17 | IN <sub>6</sub>  |                   |

|                   | SEL <sub>2</sub>  | 15 | 16 | IN <sub>5</sub>  |                   |

Data Sheet S12764EJ2V0DS

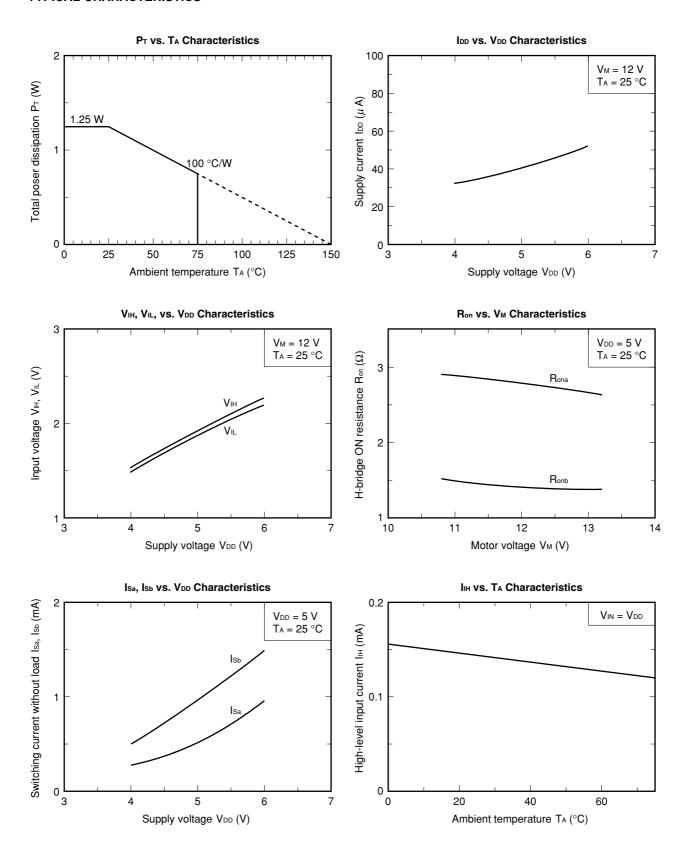

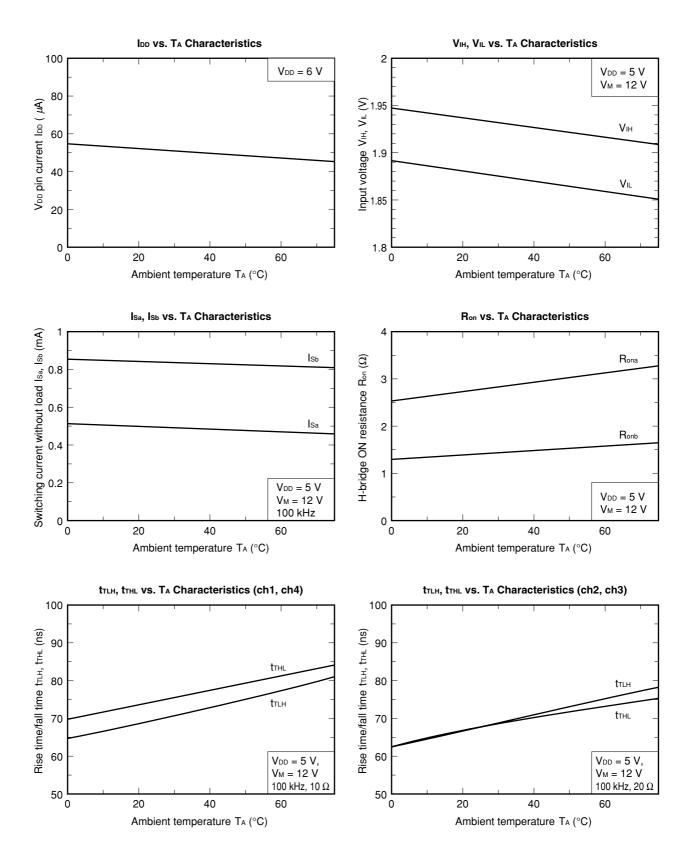

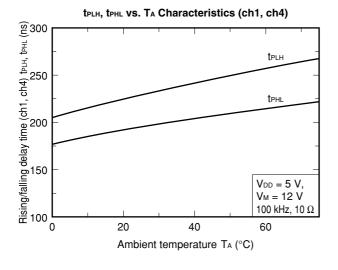

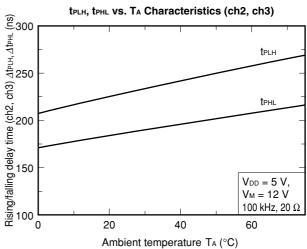

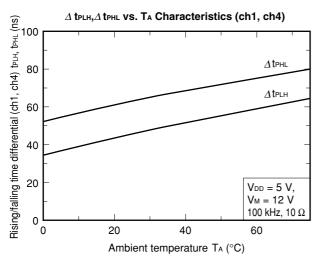

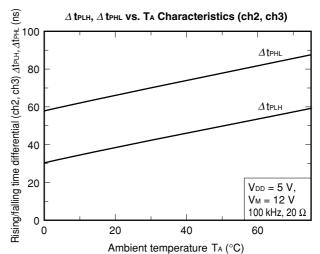

#### TYPICAL CHARACTERISTICS

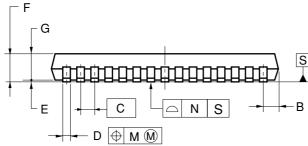

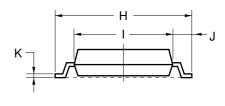

#### **★ PACKAGE DRAWING**

#### 30-PIN PLASTIC SSOP (7.62 mm (300))

NOTE

Each lead centerline is located within 0.10 mm of its true position (T.P.) at maximum material condition.

detail of lead end

(UNIT:mm)

| ITEM | DIMENSIONS             |

|------|------------------------|

| Α    | 13.0 MAX.              |

| В    | 0.9 MAX.               |

| С    | 0.8 (T.P.)             |

| D    | $0.35^{+0.10}_{-0.05}$ |

| E    | 0.1±0.1                |

| F    | 1.8 MAX.               |

| G    | 1.55±0.1               |

| Н    | 7.7±0.2                |

| 1    | 5.6±0.2                |

| J    | 1.05±0.2               |

| K    | $0.20^{+0.10}_{-0.05}$ |

| L    | 0.6±0.2                |

| M    | 0.10                   |

| N    | 0.10                   |

| Р    | 3°+7°                  |

S30GS-80-300C-1

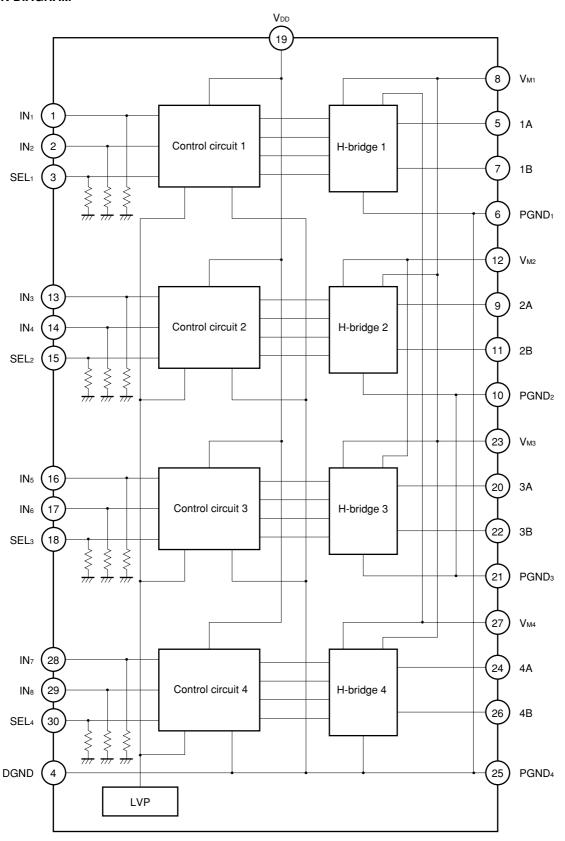

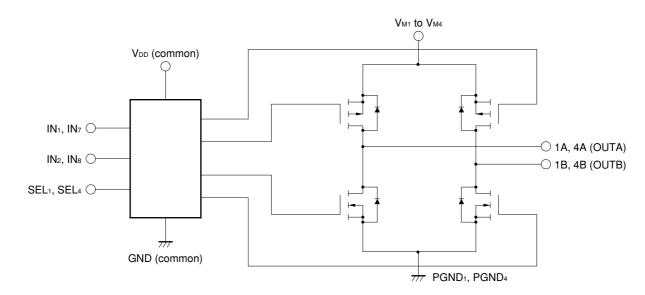

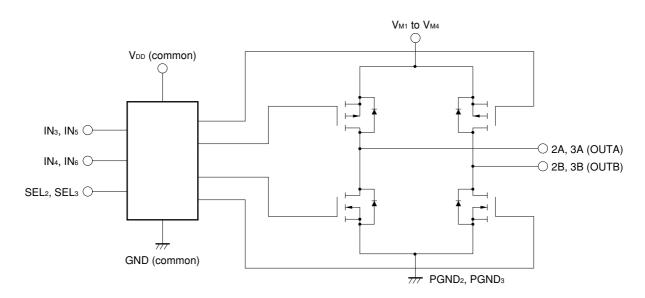

#### ★ BLOCK DIAGRAM

Cautions1. Connect all V<sub>M</sub> and GND pins.

- 2. Internally pulled down to GND via 50  $k\Omega.$

- 3. LVP (Low-voltage prevention circuit) operates by VDD = 2.5 V (TYP.).

#### **FUNCTION TABLE**

| Function Table (common to all chs) |                 |     |        |      |  |

|------------------------------------|-----------------|-----|--------|------|--|

| Input                              |                 |     | Output |      |  |

| IN <sub>1</sub>                    | IN <sub>2</sub> | SEL | OUTA   | OUTB |  |

| Н                                  | L               | Н   | Н      | L    |  |

| L                                  | L               | Н   | L      | L    |  |

| L                                  | Н               | Н   | L      | Н    |  |

| Н                                  | Н               | Н   | Н      | Н    |  |

| ×                                  | ×               | L   | Z      | Z    |  |

Remark ×: Don't care

Z: High inpedance

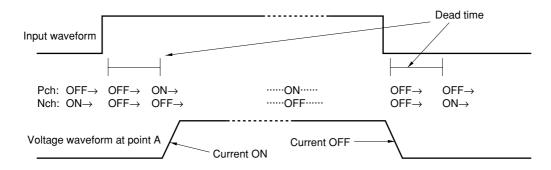

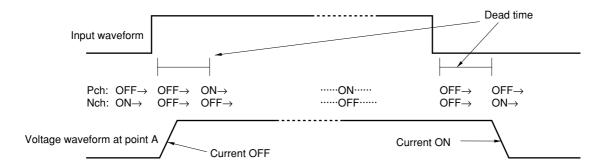

#### **ABOUT SWITCHING**

When output A is switched as shown in the figure on the right, a dead time (time during which both P ch and N ch are OFF) elapses to prevent through current. Therefore, the waveform of output A (rise time, fall time, and delay time) changes depending on whether output B is fixed to the high or low level.

The output voltage waveforms of A in response to an input waveform where output B is fixed to the low level (1) or high level (2) are shown below.

# Pch Pch Nch Nch

#### (1) Output B: Fixed to low level

Output A: Switching operation (Operations of P ch and N ch are shown.)

Output A goes into a high-impedance state and is in an undefined status during the dead time period. Because output B is pulled down by the load, a low level is output to A.

#### (2) Output B: Fixed to high level

Output A: Switching operation (Operations of P ch and N ch are shown.)

Output A goes into a high-impedance state and is in an undefined status during the dead time period. Because output B is pulled up by the load, a high level is output to A.

The switching characteristics shown on the preceding pages are specified as follows ("output at one side" means output B for H bridge output A, or output A for output B).

#### [Rise time]

Rise time when the output at one side is fixed to the low level (specified on current ON).

#### [Fall time]

Fall time when the output at one side is fixed to the high level (specified on current ON).

#### [Rising delay time]

Rising delay time when the output at one side is fixed to the low level (specified on current ON).

#### [Falling delay time]

Falling delay time when the output at one side is fixed to the high level (specified on current ON).

#### [Change in rising delay time]

Change (difference) in the rising delay time between when the output at one side is fixed to the low level and when the output at the other side is fixed to the high level.

#### [Change in falling delay time]

Change (difference) in falling delay time between when the output at one side is fixed to the low level and when the output at the other side is fixed to the high level.

#### [Rising delay time differential]

Difference in rising delay time between output A and output B.

#### [Falling delay time differential]

Difference in falling delay time between output A and output B.

### Caution Because this IC switches a high current at high speeds, surge may occur due to the V<sub>M</sub> and GND wiring and inductance and degrade the performance of the IC.

On the PWB, keep the pattern width of the  $V_M$  and GND lines as wide and short as possible, and insert the bypass capacitors between  $V_M$  and GND at a location as close to the IC as possible.

Connect a low-inductance magnetic capacitor (4700 pF or more) and an electrolytic capacitor of 10  $\mu$ F or so, depending on the load current, in parallel.

#### RECOMMENDED SOLDERING CONDITIONS

The  $\mu$  PD16837 should be soldered and mounted under the following recommended conditions.

For soldering methods and conditions other than those recommended below, contact an NEC Electronics sales representative.

For technical information, see the following website.

Semiconductor Device Mount Manual (http://www.necel.com/pkg/en/mount/index.html)

#### **Type of Surface Mount Device**

30-PIN PLASTIC SSOP (7.62 mm (300))

| Soldering Method | Soldering Conditions                                                                                                                                                                                                                    | Recommended Condition Symbol |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Infrared reflow  | Package peak temperature: 235 °C; Time: 30 secs. MAX. (210 °C MIN.); Number of times: 3 times MAX.; Number of days: none <sup>Note</sup> ; Flux: Rosin-based flux with little chlorine content (chlorine: 0.2 Wt% MAX.) is recommended. | IR35-00-3                    |

| VPS              | Package peak temperature: 215 °C; Time: 40 secs. MAX. (200 °C MIN.); Number of times: 3 times MAX.; Number of days: none <sup>Note</sup> ; Flux: Rosin-based flux with little chlorine content (chlorine: 0.2 Wt% MAX.) is recommended. | VP-15-00-3                   |

| Wave soldering   | Package peak temperature: 260 °C; Time: 10 secs. MAX.; Number of times: once; Flux: Rosin-based flux with little chlorine content (chlorine: 0.2 Wt% MAX.) is recommended.                                                              | WS60-00-1                    |

**Note** Number of days in storage after the dry pack has been opened. The storage conditions are at 25 °C, 65% RH MAX.

Caution Do not use two or more soldering methods in combination.

#### NOTES FOR CMOS DEVICES -

#### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

- The information in this document is current as of September, 2003. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).