CANH

**VREF**

6 CANL

D AND N PACKAGE (TOP VIEW)

> 8 ΠRS

7

5

**TXN**

GND [

VCC [ 3

RXD

- Pin Compatible with PCA82C250 and DeviceNet, SDS

- ISO11898 Compatible

- High Speed, up to 1 Mbps

- Differential Transmit to the Bus and Receive from the Bus to the CAN Controller

- At Least 110 Nodes Can Be Connected

- **100-V Transient Protection on the Transmit** Output

- 24-V Supply Cross Wire Protection on **CANH and CANL**

- No Bus Loading When Powered Down

- Operates between -40°C to 85°C

- **Unitrode DeviceNet ID#107**

## description

The UC5350 Control Area Network Transceiver (CAN Transceiver) is designed for industrial applications employing the CAN serial communications physical layer per ISO 11898 standard. The device is a high-speed transceiver designed for use up to 1 Mbps. Especially designed for hostile environments, this device features cross wire, loss of ground, overvoltage, and overtemperature protections well as a wide common-mode range.

The transceiver interfaces the single-ended CAN controller with the differential CAN bus found in industrial and automotive applications. It operates over the -7-V to 12-V common-mode range of the bus and will withstand common-mode transients of -25 V to 18 V as well as Schaffner tests. Performance features include high differential-input impedance, a symmetrical-differential-signal driver and very-low propagation delay that improves bus bandwidth and length by reducing reflection and distortion.

The transceiver operates over a wide temperature range, -40°C to 85°C and is available in 8-pin SOIC and dual-in-line packages.

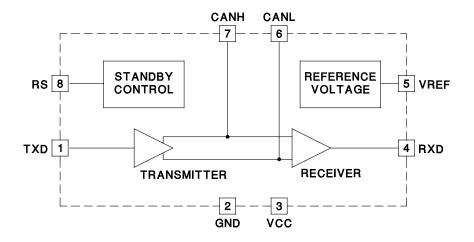

#### block diagram

UDG-96202

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### functional table (VCC = 4.5 V to 5.5 V)

| Inp    | uts | 0           | Outrant Marila | Out              | puts                 |

|--------|-----|-------------|----------------|------------------|----------------------|

| TXD    | RS  | System Mode | Output Mode    | VCANH - VCANL    | RXD                  |

| 0      | 0   | High Speed  | Dominant       | 1.5 V to 3 V     | 0                    |

| 1      | 0   | High Speed  | Recessive      | -120 mV to 12 mV | 1                    |

| High Z | 0   | High Speed  | Recessive      | -120 mV to 12 mV | 1                    |

|        |     | 0, "        |                |                  | 0 at Bus = Dominant  |

| X      | 1   | Standby     | _              | High Z           | 1 at Bus = Recessive |

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

|                                                      | <del>_</del>         |

|------------------------------------------------------|----------------------|

| Supply voltage                                       | 0.3 V to 9 V         |

| TXD, RXD, VREF, RS                                   | 0.3 V to VCC + 0.3 V |

| CANL, CANH, (0 V < VCC < 5.5 V)                      |                      |

| CANL, CANH, (non-destructive, non-operative)         |                      |

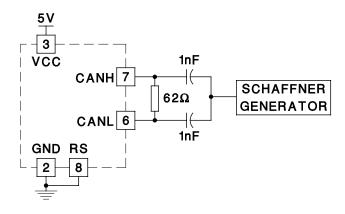

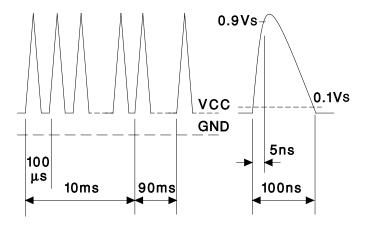

| CANL, CANH, (transient, Schaffner test) See Figure 1 | –150 V to 100 V      |

| Operating temperature                                |                      |

| Storage temperature, T <sub>stg</sub>                |                      |

| Junction temperature, $T_{J}$                        |                      |

| Lead temperature (soldering, 10 sec.)                | 300°C                |

| Crosswire protection maximum VBUS                    | 30 V                 |

| Bus differential voltage*                            | 30 V                 |

| Cross wire protection T <sub>A</sub>                 | –40°C to 125°C       |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>★</sup>Refers to Figures 9, 10, 11, 12 and 13.

NOTE: See Figure 7 for pulse timing.

UDG-96203-1

Figure 1. Schaffner Test

<sup>‡</sup> Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the *Interface Products Data Book* (TI Literature Number SLUU002) for thermal limitations and considerations of packages.

# electrical characteristics (total device disconnected from the bus line), VCC = 4.5 V to 5.5 V, 60 $\Omega$ in parallel with 100-pF load between CANH and CANL, $T_A = -40^{\circ}C$ to 85°C, $T_A = T_J$ , (unless otherwise stated)

| PARAMETER                            | TEST CONDITIONS                                | MIN          | TYP  | MAX     | UNITS |

|--------------------------------------|------------------------------------------------|--------------|------|---------|-------|

| Supply voltage                       |                                                | 4.5          |      | 5.5     | V     |

|                                      | Dominant, TXD = 1 V                            |              |      | 70      | mA    |

| Supply current                       | Recessive, TXD = 4 V                           |              | 9    | 14      | mA    |

|                                      | Standby, RS = 4 V                              |              | 1.2  | 2.0     | mA    |

| RS input current                     |                                                | -10          |      | 5       | μΑ    |

| RS voltage input = logic 1           | Standby                                        | 0.75VCC      |      |         | V     |

| RS Voltage Input = logic 0           | High speed                                     |              |      | 0.3VCC  | V     |

| Transmitter voltage input = logic 1  | Transmitter output recessive                   | 0.7VCC       |      |         | V     |

| Transmitter voltage input = logic 0  | Transmitter output dominant                    |              |      | 0.3VCC  | V     |

| Transmitter current input at logic 1 | TXD = 4 V                                      |              |      | 30      | μΑ    |

| Transmitter current input at logic 0 | TXD = 1 V                                      | -30          |      | 30      | μΑ    |

| Receiver voltage output = logic 1    | RXD = -100 mA, TXD = 4 V                       | VCC<br>-1.25 |      |         | V     |

| B                                    | $RXD = 1 \text{ mA}, \qquad TXD = 1 \text{ V}$ |              | 0.75 | 1.2     | V     |

| Receiver voltage output = logic 0    | RXD = 10 mA,                                   |              | 1.2  | 1.7     | V     |

| CANH, CANL input resistance          | No load, TXD = 4 V                             | 20           | 40   |         | kΩ    |

| Differential input resistance        | No load, TXD = 4 V                             | 40           | 80   |         | kΩ    |

| CANH, CANL input capacitance         | See Note 1                                     |              |      | 20      | pF    |

| Differential input capacitance       | See Note 1                                     |              |      | 10      | pF    |

| Reference output voltage             | VREF = ±50 mA                                  | 0.45VCC      |      | 0.55VCC | V     |

NOTE 1: Ensured by design. Not production tested.

electrical characteristics, (dc parameters for recessive state disconnected from the bus line), 60  $\Omega$  in parallel with 100-pF load between CANH and CANL,  $T_A = -40^{\circ}C$  to 85°C,  $T_A = T_J$ , (unless otherwise stated)

| PARAMETER                                       |          | TEST CONDITIONS                               |                            |  | MIN  | TYP | MAX  | UNITS |

|-------------------------------------------------|----------|-----------------------------------------------|----------------------------|--|------|-----|------|-------|

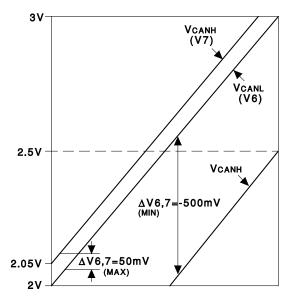

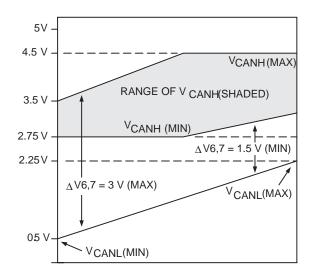

| VCANH, VCANL                                    | No load, | TXD = 4 V,                                    | See Figure 2               |  | 2    | 2.5 | 3    | V     |

| Differential output transmitter (VCANH - VCANL) | No load, | TXD = 4 V,                                    | See Figure 2               |  | -500 | 0   | 50   | mV    |

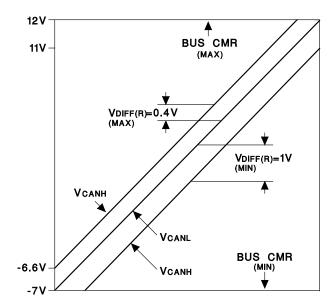

| Differential input receiver                     |          | de range = -7 V to 12 V,<br>externally driven | TXD = 4 V,<br>See Figure 3 |  | -1   |     | 0.40 | V     |

| Differential input resistance                   | No load  |                                               |                            |  | 40   |     |      | kΩ    |

| CANH, CANL input resistance                     |          |                                               |                            |  | 20   |     |      | kΩ    |

NOTE: Valid output of CANH, CANL during recessive state transmission. TXD = LOGIC 1

UDG-96204

Figure 2. Recessive State Voltage Diagram

NOTE: Valid voltage range of  $V_{CANH}$  for sensing dominant bus state as  $V_{CANL}$  varies over bus common range mode. TXD = LOGIC1 UDG-96205

Figure 3. Recessive State Voltage Diagram

electrical characteristics, (dc parameters for dominant state disconnected from the bus line), 60  $\Omega$  in parallel with 100-pF load between CANH and CANL. VCC = 4.5 V to 5.5 V, ) (unless otherwise stated)

| PARAMETER                                       | TEST CONDITIONS                                               |                                         | MIN                        | TYP  | MAX | UNITS |   |

|-------------------------------------------------|---------------------------------------------------------------|-----------------------------------------|----------------------------|------|-----|-------|---|

| CANH output voltage (VCANH)                     | TXD = 1 V,                                                    | See Figure 4                            |                            | 2.75 |     | 4.5   | V |

| CANL output voltage (VCANL)                     | TXD = 1 V,                                                    | See Figure 4                            |                            | 0.50 | 1.1 | 2.25  | V |

| Differential output transmitter (VCANH - VCANL) | TXD = 1 V,                                                    | See Figure 4                            |                            | 1.5  | 2   | 3     | V |

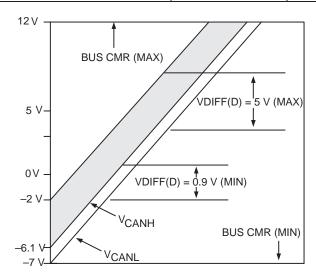

| Differential input receiver (VDIFF(D))          |                                                               | range = -2 to 7 V,<br>xternally driven, | TXD = 4 V,<br>See Figure 5 | 0.9  |     | 5     | V |

|                                                 | Common mode range = -7 to 12 V, CANH, CANL externally driven, |                                         | TXD = 4 V,<br>See Figure 5 | 1.0  |     | 5     | V |

NOTE: Valid voltage range of  $V_{CANH}$  for sensing dominant bus state as  $V_{CANL}$  varies. TXD = LOGIC 0 UDG-97160

Figure 4. Dominant State Voltage Diagram

NOTE: Valid voltage range of V<sub>CANH</sub> for sensing dominant bus state as V<sub>CANL</sub> varies over bus common mode range.

TXD = LOGIC 0

Figure 5. Dominant State Voltage Diagram

# transmitter characteristics, (disconnected from the bus line), 60 $\Omega$ in parallel with 100-pF load between CANH and CANL, (unless otherwise stated)

| PARAMETER                                             | TEST CONDITIONS                         | MIN  | TYP | MAX | UNITS |

|-------------------------------------------------------|-----------------------------------------|------|-----|-----|-------|

| Differential output transmitter                       | Dominant mode                           | 1.5  | 2   | 3   | V     |

| (VCANH - VCANL)                                       | Recessive mode                          | -500 |     | 50  | mV    |

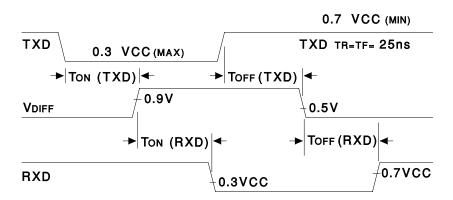

| Delay from TXD to bus active TON (TXD)                | See Figure 6                            |      | 50  | 100 | ns    |

| Delay from TXD to bus inactive T <sub>OFF</sub> (TXD) | 60 Ω across CANH and CANL, See Figure 6 |      | 20  | 110 | ns    |

# receiver characteristics, (disconnected from the bus line), 60 $\Omega$ in parallel with 100-pF load between CANH and CANL, (unless otherwise stated)

| PARAMETER                                 | TE                                      | TEST CONDITIONS                   |     |     | MAX | UNITS |

|-------------------------------------------|-----------------------------------------|-----------------------------------|-----|-----|-----|-------|

| Differential input receiver               | Dominant mode,                          | TXD = 4 V                         | 0.9 |     |     | V     |

| (VCANH – VCANL)                           | Recessive mode,                         | TXD = 4 V                         |     |     | 0.4 | V     |

| Differential input hysteresis             | TXD = 4 V                               |                                   | 75  | 150 |     | mV    |

| Delay From Bus to RXD (TON)               | Inactive to active bus,                 | See Figure 6                      |     | 60  | 100 | ns    |

| Delay from bus to RXD (T <sub>OFF</sub> ) | Active to inactive bus,<br>See Figure 6 | 60 $\Omega$ across CANH and CANL, |     | 80  | 115 | ns    |

### transceiver characteristics

| PARAMETER | TEST CONDITIONS                                                      | MIN | TYP | MAX | UNITS |

|-----------|----------------------------------------------------------------------|-----|-----|-----|-------|

|           | T <sub>ON</sub> (TXD) + T <sub>ON</sub> (RXD) inactive to active bus |     | 110 | 200 | ns    |

| Loop time | TOFF (TXD) + TOFF (RXD) active to inactive bus                       |     | 100 | 225 | ns    |

Figure 6. Transceiver ac Response

UDG-96208

# **APPLICATION INFORMATION**

Figure 7. Timing Diagram for Schaffner Tests

Table 1. Magnitude Specifications for V<sub>S</sub>

| ISO         | DIN 40839-1 | Schaffner     |

|-------------|-------------|---------------|

| DP7637/1    | (Draft)     | NSG500C/506C  |

| Up to 150 V | Up to 150 V | 40 V to 200 V |

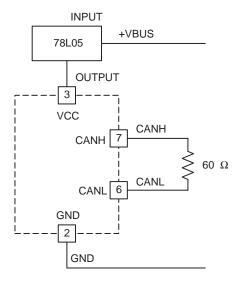

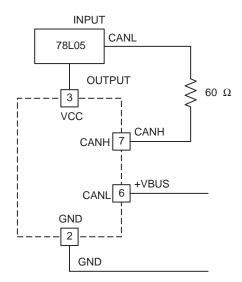

**Figure 8. Normal Connection**

OUTPUT

OUTPUT

VCC

VCC

CANH 7 +VBUS

CANL 6 GND

GND

CANL 6

CANL 6

CANL

CANH

**INPUT**

78L05

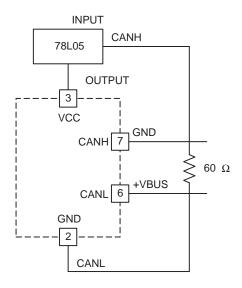

Figure 9. Crosswire No. 1

UDG-97176

UDG-96209

UDG-97175

### **APPLICATION INFORMATION**

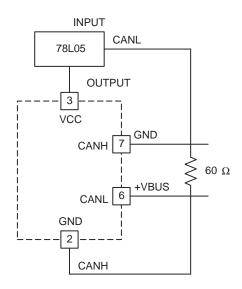

Figure 10. Crosswire No. 2 UDG-97177

Figure 11. Crosswire No. 3 UDG-97178

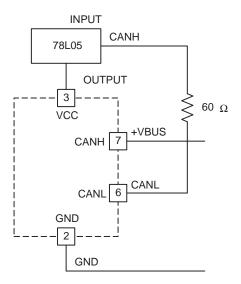

Figure 12. Crosswire No. 4 UDG-97179

Figure 13. Crosswire No. 5 UDG-97180

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated