#### DATA SHEET

### MOS INTEGRATED CIRCUIT

# $\mu$ PD78F9831

#### 8-BIT SINGLE-CHIP MICROCONTROLLER

The  $\mu$ PD78F9831 is an 8-bit single-chip microcontroller (for LCD driving) of the 78K/0S series.

The  $\mu$ PD78F9831 is produced by replacing the internal ROM of the  $\mu$ PD789830 with larger flash memory.

Flash memory can be written or erased electrically without having to remove it from board. Therefore, the  $\mu$ PD78F9831 is best suited for prototypes in system development, low-volume production, or systems likely to be upgraded frequently.

The functions of the  $\mu$ PD78F9831 are described in the following user's manuals. Refer to these manuals when designing a system based on the  $\mu$ PD78F9831.

$\mu$ PD789830 Subseries User's Manual : U13679E 78K/0S Series User's Manual, Instruction : U11047E

#### **FEATURES**

- · Internal flash memory: 48 Kbytes

- RAM sizes

- Internal RAM : 2 Kbytes

- ★ LCD data RAM: 40 × 16 bits

- ★ Variable minimum instruction execution time: From high-speed (0.4 μs: With the main system clock running at 5.0 MHz) to very low-speed (122 μs: With the subsystem clock running at 32.768 kHz)

- 38 I/O ports

- Serial interface (UART00)

- LCD controller/driver

- Up to 40 segment signal outputs

- Up to 16 common signal outputs

- 1/5 bias mode

- · Four timers:

- 16-bit timer

- 8-bit timer

- Watch timer

- · Watchdog timer

- · Pulse output: Clock output/buzzer output

- · Built-in key return signal detection circuit

- Power supply voltage: VDD = 2.7 to 5.5 V

#### **APPLICATIONS**

Card readers

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

NEC  $\mu$ PD78F9831

#### **ORDERING INFORMATION**

| Part Number      | Package                                        |

|------------------|------------------------------------------------|

| μPD78F9831GC-8EU | 100-pin plastic LQFP (fine pitch) (14 × 14 mm) |

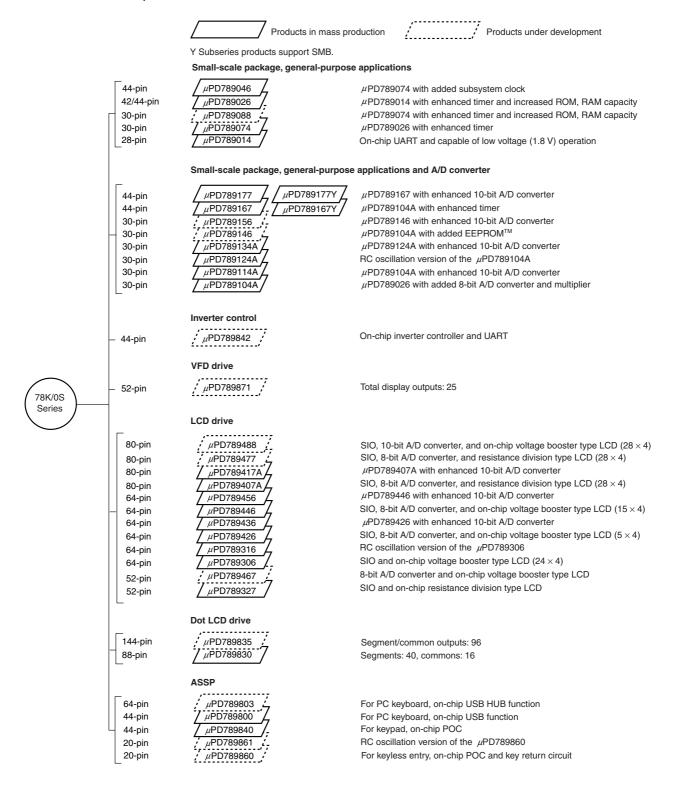

#### **★ 78K/0S SERIES DEVELOPMENT**

The 78K/0S series products are shown below. The subseries names are indicated in frames.

**Remark** The vacuum fluorescent display (VFD) is a typical name. In some documents, however, it is described as the fluorescent indicator panel (FIP®). The VFD and FIP have identical functions.

The major functional differences among the subseries are listed below.

|                    | Function   | ROM          |       | Tir  | mer    |      | 0 D:         | 40 Dit        |                   |     | V <sub>DD</sub> |                                               |

|--------------------|------------|--------------|-------|------|--------|------|--------------|---------------|-------------------|-----|-----------------|-----------------------------------------------|

|                    |            | Capacity     | 8-Bit | 16-  | Watch  | WDT  | 8-Bit<br>A/D | 10-Bit<br>A/D | Serial Interface  | I/O | MIN.            | Remark                                        |

| Subseries I        | Name       | (Bytes)      | 0-DII | Bit  | Walcii | WDI  | 7,0          | 7,0           |                   |     | Value           |                                               |

| Small scale,       | μPD789046  | 16 K         | 1 ch  | 1 ch | 1 ch   | 1 ch | _            | _             | 1 ch (UART: 1 ch) | 34  | 1.8 V           | _                                             |

| general-           | μPD789026  | 4 K to 16 K  |       |      | _      |      |              |               |                   |     |                 |                                               |

| purpose applica-   | μPD789088  | 16 K to 32 K | 3 ch  |      |        |      |              |               |                   | 24  |                 |                                               |

| tions              | μPD789074  | 2 K to 8 K   | 1 ch  |      |        |      |              |               |                   |     |                 |                                               |

|                    | μPD789014  | 2 K to 4 K   | 2 ch  | _    |        |      |              |               |                   | 22  |                 |                                               |

| Small-             | μPD789177  | 16 K to 24 K | 3 ch  | 1 ch | 1 ch   | 1ch  | _            | 8 ch          | 1 ch (UART: 1 ch) | 31  | 1.8 V           | -                                             |

| scale,<br>general- | μPD789167  |              |       |      |        |      | 8 ch         | -             |                   |     |                 |                                               |

| purpose applica-   | μPD789156  | 8 K to 16 K  | 1 ch  |      | _      |      | -            | 4 ch          |                   | 20  |                 | On-chip<br>EEPROM                             |

| tions +            | μPD789146  |              |       |      |        |      | 4 ch         | -             |                   |     |                 | LLI HOW                                       |

| A/D<br>function    | μPD789134A | 2 K to 8 K   |       |      |        |      | _            | 4 ch          |                   |     |                 | RC oscillation version                        |

|                    | μPD789124A |              |       |      |        |      | 4 ch         | -             |                   |     |                 | VOIGION                                       |

|                    | μPD789114A |              |       |      |        |      | -            | 4 ch          |                   |     |                 | _                                             |

|                    | μPD789104A |              |       |      |        |      | 4 ch         | -             |                   |     |                 |                                               |

| Inverter control   | μPD789842  | 8 K to 16 K  | 3 ch  | Note | 1 ch   | 1 ch | 8 ch         | -             | 1 ch (UART: 1 ch) | 30  | 4.0 V           | -                                             |

| VFD drive          | μPD789871  | 4 K to 8 K   | 3 ch  | _    | 1 ch   | 1 ch | -            | -             | 1 ch              | 33  | 2.7 V           | -                                             |

| LCD drive          | μPD789488  | 32 K         | 3 ch  | 1 ch | 1 ch   | 1 ch | _            | 8 ch          | 2 ch (UART: 1 ch) | 45  | 1.8 V           | -                                             |

|                    | μPD789477  | 24 K         |       |      |        |      | 8 ch         | -             |                   |     |                 |                                               |

|                    | μPD789417A | 12 K to 24 K |       |      |        |      | _            | 7 ch          | 1 ch (UART: 1 ch) | 43  |                 |                                               |

|                    | μPD789407A |              |       |      |        |      | 7 ch         | -             |                   |     |                 |                                               |

|                    | μPD789456  | 12 K to 16 K | 2 ch  |      |        |      | _            | 6 ch          |                   | 30  |                 |                                               |

|                    | μPD789446  |              |       |      |        |      | 6 ch         | _             |                   |     |                 |                                               |

|                    | μPD789436  |              |       |      |        |      | _            | 6 ch          |                   | 40  |                 |                                               |

|                    | μPD789426  |              |       |      |        |      | 6 ch         | _             |                   |     |                 |                                               |

|                    | μPD789316  | 8 K to 16 K  |       |      |        |      | -            |               | 2 ch (UART: 1 ch) | 23  |                 | RC oscillation version                        |

|                    | μPD789306  |              |       |      |        |      |              |               |                   |     |                 | _                                             |

|                    | μPD789427  | 4 K to 24 K  |       | _    |        |      | 1 ch         |               | _                 | 18  |                 |                                               |

|                    | μPD789327  |              |       |      |        |      | _            |               | 1 ch              | 21  |                 |                                               |

| Dot LCD<br>drive   | μPD789835  | 24 K to 60 K | 6 ch  | _    | 1 ch   | 1 ch | 3 ch         | _             | 1 ch (UART: 1 ch) | 28  | 1.8 V           | _                                             |

| unvo               | μPD789830  | 24 K         | 1 ch  | 1 ch |        |      | _            |               |                   | 30  | 2.7 V           |                                               |

| ASSP               | μPD789803  | 8 K to 16 K  | 2 ch  | _    | _      | 1 ch | _            | -             | 2 ch (USB: 1 ch)  | 41  | 3.6 V           | _                                             |

|                    | μPD789800  | 8 K          |       |      |        |      |              |               |                   | 31  | 4.0 V           |                                               |

|                    | μPD789840  |              |       |      |        |      | 4 ch         |               | 1 ch              | 29  | 2.8 V           |                                               |

|                    | μPD789861  | 4 K          |       |      |        |      | -            |               | _                 | 14  | 1.8 V           | RC oscillation<br>version, on-<br>chip EEPROM |

|                    | μPD789860  |              |       |      |        |      |              |               |                   |     |                 | On-chip<br>EEPROM                             |

Note 10-bit timer: 1 channel

#### **FUNCTIONS**

| Ite                   | em             | Function                                                                                                                                                    |  |  |  |

|-----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Internal memory       | Flash memory   | 48 Kbytes                                                                                                                                                   |  |  |  |

|                       | RAM            | 2 Kbytes                                                                                                                                                    |  |  |  |

|                       | LCD data RAM   | 40 × 16 bits                                                                                                                                                |  |  |  |

| Minimum instruction   | execution time | <ul> <li>0.4/1.6 μs (operation with main system clock running at 5.0 MHz)</li> <li>122 μs (operation with subsystem clock running at 32.768 kHz)</li> </ul> |  |  |  |

| General-purpose regi  | sters          | 8 bits × 8 registers                                                                                                                                        |  |  |  |

| Instruction set       |                | <ul><li>16-bit operations</li><li>Bit manipulations (such as set, reset, and test)</li></ul>                                                                |  |  |  |

| I/O ports             |                | Total of 38 port pins                                                                                                                                       |  |  |  |

|                       |                | <ul><li> 37 CMOS input/output pins</li><li> N-ch open-drain input/output pin</li></ul>                                                                      |  |  |  |

| Serial interface      |                | UART mode                                                                                                                                                   |  |  |  |

| LCD controller/driver |                | <ul> <li>Up to 40 segment signal outputs</li> <li>Up to 16 common signal outputs</li> <li>1/5 bias mode</li> </ul>                                          |  |  |  |

| Timers                |                | 16-bit timer     8-bit timer     Watch timer     Watchdog timer                                                                                             |  |  |  |

| Pulse output          |                | Clock output/buzzer output                                                                                                                                  |  |  |  |

| Vectored interrupt    | Maskable       | 10 internal and 6 external interrupts                                                                                                                       |  |  |  |

| sources               | Nonmaskable    | Internal interrupt                                                                                                                                          |  |  |  |

| Power supply voltage  | )              | V <sub>DD</sub> = 2.7 to 5.5 V                                                                                                                              |  |  |  |

| Operating ambient te  | mperature      | T <sub>A</sub> = -20 to +60 °C                                                                                                                              |  |  |  |

| Package               |                | 100-pin plastic LQFP (fine pitch) (14 × 14 mm)                                                                                                              |  |  |  |

### **CONTENTS**

|   | ١.  | PIN CONFIGURATION (TOP VIEW)                                            | /  |

|---|-----|-------------------------------------------------------------------------|----|

|   | 2.  | BLOCK DIAGRAM                                                           | 9  |

|   | 3.  | PIN FUNCTIONS                                                           | 10 |

|   |     | 3.1 Port Pins                                                           | 10 |

|   |     | 3.2 Non-Port Pins                                                       |    |

|   |     | 3.3 Pin Input/Output Circuits and Handling of Unused Pins               | 12 |

|   | 4.  | MEMORY SPACE                                                            | 15 |

|   | 5.  | INTERRUPT FUNCTIONS                                                     | 16 |

|   | 6.  | FLASH MEMORY PROGRAMMING                                                | 18 |

|   |     | 6.1 Selecting the Transmission Method                                   | 18 |

|   |     | 6.2 Flash Memory Programming Functions                                  | 19 |

|   |     | 6.3 Connecting the Flashpro III                                         |    |

|   |     | 6.4 Example of Settings for Flashpro III (PG-FP3)                       | 20 |

|   | 7.  | INSTRUCTION SET OVERVIEW                                                | 21 |

|   |     | 7.1 Legend                                                              | 21 |

|   |     | 7.2 Operations                                                          | 23 |

|   | 8.  | ELECTRICAL CHARACTERISTICS                                              | 28 |

|   | 9.  | PACKAGE DRAWINGS                                                        | 38 |

| t | 10. | RECOMMENDED SOLDERING CONDITIONS                                        | 39 |

|   | АР  | PENDIX A DIFFERENCES BETWEEN THE $\mu$ PD78F9831 AND MASKED ROM PRODUCT | 40 |

|   | ΑP  | PPENDIX B DEVELOPMENT TOOLS                                             | 41 |

|   | ΑP  | PENDIX C RELATED DOCUMENTS                                              | 43 |

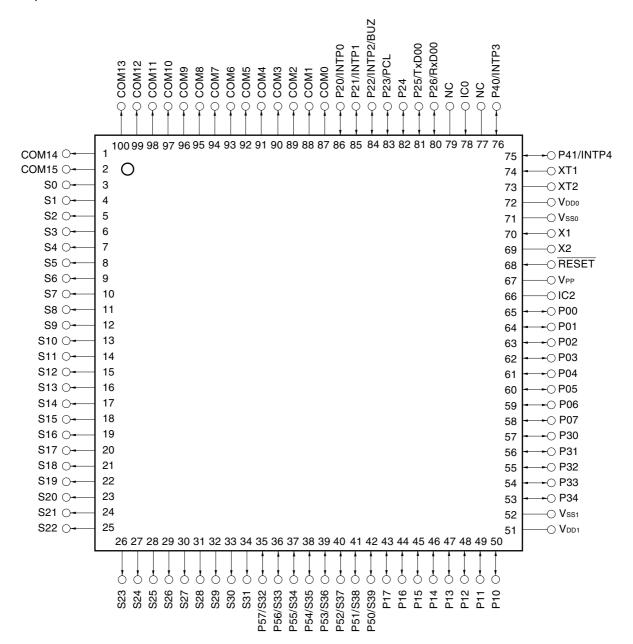

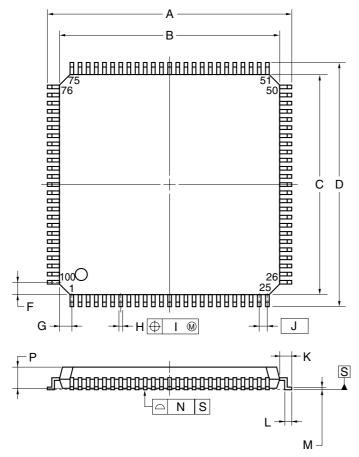

#### 1. PIN CONFIGURATION (TOP VIEW)

• 100-pin plastic LQFP (fine pitch) (14 × 14 mm)

$\mu$ PD78F9831GC-8EU

- Cautions 1. In normal operation mode, connect the VPP pin directly to the Vsso or Vss1 pin.

- 2. Connect the IC0 (Internally Connected) pin directly to the Vsso or Vss1 pin.

- 3. Leave the IC2 pin open.

NEC  $\mu$ PD78F9831

BUZ : Buzzer Clock PCL : Programming Clock

COM0-COM15 : Common Output RESET : Reset

IC0, IC2: Internally ConnectedRxD00: Receive DataINTP0-INTP4: External Interrupt InputS0-S39: Segment OutputNC: Non-connectionTxD00: Transmit Data

P00-P07 : Port 0 VDD0, VDD1 : Power Supply

P30-P34 : Port 3 X1, X2 : Crystal (Main system Clock)

P40, P41 : Port 4 XT1, XT2 : Crystal (Subsystem Clock)

P50-P57 : Port 5

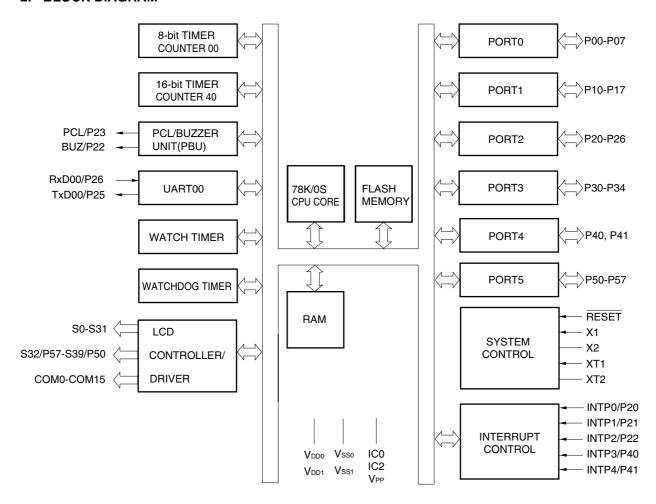

#### 2. BLOCK DIAGRAM

#### 3. PIN FUNCTIONS

#### 3.1 Port Pins

| Pin Name | I/O | Function                                                                                                                                                                                        | When Reset | Also Used As |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|

| P00-P07  | I/O | Port 0 8-bit input/output port Can be set to either input or output in 1-bit units When used as an input port, whether the on-chip pull-up resistor is to be used can be specified by software. | Input      | -            |

| P10-P17  | I/O | Port 1 8-bit input/output port Can be set to either input or output in 1-bit units When used as an input port, whether the on-chip pull-up resistor is to be used can be specified by software. | Input      | -            |

| P20      | I/O | Port 2                                                                                                                                                                                          | Input      | INTP0        |

| P21      |     | 7-bit input/output port  Can be set to either input or output in 1-bit units                                                                                                                    |            | INTP1        |

| P22      |     | P24 can be used as an N-ch open-drain input/output port pin.                                                                                                                                    |            | INTP2/BUZ    |

| P23      |     |                                                                                                                                                                                                 |            | PCL          |

| P24      |     |                                                                                                                                                                                                 |            | _            |

| P25      |     |                                                                                                                                                                                                 |            | TxD00        |

| P26      |     |                                                                                                                                                                                                 |            | RxD00        |

| P30-P34  | I/O | Port 3 5-bit input/output port Can be set to either input or output in 1-bit units When used as an input port, whether the on-chip pull-up resistor is to be used can be specified by software. | Input      | -            |

| P40      | I/O | Port 4                                                                                                                                                                                          | Input      | INTP3        |

| P41      |     | 2-bit input/output port  Can be set to either input or output in 1-bit units                                                                                                                    |            | INTP4        |

| P50-P57  | I/O | Port 5 8-bit input/output port Can be set to either input or output in 1-bit units                                                                                                              | Input      | S39-S32      |

#### 3.2 Non-Port Pins

| Pin Name         | I/O    | Function                                                                                                                                                                                             | When Reset | Also Used As |

|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|

| INTP0            | Input  | External interrupt input for which effective edges (rising and/or                                                                                                                                    | Input      | P20          |

| INTP1            | 1      | falling edges) can be specified                                                                                                                                                                      |            | P21          |

| INTP2            | 1      |                                                                                                                                                                                                      |            | P22/BUZ      |

| INTP3            | 1      |                                                                                                                                                                                                      |            | P40          |

| INTP4            | 1      |                                                                                                                                                                                                      |            | P41          |

| RxD00            | Input  | Serial data input to asynchronous serial interface                                                                                                                                                   | Input      | P26          |

| TxD00            | Output | Serial data output from asynchronous serial interface                                                                                                                                                | Input      | P25          |

| BUZ              | Output | Buzzer output                                                                                                                                                                                        | Input      | P22/INTP2    |

| PCL              | Output | Clock output                                                                                                                                                                                         | Input      | P23          |

| S0-S31           | Output | Segment signal output from LCD controller/driver                                                                                                                                                     | Output     | _            |

| S32-S39          | 1      |                                                                                                                                                                                                      |            | P57-P50      |

| COM0-<br>COM15   | Output | Common signal output from LCD controller/driver                                                                                                                                                      | Output     | -            |

| X1               | Input  | Connected to crystal for main system clock oscillation                                                                                                                                               | -          | _            |

| X2               | _      |                                                                                                                                                                                                      | _          | -            |

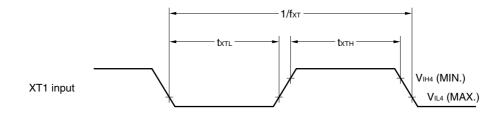

| XT1              | Input  | Connected to crystal for subsystem clock oscillation                                                                                                                                                 | -          | -            |

| XT2              | _      |                                                                                                                                                                                                      | _          | _            |

| RESET            | Input  | System reset input                                                                                                                                                                                   | Input      | -            |

| V <sub>DD0</sub> | _      | Positive supply voltage for ports                                                                                                                                                                    | -          | _            |

| V <sub>DD1</sub> | _      | Positive supply voltage for circuits other than ports                                                                                                                                                | -          | _            |

| Vsso             | _      | Port section ground potential                                                                                                                                                                        | -          | -            |

| V <sub>SS1</sub> | _      | Ground potential of circuits other than ports                                                                                                                                                        | -          | -            |

| NC               | _      | This pin is not internally connected. Connect this pin directly to the Vsso or Vss1 pin (it can also be left open).                                                                                  | _          | -            |

| IC0              | Input  | This pin is internally connected. Connect this pin directly to the Vsso or Vss <sub>1</sub> pin.                                                                                                     | -          | -            |

| IC2              | _      | This pin is internally connected. Leave this pin open.                                                                                                                                               | -          | _            |

| V <sub>PP</sub>  | _      | This pin is used to set flash memory programming mode and applies a high voltage when a program is written or verified. In normal operation mode, connect this pin directly to the Vsso or Vss1 pin. | _          | -            |

Data Sheet U13477EJ1V0DS 11

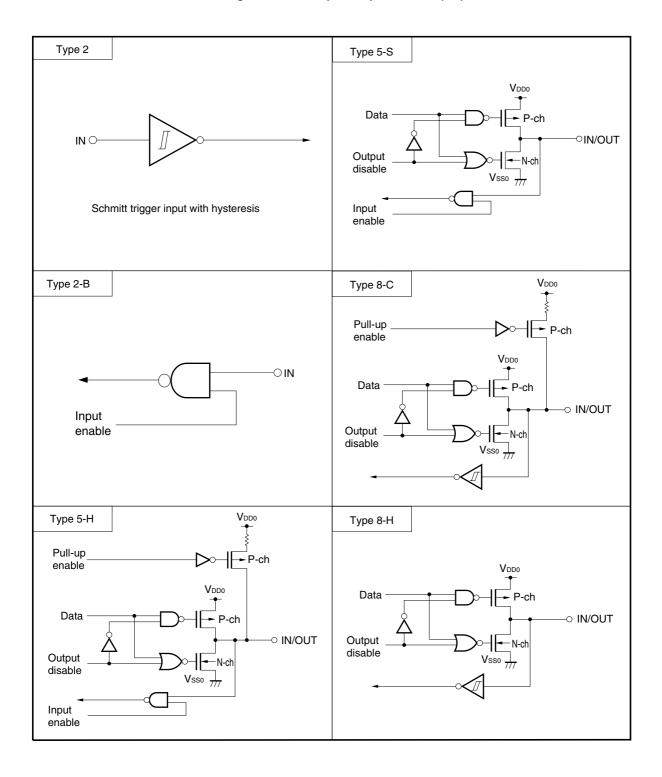

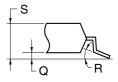

#### 3.3 Pin Input/Output Circuits and Handling of Unused Pins

Table 3-1 lists the types of input/output circuits for each pin and explains how unused pins are handled. Figure 3-1 shows the configuration of each type of input/output circuit.

Table 3-1. Type of Input/Output Circuit for Each Pin and Handling of Unused Pins

| Pin Name            | I/O Circuit Type | I/O    | Recommended Connection Of Unused Pins                                                           |

|---------------------|------------------|--------|-------------------------------------------------------------------------------------------------|

| P00-P07             | 5-H              | I/O    | Connect these pins to the VDD0, VDD1, VSS0, or VSS1 pin via the respective                      |

| P10-P17             | 1                |        | resistor.                                                                                       |

| P20/INTP0           | 8-H              |        | Connect these pins to the V <sub>SS0</sub> or V <sub>SS1</sub> pin via the respective resistor. |

| P21/INTP1           |                  |        |                                                                                                 |

| P22/INTP2/BUZ       |                  |        |                                                                                                 |

| P23/PCL             | 5-S              |        | Connect these pins to the VDD0, VDD1, VSS0, or VSS1 pin via the respective                      |

| P24                 | 13-AB            |        | resistor.                                                                                       |

| P25/TxD00           | 5-S              |        |                                                                                                 |

| P26/RxD00           | 8-H              |        |                                                                                                 |

| P30-P34             | 8-C              |        |                                                                                                 |

| P40/INTP3           | 8-H              |        | Connect these pins to the V <sub>SS0</sub> or V <sub>SS1</sub> pin via the respective resistor. |

| P40/INTP4           |                  |        |                                                                                                 |

| P50/S39-<br>P57/S32 | 17-I             |        | Connect these pins to the VDD0, VDD1, VSS0, or VSS1 pin via the respective resistor.            |

| S0-S31              | 17-H             | Output | Leave these pins open.                                                                          |

| COM0-COM15          | 18-C             |        |                                                                                                 |

| XT1                 | 16               | Input  | Connect this pin to the Vsso or Vss1 pin.                                                       |

| XT2                 |                  | -      | Leave this pin open.                                                                            |

| RESET               | 2                | Input  | _                                                                                               |

| NC                  | _                | -      | Connect this pin directly to the Vsso or Vss1 pin, or leave it open.                            |

| IC0                 | -                | Input  | Connect this pin directly to the Vsso or Vss1 pin.                                              |

| IC2                 | 2-B              | -      | Leave this pin open.                                                                            |

| V <sub>PP</sub>     | -                | -      | Connect this pin directly to the V <sub>SS0</sub> or V <sub>SS1</sub> pin.                      |

Figure 3-1. Pin Input/Output Circuits (1/2)

Type 13-AB Type 17-I -○ IN/OUT Data ■ N-ch disable Vsso /// OIN/OUT  $V_{\text{DD0}}$ Output disable Vsso 777 RD -P-ch Input enable Port Input buffer with intermediate withstand voltage read  $V_{LC0}$ Type 16  $V_{\text{LC3}}$ feedback cut-off SEG P-ch data N-ch  $V_{\text{LC2}}$ N-ch O XT2 XT1 Type 17-H Type 18-C  $V_{LC0}$  $V_{\text{\tiny LC0}}$  $V_{\text{LC1}}$ N-ch OUT OUT СОМ SEG N-ch P-ch data data  $V_{LC4}$  $V_{LC2}$ N-ch

Figure 3-1. Pin Input/Output Circuits (2/2)

Vss1 ///

Vss1

#### 4. MEMORY SPACE

The  $\mu$ PD78F9831 can access up to 64 Kbytes of memory space. Figure 4-1 shows the memory map.

FFFFH Special function register  $256\times 8$  bits FF00H **FEFFH** Internal high-speed RAM  $1,024 \times 8$  bits FB00H **FAFFH** Unusable FA50H FA4FH LCD data RAM  $40 \times 16 \text{ bits}$ FA00H F9FFH Data memory space Unusable F700H F6FFH Internal low-speed RAM  $1,024 \times 8$  bits F300H **BFFFH** F2FFH Unusable C000H Program area BFFFH 0080H Internal flash memory 007FH CALLT table area  $49,152 \times 8$  bits Program memory 0040H space 003FH Program area 0020H 001FH Vector table area 0000H 0000H

Figure 4-1. Memory Map

#### 5. INTERRUPT FUNCTIONS

There are two types and 17 sources of interrupt functions as shown below.

Nonmaskable interrupt: 1 sourceMaskable interrupts : 16 sources

**Table 5-1. Interrupt Source List**

| International Trans | Note 1                     |          | Interrupt Source                                               | Internal/ | Vector           | Basic                                |

|---------------------|----------------------------|----------|----------------------------------------------------------------|-----------|------------------|--------------------------------------|

| Interrupt Type      | Priority <sup>Note 1</sup> | Name     | Trigger                                                        | External  | Table<br>Address | Configuration Type <sup>Note 2</sup> |

| Nonmaskable         | П                          | INTWDT   | Watchdog timer overflow (watchdog timer mode 1 selected)       | Internal  | 0004H            | (A)                                  |

| Maskable            | 0                          | INTWDT   | Watchdog timer overflow (interval timer mode selected)         |           |                  | (B)                                  |

|                     | 1                          | INTP0    | Pin input edge detection                                       | External  | 0006H            | (C)                                  |

|                     | 2                          | INTP1    |                                                                |           | H8000            |                                      |

|                     | 3                          | INTP2    |                                                                |           | 000AH            |                                      |

|                     | 4                          | INTSER00 | Occurrence of serial interface (UART00) reception error        | Internal  | 000CH            | (B)                                  |

|                     | 5                          | INTSR00  | End of serial interface (UART00) reception                     |           | 000EH            |                                      |

|                     | 6                          | INTST00  | End of serial interface (UART00) transmission                  |           | 0010H            |                                      |

|                     | 7                          | INTTM40  | Generation of 16-bit timer 40 match signal                     |           | 0012H            |                                      |

|                     | 8                          | INTTM41  | Occurrence of 16-bit timer 40 overflow                         |           | 0014H            |                                      |

|                     | 9                          | INTTM4   | Logical OR of 16-bit timer 40 match signal and overflow signal |           | 0016H            |                                      |

|                     | 10                         | INTTM00  | Generation of 8-bit timer 00 match signal                      |           | 0018H            |                                      |

|                     | 11                         | INTWTI   | Interval timer interrupt                                       |           | 001AH            |                                      |

|                     | 12                         | INTWT    | Watch timer interrupt                                          |           | 001CH            |                                      |

|                     | 13                         | INTKR00  | Key return signal detection                                    | External  | 001EH            | (C)                                  |

|                     | 14                         | INTP3    | Pin input edge detection                                       |           | 0020H            |                                      |

|                     | 15                         | INTP4    |                                                                |           | 0022H            |                                      |

**Notes 1.** Priorities are intended for the priority for two or more simultaneously generated maskable interrupts. 0 is the highest priority and 15 is the lowest priority.

2. Basic configuration types (A) to (C) correspond to (A) to (C) of Figure 5-1.

**Remark** Only one of the two watchdog timer interrupt sources, non-maskable or maskable (internal), can be selected.

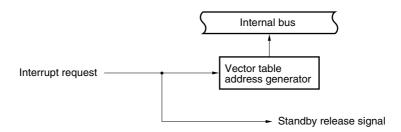

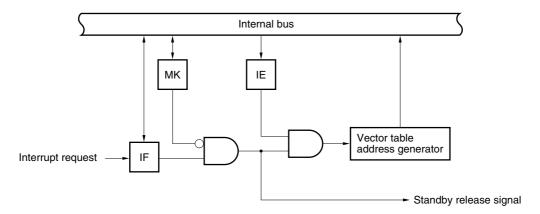

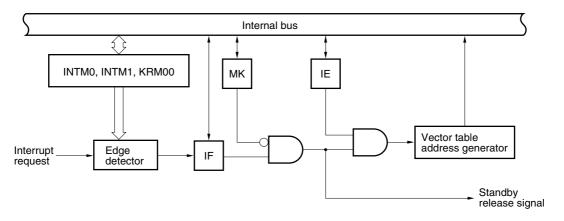

Figure 5-1. Basic Configuration of Interrupt Function

#### (A) Internal nonmaskable interrupt

#### (B) Internal maskable interrupt

#### (C) External maskable interrupt

INTM0: External interrupt mode register 0

INTM1: External interrupt mode register 1

KRM00: Key return mode register 00

IF : Interrupt request flag

IE : Interrupt enable flag

MK : Interrupt mask flag

Data Sheet U13477EJ1V0DS 17

#### 6. FLASH MEMORY PROGRAMMING

Flash memory is used as the built-in program memory of the  $\mu$ PD78F9831.

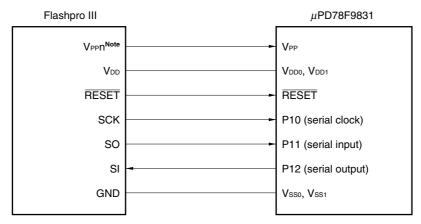

The flash memory can be written even while the device is mounted in the target system (on-board write). To write a program into the flash memory, connect the dedicated flash writer (Flashpro III (model number: FL-PR3, PG-FP3)) to both the host machine and target system.

Remark The FL-PR3 is manufactured by Naito Densei Machida Mfg. Co., Ltd.

#### 6.1 Selecting the Transmission Method

The Flashpro III writes into flash memory by means of serial transmission. The transmission method to be used for writing is selected from those listed in Table 6-1. To select a transmission method, use the format shown in Figure 6-1, according to the number of VPP pulses listed in Table 6-1.

| Transmission Method                  | Pins <sup>Note 1</sup>                                                    | Number of VPP Pulses |

|--------------------------------------|---------------------------------------------------------------------------|----------------------|

| UART                                 | TxD00/P25<br>RxD00/P26                                                    | 8                    |

| Pseudo 3-wire mode <sup>Note 2</sup> | P10 (serial clock input) P11 (serial data input) P12 (serial data output) | 12                   |

Table 6-1. Transmission Methods

- Notes 1. When flash memory programming mode is set, all pins not used for memory programming enter the same state as that immediately after a reset. Therefore, when the external device connected to a port cannot recognize that state of the port immediately after a reset, the pins must be connected to the VDD0 or VDD1 pin, or the Vss0 or Vss1 pin via a resistor.

- 2. Serial transfer by controlling the ports using software

Caution To select a transmission method, always use the corresponding number of VPP pulses listed in Table 6-1.

10 V  $V_{PP}$  $V_{DD}$ Vss

Figure 6-1. Format of Transmission Method Selection

18

$V_{DD}$

Vss

RESET

#### 6.2 Flash Memory Programming Functions

Flash memory writing and other operations can be performed by transmitting/receiving commands and data according to the selected transmission method. Table 6-2 lists the main flash memory programming functions.

Table 6-2. Main Flash Memory Programming Functions

| Function          | Description                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------|

| Batch erase       | Erases the entire contents of memory.                                                                               |

| Batch blank check | Checks that the entire contents of memory have been erased.                                                         |

| Data write        | Write to the flash memory according to the specified write start address and number of bytes of data to be written. |

| Batch verify      | Compares the entire contents of memory with the input data.                                                         |

#### 6.3 Connecting the Flashpro III

The connection between the Flashpro III and  $\mu$ PD78F9831 varies with the transmission method (UART or pseudo 3-wire). Figures 6-2 and 6-3 show the connection for each transmission method.

Figure 6-2. Flashpro III Connection in UART Mode

Note n: 1 or 2

Figure 6-3. Flashpro III Connection in Pseudo 3-Wire Mode

Note n: 1 or 2

#### 6.4 Example of Settings for Flashpro III (PG-FP3)

When writing to flash memory using Flashpro III (PG-FP3), make the following settings.

- <1> Load a parameter file.

- <2> Select the mode of serial communication and serial clock with a type command.

- <3> Make the settings according to the example of settings for PG-FP3 shown below.

Table 6-3. Example of Settings for PG-FP3

| Communication Mode | Example of Settings for F | G-FP3                       | VPP Pulse NumberNote 1 |

|--------------------|---------------------------|-----------------------------|------------------------|

| UART               | COMM PORT                 | UART-ch0                    | 8                      |

|                    | CPU CLK                   | On Target Board             |                        |

|                    | On Target Board           | 4.1943 MHz                  |                        |

|                    | UART BPS                  | 9,600 bps <sup>Note 2</sup> |                        |

| Pseudo 3-wire mode | COMM PORT                 | Port A                      | 12                     |

|                    | CPU CLK                   | On Target Board             |                        |

|                    |                           | In Flashpro                 |                        |

|                    | On Target Board           | 4.1943 MHz                  |                        |

|                    | SIO CLK                   | 1.0 kHz                     |                        |

|                    | In Flashpro               | 4.0 MHz                     |                        |

|                    | SIO CLK                   | 1.0 kHz                     |                        |

**Notes 1**. This is the number of VPP pulses that are supplied by the Flashpro III at serial communication initialization. The pins that will be used for communication are determined according to this number.

2. Select one of 9,600 bps, 19,200 bps, 38,400 bps, or 76,800 bps.

Remark COMM PORT: Serial port selection

SIO CLK : Serial clock frequency selection

CPU CLK : Input CPU clock source selection

#### 7. INSTRUCTION SET OVERVIEW

The instruction set for the  $\mu$ PD78F9831 is listed later.

#### 7.1 Legend

#### 7.1.1 Operand formats and descriptions

The description made in the operand field of each instruction conforms to the operand format for the instructions listed below (the details conform with the assembly specification). If more than one operand format is listed for an instruction, one is selected. Uppercase letters, #, !, \$, and a pair of [ and ] are used to specify keywords, which must be written exactly as they appear. The meanings of these special characters are as follows:

- #: Immediate data specification

- \$: Relative address specification

- !: Absolute address specification

- [ and ]: Indirect address specification

Immediate data should be described using appropriate values or labels. The specification of values and labels must be accompanied by #, !, \$, or a pair of [ and ].

Operand registers, expressed as r or rp in the formats, can be described using both functional names (X, A, C, etc.) and absolute names (R0, R1, R2, and other names listed in Table 7-1).

Table 7-1. Operand Formats and Descriptions

| Format | Description                                                    |

|--------|----------------------------------------------------------------|

| r      | X (R0), A (R1), C (R2), B (R3), E (R4), D (R5), L (R6), H (R7) |

| rp     | AX (RP0), BC (RP1), DE (RP2), HL (RP3)                         |

| sfr    | Special function register symbol                               |

| saddr  | FE20H to FF1FH: Immediate data or label                        |

| saddrp | FE20H to FF1FH: Immediate data or label (even addresses only)  |

| addr16 | 0000H to FFFFH: Immediate data or label                        |

|        | (only even address for 16-bit data transfer instructions)      |

| addr5  | 0040H to 007FH: Immediate data or label (even addresses only)  |

| word   | 16-bit immediate data or label                                 |

| byte   | 8-bit immediate data or label                                  |

| bit    | 3-bit immediate data or label                                  |

Data Sheet U13477EJ1V0DS 21

#### 7.1.2 Descriptions of the operation field

A : A register (8-bit accumulator)

X : X register

B : B register

C : C register

D : D register

E : E register

H : H register

L : L register

AX : AX register pair (16-bit accumulator)

BC : BC register pair

DE : DE register pair

HL : HL register pair

PC : Program counter

SP : Stack pointer

PSW: Program status word

CY: Carry flag

AC : Auxiliary carry flag

Z : Zero flag

IE : Interrupt request enable flag

NMIS : Flag to indicate that a nonmaskable interrupt is being handled

() : Contents of a memory location indicated by a parenthesized address or register name

XH, XL : Upper and lower 8 bits of a 16-bit register

∴ Logical product (AND)

✓ Logical sum (OR)

✓ Exclusive OR

∴ Inverted data

addr16: 16-bit immediate data or label

jdisp8 : Signed 8-bit data (displacement value)

#### 7.1.3 Description of the flag operation field

(blank): No change

0 : To be cleared to 0 1 : To be set to 1

$\times$  : To be set or cleared according to the result

R : To be restored to the previous value

#### 7.2 Operations

| Marana   | 0                  | Duta | Olasala | Operation                       |   | Flag | J          |

|----------|--------------------|------|---------|---------------------------------|---|------|------------|

| Mnemonic | Operand            | Byte | Clock   | Operation                       | Z | AC   | CY         |

| MOV      | r, #byte           | 3    | 6       | $r \leftarrow \text{byte}$      |   |      |            |

|          | saddr, #byte       | 3    | 6       | (saddr) ← byte                  |   |      |            |

|          | sfr, #byte         | 3    | 6       | sfr ← byte                      |   |      |            |

|          | A, r               | 2    | 4       | A ← r                           |   |      |            |

|          | r, A               | 2    | 4       | $r \leftarrow A$                |   |      |            |

|          | A, saddr           | 2    | 4       | A ← (saddr)                     |   |      |            |

|          | saddr, A           | 2    | 4       | (saddr) ← A                     |   |      |            |

|          | A, sfr             | 2    | 4       | A ← sfr                         |   |      |            |

|          | sfr, A 2 4 sfr ← A |      | sfr ← A |                                 |   |      |            |

|          | A, !addr16         | 3    | 8       | A ← (addr16)                    |   |      |            |

|          | !addr16, A         | 3    | 8       | (addr16) ← A                    |   |      |            |

|          | PSW, #byte         | 3    | 6       | PSW ← byte                      | × | ×    | ×          |

|          | A, PSW             | 2    | 4       | $A \leftarrow PSW$              |   |      |            |

|          | PSW, A             | 2    | 4       | PSW ← A                         | × | ×    | ×          |

|          | A, [DE]            | 1    | 6       | $A \leftarrow (DE)$             |   |      |            |

|          | [DE], A            | 1    | 6       | (DE) ← A                        |   |      |            |

|          | A, [HL]            | 1    | 6       | $A \leftarrow (HL)$             |   |      |            |

|          | [HL], A            | 1    | 6       | (HL) ← A                        |   |      |            |

|          | A, [HL + byte]     | 2    | 6       | A ← (HL + byte)                 |   |      |            |

|          | [HL + byte], A     | 2    | 6       | (HL + byte) ← A                 |   |      |            |

| XCH      | A, X               | 1    | 4       | $A \leftrightarrow X$           |   |      |            |

|          | A, r               | 2    | 6       | $A \leftrightarrow r$           |   |      |            |

|          | A, saddr           | 2    | 6       | $A \leftrightarrow (saddr)$     |   |      |            |

|          | A, sfr             | 2    | 6       | $A \leftrightarrow (sfr)$       |   |      |            |

|          | A, [DE]            | 1    | 8       | $A \leftrightarrow (DE)$        |   |      |            |

|          | A, [HL]            | 1    | 8       | $A \leftrightarrow (HL)$        |   |      |            |

|          | A, [HL + byte]     | 2    | 8       | $A \leftrightarrow (HL + byte)$ |   |      |            |

| MOVW     | rp, #word          | 3    | 6       | rp ← word                       |   |      |            |

|          | AX, saddrp         | 2    | 6       | $AX \leftarrow (saddrp)$        |   |      | _          |

|          | saddrp, AX         | 2    | 8       | (saddrp) ← AX                   |   |      | · <u> </u> |

|          | AX, rp             | 1    | 4       | $AX \leftarrow rp$              |   |      |            |

|          | rp, AX             | 1    | 4       | $rp \leftarrow AX$              |   |      |            |

**Notes 1.** Except when r = A.

- **2.** Except when r = A or X.

- **3.** Only when rp = BC, DE, or HL.

**Remark** The instruction clock cycle is based on the CPU clock (fcPU), specified in the processor clock control register (PCC).

Data Sheet U13477EJ1V0DS 23

| Mnomonic | Operand        | B) #0 | Clock | Operation                               |   | Fla | g  |

|----------|----------------|-------|-------|-----------------------------------------|---|-----|----|

| Mnemonic | Operand        | Byte  | Clock | Operation                               | Z | AC  | CY |

| XCHW     | AX, rp         | 1     | 8     | $AX \leftrightarrow rp$                 |   |     |    |

| ADD      | A, #byte       | 2     | 4     | $A, CY \leftarrow A + byte$             | × | ×   | ×  |

|          | saddr, #byte   | 3     | 6     | (saddr), CY ← (saddr) + byte            | × | ×   | ×  |

|          | A, r           | 2     | 4     | $A, CY \leftarrow A + r$                | × | ×   | ×  |

|          | A, saddr       | 2     | 4     | A, CY ← A + (saddr)                     | × | ×   | ×  |

|          | A, !addr16     | 3     | 8     | A, CY ← A + (addr16)                    | × | ×   | ×  |

|          | A, [HL]        | 1     | 6     | $A, CY \leftarrow A + (HL)$             | × | ×   | X  |

|          | A, [HL + byte] | 2     | 6     | A, CY ← A + (HL + byte)                 | × | ×   | ×  |

| ADDC     | A, #byte       | 2     | 4     | $A, CY \leftarrow A + byte + CY$        | × | ×   | ×  |

|          | saddr, #byte   | 3     | 6     | (saddr), CY ← (saddr) + byte + CY       | × | ×   | ×  |

|          | A, r           | 2     | 4     | $A, CY \leftarrow A + r + CY$           | × | ×   | ×  |

|          | A, saddr       | 2     | 4     | $A, CY \leftarrow A + (saddr) + CY$     | × | ×   | ×  |

|          | A, !addr16     | 3     | 8     | A, CY ← A + (addr16) + CY               | × | ×   | ×  |

|          | A, [HL]        | 1     | 6     | $A, CY \leftarrow A + (HL) + CY$        | × | ×   | ×  |

|          | A, [HL + byte] | 2     | 6     | $A, CY \leftarrow A + (HL + byte) + CY$ | × | ×   | ×  |

| SUB      | A, #byte       | 2     | 4     | A, CY ← A – byte                        | × | ×   | ×  |

|          | saddr, #byte   | 3     | 6     | (saddr), CY ← (saddr) – byte            | × | ×   | ×  |

|          | A, r           | 2     | 4     | $A, CY \leftarrow A - r$                | × | ×   | ×  |

|          | A, saddr       | 2     | 4     | A, CY ← A − (saddr)                     | × | ×   | ×  |

|          | A, !addr16     | 3     | 8     | A, CY ← A – (addr16)                    | × | ×   | ×  |

|          | A, [HL]        | 1     | 6     | $A, CY \leftarrow A - (HL)$             | × | ×   | ×  |

|          | A, [HL + byte] | 2     | 6     | $A, CY \leftarrow A - (HL + byte)$      | × | ×   | ×  |

| SUBC     | A, #byte       | 2     | 4     | A, CY ← A − byte − CY                   | × | ×   | ×  |

|          | saddr, #byte   | 3     | 6     | (saddr), CY ← (saddr) – byte – CY       | × | ×   | X  |

|          | A, r           | 2     | 4     | $A, CY \leftarrow A - r - CY$           | × | ×   | ×  |

|          | A, saddr       | 2     | 4     | $A, CY \leftarrow A - (saddr) - CY$     | × | ×   | ×  |

|          | A, !addr16     | 3     | 8     | $A, CY \leftarrow A - (addr16) - CY$    | × | ×   | ×  |

|          | A, [HL]        | 1     | 6     | $A, CY \leftarrow A - (HL) - CY$        | × | ×   | ×  |

|          | A, [HL + byte] | 2     | 6     | $A, CY \leftarrow A - (HL + byte) - CY$ | × | ×   | ×  |

| AND      | A, #byte       | 2     | 4     | $A \leftarrow A \wedge byte$            | × |     |    |

|          | saddr, #byte   | 3     | 6     | (saddr) ← (saddr) ∧ byte                | × |     |    |

|          | A, r           | 2     | 4     | $A \leftarrow A \wedge r$               | × |     |    |

|          | A, saddr       | 2     | 4     | $A \leftarrow A \wedge (saddr)$         | × |     |    |

|          | A, !addr16     | 3     | 8     | $A \leftarrow A \wedge (addr16)$        | × |     |    |

|          | A, [HL]        | 1     | 6     | $A \leftarrow A \wedge (HL)$            | × |     |    |

|          | A, [HL + byte] | 2     | 6     | $A \leftarrow A \wedge (HL + byte)$     | × |     |    |

**Note** Only when rp = BC, DE, or HL.

**Remark** The instruction clock cycle is based on the CPU clock (fcpu), specified in the processor clock control register (PCC).

| Mnemonic  | Operand        | Buto | Clock | Operation                                                                 | Flag   |

|-----------|----------------|------|-------|---------------------------------------------------------------------------|--------|

| winemonic | Operand        | Byte | Clock | Operation                                                                 | Z AC C |

| OR        | A, #byte       | 2    | 4     | $A \leftarrow A \lor byte$                                                | ×      |

|           | saddr, #byte   | 3    | 6     | $(saddr) \leftarrow (saddr) \lor byte$                                    | ×      |

|           | A, r           | 2    | 4     | $A \leftarrow A \lor r$                                                   | ×      |

|           | A, saddr       | 2    | 4     | $A \leftarrow A \lor (saddr)$                                             | ×      |

|           | A, !addr16     | 3    | 8     | $A \leftarrow A \lor (addr16)$                                            | ×      |

|           | A, [HL]        | 1    | 6     | $A \leftarrow A \lor (HL)$                                                | ×      |

|           | A, [HL + byte] | 2    | 6     | $A \leftarrow A \lor (HL + byte)$                                         | ×      |

| XOR       | A, #byte       | 2    | 4     | $A \leftarrow A \forall$ byte                                             | ×      |

|           | saddr, #byte   | 3    | 6     | (saddr) ← (saddr) <del>∨</del> byte                                       | ×      |

|           | A, r           | 2    | 4     | $A \leftarrow A \forall r$                                                | ×      |

|           | A, saddr       | 2    | 4     | $A \leftarrow A \forall$ (saddr)                                          | ×      |

|           | A, !addr16     | 3    | 8     | A ← A <del>∨</del> (addr16)                                               | ×      |

|           | A, [HL]        | 1    | 6     | $A \leftarrow A \leftrightarrow (HL)$                                     | ×      |

|           | A, [HL + byte] | 2    | 6     | $A \leftarrow A \forall (HL + byte)$                                      | ×      |

| CMP       | A, #byte       | 2    | 4     | A – byte                                                                  | × × ×  |

|           | saddr, #byte   | 3    | 6     | (saddr) - byte                                                            | × × ×  |

|           | A, r           | 2    | 4     | A – r                                                                     | × × ×  |

|           | A, saddr       | 2    | 4     | A – (saddr)                                                               | × × ×  |

|           | A, !addr16     | 3    | 8     | A – (addr16)                                                              | × × ×  |

|           | A, [HL]        | 1    | 6     | A – (HL)                                                                  | × × ×  |

|           | A, [HL + byte] | 2    | 6     | A – (HL + byte)                                                           | × × ×  |

| ADDW      | AX, #word      | 3    | 6     | $AX, CY \leftarrow AX + word$                                             | × × ×  |

| SUBW      | AX, #word      | 3    | 6     | $AX, CY \leftarrow AX - word$                                             | × × ×  |

| CMPW      | AX, #word      | 3    | 6     | AX – word                                                                 | × × ×  |

| INC       | r              | 2    | 4     | r ← r + 1                                                                 | × ×    |

|           | saddr          | 2    | 4     | (saddr) ← (saddr) + 1                                                     | × ×    |

| DEC       | r              | 2    | 4     | r ← r − 1                                                                 | × ×    |

|           | saddr          | 2    | 4     | (saddr) ← (saddr) – 1                                                     | × ×    |

| INCW      | rp             | 1    | 4     | rp ← rp + 1                                                               |        |

| DECW      | rp             | 1    | 4     | $rp \leftarrow rp - 1$                                                    |        |

| ROR       | A, 1           | 1    | 2     | $(CY,A_7 \leftarrow A_0,A_{m-1} \leftarrow A_m) \times 1$                 | ×      |

| ROL       | A, 1           | 1    | 2     | $(CY,A_0 \leftarrow A_7,A_{m+1} \leftarrow A_m) \times 1$                 | ×      |

| RORC      | A, 1           | 1    | 2     | $(CY \leftarrow A_0, A_7 \leftarrow CY, A_{m-1} \leftarrow A_m) \times 1$ | ×      |

| ROLC      | A, 1           | 1    | 2     | $(CY \leftarrow A_7, A_0 \leftarrow CY, A_{m+1} \leftarrow A_m) \times 1$ | ×      |

**Remark** The instruction clock cycle is based on the CPU clock (fcPu), specified in the processor clock control register (PCC).

| Maranasia | On a second | D. t. | Olevelo | On continu                                                                                                                                                                      |   | Flag | J  |

|-----------|-------------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----|

| Mnemonic  | Operand     | Byte  | Clock   | Operation                                                                                                                                                                       | Z | AC   | CY |

| SET1      | saddr. bit  | 3     | 6       | (saddr. bit) ← 1                                                                                                                                                                |   |      |    |

|           | sfr. bit    | 3     | 6       | sfr. bit ← 1                                                                                                                                                                    |   |      |    |

|           | A. bit      | 2     | 4       | A. bit ← 1                                                                                                                                                                      |   |      |    |

|           | PSW. bit    | 3     | 6       | PSW. bit ← 1                                                                                                                                                                    | × | ×    | ×  |

|           | [HL]. bit   | 2     | 10      | (HL). bit ← 1                                                                                                                                                                   |   |      |    |

| CLR1      | saddr. bit  | 3     | 6       | (saddr. bit) ← 0                                                                                                                                                                |   |      |    |

|           | sfr. bit    | 3     | 6       | sfr. bit ← 0                                                                                                                                                                    |   |      |    |

|           | A. bit      | 2     | 4       | A. bit ← 0                                                                                                                                                                      |   |      |    |

|           | PSW. bit    | 3     | 6       | PSW. bit ← 0                                                                                                                                                                    | × | ×    | ×  |

|           | [HL]. bit   | 2     | 10      | (HL). bit ← 0                                                                                                                                                                   |   |      |    |

| SET1      | CY          | 1     | 2       | CY ← 1                                                                                                                                                                          |   |      | 1  |

| CLR1      | CY          | 1     | 2       | CY ← 0                                                                                                                                                                          |   |      | 0  |

| NOT1      | CY          | 1     | 2       | $CY \leftarrow \overline{CY}$                                                                                                                                                   |   |      | ×  |

| CALL      | !addr16     | 3     | 6       | $(SP-1) \leftarrow (PC+3)H, (SP-2) \leftarrow (PC+3)L,$<br>PC $\leftarrow$ addr16, SP $\leftarrow$ SP - 2                                                                       |   |      |    |

| CALLT     | [addr5]     | 1     | 8       | $(SP - 1) \leftarrow (PC + 1)_H, (SP - 2) \leftarrow (PC + 1)_L,$<br>$PC_H \leftarrow (00000000, addr5 + 1),$<br>$PC_L \leftarrow (00000000, addr5),$<br>$SP \leftarrow SP - 2$ |   |      |    |

| RET       |             | 1     | 6       | $PC_H \leftarrow (SP + 1), PC_L \leftarrow (SP),$<br>$SP \leftarrow SP + 2$                                                                                                     |   |      |    |

| RETI      |             | 1     | 8       | $\begin{aligned} & PCH \leftarrow (SP+1), PCL \leftarrow (SP), \\ & PSW \leftarrow (SP+2), SP \leftarrow SP+3, \\ & NMIS \leftarrow 0 \end{aligned}$                            | R | R    | R  |

| PUSH      | PSW         | 1     | 2       | (SP − 1) ← PSW, SP ← SP − 1                                                                                                                                                     |   |      |    |

|           | rp          | 1     | 4       | $(SP-1) \leftarrow rp_H, (SP-2) \leftarrow rp_L,$<br>$SP \leftarrow SP-2$                                                                                                       |   |      |    |

| POP       | PSW         | 1     | 4       | $PSW \leftarrow (SP),SP \leftarrow SP + 1$                                                                                                                                      | R | R    | R  |

|           | гр          | 1     | 6       | $rp_{H} \leftarrow (SP + 1), rp_{L} \leftarrow (SP),$<br>$SP \leftarrow SP + 2$                                                                                                 |   |      |    |

| MOVW      | SP, AX      | 2     | 8       | SP ← AX                                                                                                                                                                         |   |      |    |

|           | AX, SP      | 2     | 6       | AX ← SP                                                                                                                                                                         |   |      |    |

| BR        | !addr16     | 3     | 6       | PC ← addr16                                                                                                                                                                     |   |      |    |

|           | \$addr16    | 2     | 6       | PC ← PC + 2 + jdisp8                                                                                                                                                            |   |      |    |

|           | AX          | 1     | 6       | $PC_H \leftarrow A, PC_L \leftarrow X$                                                                                                                                          |   |      |    |

**Remark** The instruction clock cycle is based on the CPU clock (fcpu), specified in the processor clock control register (PCC).

| Managania | Onemand              | Dista                                                       | Clask | On a wati a w                                                                 |   | Flag |    |

|-----------|----------------------|-------------------------------------------------------------|-------|-------------------------------------------------------------------------------|---|------|----|

| Mnemonic  | Operand              | Byte                                                        | Clock | Operation                                                                     | Z | AC   | CY |

| ВС        | \$addr16             | 2                                                           | 6     | PC ← PC + 2 + jdisp8 if CY = 1                                                |   |      |    |

| BNC       | \$addr16             | 2                                                           | 6     | $PC \leftarrow PC + 2 + jdisp8 \text{ if } CY = 0$                            |   |      |    |

| BZ        | \$addr16             | 2                                                           | 6     | PC ← PC + 2 + jdisp8 if Z = 1                                                 |   |      |    |

| BNZ       | \$addr16             | 2                                                           | 6     | $PC \leftarrow PC + 2 + jdisp8 \text{ if } Z = 0$                             |   |      |    |

| ВТ        | saddr. bit, \$addr16 | 4 10 $PC \leftarrow PC + 4 + jdisp8$<br>if (saddr. bit) = 1 |       |                                                                               |   |      |    |

|           | sfr. bit, \$addr16   | 4                                                           | 10    | PC ← PC + 4 + jdisp8 if sfr. bit = 1                                          |   |      |    |

|           | A. bit, \$addr16     | 3                                                           | 8     | $PC \leftarrow PC + 3 + jdisp8 \text{ if A. bit} = 1$                         |   |      |    |

|           | PSW. bit, \$addr16   | 4                                                           | 10    | PC ← PC + 4 + jdisp8 if PSW. bit = 1                                          |   |      |    |

| BF        | saddr. bit, \$addr16 | 4                                                           | 10    | $PC \leftarrow PC + 4 + jdisp8$<br>if (saddr. bit) = 0                        |   |      |    |

|           | sfr. bit, \$addr16   | 4                                                           | 10    | PC ← PC + 4 + jdisp8 if sfr. bit = 0                                          |   |      |    |

|           | A. bit, \$addr16     | 3                                                           | 8     | $PC \leftarrow PC + 3 + jdisp8 \text{ if A. bit} = 0$                         |   |      |    |

|           | PSW. bit, \$addr16   | 4                                                           | 10    | PC ← PC + 4 + jdisp8 if PSW. bit = 0                                          |   |      |    |

| DBNZ      | B, \$addr16          | 2                                                           | 6     | $B \leftarrow B - 1$ , then<br>PC $\leftarrow$ PC + 2 + jdisp8 if B $\neq$ 0  |   |      |    |

|           | C, \$addr16          | 2                                                           | 6     | $C \leftarrow C - 1$ , then<br>$PC \leftarrow PC + 2 + jdisp8$ if $C \neq 0$  |   |      |    |

|           | saddr, \$addr16      | 3                                                           | 8     | (saddr) ← (saddr) – 1, then<br>$PC \leftarrow PC + 3 + jdisp8$ if (saddr) ≠ 0 |   |      |    |

| NOP       |                      | 1                                                           | 2     | No Operation                                                                  |   |      |    |

| El        |                      | 3                                                           | 6     | IE ← 1 (Enable Interrupt)                                                     |   |      |    |

| DI        |                      | 3                                                           | 6     | IE ← 0 (Disable Interrupt)                                                    |   |      |    |

| HALT      |                      | 1                                                           | 2     | Set HALT Mode                                                                 |   |      |    |

| STOP      |                      | 1                                                           | 2     | Set STOP Mode                                                                 |   |      |    |

**Remark** The instruction clock cycle is based on the CPU clock (fcpu), specified in the processor clock control register (PCC).

#### 8. ELECTRICAL CHARACTERISTICS

#### ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)

| Parameter                     | Symbol           | Conditions              |                  | Rated Value                                   | Unit |

|-------------------------------|------------------|-------------------------|------------------|-----------------------------------------------|------|

| Supply voltage                | V <sub>DD</sub>  |                         |                  | -0.3 to +6.5                                  | V    |

|                               | V <sub>PP</sub>  |                         |                  | -0.3 to +10.5                                 | ٧    |

| Input voltage                 | VII              | Pins other than P24     |                  | -0.3 to V <sub>DD</sub> + 0.3 <sup>Note</sup> | V    |

|                               | V <sub>I2</sub>  | P24                     | N-ch open drain  | -0.3 to +13                                   | ٧    |

| Output voltage                | Vo               |                         |                  | -0.3 to V <sub>DD</sub> + 0.3 <sup>Note</sup> | ٧    |

| High-level output current     | Іон              | Each pin                |                  | -10                                           | mA   |

|                               |                  | Total for all pins      |                  | -30                                           | mA   |

| Low-level output current      | Іоь              | Each pin                |                  | 30                                            | mA   |

|                               |                  | Total for all pins      |                  | 160                                           | mA   |

| Operating ambient temperature | TA               | During normal operation |                  | -20 to +60                                    | °C   |

|                               |                  | During flash mer        | nory programming | 10 to 40                                      | °C   |

| Storage temperature           | T <sub>stg</sub> |                         |                  | -40 to +125                                   | °C   |

Note 6.5 V or less

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter.

That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

**Remark** The characteristic of a dual-function pin does not differ between the port function and the secondary function, unless otherwise stated.

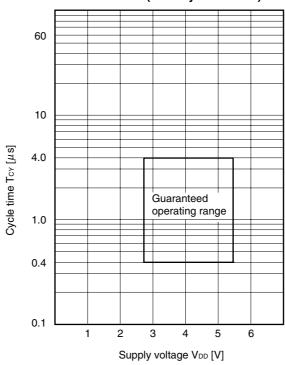

## CHARACTERISTICS OF THE MAIN SYSTEM CLOCK OSCILLATION CIRCUIT ( $T_A = -20$ to +60 °C, $V_{DD} = 2.7$ to 5.5 V)

|   | Resonator         | Recommended Circuit | Parameter                                   | Conditions                                                                     | MIN. | TYP. | MAX. | Unit |

|---|-------------------|---------------------|---------------------------------------------|--------------------------------------------------------------------------------|------|------|------|------|

|   | Ceramic resonator | ICO X1 X2           | Oscillator frequency (fx) <sup>Note 1</sup> |                                                                                | 2.0  |      | 5.0  | MHz  |

|   |                   | C1 = C2 =           | Oscillation settling time <sup>Note 2</sup> | Time after V <sub>DD</sub> reaches<br>MIN. of the oscillation<br>voltage range |      |      | 4    | ms   |

|   | Crystal IC0 X1 X2 |                     | Oscillator frequency (fx) <sup>Note 1</sup> |                                                                                | 2.0  |      | 5.0  | MHz  |

|   |                   | C1= C2=             | Oscillation settling time <sup>Note 2</sup> | V <sub>DD</sub> = 4.5 to 5.5 V                                                 |      |      | 10   | ms   |

|   |                   | ' <del></del>       |                                             |                                                                                |      |      | 30   | ms   |

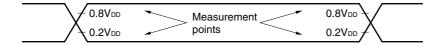

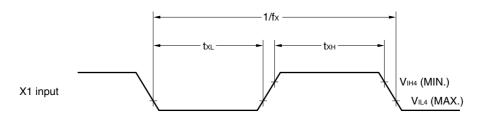

| + | External clock    | X1 X2               | X1 input frequency (fx) <sup>Note 1</sup>   |                                                                                | 2.0  |      | 5.0  | MHz  |

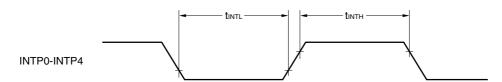

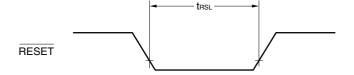

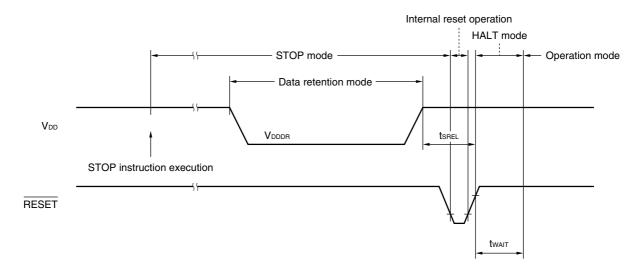

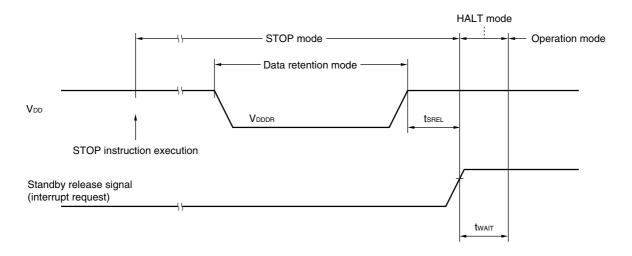

|   | OPEN              |                     | X1 input high/low level width (txH, txL)    |                                                                                | 85   |      | 250  | ns   |