UCC1895 UCC2895 UCC3895

# BiCMOS Advanced Phase Shift PWM Controller

#### **FEATURES**

- Programmable Output Turn-on Delay

- · Adaptive Delay Set

- Bidirectional Oscillator Synchronization

- Capability for Voltage Mode or Current Mode Control

- Programmable Soft Start/Soft Stop and Chip Disable via a Single Pin

- 0% to 100% Duty Cycle Control

- 7MHz Error Amplifier

- Operation to 1MHz

- Low Active Current Consumption (5mA Typical @ 500kHz)

- Very Low Current Consumption During Undervoltage Lock-out (150μA typical)

#### **DESCRIPTION**

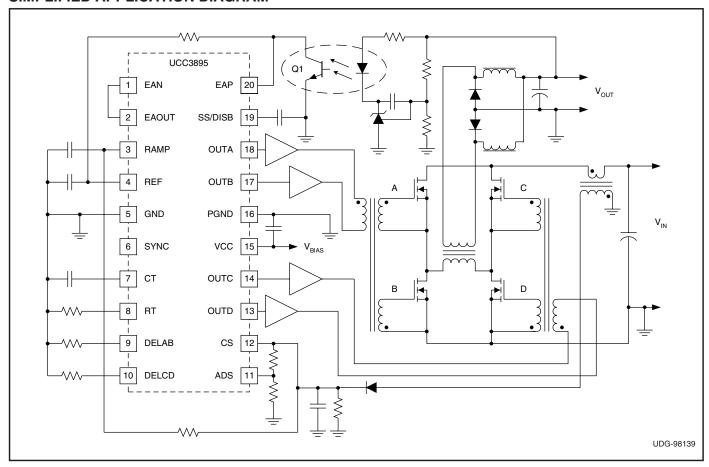

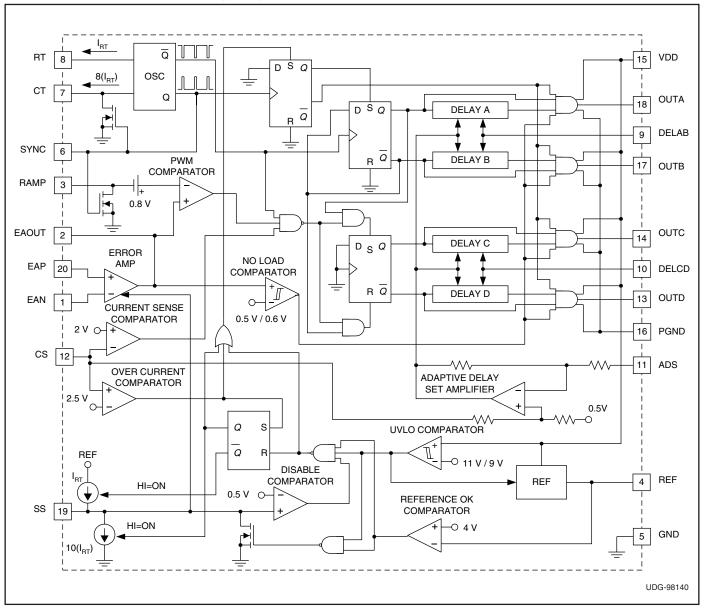

The UCC3895 is a phase shift PWM controller that implements control of a full-bridge power stage by phase shifting the switching of one half-bridge with respect to the other. It allows constant frequency pulse-width modulation in conjunction with resonant zero-voltage switching to provide high efficiency at high frequencies. The part can be used either as a voltage mode or current mode controller.

While the UCC3895 maintains the functionality of the UC3875/6/7/8 family and UC3879, it improves on that controller family with additional features such as enhanced control logic, adaptive delay set, and shutdown capability. Since it is built in BCDMOS, it operates with dramatically less supply current than it's bipolar counterparts. The UCC3895 can operate with a maximum clock frequency of 1MHz.

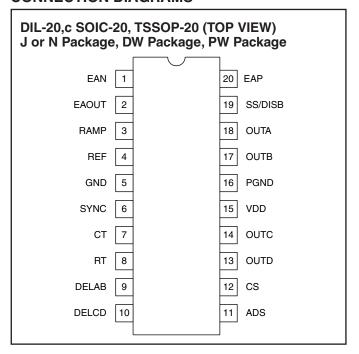

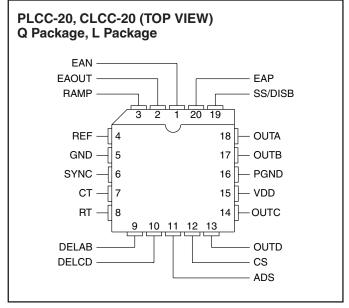

The UCC3895 and UCC2895 are offered in the 20 pin SOIC (DW) package, 20 pin PDIP (N) package, 20 pin TSSOP (PW) package, and 20 pin PLCC (Q). The UCC1895 is offered in the 20 pin CDIP (J) package, and 20 pin CLCC package (L).

#### SIMPLIFIED APPLICATION DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

Currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of package.

# TEMPERATURE & PACKAGE SELECTION TABLE

|         | TEMPERATURE<br>RANGE | PACKAGE<br>SUFFIX |

|---------|----------------------|-------------------|

| UCC1895 | −55°C to +125°C      | J, L              |

| UCC2895 | -40°C to +85°C       | DW, N, PW, Q      |

| UCC3895 | 0°C to +70°C         | DW, N, PW, Q      |

#### **ORDERING INFORMATION**

#### **CONNECTION DIAGRAMS**

**ELECTRICAL CHARACTERISTICS:** Unless otherwise specified, VDD=12V, RT=82kΩ, CT=220pF, RDELAB=10kΩ, RDELCD=10kΩ,  $C_{REF}$ =0.1μF,  $C_{VDD}$ =1.0μF, no load at outputs.  $T_A$  =  $T_J$ .  $T_A$  =  $0^{\circ}$ C to  $70^{\circ}$ C for UCC3895x,  $-40^{\circ}$ C to  $+85^{\circ}$ C for UCC2895x, and  $-55^{\circ}$ C to  $+125^{\circ}$ C for UCC1895x.

| PARAMETER              | TEST CONI  | DITIONS | TYP  | MAX  | UNITS |

|------------------------|------------|---------|------|------|-------|

| UVLO Section           |            |         |      |      |       |

| Start Threshold        |            | 10.2    | 11   | 11.8 | V     |

| Stop Threshold         |            | 8.2     | 9    | 9.8  | V     |

| Hysteresis             |            | 1.0     | 2.0  | 3.0  | V     |

| Supply Current         |            |         |      |      |       |

| Start-up Current       | VDD = 8V   |         | 150  | 250  | μΑ    |

| I <sub>DD</sub> Active |            |         | 5    | 6    | mA    |

| VDD Clamp Voltage      | IDD = 10mA | 16.5    | 17.5 | 18.5 | V     |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise specified, VDD=12V, RT=82kΩ, CT=220pF, RDELAB=10kΩ, RDELCD=10kΩ,  $C_{REF}=0.1\mu F$ ,  $C_{VDD}=1.0\mu F$ , no load at outputs.  $C_{A}=C_{A}$  = 0°C to 70°C for UCC3895x,  $C_{A}=0.0$ 0°C to  $C_{A}=0.0$ 0°C for UCC3895x,  $C_{A}=0.0$ 0°C for UCC1895x.

| PARAMETER                                           | TEST CONDITIONS                                                      | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------------------|----------------------------------------------------------------------|-------|-------|-------|-------|

| Voltage Reference Section                           |                                                                      |       |       |       |       |

| Output Voltage                                      | $T_J = 25^{\circ}C$                                                  | 4.94  | 5.00  | 5.06  | V     |

|                                                     | 10V < VDD < 17.5V, 0mA < IREF < 5mA, Temperature                     | 4.85  | 5     | 5.15  | V     |

| Short Circuit Current                               | REF = 0V, T <sub>J</sub> = 25°C                                      | 10    | 20    |       | mA    |

| Error Amplifier Section                             |                                                                      | •     |       |       |       |

| Common Mode Input Voltage Range                     |                                                                      | -0.1  |       | 3.6   | V     |

| Offset Voltage                                      |                                                                      | -7    |       | 7     | mV    |

| Input Bias Current (EAP, EAN)                       |                                                                      | -1    |       | 1     | μΑ    |

| EAOUT VOH                                           | EAP-EAN = 500mV, I <sub>EAOUT</sub> = -0.5mA                         | 4.0   | 4.5   | 5.0   | V     |

| EAOUT VOL                                           | $EAP-EAN = -500mV$ , $I_{EAOUT} = 0.5mA$                             | 0     | 0.2   | 0.4   | V     |

| EAOUT Source Current                                | EAP-EAN = 500mV, EAOUT= 2.5V                                         | 1.0   | 1.5   |       | mA    |

| EAOUT Sink Current                                  | EAP-EAN = -500mV, EAOUT= 2.5V, (Note 4)                              | 2.5   | 4.5   |       | mA    |

| Open Loop DC Gain                                   |                                                                      | 75    | 85    |       | dB    |

| Unity Gain Bandwidth                                | (Note 3)                                                             | 5.0   | 7.0   |       | MHz   |

| Slew Rate                                           | EAN from 1V to 0V, EAP = 500mV,<br>EAOUT from 0.5V to 3.0V, (Note 3) | 1.5   | 2.2   |       | V/μs  |

| No Load Comparator Turn-Off Threshold               |                                                                      | 0.45  | 0.50  | 0.55  | V     |

| No Load Comparator Turn-On Threshold                |                                                                      | 0.55  | 0.60  | 0.69  | V     |

| No Load Comparator Hysteresis                       |                                                                      | 0.035 | 0.100 | 0.165 | V     |

| Oscillator Section                                  |                                                                      | •     |       |       |       |

| Frequency                                           | T <sub>J</sub> = 25°C                                                | 473   | 500   | 527   | kHz   |

| Total Variation                                     | Line, Temperature (Note 3)                                           |       | 2.5   | 5     | %     |

| SYNC VIH                                            |                                                                      | 2.05  | 2.10  | 2.25  | V     |

| SYNC VIL                                            |                                                                      | 1.85  | 1.90  | 1.95  | V     |

| SYNC VOH                                            | I <sub>SYNC</sub> = -400μA, CT = 2.6V                                | 4.1   | 4.5   | 5.0   | V     |

| SYNC VOL                                            | I <sub>SYNC</sub> = 100μA, CT = 0V                                   | 0.0   | 0.5   | 1.0   | V     |

| SYNC Output Pulse Width                             | SYNC Load = $3.9k\Omega$ and $30pF$ in parallel                      |       | 85    | 135   | ns    |

| RT Voltage                                          |                                                                      | 2.9   | 3     | 3.1   | V     |

| CT Peak Voltage                                     |                                                                      | 2.25  | 2.35  | 2.50  | V     |

| CT Valley Voltage                                   | UCC2895, UCC3895                                                     | 0.0   | 0.2   | 0.4   | V     |

| CT Valley Voltage                                   | UCC1895                                                              | 0.0   | 0.2   | 0.6   | V     |

| PWM Comparator Section                              |                                                                      | •     |       | •     |       |

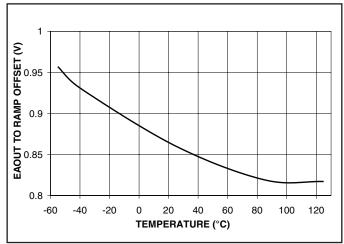

| EAOUT to RAMP Input Offset Voltage                  | RAMP = 0V, DELAB = DELCD = REF                                       | 0.72  | 0.85  | 1.05  | V     |

| Minimum Phase Shift<br>(OUTA to OUTC, OUTB to OUTD) | RAMP = 0V, EAOUT = 650mV (Note 1)                                    | 0.00  | 0.85  | 1.40  | %     |

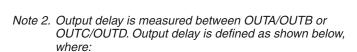

| RAMP to OUTC/OUTD Delay                             | RAMP from 0V to 2.5V, EAOUT = 1.2V,<br>DELAB = DELCD = REF (Note 2)  |       | 70    | 120   | ns    |

| RAMP Bias Current                                   | RAMP < 5V, CT < 2.2V                                                 | -5    |       | 5     | μΑ    |

| RAMP Sink Current                                   | RAMP = 5V, CT < 2.6V                                                 | 12    | 19    |       | mA    |

| Current Sense Section                               |                                                                      |       |       | •     | •     |

| CS Bias Current                                     | 0 < CS , 2.5V, 0 < ADS < 2.5V                                        | -4.5  |       | 20    | μА    |

| Peak Current Threshold                              |                                                                      | 1.90  | 2.00  | 2.10  | V     |

| Overcurrent Threshold                               |                                                                      | 2.4   | 2.5   | 2.6   | V     |

| CS to Output Delay                                  | CS from 0 to 2.3V, DELAB = DELCD = REF                               |       | 75    | 110   | ns    |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise specified, VDD=12V, RT=82kΩ, CT=220pF, RDELAB=10kΩ, RDELCD=10kΩ,  $C_{REF}=0.1\mu F$ ,  $C_{VDD}=1.0\mu F$ , no load at outputs.  $T_A=T_J$ .  $T_A=0$ °C to 70°C for UCC3895x, -40°C to +85°C for UCC2895x, and -55°C to +125°C for UCC1895x.

| PARAMETER                               | TEST CONDITIONS                     | MIN  | TYP  | MAX  | UNITS |  |

|-----------------------------------------|-------------------------------------|------|------|------|-------|--|

| Soft Start/Shutdown Section             |                                     |      |      |      |       |  |

| Soft Start Source Current               | SS/DISB = 3.0V, CS < 1.9V           | -40  | -35  | -30  | μΑ    |  |

| Soft Start Sink Current                 | SS/DISB = 3.0V, CS > 2.6V           | 325  | 350  | 375  | μΑ    |  |

| Soft Start/Disable Comparator Threshold |                                     | 0.44 | 0.50 | 0.56 | V     |  |

| Delay Set Section                       | Delay Set Section                   |      |      |      |       |  |

| DELAB/DELCD Output Voltage              | ADS = CS = 0V                       | 0.45 | 0.50 | 0.55 | V     |  |

|                                         | ADS = 0V, CS = 2.0V                 | 1.9  | 2.0  | 2.1  | V     |  |

| Output Delay                            | ADS = CS = 0V (Notes 2 and 3)       | 450  | 525  | 600  | ns    |  |

| ADS Bias Current                        | 0V < ADS < 2.5V, 0V < CS < 2.5V     | -20  |      | 20   | μΑ    |  |

| Output Section                          |                                     | _    |      |      | _     |  |

| VOH (all outputs)                       | IOUT = −10mA, VDD to Output         |      | 250  | 400  | mV    |  |

| VOL (all outputs)                       | IOUT = 10mA                         |      | 150  | 250  | mV    |  |

| Rise Time                               | C <sub>LOAD</sub> = 100pF, (Note 3) |      | 20   | 35   | ns    |  |

| Fall Time                               | C <sub>LOAD</sub> = 100pF, (Note 3) |      | 20   | 35   | ns    |  |

Note 1: Minimum phase shift is defined as followed:

$$\Phi = 200 \bullet \frac{t_{f(OUTA)} - t_{f(OUTC)}}{t_{PERIOD}} \ Or$$

$$\Phi = 200 \bullet \frac{t_{f(OUTB)} - t_{f(OUTD)}}{t_{PERIOD}} \quad \textit{where}$$

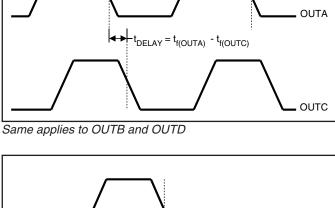

$t_{f(OUTA)}$  = falling edge of OUTA signal  $t_{f(OUTB)}$  = falling edge of OUTB signal  $t_{f(OUTC)}$  = falling edge of OUTC signal  $t_{f(OUTD)}$  = falling edge of OUTD signal  $t_{f(PERIOD)}$  = period of OUTA or OUTB signal

$t_{f(OUTA)}$  = falling edge of OUTA signal  $t_{r(OUTB)}$  = rising edge of OUTB signal

#### Note 3: Ensured by design. Not 100% tested in production. Note 4: For UCC1895, MIN limit is 2.2 mA at -55°C

t<sub>PERIOD</sub>

Same applies to OUTC and OUTD

#### PIN DESCRIPTIONS

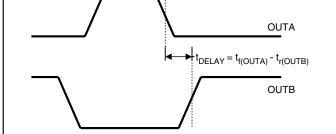

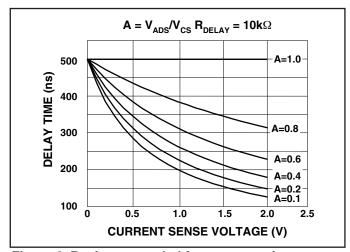

**ADS:** Adaptive Delay Set. This function sets the ratio between the maximum and minimum programmed output delay dead time. When the ADS pin is directly connected to the CS pin, no delay modulation occurs. The maximum delay modulation occurs when ADS is grounded. In this case, delay time is four times longer when CS = 0 than when CS = 2.0V (the Peak Current threshold), ADS changes the output voltage on the delay pins DELAB and DELCD by the following formula:

$$V_{DEL} = [0.75 \bullet (V_{CS} - V_{ADS})] + 0.5V$$

where  $V_{CS}$  and  $V_{ADS}$  are in Volts. ADS must be limited to between 0V and 2.5V and must be less than or equal to CS. DELAB and DELCD also will be clamped to a minimum of 0.5V.

**EAOUT:** Error Amplifier Output. It is also connected internally to the non-inverting input of the PWM comparator and the no-load comparator. EAOUT is internally clamped to the soft start voltage. The no-load comparator shuts down the output stages when EAOUT falls below 500mV, and allows the outputs to turn-on again when EAOUT rises above 600mV.

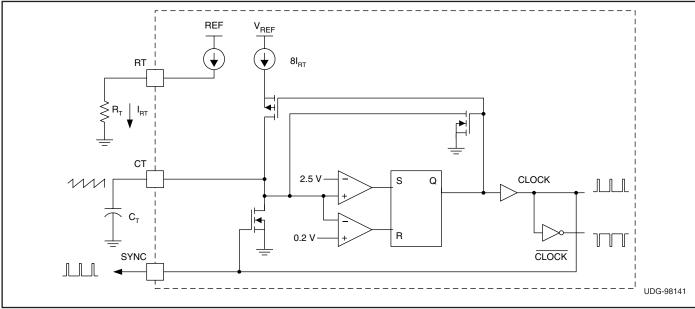

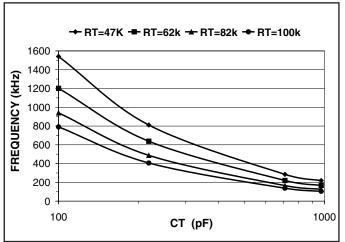

**CT:** Oscillator Timing Capacitor. (Refer to Fig. 1, Oscillator Block Diagram) The UCC3895's oscillator charges CT via a programmed current. The waveform on  $C_T$  is a sawtooth, with a peak voltage of 2.35V. The approximate oscillator period is calculated by the following formula:

$$t_{OSC} = \frac{5 \bullet R_T \bullet C_T}{48} + 120 \, ns$$

where  $C_T$  is in Farads, and  $R_T$  is in Ohms and  $t_{OSC}$  is in seconds.  $C_T$  can range from 100pF to 880pF. Please note that a large  $C_T$  and a small  $R_T$  combination will result in extended fall times on the  $C_T$  waveform. The increased fall time will increase the SYNC pulse width, hence limiting the maximum phase shift between OUTA, OUTB and OUTC, OUTD outputs, which limits the maximum duty cycle of the converter.

**CS:** Current Sense. This is the inverting input of the Current Sense comparator and the non-inverting input of the Over-current comparator, and the ADS amplifier. The current sense signal is used for cycle-by-cycle current limiting in peak current mode control, and for overcurrent protection in all cases with a secondary threshold for output shutdown. An output disable initiated by an overcurrent fault also results in a restart cycle, called "soft stop", with full soft start.

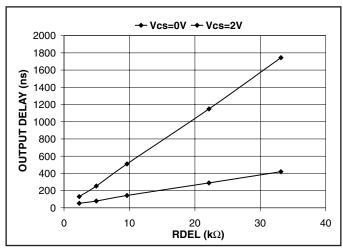

**DELAB, DELCD:** Delay Programming Between Complementary Outputs. DELAB programs the dead time between switching of OUTA and OUTB, and DELCD programs the dead time between OUTC and OUTD. This delay is introduced between complementary outputs in the same leg of the external bridge. The UCC3895 allows the user to select the delay, in which the resonant switching of the external power stages takes place. Separate delays are provided for the two half-bridges to accommodate differences in resonant capacitor charging currents. The delay in each stage is set according to the following formula:

$$t_{DELAY} = \frac{(25 \cdot 10^{-12}) \cdot R_{DEL}}{V_{DEL}} + 25 \, ns$$

where  $V_{DEL}$  is in Volts, and  $R_{DEL}$  is in Ohms and  $t_{DELAY}$  is in seconds. DELAB and DELCD can source about 1mA maximum. Choose the delay resistors so that this maximum is not exceeded. Programmable output delay can be defeated by tying DELAB and/or DELCD to REF. For an optimum performance keep stray capacitance on these pins at <10pF.

**EAP:** The non-inverting input to the error amplifier.

**EAN:** The inverting input to the error amplifier.

**GND:** Chip ground for all circuits except the output stages.

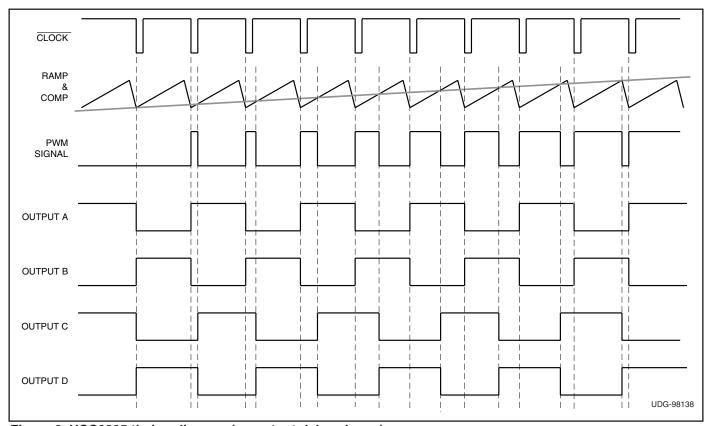

OUTA, OUTB, OUTC, OUTD: The 4 outputs are 100mA complementary MOS drivers, and are optimized to drive FET driver circuits. OUTA and OUTB are fully complementary, (assuming no programmed delay). They operate near 50% duty cycle and one-half the oscillating frequency. OUTA and OUTB are intended to drive one half-bridge circuit in an external power stage. OUTC and OUTD will drive the other half-bridge and will have the same characteristics as OUTA and OUTB. OUTC is phase shifted with respect to OUTA, and OUTD is phase shifted with respect to OUTB. Note that changing the phase relationship of OUTC and OUTD with respect to OUTA and OUTB requires other than the nominal 50% duty ratio on OUTC and OUTD during those transients.

**PGND:** Output Stage Ground. To keep output switching noise from critical analog circuits, the UCC3895 has 2 different ground connections. PGND is the ground connection for the high-current output stages. Both GND and PGND must be electrically tied together closely near the IC. Also, since PGND carries high current, board traces must be low impedance.

# PIN DESCRIPTIONS (cont.)

**RAMP:** The Inverting Input of the PWM Comparator. This pin receives either the CT waveform in voltage and average current mode controls, or the current signal (plus slope compensation) in peak current mode control. An internal discharge transistor is provided on RAMP, which is triggered during the oscillator dead time.

**RT:** Oscillator Timing Resistor. (Refer to Fig. 1, Oscillator Block Diagram) The oscillator in the UCC3895 operates by charging an external timing capacitor, CT, with a fixed current programmed by  $R_{T.}$   $R_{T}$  current is calculated as follows:

$$I_{RT} = \frac{3.0 \, V}{R_T}$$

where  $R_T$  is in Ohms and  $I_{RT}$  is in Amperes.  $R_T$  can range from  $40k\Omega$  to  $120k\Omega$  Soft start charging and discharging current are also programmed by  $I_{RT}$ .

**SS/DISB:** Soft Start/Disable. This pin combines the two independent functions.

Disable Mode: A rapid shutdown of the chip is accomplished by any one of the following: externally forcing SS/DISB below 0.5V, externally forcing REF below 4V,  $V_{DD}$  dropping below the UNLO threshold, or an overcurrent fault is sensed (CS = 2.5V).

In the case of REF being pulled below 4V or an UVLO condition, SS/DISB is actively pulled to ground via an internal MOSFET switch. If an overcurrent is sensed, SS/DISB will sink a current of (10 • I<sub>RT</sub>) until SS/DISB falls below 0.5V.

Note that if SS/DISB is externally forced below 0.5V the pin will start to source current equal to  $I_{RT}$ . Also note that the only time the part switches into the low IDD current mode is when the part is in undervoltage lockout.

Soft Start Mode: After a fault or disable condition has passed, VDD is above the start threshold, and/or SS/DISB falls below 0.5V during a soft stop, SS/DISB will switch to a soft start mode. The pin will now source current, equal to I<sub>RT</sub>. A user-selected capacitor on SS/DISB determines the soft start (and soft-start) time. In addition, a resistor in parallel with the capacitor may be used, limiting the maximum voltage on SS/DISB. Note that SS/DISB will actively clamp the EAOUT pin voltage to approximately the SS/DISB pin voltage during both soft start, soft stop, and disable conditions.

SYNC: Oscillator Synchronization. (Refer to Fig. 1, Oscillator Block Diagram) This pin is bidirectional. When used as an output, SYNC can be used as a clock, which is the same as the chip's internal clock. When used as an input, SYNC will override the chip's internal oscillator and act as it's clock signal. This bidirectional feature allows synchronization of multiple power supplies. The SYNC signal will also internally discharge the CT capacitor and any filter capacitors that are present on the RAMP pin. The internal SYNC circuitry is level sensitive, with an input low threshold of 1.9V, and an input high threshold of 2.1V. A resistor as small as  $3.9 \mathrm{k}\Omega$  may be tied between SYNC and GND to reduce the sync pulse width.

**VDD:** Power Supply. VDD must be bypassed with a minimum of a  $1.0\mu F$  low ESR, low ESL capacitor to ground.

**REF:** 5V,  $\pm 1.2\%$  voltage reference. The reference supplies power to internal circuitry, and can also supply up to 5mA to external loads. The reference is shut down during undervoltage lock-out but is operational during all other disable modes. For best performance, bypass with a  $0.1\mu F$  low ESR, low ESL capacitor to ground.

# **APPLICATION INFORMATION**

## Programming DELAB, DELCD, and the Adaptive Delay Set

The UCC3895 allows the user to set the delay between switch commands within each leg of the full bridge power circuit according to the following formula from the data sheet:

$$t_{DELAY} = \frac{(25 \bullet 10^{-12}) \bullet R_{DEL}}{V_{DEL}} + 25n \sec t$$

For this equation  $V_{DEL}$  is determined in conjunction with the desire to utilize (or not utilize) the adaptive delay set feature from the following formula:

$$V_{DEL} = [0.75 \bullet (V_{CS} - V_{ADS})] + 0.5V$$

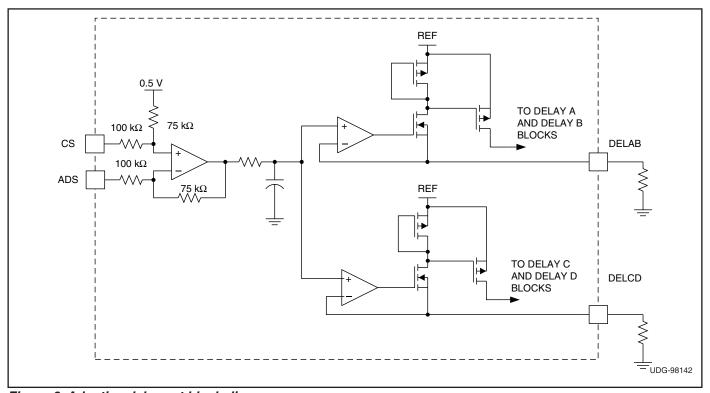

The following diagram illustrates the resistors needed to program the delay periods and the adaptive delay set function.

Figure 1. Resistors needed in programming.

# **APPLICATION INFORMATION (CONT.)**

The Adaptive Delay Set feature (ADS) allows the user to vary the delay times between switch commands within each of the converter's two legs. The delay time modulation is implemented by connecting ADS (pin 11) to CS, GND, or a resistive divider from CS to GND to set V<sub>ADS</sub>. From the equation for V<sub>DEL</sub> above, if ADS is tied to GND then V<sub>DEL</sub> rises in direct proportion to V<sub>CS</sub>, causing a decrease in t<sub>DELAY</sub> as the load increases. In this condition the maximum value of V<sub>DEL</sub> is 2V. If ADS is connected to a resistive divider between CS and GND the term (V<sub>CS</sub>-V<sub>DS</sub>) becomes smaller, reducing the level of V<sub>DEL</sub>. This will decrease the amount of delay modulation. In the limit of ADS tied to CS, V<sub>DFI</sub> =0.5V and no delay modulation occurs. In the case with maximum delay modulation (ADS=GND), when the circuit goes from light load to heavy load the variation of V<sub>DFI</sub> is from 0.5V to 2V. This causes the delay times to vary by a 4:1 ratio as the load is changed.

The ability to program an adaptive delay is a desirable feature because the optimum delay time is a function of the current flowing in the primary winding of the transformer, and can change by a factor of 10:1 or more as circuit loading changes. Reference [1] delves into the many interrelated factors for choosing the optimum delay times for the most efficient power conversion, and illustrates an external circuit to enable adaptive delay set us-

ing the UC3879. Implementing this adaptive feature is simplified in the UCC3895 controller, giving the user the ability to tailor the delay times to suit a particular application with a minimum of external parts.

Figure 2. Resistors needed for programming.

[1] L. Balogh, "Design Review: 100W, 400kHz, DC/DC Converter With Current Doubler Synchronous Rectification Achieves 92% Efficiency," Unitrode Power Supply Design Seminar Manual, Unitrode Corporation, 1996, Topic 2.

Figure 3. UCC3895 timing diagram (no output delay shown).

# **APPLICATION INFORMATION (cont.)**

Figure 4. Block diagram.

# **CIRCUIT DESCRIPTION**

Figure 5. Oscillator block diagram.

Figure 6. Adaptive delay set block diagram.

# **CIRCUIT DESCRIPTION (cont.)**

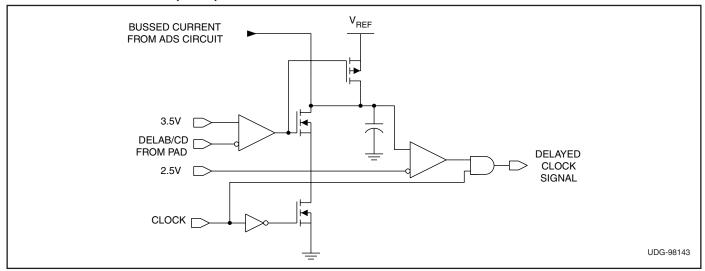

Figure 7. Delay block diagram (one delay block per output).

## **TYPICAL CHARACTERISTIC**

Figure 8. Delay programming: characterizes the output delay between A/B, C/D.

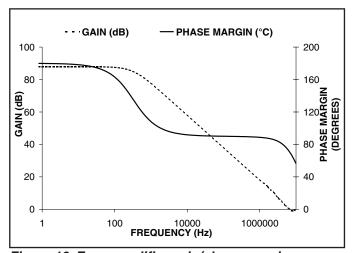

Figure 10. Error amplifier gain/phase margin.

Figure 9. EAOUT to RAMP offset over temperature.

Figure 11. Frequency vs. RT/CT (oscillator frequency).

# **TYPICAL CHARACTERISTIC (cont.)**

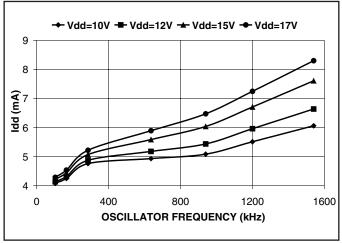

Figure 12. Idd vs. Vdd / oscillator frequency (no output loading).

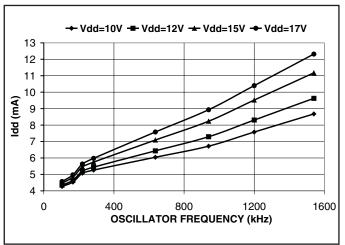

Figure 13. Idd vs. Vdd / oscillator frequency (with 0.1nf output loads).

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265