# UT1750AR RISC Microprocessor

**Data Sheet**

Oct. 1998

### **FEATURES**

- ☐ Operates in either RISC (Reduced Instruction Set Computer) mode or MIL-STD-1750A mode

- ☐ Supports MIL-STD-1750A 32-bit floating-point operations and 48-bit extended-precision floating-point operations on chip

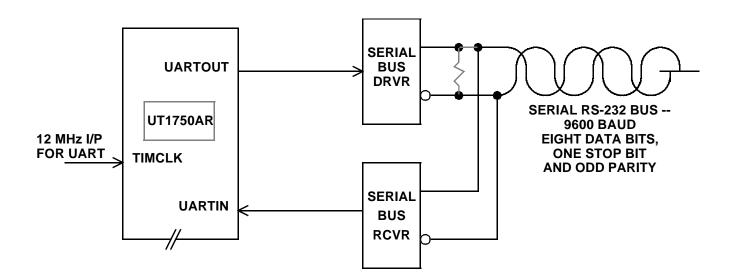

- ☐ Built-in 9600 baud UART

- ☐ Supports defined MIL-STD-1750A Console Mode of Operation

- ☐ Full 64K-word address space. Expandable to 1M words with optional MMU (operand port)

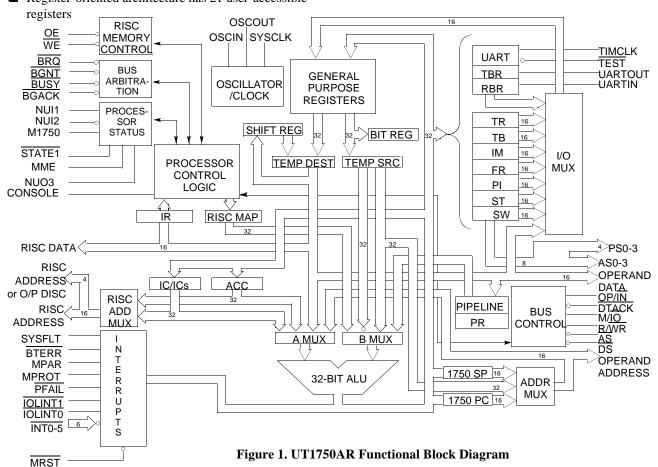

- ☐ Register-oriented architecture has 21 user-accessible

- ☐ Registers may be in 16-bit word or 32-bit double-word configurations

- ☐ Built-in multiprocessor bus arbitration and Direct Memory Access support (DMA)

- ☐ TTL-compatible I/O

- ☐ Stable 1.5-micron CMOS technology

- ☐ Standard Military Drawing available

- ☐ Full military operating range, -55°C to +125°C, screened to specific test methods listed in Table I MIL-STD-883 Method 5004, Class B

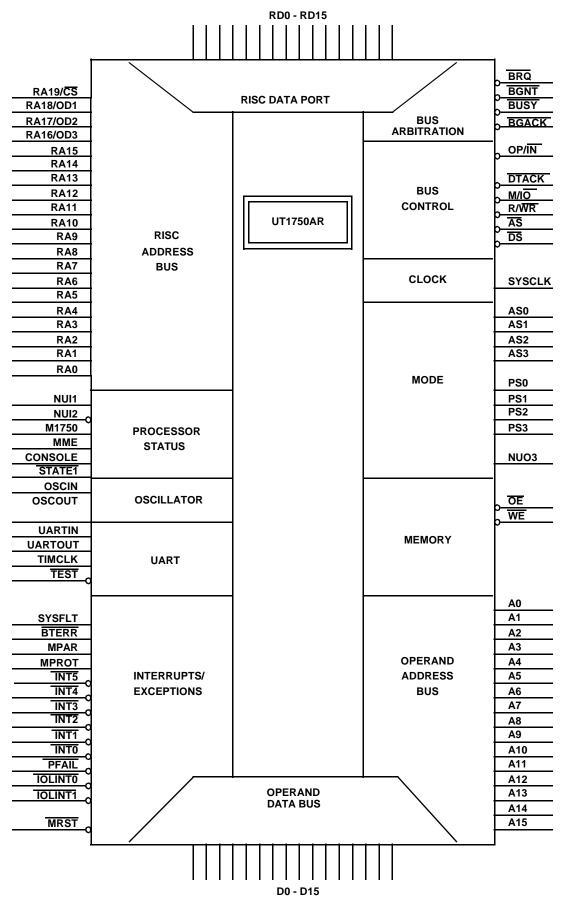

Figure 2. UT1750AR Pin Function Diagram

#### **GENERAL DESCRIPTION**

The UT1750AR (figures 1 and 2) is a high performance monolithic CMOS 16-bit RISC microprocessor that supports the complete MIL-STD-1750A Instruction Set Architecture (ISA). Underlying the MIL-STD-1750A support is a high-performance RISC that provides MIL-STD-1750A emulation capability. Developed to provide effective real-time avionics processing, the high performance of the native RISC machine is available to the MIL-STD-1750A systems designer through the MIL-STD-1750A Built-In-Function (BIF) opcode.

The UT1750AR is the first member of a family of high-performance MIL-STD-1750 processors and support peripherals from UTMC.

#### PRODUCT DESCRIPTION

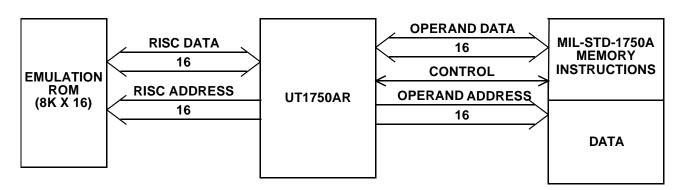

The UTMC UT1750AR operates in its native RISC language mode or MIL-STD-1750A ISA mode. As a MIL-STD-1750A microprocessor, the UT1750AR requires 8K x 16 of ROM to map the MIL-STD-1750A instruction set into the native RISC machine language instructions. Each MIL-STD-1750A opcode has a unique RISC code macro in the external ROM. The UT1750AR executes the corresponding resident RISC code macro to perform the MIL-STD-1750A instruction requirements. When in this mode and operating with a 12 MHz clock, the UT1750AR can throughput 600 KIPS using the DAIS mix (800 KIPS @ 16 MHz).

The native RISC language mode is available to the user when the UT1750AR is operating as MIL-STD-1750A processor through MIL- STD-1750A's Built-In Function (BIF) opcode. When operating as a RISC processor, the UT1750AR executes most RISC instructions in two clock cycles. Thus, a 12 MHz operating clock frequency provides up to 6 MIPS of RISC throughput (8 MIPS @16 MHz). This high execution rate, along with its efficient architecture, make the RISC mode especially effective in applications requiring real-time processing.

The architecture of the UT1750AR is based around 20 user-accessible, 16-bit general purpose registers providing the programmer with extensive register support. The UT1750AR's flexibility is enhanced by its ability to concatenate the 16-bit registers into ten 32-bit registers. In addition, all registers are available for use as either the source or the destination for any register operation.

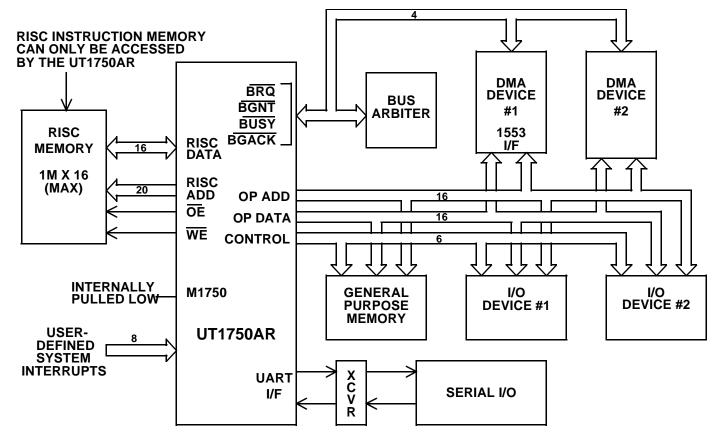

The UT1750AR fully supports multiprocessor, DMA, and complex bus arbitration for managing the system bus and preventing bus contention. Bus control passes among bus masters operating on the same bus. The bus masters can be several UT1750ARs or any other device requiring Direct Memory Access, such as a MIL-STD-1553B interface.

The UT1750AR supports 16 levels of vectored interrupts. Ten of these are external interrupts, eight of which are user-definable. All 16 interrupt levels are prioritized and serviced in order of priority.

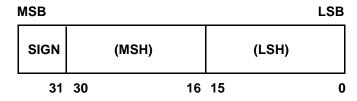

When used as a MIL-STD-1750A microprocessor, the UT1750AR's instruction set supports 16-bit fixed-point single-precision and 32-bit fixed-point double-precision data formats. Also, the UT1750AR can emulate 32-bit floating-point and 48-bit floating-point extended-precision data in two's complement representation.

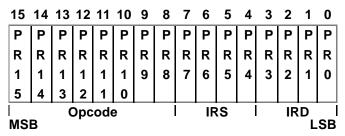

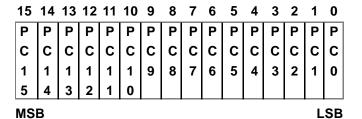

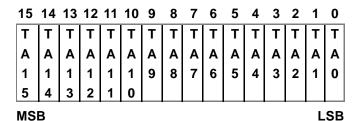

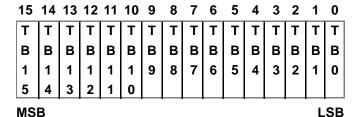

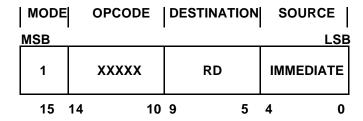

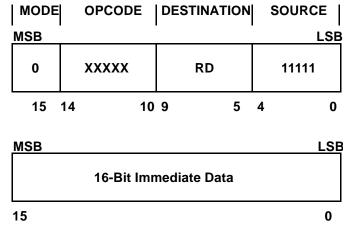

In its native RISC mode, the UT1750AR's three basic instruction formats support 16-bit and 32-bit instructions. The formats are Register-to-Register, Register-to-Literal, and Register-to-Long-Immediate instructions.

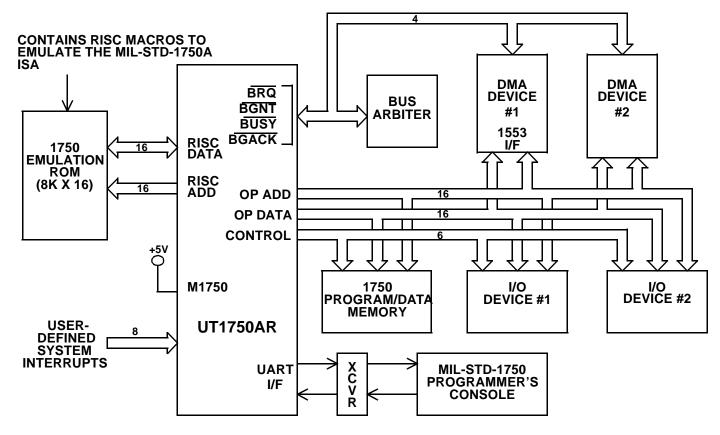

Figure 3 shows the UT1750AR's general system architecture, its emulation ROM, instruction and data memory, and the system interface. The emulation ROM is isolated from the system; only the UT1750AR microprocessor accesses it.

Figure 3. UT1750AR MIL-STD-1750A General System Architecture

# **FUNCTIONAL PINOUT**

Legend for TYPE and ACTIVE fields:

TO = TTL output TI = TTL input

TUI = TTL input (pull-up)

TDI = TTL input (pull-down)

TTO = Three-state TTL output

TTB = Three-state TTL bidirectional

CO = CMOS output

OSC = Oscillator input to a Pierce Oscillator inverter

AH = Active High AL = Active Low

# OSCILLATOR AND CLOCK SIGNALS

| PIN NAME | PIN NU<br>FLTPK | MBER<br>PGA | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                              |

|----------|-----------------|-------------|------|--------|----------------------------------------------------------------------------------------------------------|

| OSCIN    | 50              | P14         | OSC  |        | Oscillator Input. A 50% duty cycle crystal-drive input for                                               |

| OSCOUT   | 51              | P15         | СО   |        | Oscillator Output. A 50% duty cycle, single-phase clock output at the same frequency as the OSCIN input. |

| SYSCLK   | 52              | M14         | ТО   |        | System Output. The buffered equivalent of the OSCOUT                                                     |

# **PROCESSOR STATUS**

| PIN NAME | PIN NU | MBER<br>PGA | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                         |

|----------|--------|-------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUI1     | 129    | H2          | TI   | АН     | Not used input 1. Internal UTMC use only. Tie either high                                                                                                                                                                                                                                                           |

| NUI2     | 44     | P12         | TUI  | AL     | Not used input 2. Internal UTMC use only. Tie low.                                                                                                                                                                                                                                                                  |

| NUO3     | 126    | G3          | TTO  | АН     | Not used output 3. Internal UTMC use only. NUO3 enter high impedance state when the UT1750AR is in the test mode (TEST=0)                                                                                                                                                                                           |

| M1750    | 45     | N11         | TDI  | АН     | Mode Select RISC/1750. A high on M1750 places the UT1750AR into the MIL-STD-1750A emulation mode. A low on M1750 places the UT1750AR into the RISC mode. It is tied to an internal pull-down resistor.                                                                                                              |

| STATE1   | 54     | N15         | ТТО  |        | Processor State. This signal indicates the internal state of the UT1750AR. A low on STATE1 indicates the UT1750AR is executing a new RISC instruction. A high on STATE1 indicates the UT1750AR is fetching a RISC instruction. STATE1 enters a high-impedance state when the UT1750AR is in the test mode (TEST=0). |

# OPERAND DATA BUS ARBITRATION

| PIN NAME | PIN NU | 1      | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                           |

|----------|--------|--------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRQ      | 118    | PGA D2 | TTO  | AL     | Bus Request. The UT1750AR asserts this signal to indicate it is requesting control of the Operand data bus (D0 - D15). $\overline{BRQ}$ enters a high-impedance state when the UT1750AR is in the test mode ( $\overline{TEST} = 0$ ).                                |

| BGNT     | 119    | E3     | TUI  | AL     | Bus Grant. When asserted, this signal indicates the UT1750AR may take control of the Operand data bus. It is tied to an internal pull-up resistor.                                                                                                                    |

| BUSY     | 120    | C1     | TUI  | AL     | Bus Busy. A bus master asserts this input to inform the UT1750AR that another bus master is using the Operand data bus. It is tied to an internal pull-up resistor.                                                                                                   |

| BGACK    | 117    | B1     | TTO  | AL     | Bus Grant Acknowledge Output. The UT1750AR asserts this signal to indicate it is the current bus master. When low, BGACK inhibits other devices from becoming the bus master. When the UT1750AR relinquishes control of the bus, BGACK enters a high-impedance state. |

# OPERAND DATA BUS CONTROL

| PIN NAME         | PIN NU | MBER | TYPE | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------|------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | FLTPK  | PGA  | 1112 | HellvE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

| OP/IN            | 113    | A2   | TTO  |        | Operand/Instruction. This indicates whether the UT1750AR's current bus cycle is for Data (high) or Instruction (low) acquisition. OP/IN remains in a high state whenever a bus cycle (Memory or I/O) is not an instruction fetch.                                                                                                                |

| DTACK            | 121    | E2   | TUI  | AL     | Data Transfer Acknowledge. This signal tells the UT1750AR that a data transfer has been acknowledged and the UT1750AR can complete the bus cycle. To assure the UT1750AR operates with no wait states, DTACK can be tied low. DTACK is tied to an internal pull-up resistor.                                                                     |

| M/IO             | 112    | В3   | TTO  |        | Memory or I/O. Indicates whether the current bus cycle is for memory (high) or I/O (low). It remains in the high-impedance state during bus cycles when the UT1750AR does not control the Operand busses.                                                                                                                                        |

| R/ <del>WR</del> | 114    | C4   | ТТО  |        | Read/Write. Indicates the direction of data flow with respect to the UT1750AR. R/WR high means the UT1750AR is attempting to read data from an external device, and R/WR low means the UT1750AR is attempting to write data to an external device. R/WR remains in a high-impedance state when the UT1750AR does not control the Operand busses. |

Continued on page 6.

# OPERAND DATA BUS CONTROL

# Continued from page 5.

| PIN NAME | PIN NU<br>FLTPK | MBER<br>PGA | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                              |

|----------|-----------------|-------------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĀS       | 115             | С3          | ТТО  | AL     | Address Strobe. Indicates a valid address on the Operand Address bus. UT1750AR places <u>AS</u> in a high-impedance state when it does not control the Operand busses.   |

| DS       | 116             | B2          | ТТО  | AL     | Data Strobe. Indicates valid data is on the Operand Data bus. The UT1750AR places $\overline{DS}$ in a high-impedance state when it does not control the Operand busses. |

# RISC MEMORY CONTROL

| PIN NAME | PIN NU<br>FLTPK | MBER<br>PGA | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |

|----------|-----------------|-------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ŌE       | 42              | R12         | TTO  | AL     | Output Enable RISC Memory. This signal allows RISC memory to place data on the RISC instruction data bus. The Store Register to Instruction Memory (STRI) instruction removes $\overline{OE}$ during the CK2 internal clock cycle. $\overline{OE}$ enters a high-impedance state when the UT1750AR is in the test mode ( $\overline{TEST} = 0$ ). |

| WE       | 43              | R13         | TTO  | AL     | Write Enable RISC Memory. This signal allows the UT1750AR to write to RISC instruction memory. The Store Register to Instruction Memory (STRI) instruction asserts $\overline{WE}$ during the CK2 internal clock cycle. $\overline{WE}$ enters a high-impedance state when the UT1750AR is in the test mode ( $\overline{TEST}=0$ ).              |

# **UART CONTROL/TIMER CLOCK**

| PIN NAME | PIN NU | MBER<br>PGA | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

|----------|--------|-------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UARTIN   | 127    | F1          | TUI  | АН     | UART Input. The UT1750AR receives serial data through this input. The serial data is stored in the UT1750AR's Receiver Buffer Register (RCVR). It is tied to an internal pull-up resistor.                                                                                                                    |

| UARTOUT  | 128    | G1          | TTO  | АН     | UART Output. The serial data stored in the UT1750AR's Transmitter Buffer Register (TXMT) is transmitted through this output. The UART output is fixed at 9600 baud, with eight data bits, odd-parity, and one stop bit. UARTOUT enters a high-impedance state when the UT1750AR is in the test mode (TEST=0). |

Continued on page 7.

| PIN NAME | PIN NU | MBER | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------|------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIN NAME | FLTPK  | PGA  | LIFE | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                            |

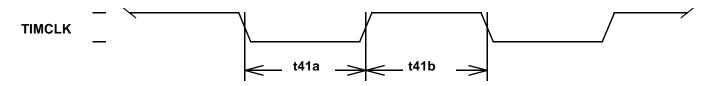

| TIMCLK   | 53     | L13  | TI   |        | Timer Clock. This 12 MHz clock input generates the baud rate for the UT1750AR's internal UART. The input also provides the clock for the UT1750AR's two internal MILSTD-1750A timers (TIMER A and TIMER B).                                                                                                                                                                                            |

| CONSOLE  | 48     | N12  | TDI  | АН     | Console (Command). Asserting this input sets bit 3 in the System Status Register. Bit 3 is read with the Input Register Instruction (INR). When the UT1750AR is operating in the MIL-STD-1750 mode, asserting CONSOLE during a Master Reset invokes the maintenance console option. Tied to an internal pull-down resistor.                                                                            |

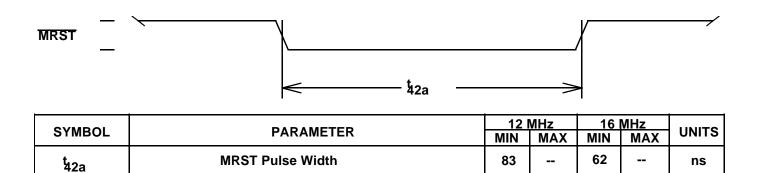

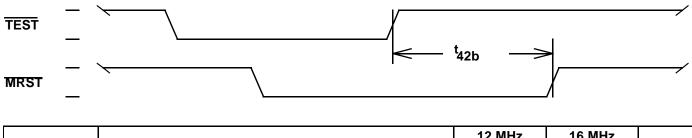

| TEST     | 46     | P13  | TUI  | AL     | Test (Input). Asserting this input places the UT1750AR into a test mode. In this mode, all the UT1750AR's outputs, except OSCOUT and SYSCLK, enter a high-impedance state. When using TEST, the UT1750AR must have a MRST. MRST must be held active for at least one SYSCLK period after TEST is deasserted to assure proper operation (see figure 42b). TEST is tied to an internal pull-up resistor. |

| ММЕ      | 49     | N13  | TDI  | АН     | Memory Management Enable. This signal indicates to the UT1750AR that a Memory Management Unit (MMU) is present and that the memory management option is enabled. MME is tied to an internal pull-down resistor.                                                                                                                                                                                        |

# PROCESSOR MODE

| PIN NAME                 | PIN NU                   |                      | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|--------------------------|----------------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AS0<br>AS1<br>AS2<br>AS3 | 104<br>105<br>106<br>107 | PGA  B7 B6 C6 A5     | ТТО  | АН     | Address State. These outputs indicate the current address state of the UT1750AR. Using these outputs with a Memory Management Unit (MMU) allows selecting the MMU's page register group. These outputs enter a high-impedance state when the UT1750AR is placed in the test mode (TEST=0) or during bus cycles not assigned to this processor. |

| PS0<br>PS1<br>PS2<br>PS3 | 108<br>109<br>110<br>111 | A4<br>A3<br>B4<br>C5 | TTO  | АН     | Processor State. These outputs indicate the current state of the processor. These outputs enter a high-impedance state when the UT1750AR is in the test mode (TEST=0) or during bus cycles not assigned to this processor.                                                                                                                     |

# INTERRUPTS/EXCEPTIONS

| PIN NAME                      | PIN NU<br>FLTPK                  | MBER<br>PGA                            | TYPE | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|----------------------------------|----------------------------------------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSFLT                        | 125                              | G2                                     | TUI  |        | System Fault. This positive edge-triggered input sets bit 8 (SYSFLT) in the UT1750AR's Fault Register. Under no circumstances should SYSFLT be tied in its active state. It is tied to an internal pull-up resistor.                                                                                                                                                                                                                                                                                |

| BTERR                         | 122                              | D1                                     | TUI  | AL     | Bus Time Error. It is asserted when a bus error or a timeout occurs. During I/O bus cycles, an active BTERR sets bit 10 of the Fault Register. During Memory bus cycles, an active BTERR sets bit 7 of the Fault Register. Under no circumstances should BTERR be tied in its active state. It is tied to an internal pull-up resistor.                                                                                                                                                             |

| MPAR                          | 124                              | F2                                     | TDI  | АН     | Memory Parity (Error). Asserting this input indicates a MIL-STD-1750 memory parity error. Bit 13 of the UT1750AR's Fault Register, Memory Parity Fault, is set when MPAR is active. Under no circumstances should MPAR be tied in its active state. It is tied to an internal pull-down resistor.                                                                                                                                                                                                   |

| MPROT                         | 123                              | F3                                     | TUI  | АН     | Memory Protect Fault. When asserted, it informs the UT1750AR that a memory-protect fault has occurred on the Operand Data Bus. An access fault, a write-protect fault, or an execute-protect fault causes a memory-protect fault. If the UT1750AR is using the bus and MPROT is asserted, bit 15 of the Fault Register (CPU Fault) is set. If the UT1750AR is not using the bus and MPROT is asserted, bit 14 of the Fault Register (DMA Error) is set. It is tied to an internal pull-up resistor. |

| INTO INT1 INT2 INT3 INT4 INT5 | 56<br>57<br>58<br>59<br>60<br>61 | M15<br>K13<br>K14<br>J14<br>J13<br>K15 | TUI  |        | User Interrupts. These interrupts are active on a negative-going edge and each will set, when active, its associated bit in the Pending Interrupt Register. The interrupts are maskable by setting the associated bits in the Interrupt Mask Register. Asserting MRST resets all interrupts. They are tied to an internal pull-up resistor.                                                                                                                                                         |

| IOLINTO<br>IOLINT1            | 62<br>63                         | J15<br>H14                             | TUI  |        | I/O Level Interrupts. These inputs are active on a negative-going edge and each sets, when active, its associated bit in the Pending Interrupt Register. The interrupts are maskable by setting the associated bits in the Interrupt Mask Register. Asserting MRST resets all interrupts. They are tied to an internal pull-up resistor.                                                                                                                                                            |

| PFAIL                         | 55                               | L14                                    | TUI  | AL     | Power Fail (Interrupt). Asserting this input informs the UT1750AR that a power failure has occurred and the present process will be interrupted. This input sets bit 15 in the Pending Interrupt Register. A Power Fail Interrupt (bit 15) cannot be disabled. When operating in the RISC mode, the UT1750AR must be reset after a PFAIL to assure normal operation. It is tied to an internal pull-up resistor.                                                                                    |

| MRST                          | 47                               | R14                                    | TUI  | AL     | Master Reset. This input initializes the UT1750AR to a reset state. The UT1750AR must be reset after power (Vcc) is within specification and stable to ensure proper operation. The system must hold MRST active for at least one period of SYSCLK to assure the UT1750AR will be reset. It is tied to an internal pull-up resistor.                                                                                                                                                                |

# **OPERAND BUSSES**

| PIN NAME                                                                                           | PIN NU                                                                                         | MBER                                                                                                         | TYPE | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME                                                                                           | FLTPK                                                                                          | PGA                                                                                                          | TIPE | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

| A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15 | 84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>102<br>103 | A14<br>B12<br>C11<br>A13<br>B11<br>A12<br>C10<br>B10<br>B9<br>C9<br>A10<br>A9<br>B8<br>A8<br>A7              | TTO  | АН     | Address Bus - Operand. When asserted, this bus is unidirectional and represents the Operand Address. The bus is in the high-impedance state when the UT1750AR does not control the bus. A15 is the most significant bit. The Operand Address enters a high-impedance state when the UT1750AR is in the test mode (TEST = 0). |

| D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15                                              | 64<br>69<br>70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78<br>79<br>80<br>81<br>82<br>83   | H15<br>G15<br>F15<br>G14<br>F14<br>F13<br>E15<br>D15<br>C15<br>D14<br>E13<br>C14<br>B15<br>D13<br>C13<br>B14 | TTB  | АН     | Data Bus - Operand. This bidirectional data bus remains in a high-impedance state when the UT1750AR does not control the bus. D15 is the most significant bit. The Operand Data Bus enters a high-impedance state when the UT1750AR is in the test mode (TEST = 0).                                                          |

# RISC BUSSES

| PIN NAME                                                                                                   | PIN NU                                                                                       | MBER                                                                                   | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                            | FLTPK                                                                                        | PGA                                                                                    |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

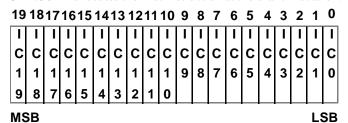

| RA0<br>RA1<br>RA2<br>RA3<br>RA4<br>RA5<br>RA6<br>RA7<br>RA8<br>RA9<br>RA10<br>RA11<br>RA12<br>RA13<br>RA14 | 18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>36<br>37 | R2<br>P4<br>N5<br>R3<br>P5<br>R4<br>N6<br>P6<br>P7<br>N7<br>R6<br>R7<br>P8<br>R8<br>R9 | TTO  | АН     | RISC (Instruction) Address Bus. This unidirectional bus represents the address of the data in RISC memory. With the MIL-STD-1750A mode of operation selected (M1750 = 1), the data from RISC memory is from the emulation ROMs. This data is the RISC instructions that the UT1750AR executes to emulate MIL-STD-1750A instructions. RA15 is the most significant bit. The RISC address enters a high-impedance state when the UT1750AR is in the test mode (TEST = 0). |

Continued on page 10.

| PIN NAME                                                                                                           | PIN NU                                                                                 | MBER                                                                                         | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IIIIIIAMIL                                                                                                         | FLTPK                                                                                  | PGA                                                                                          |      | ACIIVE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RA16/OD3<br>RA17/OD2<br>RA18/ <u>OD</u> 1<br>RA19/CS                                                               | 38<br>39<br>40<br>41                                                                   | P9<br>P10<br>N10<br>R11                                                                      | TTO  | АН     | RISC Instruction Address Bus/Output Discretes. When the UT1750AR is operating in the RISC mode (M1750 = 0) these four bits represent the four most significant address bits. In the MIL- STD-1750A mode (M1750 = 1) these four bits are user-programmable output discretes defined as follows:  RA19/\overline{CS} = Chip Select (AL) RA18/OD1 = Output Discrete 1 RA17/OD2 = Output Discrete 2 RA16/OD3 = Output Discrete 3  These output discretes are programmed with the Output Register (OTR) RISC opcode. These signals enter a high-impedance state when the UT1750AR is in the test mode (\overline{TEST} = 0). |

| RD0<br>RD1<br>RD2<br>RD3<br>RD4<br>RD5<br>RD6<br>RD7<br>RD8<br>RD9<br>RD10<br>RD11<br>RD12<br>RD13<br>RD14<br>RD15 | 130<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | H1<br>J1<br>K1<br>J2<br>K2<br>K3<br>L1<br>M1<br>N1<br>M2<br>L3<br>N2<br>P1<br>M3<br>N3<br>P2 | TTB  | АН     | RISC Instruction Data Bus. This bidirectional data bus is the interface with the RISC memory. When the UT1750AR is in the MIL-STD-1750A mode of operation, the data comes from the emulation ROMs. This data is executed to emulate the MIL-STD-1750A Instruction Set. RD15 is the most significant bit. The RISC Data Bus enters a high-impedance state only when the UT1750AR is in the test mode (TEST = 0).                                                                                                                                                                                                         |

# POWER AND GROUND

| DININIAME       | PIN NU                 | MBER                  | TXDE | A CODING | DESCRIPTION                              |

|-----------------|------------------------|-----------------------|------|----------|------------------------------------------|

| PIN NAME        | FLTPK                  | PGA                   | TYPE | ACTIVE   | DESCRIPTION                              |

| V <sub>DD</sub> | 34<br>67<br>100<br>132 | H3<br>N9<br>G13<br>C7 |      |          | +5 VDC Power. Power supply input.        |

| V <sub>SS</sub> | 1<br>33<br>66<br>99    | J3<br>N8<br>H13<br>C8 |      |          | Reference Ground. Zero VDC logic ground. |

#### GENERAL OPERATION

The UT1750AR can operate in two modes. The first operating mode is the Reduced Instruction Set Computer (RISC) mode; the second is the MIL-STD-1750A Instruction Set Architecture (ISA) emulation mode. The mode-select input pin (M1750) determines the UT1750AR's operating mode. M1750 must be tied high to enable the MIL-STD-1750A ISAemulation mode of operation; otherwise, an internal pull-down resistor pulls M1750 low, selecting the RISC mode.

The UT1750AR has a Harvard architecture when it operates in the RISC mode (M1750 = 0). A processor with a Harvard architecture has two sets of address and data busses; one set interfaces with instruction memory and the other set interfaces with operand memory. This architecture allows the UT1750AR to perform overlapping instruction fetch-and-execute bus cycles that enhance processor throughput.

The UT1750AR's reduced instruction set consists of 30 separate instructions. The UT1750AR executes most of these instructions in two clock cycles providing fast execution of RISC-coded programs. All the UT1750AR's processing capabilities in the RISC mode are available to the system programmer by using the companion RISC Assembler (RASM)/Linker (RLNK), RISC Interactive Software Simulator (IRSIM), and hardware development debug tools.

In the MIL-STD-1750A mode of operation (M1750 = 1), the UT1750AR has a Von Neumann architecture. A processor with a Von Neumann architecture has a common set of address and data busses that make instructions and operand data available to the processor.

The UT1750AR emulates the MIL-STD-1750A instruction set when it has a specially programmed set of RISC PROMs. These PROMs contain RISC-coded macros that correspond to each MIL-STD-1750 instruction. When the UT1750AR fetches a 1750 instruction from memory, it decodes this instruction's opcode and generates an address for the RISC PROMs. This address points to a RISC macro that, when executed, performs the operation the 1750 instruction requires.

The high execution rate of the UT1750AR's native RISC language is also available when the UT1750AR is in the MIL-STD-1750 mode of operation by using the MIL-STD-1750 Built-in-Function (BIF) opcode. The system designer can develop a RISC macro for a specific function, such as poweron self-test routines, built-in-test routines, signal-processing routines, or any routine that requires real-time processing. The UT1750AR executes this function when it encounters the BIF in the MIL-STD-1750 program flow.

#### The RISC Mode of Operation

The configuration for the UT1750AR in the RISC mode of operation is shown in figure 4. RISC is the default mode of operation for the UT1750AR since the M1750 input is tied to an internal pull-down resistor.

When the UT1750AR operates in the RISC mode, the system designer stores the executable RISC program in RISC memory. The UTMC RISC Assembler generates this executable RISC program. All 20 of the RISC address lines can access a user-defined program in RISC memory. This means the maximum length of any RISC program is 1 mega- word.

Although the executable RISC program is all that is stored in RISC memory, two RISC instructions allow the programmer to manipulate the data in RISC memory. These instructions are the Load Register from (RISC) Instruction Memory (LRI) and the Store Register to (RISC) Instruction Memory (STRI).

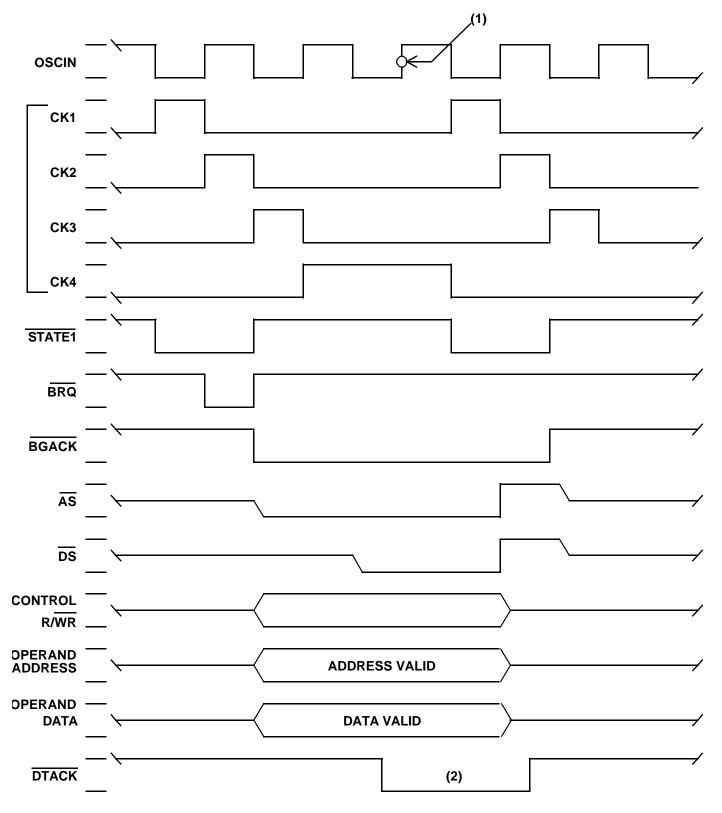

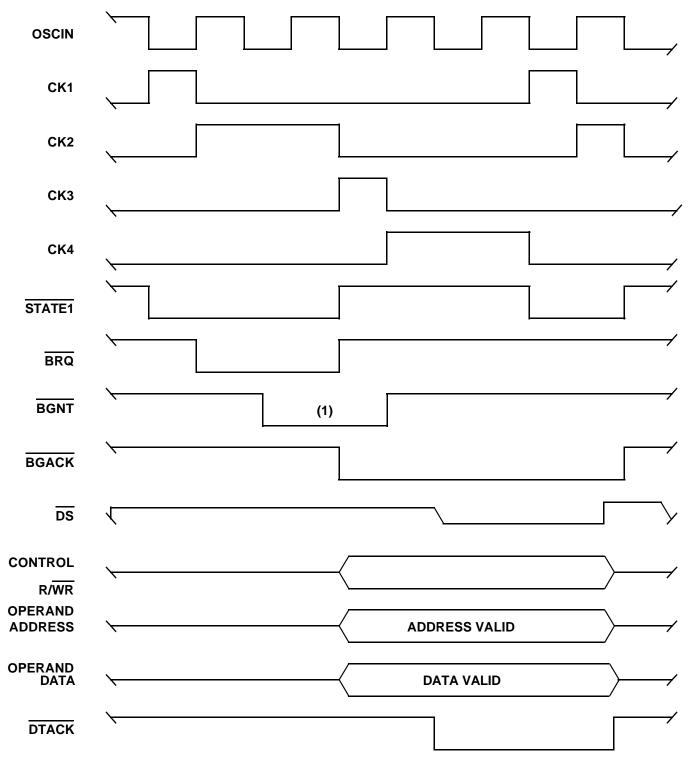

When operating in the RISC mode, the UT1750AR first generates an address on the RISC address bus for the instruction it stores in the Primary Instruction Register (PIR). After the UT1750AR stores the RISC instruction in the PIR, the UT1750AR begins executing the instruction in the Instruction Register (IR). If the present instruction in the IR requires only internal processing, the UT1750AR does not exercise the Operand Address and data busses. If, on the other hand, the instruction in the IR requires some type of Operand Data, the UT1750AR begins an Operand bus arbitration cycle midway through the next processor clock cycle.

The Operand bus arbitration cycle begins with the UT1750AR asserting the Bus Request  $(\overline{BRQ})$  signal. The UT1750AR samples the Bus Grant  $(\overline{BGNT})$  and the Bus Busy  $(\overline{BUSY})$  signals on every falling edge of the processor clock. When the UT1750AR detects that the previous bus controller has relinquished control of the bus, the UT1750AR generates the Bus Grant Acknowledge  $(\overline{BGACK})$  signal signifying that it has taken control of the bus.

After the UT1750AR has taken control of the bus, it generates the Operand address and data. The Address Strobe  $(\overline{AS})$  and Data Strobe  $(\overline{DS})$  signals indicate when the Operand address and data are valid. If the UT1750AR is interfacing to slow memory or other peripheral devices that require long memory-access times, the Data Transfer Acknowledge  $(\overline{DTACK})$  signal extends the memory cycle time. By holding off the assertion of  $\overline{DTACK}$ , the slow memory device lengthens the memory cycle until it can provide data for the UT1750AR.

Figure 4. The UT1750AR in the RISC Mode of Operation

All user-definable interrupts are available when the UT1750AR is operating as a RISC. In addition, the system programmer can read or write to virtually all of the UT1750AR's internal registers, either general purpose or specialized, when the UT1750AR is in the RISC mode by using the Internal I/O command (INR) or the Output Register command (OTR), respectively.

### The 1750A Mode of Operation

The configuration for the UT1750AR in the MIL-STD-1750A mode of operation is shown in figure 5. The UT1750AR enters the 1750 mode of operation when the mode input, M1750, is pulled high.

The functional operation of the UT1750AR in the MIL-STD-1750 mode is similar to the RISC mode of operation, although it has two important differences. The first difference is that when the system designer selects the MIL-STD-1750 mode, the UT1750AR requires a specific set of RISC PROMs specially programmed to allow the UT1750AR to emulate the 1750 ISA.

This special set of RISC PROMs contains a set of RISC-coded macros that allow the UT1750AR to serve as a full-feature MIL-STD-1750A microprocessor. In this respect, the RISC PROMs hold external microcode, or "Mili"-code. This "Mili"-code tells the UT1750AR how to function as a 1750 processor and, if necessary, the user can change the "Mili"-code if the application requires additional capability for real-time processing.

The second difference between the operation of the UT1750AR in the 1750 mode and the RISC mode is that in the 1750 mode the RISC address bus is limited to 16 address lines or 64K words instead of the UT1750AR's 20-bit RISC address bus in the RISC mode. When in the 1750 mode, the UT1750AR uses the four most significant bits of the RISC address bus for output discretes. The output discrete that replaces the most significant address bit (RA19) is a dedicated chip select.

Figure 5. The UT1750AR in the MIL-STD-1750 Mode of Operation

The next three RISC address bits (RA16-RA18) are user-definable discrete outputs. These outputs are defined as:

RA16/OD3  $\longrightarrow$  DMA enable ( $\overline{DMAEN}$ )

RA17/OD2  $\longrightarrow$  power-up ( $\overline{GOOD}$ )

RA18/OD1  $\longrightarrow$  start-up ROM enable ( $\overline{SUREN}$ )

After reset these signals will be in the following states:

RA16  $\longrightarrow$  1, RA17  $\longrightarrow$  0, RA18  $\longrightarrow$  0.

When the UT1750AR operates in the MIL-STD-1750 mode, it generates an address on the Operand address bus for the next 1750 instruction. If the UT1750AR has just been initialized or has just been reset, the first memory location placed on the Operand Address Bus is 0000H; this instruction is the first one fetched from the 1750 memory. After this instruction is fetched and entered into the UT1750AR, the UT1750AR uses the opcode to "map" or point to a specific address in the RISC memory. Since the RISC PROM programming provides 1750 emulation capability, this address in RISC memory contains a specific RISC-coded macro allowing the UT1750AR to perform the requisite 1750 function.

When the UT1750AR begins executing this RISC macro for 1750 emulation, the UT1750AR begins to operate as if it were in the RISC mode (see the previous section on RISC mode of operation). The processor cycles of all the RISC instructions

that make up the particular macro are executed as if the UT1750AR were operating purely as a RISC.

During RISC macro execution for the MIL-STD-1750 instruction, the internal registers of the UT1750AR hold the intermediate results from the execution of the RISC instructions. When the macro is complete, the UT1750AR's registers contain the data the MIL-STD-1750A instruction requires.

If the UT1750AR receives an interrupt during RISC macro execution, the RISC macro completes execution before the UT1750AR recognizes the interrupt. This is similar to completing a single 1750 instruction rather than allowing its interruption. The only exception is with the multiple-word MOV 1750 instruction. For this instruction, the UT1750AR interrupts macro execution after transferring the current word.

After the RISC macro is complete, all the UT1750AR's internal registers, including the status registers and/or memory locations, contain the results of the MIL-STD-1750A instruction that has just completed execution. The UT1750AR now fetches the next 1750 instruction from Operand memory and the process repeats.

The advanced architecture of the UT1750AR allows the system designer to define RISC macros accessible through the MIL-STD-1750A Built-In Function (BIF) opcode. These user-defined RISC macros can be any regularly-used function requiring the UT1750AR's high-speed, real-time processing capabilities. The UT1750AR fetches the BIF instruction from Operand memory just like any other 1750 instruction; it then decodes the BIF. The resulting UT1750AR-generated RISC address points to the location of the user-defined macro in RISC memory. RISC macro execution proceeds just as it would for any other 1750 instruction. MIL-STD-1750A permits the system designer to define up to 256 BIF variations.

#### REGISTER ARCHITECTURE

The UT1750AR has a register-oriented architecture (figure 1). The registers within the UT1750AR fall into two categories: general purpose registers, and specialized registers. All the UT1750AR's registers are accessible to the programmer through the RISC instruction set. The programmer uses data from these registers to perform arithmetic and logical functions, alter program flow, detect various system and processor faults, determine processor status, provide control for UART and timer functions, and provide interrupt processing and exception-handling control.

| 16 BITS | 16 BITS | CONCATENATED 32-BIT<br>REGISTER PAIR |

|---------|---------|--------------------------------------|

| R0      | R1      | XR0                                  |

| R2      | R3      | XR2                                  |

| R4      | R5      | XR4                                  |

| R6      | R7      | XR6                                  |

| R8      | R9      | XR8                                  |

| R10     | R11     | XR10                                 |

| R12     | R13     | XR12                                 |

| R14     | R15     | XR14                                 |

| R16     | R17     | XR16                                 |

| R18     | R19     | XR18                                 |

| ACCUM   | ULATOR  | ACC                                  |

Figure 6. General Register Set

# **General Purpose Registers**

Figure 6 shows the UT1750AR's 20 general purpose registers. All RISC instructions use these registers; any register or register pair can be either the source or the destination for any RISC instruction. The UT1750AR normally accesses these registers as single-word 16-bit registers although the UT1750AR can

concatenate these registers into 32-bit double-word register pairs. When the programmer uses the general purpose registers as a double-word register pair, the most significant 16 bits of the 32-bit words are stored in the even-numbered register of the register pair. For instance, if a 32-bit word is stored in Register Pair XR6, the most significant word is stored in register R6 and the least significant word is stored in register R7.

In addition to the 20 general purpose registers, the UT1750AR has a 32-bit Accumulator (ACC). The ACC is normally a destination register, although under certain circumstances it can be the source register. The Accumulator retains the most significant half of the product during a multiply instruction or the remainder during a divide operation.

#### **Specialized Registers**

The UT1750AR has 16 special purpose registers (figures 7 through 24). The values in the brackets indicate the power-up condition. They are:

- 1. Stack Pointer Register (SP) [XXXX16]

- 2. System Status Register (STATUS)

- 3. UART Receiver Buffer Register (RCVR) [XX0016]

- 4. UART Transmitter Buffer Register (TXMT) [XX0016]

- 5. Pending Interrupt Register (PI) [000016]

- 6. Fault Register (FT) [000016]

- 7. Interrupt Mask Register (MK) [XXXX16]

- 8. 1750 Status Register (SW) [000016]

- 9. RISC Instruction Counter Register (IC) [0000016]

- 10. RISC Instruction Counter Save Register (ICS) [XXXXX16]

- 11. RISC Instruction Register (IR) [000016]

- 12. 1750 Pipeline Register (PIPE) [XXXX16]

- 13. 1750 Program Register (PR) [XXXX16]

- 14. 1750 Program Counter (PC) [XXXX16]

- 15. 1750 Timer A Register (TA) [000016]

- 16. 1750 Timer B Register (TB) [000016]

The RISC instruction set provides access to most of the special purpose registers.

The Stack Pointer Register

Figure 7. The UT1750AR uses the 16-bit Stack Pointer Register as an address pointer on Push and

Figure 7. The Stack Pointer Register (SP)

| mode, it pre<br>the SP. In the                  | e-increments (pops)<br>e 1750 mode, the UT                                                | 750AR is operating in the RISC and post-decrements (pushes) Γ1750AR pre-increments (pops) | 7 | RE  | Receiver Error. This bit is the logical OR combination of the OE, FE, and PE status bits. [0]                                                                                                         |

|-------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The program to Load and The System Figure 8. Th | Status Register<br>ne System Status Re                                                    | P by using local I/O commands                                                             | 6 | OE  | Overrun Error. When active, this bit indicates that at least one data word was lost because the Data Ready (DR is bit 0 of the STATUS) signal was active twice consecutively without an RBR read. [0] |

| status of the given below                       | internal UART. The                                                                        | e bit definitions for STATUS are                                                          | 5 | FE  | Framing Error. When active, this bit indicates a stop bit was missing from the serial transmission. [0]                                                                                               |

| C P Z                                           | N V J I M E E                                                                             | R O F P C B T D B E R                                                                     | 4 | PE  | Parity Error. When active, this bit indicates the serial transmission wasreceived with the incorrect parity. [0]                                                                                      |

| Bit Definition                                  | ons                                                                                       | LSB tatus Register (STATUS)                                                               | 3 | CN  | MIL-STD-1750A Console<br>Enabled. When active, this bit<br>indicates the CONSOLE<br>discrete input is active.<br>CONSOLEactivesetsbit3inthe<br>System Status Register.                                |

|                                                 | ets indicate the pov                                                                      |                                                                                           | 2 | TBE | UART Transmitter Buffer<br>Empty. This bit indicates the<br>Transmitter Buffer Register is<br>empty and ready for data. [0]                                                                           |

| 15                                              | C                                                                                         | Carry. This conditional status is set if a carry generated. [0]                           | 1 | TE  | UART Transmitter Empty. This bit is low while the UART is transmitting data and goes high when the                                                                                                    |

| 14                                              | P                                                                                         | Positive. This conditional status is set if the result of operation is positive. [0]      | 0 | DR  | transmission is complete. [0] UART Data Ready. This                                                                                                                                                   |

| 13                                              | Z                                                                                         | Zero. This conditional statusis set if the result of an operation is equal to zero. [0]   |   |     | active-high signal indicates the UART received a serial data word and this data is available. [0]                                                                                                     |

| 12                                              | N Negative. This conditional status is set if the result of an operation is negative. [0] |                                                                                           |   |     |                                                                                                                                                                                                       |

| 11                                              | 11 V Overflow. This conditional status is set when an overflow condition occurs. [0]      |                                                                                           |   |     |                                                                                                                                                                                                       |

| 10                                              | J                                                                                         | Normalized. This conditional status is set as the result of a long instruction. [0]       |   |     |                                                                                                                                                                                                       |

| 9                                               | IE                                                                                        | Interrupts enabled. [0]                                                                   |   |     |                                                                                                                                                                                                       |

| 8                                               | MME                                                                                       | Memory Management enabled. [0]                                                            |   |     |                                                                                                                                                                                                       |

#### UART Receiver Register (RCVR)

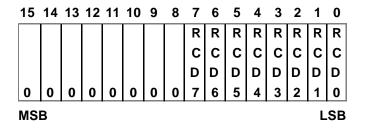

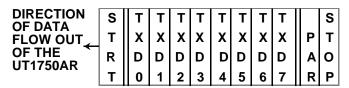

The UART Receiver Buffer Register (see figure 9) receives 9600-baud asynchronous serial data through the UARTIN input pin on the UT1750AR. Each serial data string contains an active-low Start bit, eight Data bits, an odd Parity bit, and an active-high Stop bit. Figure 10 shows a single serial data string.

Figure 9. The UART Receiver

Figure 10. UART Receiver Data String

While receiving a serial data string, the UT1750AR generates four status flags: Data Ready (DR); Overrun Error (OE); Framing Error (FE); and Parity Error (PE). The UT1750AR stores these status bits in the System Status Register (STATUS).

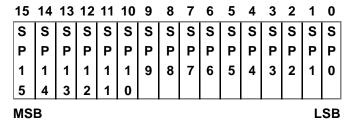

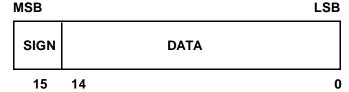

Receiver buffer register bits 15-8 are always low. Bit numbers 7-0 (RCD7-RCD0) contain data the UT1750AR receives via the serial data port. RCD7 is the MSB; RCD0 is the LSB.

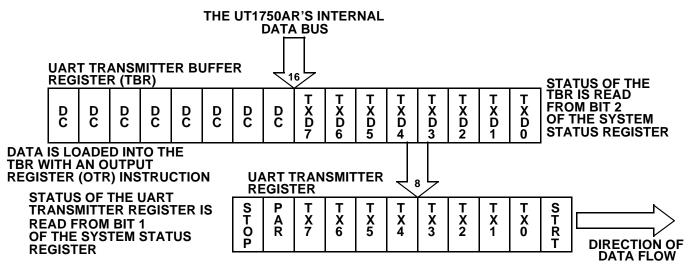

#### UART Transmitter Buffer Register (TXMT)

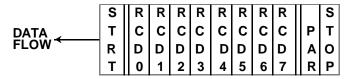

The UT1750AR's internal UART forms an 11-bit serial data string by combining a Start bit, the eight Data bits from the Transmitter Buffer Register (TXMT), an odd Parity bit, and a Stop bit. Figure 11 shows the composition of the serial data string.

The UT1750AR transmits this serial data string through the UARTOUT pin at a rate of 9600 baud.

Figure 11. UART Transmitter Data String

Two status signals are associated with transmitting serial data. These signals are the UART Transmitter Buffer Empty (TBE) and UART Transmitter Register Empty (TE). TBE and TE are both active high and provide information on the status of double buffering the UART's transmitted data. TBE and TE are read from the System Status Register as bits 2 and 1, respectively.

The UT1750AR's internal UART has a double-buffered data transmission scheme (figure 12). The UT1750AR first loads the data for transmission into the Transmitter Buffer Register. If the UART Transmitter Register is empty, data from the TXMT automatically transfers to the UART Transmitter Register. At this time, the TBE bit goes active indicating more data may be loaded into the TXMT. This double-buffering scheme allows contiguous transmission of serial data streams and also decreases the UT1750AR's required overhead for the UART interface.

Figure 12. The UT1750AR UART Double-Buffered Transmitter Register

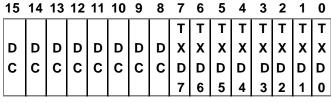

The UT1750AR loads the eight bits of serial data into the lower eight bits of the TXMT (figure 13).

**MSB LSB** DC = Don't Care

Figure 13. The UART Transmitter

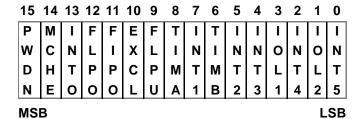

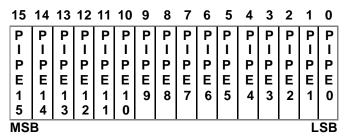

The Pending Interrupt Register (PI)

The Pending Interrupt Register (PI) contains information on pending interrupts attempting to vector the Instruction Counter Register (IC) to a new location. Software or hardware controls the PI. Any system interrupt, when active, sets the corresponding bit in the PI. RISC I/O instructions can also set, clear, and read the PI (figure 14).

| 15          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Р           | М | ı | F | F | Е | F | Т | I | Т | ı | 1 | I | I | I | I |

| W           | С | Ν | L | ı | X | L | 1 | Ν | ı | Ν | Ν | 0 | Ν | 0 | N |

| D           | Н | Т | Р | Р | С | Р | М | Т | М | Т | Т | L | Т | L | Т |

| P<br>W<br>D | Ε | 0 | 0 | 0 | L | U | Α | 1 | В | 2 | 3 | 1 | 4 | 2 | 5 |

Figure 14. The Pending Interrupt Register (PI)

**LSB**

### The Fault Register (FT)

**MSB**

**MSB**

The UT1750AR uses the Fault Register (FT) (figure 15) to indicate the occurrence of a machine-error fault. A machineerror fault cannot be disabled. The UT1750AR uses the logical OR combination of the 16 FT bits to generate the Machine Error interrupt, bit 14 of the PI. Any bits in the FT the UT1750AR does not use are set to a logic zero. The UT1750AR reads, loads, and clears the FT with RISC I/O instructions. The configuration of the FT is shown in figure 15.

#### 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

| MEM PARITY I/O |  | EGAL R<br>TRUC-<br>N AND<br>D FAULT S | BUILT-<br>IN-<br>TEST |

|----------------|--|---------------------------------------|-----------------------|

|----------------|--|---------------------------------------|-----------------------|

**LSB**

Figure 15. The Fault Register (FT)

Bit Definitions

| BIT<br>NUMBER | MNEMONIC | DESCRIPTION                                                                                                                                     |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | CMPF     | CPU Memory Protect Fault. This bit indicates the UT1750AR has detected an access fault, write-protect fault, or an execute-protect fault. [0]   |

| 14            | DMPF     | DMA Memory Protect Fault.<br>This bit indicates a DMA<br>device has detected an access<br>fault or a write-protect fault.<br>[0]                |

| 13            | MPF      | Memory Parity Fault. [0]                                                                                                                        |

| 12            | PCPF     | Parallel I/O (PIO) Channel<br>Parity Fault. [0] No user<br>access.                                                                              |

| 11            | DCPF     | DMA Channel Parity Fault. [0] No user access.                                                                                                   |

| 10            | ICF      | Illegal Command Fault. This bit indicates an attempt to execute an unimplemented or reserved I/O command. [0]                                   |

| 9             | PTF      | PIO Transmission Fault. Can wire-OR I/O error-checking devices together and feed ther into this input to indicate an error. [0] No user access. |

| 8             | SYSFLT   | System Fault. [0]                                                                                                                               |

| 7             | IAF      | Illegal Address Fault. This bi<br>indicates addressing a memor<br>location not physically<br>present. [0]                                       |

| 6             | IIF      | Illegal Instruction Fault. This bit indicates an attempt to execute a reserved code. [0]                                                        |

| 5             | PIF      | Privileged Instruction Fault.                                                                                                                   |

|               |          | This bit indicates an attempt to execute a privileged instruction with the Processo State not equal to zero. [0]                                |

| 4             | ASF      | Address State Fault. This bit indicates an attempt to establish an Address State                                                                |

value for an unimplemented page register set. [0]

| 3     |      | Reserved.                                                                                             |

|-------|------|-------------------------------------------------------------------------------------------------------|

| 2     | BITF | Built-In-Test Fault. This bit indicates the UT1750AR has detected a hardware built-in-test error. [0] |

| 1 - 0 |      | Spare BIT. The user defines these bits as additional BIT parameters. [0]                              |

|       |      |                                                                                                       |

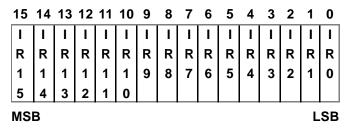

#### The Interrupt Mask Register (MK)

The Interrupt Mask Register (MK) (figure 16) contains one mask bit for each of the 16 system interrupts. All bits in the MK are set or reset under software control, although setting bits 15 and 10, Power Down Interrupt and Executive Call respectively, has no effect on the UT1750AR's operation because these interrupts cannot be masked. The UT1750AR reads or loads the MK with RISC I/O instructions.

Figure 16. The Interrupt Mask Register (MK)

The 1750 Status Word Register (SW)

15 14 12 12 11 10 0 0

The MIL-STD-1750A Instruction Set Architecture (ISA) defines the Status Word Register (SW). The UT1750AR reads and loads the SW with RISC I/O instructions. Figure 17 shows the definitions of various bits in the SW.

| CONDITION<br>STATUS<br>(CS) | PROCESSOI<br>STATE<br>(PS) |     |

|-----------------------------|----------------------------|-----|

| MSB                         | <b>!</b>                   | LSB |

Figure 17. The 1750 Status Register (SW)

| Bit Definition | Bit Definitions BIT |                                                                                                                                                              |  |  |  |  |  |  |

|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NUMBER         | MNEMONIC            | DESCRIPTION                                                                                                                                                  |  |  |  |  |  |  |

| 15             | С                   | Carry. This bit is set if the result of an addition operation generates a carry or if the result of a subtraction generates no borrow.                       |  |  |  |  |  |  |

| 14             | P                   | Positive. This bit is set if the result of an operation is greater than zero.                                                                                |  |  |  |  |  |  |

| 13             | Z                   | Zero. This bit is set if the result of an operation is equal to zero.                                                                                        |  |  |  |  |  |  |

| 12             | N                   | Negative. This bit is set if the result of an operation is less than zero.                                                                                   |  |  |  |  |  |  |

| 11 - 8         |                     | Reserved Bits.                                                                                                                                               |  |  |  |  |  |  |

| 7 - 4          | PS3 -               | Processor State. This PS0four<br>bit field determinesthe legal<br>illegal criteriafor privileged<br>instructions.                                            |  |  |  |  |  |  |

| 3 - 0          | AS3 -               | Address State. Used in AS0 conjunction with the optional UT1750 MMUMemory Management Unit, this four-bit field determines the current extended address page. |  |  |  |  |  |  |

Note: If condition codes are turned on (default after reset) the condition codes reflect the corresponding bits in the STATUS register.

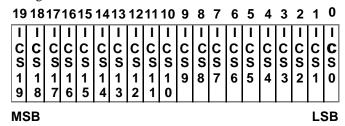

The RISC Instruction Counter Register (IC) and The RISC Instruction Register (IR)

The UT1750AR's RISC interface consists of a 20-bit instruction address and a 16-bit data bus. The RISC Instruction Counter Register (IC) supplies the 20-bit address to RISC memory. The RISC's instruction data that is read from memory is then input into the RISC's Instruction Register (IR). The IR consists of two sets of latches, a Primary Instruction Register latch (PIR) and the Instruction Register latch (IRL). These two sets of latches allow the UT1750AR to perform overlapping memory fetch and execute cycles. This means the UT1750AR performs a delayed branch when the flow of the program is interrupted. A delayed branch implies that the UT1750AR fetches and executes the instruction following the branch condition BEFORE the UT1750AR executes the first instruction at the branch location.

Figure 18. RISC Instruction Counter Register (IC)

The RISC Instruction Register (IR) is made of two 16-bit latches: the Primary Instruction Register (PIR) latch, and the Instruction Register (IRL) latch.

Figure 19. Instruction Register (IR)

The RISC Instruction Counter Save Register (ICS)

The UT1750AR uses the RISC's Instruction Counter Save

Register (ICS) (figure 20) when servicing interrupts and branch

instructions. When an interrupt or branch occurs, the

UT1750AR saves the IC in the ICS. Read the ICS

IMMEDIATELY after entering the target routine so the return

location can be stored before any other IC saves. The UT1750AR reads the ICS using the RISC Input instruction. The configuration of the ICS is shown below.

Figure 20. RISC Instruction Counter Save Register (ICS)

Pipe Register (PIPE)

The PIPE Register (figure 21) holds the pre-fetched MIL-STD-1750A instruction. The UT1750AR reads the PIPE Register with the RISC I/O instruction.

Figure 21. The PIPE Register (PIPE)

Program Register (PR)

The Program Register holds the present MIL-STD-1750A instruction. Figure 22 shows the configuration of the Program Register (PR).

Figure 22. Program Register (PR)

Program Counter Register (PC)

The Program Counter Register (PC) (figure 23) contains the 16-bit address for the present MIL-STD-1750A instruction. The RISC I/O instruction reads from or writes to the PC.

Figure 23. The Program Counter Register (PC)

1750 Timer A (TA) and 1750 Timer B (TB)

The Timer A (TA) and Timer B (TB) registers, figures 24a and 24b respectively, are 16-bit binary counters as defined by MIL-STD-1750A. The RISC I/O instruction starts, halts, reads, and loads them. When one of the timers reaches its programmed time setting, such as going from FFFFH to 0000H, a timeout occurs. This timeout sets the appropriate bit in the Pending Interrupt Register (PI).

Figure 24a. 1750 Timer A (TA)

Figure 24b. 1750 Timer B (TB)

#### SYSTEM INTERFACE

The System Interface describes how the Instruction and Operand address and data busses operate during the UT1750AR's many machine cycles and bus operations. The discussion about the UT1750AR's machine cycles and bus operations applies to both the RISC mode and the MIL-STD-1750A mode of operation, since in the 1750 mode of operation the UT1750AR executes a specialized set of RISC macros that allow the UT1750AR to emulate the MIL-STD-1750A Instruction Set Architecture.

The UT1750AR has the following seven types of machine operations or bus cycle operations:

- Data Bus Cycle Operation

- DMA Operation and Bus Arbitration

- Interrupt Operation and Exception Handling

- RISC Instruction Bus Cycle Operation

- Internal UART Operation

- Console Mode of Operation

- 1750 Instruction Memory Mapping

### **Operand Bus and Instruction Bus Interfaces**

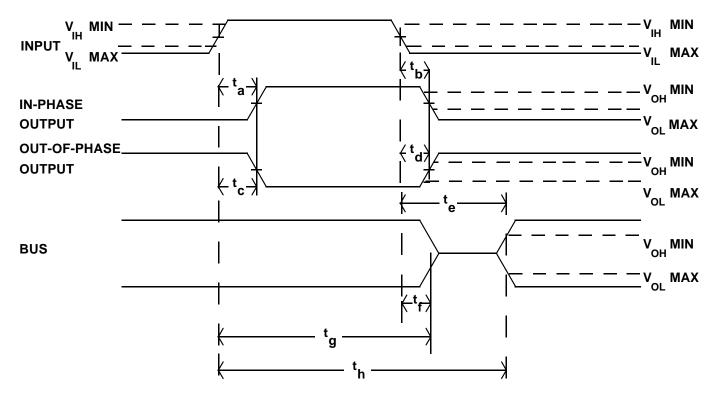

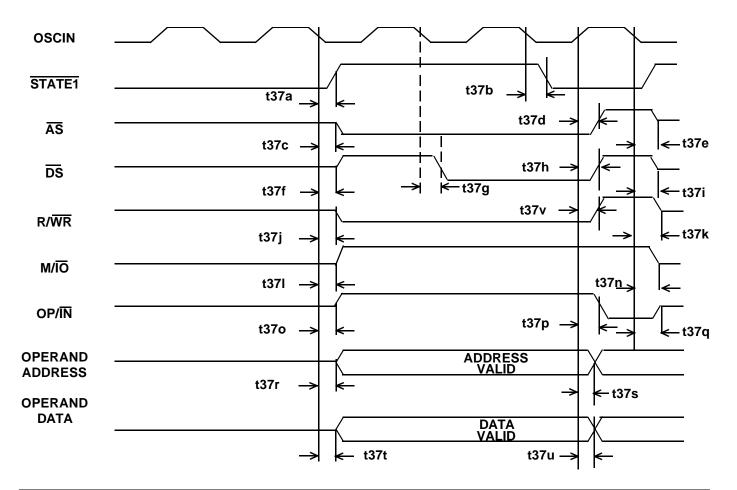

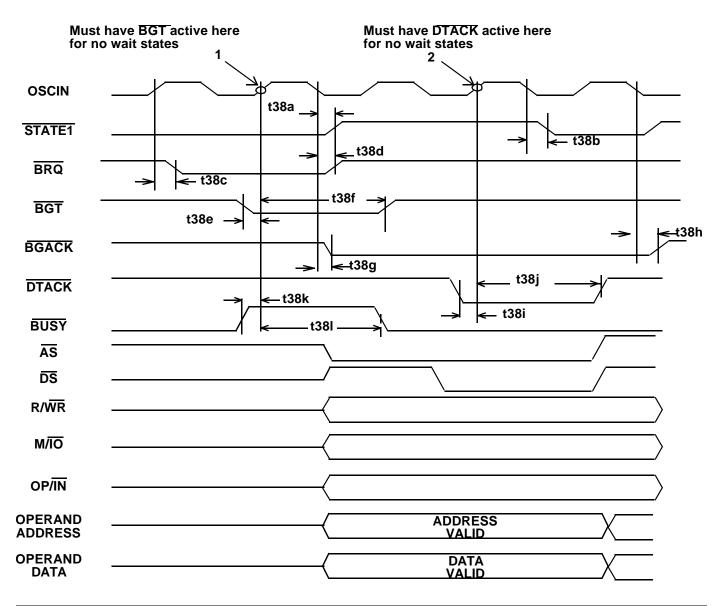

The UT1750AR Operand Data Bus interface supports multiple processor and Direct Memory Access (DMA) configurations. The Operand Address Bus (A15-A0), Data Bus (D15-D0), and memory control bus signals ( $\overline{AS}$ ,  $\overline{DS}$ ,  $R/\overline{WR}$ ,  $M/\overline{IO}$ , and  $OP/\overline{IN}$ ) are TTL-compatible signals that may be placed in a high-impedance state. These signals are only active during bus cycles when the UT1750AR is the current bus master. On other bus cycles, these signals enter a high-impedance state so an alternate bus master can control the busses.

The four signals that make up the Arbitration Control Bus -- Bus Request ( $\overline{BRQ}$ ), Bus Grant ( $\overline{BGNT}$ ), Bus Busy ( $\overline{BUSY}$ ), and Bus Grant Acknowledge ( $\overline{BGACK}$ ) -- control the UT1750AR's Operand Data Bus arbitration process. The arbitration process allows asynchronous bus arbitration.

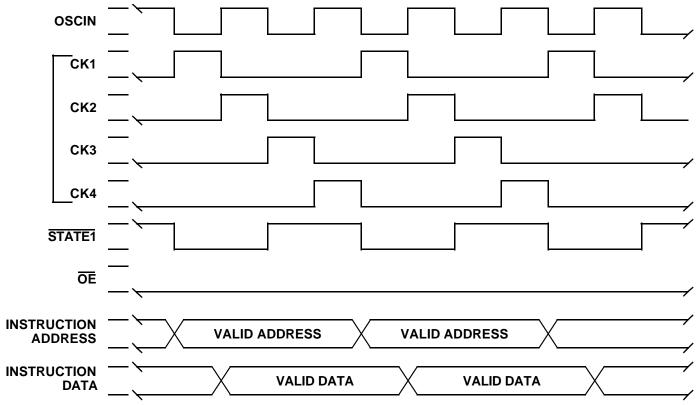

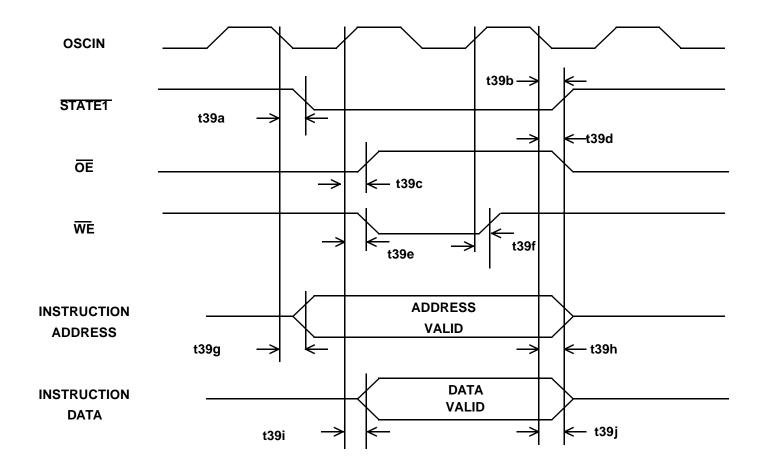

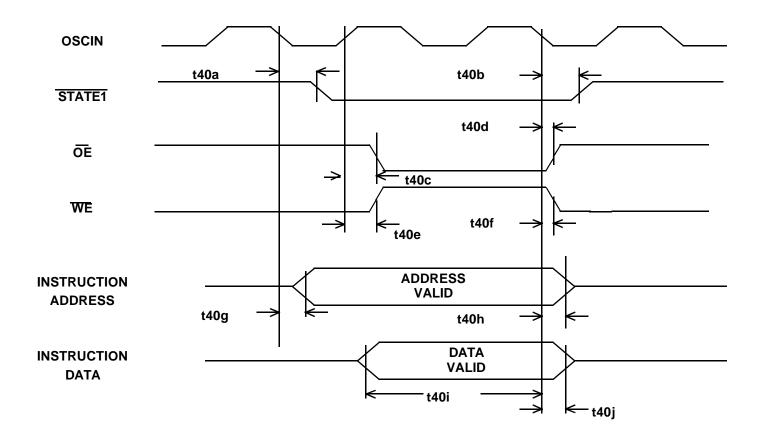

The Instruction Bus does not allow any type of bus arbitration. The UT1750AR is the only device permitted to access Instruction memory; this access is generally confined to reading RISC instructions the UT1750AR subsequently executes, although the RISC instruction set does provide one instruction the UT1750AR uses to alter RISC memory. This instruction is the Store Register to Instruction Memory (STRI).

The Instruction address and data busses only enter a high-impedance state when the  $\overline{TEST}$  input is low.

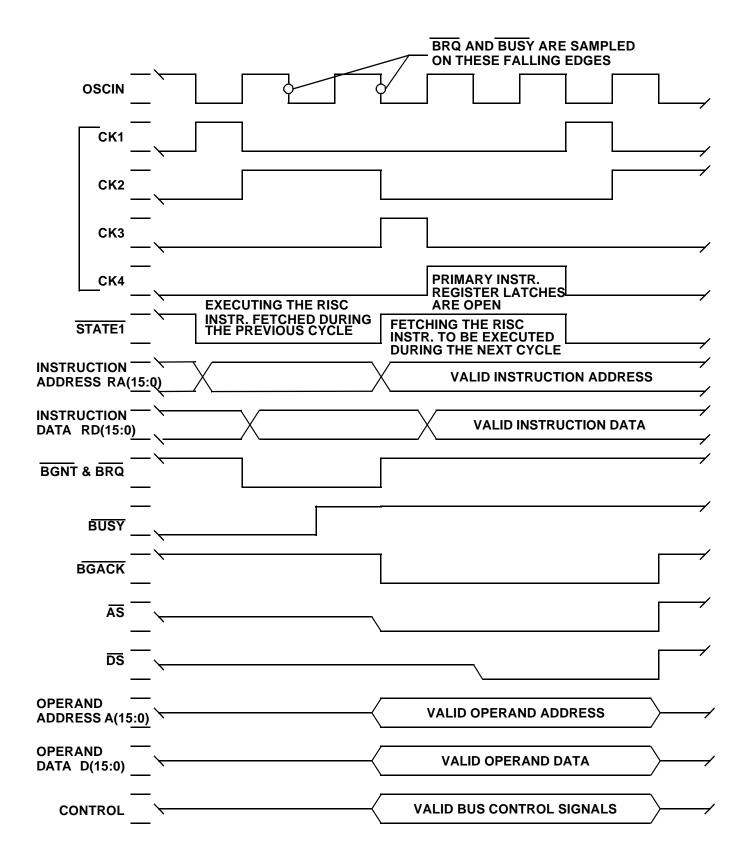

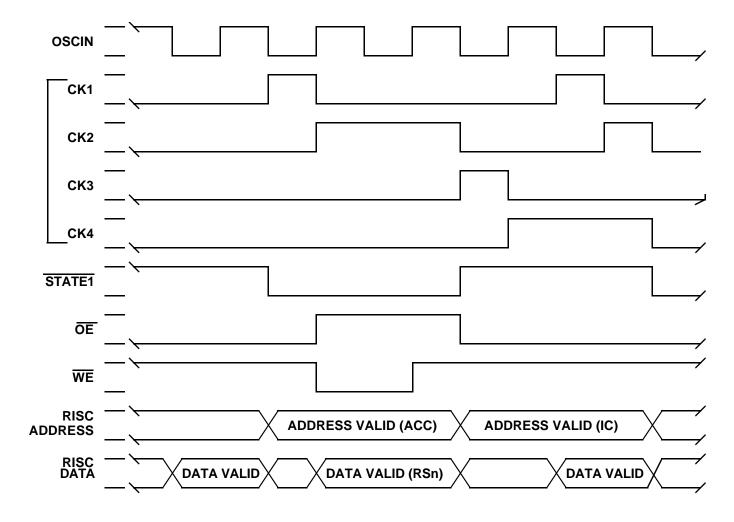

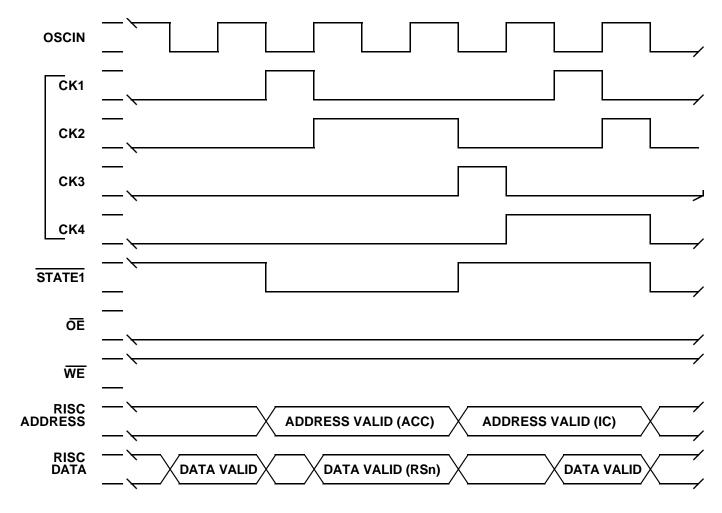

### A TYPICAL UT1750AR BUS CYCLE

Figure 25a (see page 21), a generalized diagram for a typical UT1750AR bus cycle, shows the UT1750AR's bus cycle separated into four distinct time periods (CK1 through CK4). These time periods are based on the processor clock. The UT1750AR performs a separate function during each of these four time periods.

Figure 25a. Typical UT1750AR Bus Cycle With Extended Clock Cycles

Figure 25b. Typical UT1750AR Bus Cycle

During the time period CK1, the UT1750AR begins executing the instruction in the Primary Instruction Register (PIR). The instruction executed is the instruction the UT1750AR fetched during the previous bus cycle, thus the overlapping fetch and execute cycles of the UT1750AR. During CK1, the RISC address for the next instruction to fetch from memory becomes valid. Also, the STATE1 output goes low, indicating the UT1750AR is executing an instruction.

At the beginning of time period CK2, the data addressed during CK1 becomes valid. The following conditions extend time period CK2 one clock cycle: (1) Executing a STRI instruction, (2) Executing a LRI instruction, or (3) Executing any instruction with Long Immediate data. The UT1750AR also extends clock period CK2 because of the Operand bus arbitration process. The UT1750AR samples the logical AND combination of the Bus Busy ( $\overline{BUSY}$ ) and Bus Grant ( $\overline{BGNT}$ ) inverted on the falling edge of CK2. If this combination is low during the falling edge of CK2, time period CK2 extends until the combination of the two signals is high, indicating the UT1750AR now controls the Operand busses. The  $\overline{STATE1}$  output remains low for the entire CK2 time period.