UCC1888 UCC2888 UCC3888

# Off-line Power Supply Controller

# **FEATURES**

- Transformerless Off-line Power Supply

- Wide 100VDC to 400VDC Allowable Input Range

- Fixed 5VDC or Adjustable Low Voltage Output

- Output Sinks 200mA, Sources 150mA Into a MOSFET Gate

- Uses Low Cost SMD Inductors

- Short Circuit Protected

- Optional Isolation Capability

# **DESCRIPTION**

The UCC3888 controller is optimized for use as an off-line, low power, low voltage, regulated bias supply. The unique circuit topology utilized in this device can be visualized as two cascaded flyback converters, each operating in the discontinuous mode, both driven from a single external power switch. The significant benefit of this approach is the ability to achieve voltage conversion ratios as high as 400V to 2.7V with no transformer and low internal losses.

The control algorithm utilized by the UCC3888 sets the switch on time inversely proportional to the input line voltage and sets the switch off time inversely proportional to the output voltage. This action is automatically controlled by an internal feedback loop and reference. The cascaded configuration allows a voltage conversion from 400V to 2.7V to be achieved with a switch duty cycle of 7.6%. This topology also offers inherent short circuit protection since as the output voltage falls to zero, the switch off time approaches infinity.

The output voltage is set internally to 5V. It can be programmed for other output voltages with two external resistors. An isolated version can be achieved with this topology as described further in Unitrode Application Note U-149.

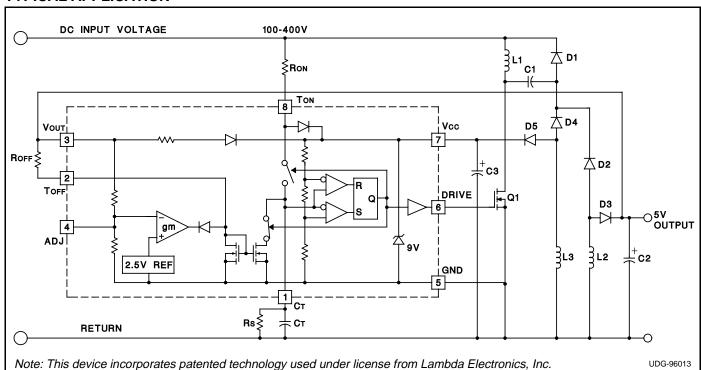

#### **OPERATION**

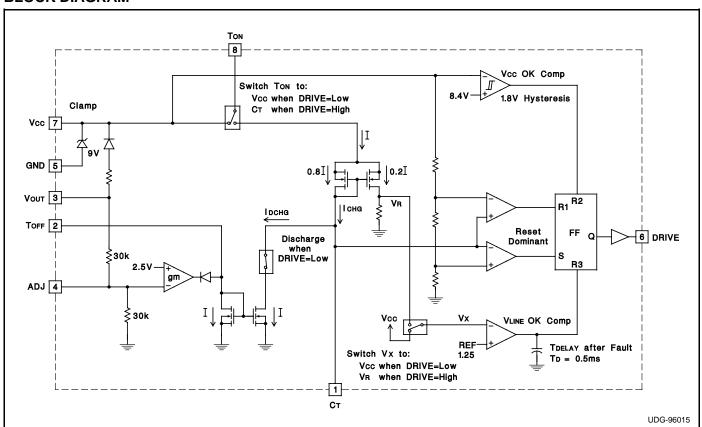

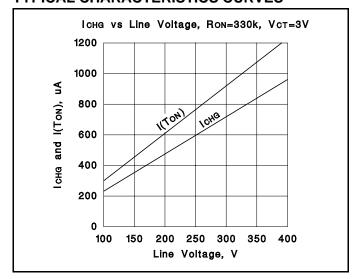

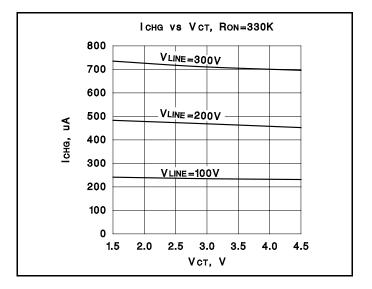

With reference to the application diagram below, when input voltage is first applied, the current through Ron into Ton is directed to VCC where it charges the external capacitor, C3, connected to VCC. As voltage builds on VCC, an internal undervoltage lockout holds the circuit off and the output at DRIVE low until VCC reaches 8.4V. At this time, DRIVE goes high turning on the power switch, Q1, and redirecting the current into Ton to the timing capacitor, CT. CT charges to a fixed threshold with a current ICHG=0.8 • (VIN - 4.5V)/Ron. Since DRIVE will only be high for as long as CT charges, the power switch on time will be inversely proportional to line voltage. This provides a constant (line voltage) • (switch on time) product.

#### TYPICAL APPLICATION

# **OPERATION** (cont.)

At the end of the on time, Q1 is turned off and the current through RON is again diverted to VCC. Thus the current through RON, which charges CT during the on time, contributes to supplying power to the chip during the off time.

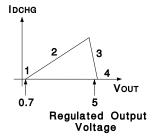

The power switch off time is controlled by the discharge of CT which, in turn, is programmed by the regulated output voltage. The relationship between CT discharge current, IDCHG, and output voltage is illustrated as follows:

Region 1. When Vout = 0, the off time is infinite. This feature provides inherent short circuit protection. However, to ensure output voltage startup when the output is not a short, a high value resistor, Rs, is placed in parallel with Ct to establish a minimum switching frequency.

Region 2. As VOUT rises above approximately 0.7V to its regulated value, IDCHG is defined by ROFF, and is equal to:

As Vout increases, IDCHG increases reducing off time. The operating frequency increases and Vout rises quickly to its regulated value.

Region 3. In this region, a transconductance amplifier reduces IDCHG in order to maintain a regulated VOUT.

Region 4. If Vout should rise above its regulation range, IDCHG falls to zero and the circuit returns to the minimum frequency established by Rs and Ct.

The range of switching frequencies is established by Ron, Roff, Rs, and CT as follows:

Toff = Roff • CT • 3.7V /(Vout - 0.7V)

Region 2, excluding the effects of Rs

which have a minimal impact on Toff.

The above equations assume that VCC equals 9V. The voltage at TON increases from approximately 2.5V to 6.5V while CT is charging. To take this into account, VIN is adjusted by 4.5V in the calculation of TON. The voltage at TOFF is approximately 0.7V.

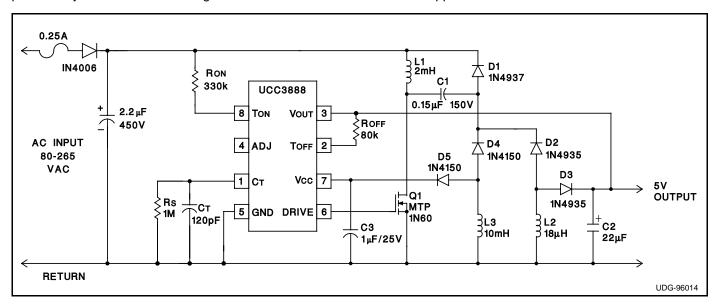

#### **DESIGN EXAMPLE**

The UCC3888 regulates a 5 volt, 1 Watt nonisolated DC output from AC inputs between 80 and 265 volts. In this example, the IC is programmed to deliver a maximum on time gate drive pulse width of 2.2 microseconds which occurs at 80 VAC. The corresponding switching frequency is approximately 100kHz at low line, and overall efficiency is approximately 50%. Additional design information is available in Unitrode Application Note U-149.

# **ABSOLUTE MAXIMUM RATINGS**

| lcc 8mA                                                            |

|--------------------------------------------------------------------|

| Current into Ton Pin                                               |

| Voltage on Vout Pin                                                |

| Current into Toff Pin                                              |

| Storage Temperature65°C to +150°C                                  |

| Note: Unless otherwise indicated, voltages are referenced to       |

| ground and currents are positive into, negative out of, the speci- |

| fied terminals                                                     |

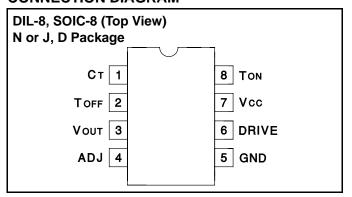

# **CONNECTION DIAGRAM**

**ELECTRICAL CHARACTERISTICS** Unless otherwise stated, these specifications hold for TA = 0°C to 70°C for the UCC3888, -40°C to +85°C for the UCC2888, and -55°C to +125°C for the UCC1888. No load at DRIVE pin (CLOAD=0).

| PARAMETER                             | TEST CONDITIONS                      | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------|--------------------------------------|------|------|------|-------|

| General                               |                                      |      |      |      |       |

| Vcc Zener Voltage                     | Icc < 1.5mA                          | 8.6  | 9.0  | 9.3  | V     |

| Startup Current                       | Vout = 0                             |      | 150  | 250  | μΑ    |

| Operating Current I(Vcc)              | Vcc = Vcc(zener) - 100mV, F = 150kHz |      | 1.2  | 2.5  | mA    |

| Under-Voltage-Lockout                 |                                      |      |      |      |       |

| Start Threshold                       | Vout = 0                             | 8.0  | 8.4  | 8.8  | V     |

| Minimum Operating Voltage after Start | Vout = 0                             | 6.0  | 6.3  | 6.6  | V     |

| Hysteresis                            | Vout = 0                             | 1.8  |      |      | V     |

| Oscillator                            |                                      |      |      |      |       |

| Amplitude                             | Vcc = 9V                             | 3.5  | 3.7  | 3.9  | V     |

| Ст to DRIVE high Propagation Delay    | Overdrive = 0.2V                     |      | 100  | 200  | ns    |

| Ст to DRIVE low Propagation Delay     | Overdrive = 0.2V                     |      | 50   | 100  | ns    |

| Driver                                |                                      |      |      |      |       |

| VOL                                   | I = 20mA, Vcc = 9V                   |      | 0.15 | 0.4  | V     |

|                                       | I = 100mA, Vcc = 9V                  |      | 0.7  | 1.8  | V     |

| VOH                                   | I = -20mA, Vcc = 9V                  | 8.5  | 8.8  |      | V     |

|                                       | I = -100mA, Vcc = 9V                 | 6.1  | 7.8  |      | V     |

| Rise Time                             | CLOAD = 1nF                          |      | 35   | 70   | ns    |

| Fall Time                             | CLOAD = 1nF                          |      | 30   | 60   | ns    |

| Line Voltage Detection                |                                      |      |      |      |       |

| Charge Coefficient: ICHG / I(TON)     | VCT = 3V, DRIVE = High, I(Ton) = 1mA | 0.73 | 0.79 | 0.85 |       |

| Minimum Line Voltage for Fault        | Ron = 330k                           | 60   | 80   | 100  | V     |

| Minimum Current I(TON) for Fault      | Ron = 330k                           |      | 220  |      | μΑ    |

| On Time During Fault                  | CT = 150pF, $VLINE = Min - 1V$       |      | 2    |      | μs    |

| Oscillator Restart Delay after Fault  |                                      |      | 0.5  |      | ms    |

| Vout Error Amp                        |                                      |      |      |      |       |

| Vout Regulated 5V (ADJ Open)          | Vcc = 9V, IDCHG = I(TOFF)/2          | 4.5  | 5.0  | 5.5  | V     |

| Discharge Ratio: IDCHG / I(TOFF)      | $I(TOFF) = 50\mu A$                  | 0.93 | 1.00 | 1.07 |       |

| Voltage at Toff                       | $I(TOFF) = 50\mu A$                  | 0.6  | 0.95 | 1.3  | V     |

| Regulation gm (Note 1)                | Max IDCHG = 50μA                     |      | 2.4  |      | mA/V  |

|                                       | Max IDCHG = 125μA                    | 1.9  | 4.1  | 7.0  | mA/V  |

Note 1: gm is defined as  $\frac{\Delta \text{IDCHG}}{\Delta \text{VOUT}}$  for the values of VOUT when VOUT is in regulation. The two points used to calculate gm are for IDCHG at 65% and 35% of its maximum value.

#### PIN DESCRIPTIONS

**ADJ:** The ADJ pin is used to provide a 5V regulated supply without additional external components. Other output voltages can be obtained by connecting a resistor divider between Vout, ADJ and GND. Use the formula

$$VOUT = 2.5V \bullet \frac{R1 + R2}{R2}$$

where R1 is connected between VouT and ADJ, and R2 is connected between ADJ and GND. R1  $\parallel$  R2 should be less than 1k $\Omega$  to minimize the effect of the temperature coefficient of the internal 30k resistors which also connect to VouT, ADJ, and GND. See Block Diagram.

**CT (timing capacitor):** The signal voltage at CT has a peak-to-peak swing of 3.7V for 9V VCC. As the voltage at CT crosses the oscillator upper threshold, DRIVE goes low. As the voltage on CT crosses the oscillator lower threshold, DRIVE goes high.

**DRIVE:** This output is a CMOS stage capable of sinking 200mA peak and sourcing 150mA peak. The output voltage swing is 0 to VCC.

**GND (chip ground):** All voltages are measured with respect to GND.

**Toff (regulated output control):** Toff sets the discharge current of the timing capacitor through an external resistor connected between Vout and Toff.

**TON (line voltage control):** TON serves three functions. When CT is discharging (off time), the current through TON is routed to VCC. When CT is charging (on time), the current through TON is split 80% to set the CT charge time and 20% to sense minimum line voltage which occurs for a TON current of  $220\mu A$ . For a minimum line voltage of 80V, RON is  $330k\Omega$ .

The CT voltage slightly affects the value of the charge current during the on time. During this time, the voltage at the Ton pin increases from 2.5V to 6.5V.

Vcc (chip supply voltage): The supply voltage of the device at pin Vcc is internally clamped at 9V. The device needs an external supply, from a source such as the rectified AC line or derived from the switching circuit. Precautions must be taken to ensure that total Icc does not exceed 8mA.

**Vout (regulated output):** The Vout pin is directly connected to the power supply output voltage. When Vout is greater than Vcc, Vout bootstraps Vcc.

### **BLOCK DIAGRAM**

# **TYPICAL CHARACTERISTICS CURVES**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated