# VR4310 64-Bit MIPS RISC Microprocessor for Windows CE

Product Brief February 1998

## **Description**

The 64-bit VR4310<sup>™</sup> (µPD30210) RISC microprocessor is one of NEC's VR Series<sup>™</sup> families supporting Windows® CE-based embedded consumer applications. Designed around the popular MIPS® architecture, the VR4310 processor has an internal operating frequency of either 100 MHz, 133 MHz, or 167 MHz at 3.3 volts. Its CPU has an optimized five-stage pipeline, 16K instruction cache, 8K data cache, memory management unit, floating-point arithmetic unit (FPU), and clock generator, and is compatible with MIPS I, II, and III instruction set architectures (ISAs). Based on the advanced 0.28-micron (drawn) process technology, the VR4310 uses 50% of the power that its predecessor, the VR4300<sup>™</sup>, uses at the same frequency. The VR4310 is also one of the most powerful processors available to support Windows CE, which makes it ideal for many performance-intensive tethered applications.

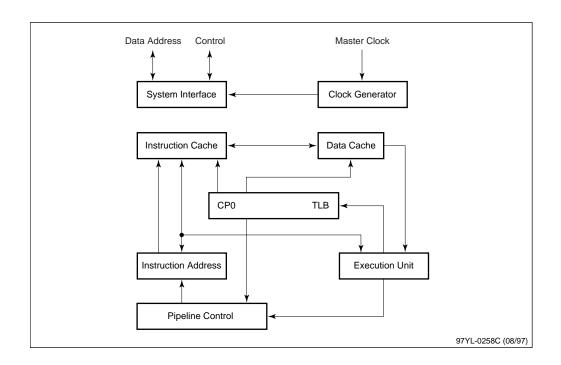

# **Block Diagram**

#### **Ordering Information**

| Part Number        | Operating Frequency | Package                          |

|--------------------|---------------------|----------------------------------|

| μPD30210GD-100-MBB | 100 MHz             | 120-pin plastic QFP (28 x 28 mm) |

| μPD30210GD-133-MBB | 133 MHz             | _                                |

| μPD30210GD-167-MBB | 167 MHz             | _                                |

|                                | 64-bit register file                                                                                                                                                       |       |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|

| C                              | 64-bit integer/mantissa data bus                                                                                                                                           |       |  |  |

| C                              | 12-bit exponent data bus                                                                                                                                                   |       |  |  |

| (                              | Coprocessor 0                                                                                                                                                              |       |  |  |

| C                              | Exception processing unit with system control coprocessor registers                                                                                                        |       |  |  |

|                                | Memory management unit that converts virtual addresses into physical a and verifies memory access of kernel, supervisor, and user memory see                               |       |  |  |

|                                | Seven page sizes: 4K, 16K, 64K, 256K, 1M, 4M, and 16M (VSIZE = 40 PSIZE = 32)                                                                                              | and   |  |  |

|                                | Translation lookaside buffer with 32 entries, each mapped to an even or frame buffer page                                                                                  | odd   |  |  |

| Pipeline Control               |                                                                                                                                                                            |       |  |  |

| C                              | Occurrence of cache misses                                                                                                                                                 |       |  |  |

| C                              | Flash buffer full                                                                                                                                                          |       |  |  |

| C                              | Multicycle instructions                                                                                                                                                    |       |  |  |

| C                              | Occurrence of system exceptions                                                                                                                                            |       |  |  |

| Floating-Point Arithmetic Unit |                                                                                                                                                                            |       |  |  |

| C                              | Integrated into CPU's integer arithmetic unit                                                                                                                              |       |  |  |

| C                              | Supports both 32-bit (single-precision) and 64-bit (double-precision) IEE floating-point arithmetic                                                                        | E 754 |  |  |

| Instruction Address            |                                                                                                                                                                            |       |  |  |

|                                | PC incrementer                                                                                                                                                             |       |  |  |

|                                | Branch address adder                                                                                                                                                       |       |  |  |

|                                | Conditional branch address selector                                                                                                                                        |       |  |  |

| 16K Instruction Cache          |                                                                                                                                                                            |       |  |  |

| C                              | Direct map                                                                                                                                                                 |       |  |  |

| C                              | Virtual index address                                                                                                                                                      |       |  |  |

|                                | Physical tag cache                                                                                                                                                         |       |  |  |

|                                | No hardware is provided to check generation of a cache alias due to virtual address. Each line consists of 8-word data, a 20-bit tag, and a valid line bit. The cache data |       |  |  |

interface is 64 bits wide. Cache parity is not supported.

**Execution Unit**

| BK               | Data Cache                                                                                                                                                                                                                                                                                 |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| _                | Direct map                                                                                                                                                                                                                                                                                 |  |  |

| _                | Virtual index address                                                                                                                                                                                                                                                                      |  |  |

| ⊐                | Physical tag write-back cache                                                                                                                                                                                                                                                              |  |  |

| oac<br>rea       | ch cache line consists of 4-word data, a 20-bit tag and valid line bit, and a write-ck bit and its bit parity. Two cache lines correspond to one physical line. Data is ad from the cache in one cycle and written to the cache in two cycles. Cache parity not supported.                 |  |  |

| Sy               | stem Interface                                                                                                                                                                                                                                                                             |  |  |

| ⊐                | Multiplexed 32-bit address/data bus                                                                                                                                                                                                                                                        |  |  |

| _                | Clock signal                                                                                                                                                                                                                                                                               |  |  |

| ⊐                | Interrupt request                                                                                                                                                                                                                                                                          |  |  |

| _                | Control signal                                                                                                                                                                                                                                                                             |  |  |

| Clo              | ock Generator                                                                                                                                                                                                                                                                              |  |  |

| Ge               | nerates four clocks from MasterClock input                                                                                                                                                                                                                                                 |  |  |

| ⊐                | PClock: frequency is set using DivMode(1.0) signals at cold reset                                                                                                                                                                                                                          |  |  |

| _                | SClock: system interface clock (internal)                                                                                                                                                                                                                                                  |  |  |

| <b>_</b>         | TClock: output clock reference for external agent; same frequency as MasterClock, except in low-power mode where operating frequency = one-fourth of normal. Low-power mode is set using the status register RP bit; PClock and SClock frequencies are dynamically switched by this means. |  |  |

|                  | e VR4310 uses a phase-locked loop (PLL) to suppress skew between the input<br>ck and internal clock.                                                                                                                                                                                       |  |  |

| High Performance |                                                                                                                                                                                                                                                                                            |  |  |

| _                | 60 SPECint92, 45 SPECfp92, 133 MIPS (100 MHz)                                                                                                                                                                                                                                              |  |  |

| ⊐                | 80 SPECint92, 60 SPECfp92, 176 MIPS (133 MHz)                                                                                                                                                                                                                                              |  |  |

| ⊐                | 100 SPECint92, 75 SPECfp92, 221MIPS (187 MHz)                                                                                                                                                                                                                                              |  |  |

| Lo               | w Power Consumption                                                                                                                                                                                                                                                                        |  |  |

| ⊐                | 0.9 W (typ.) at 100 MHz                                                                                                                                                                                                                                                                    |  |  |

| ⊐                | 1.2 W (typ.) at 133 MHz                                                                                                                                                                                                                                                                    |  |  |

|                  | 1.5 W (typ.) at 167 MHz                                                                                                                                                                                                                                                                    |  |  |

| Su               | pply Voltage                                                                                                                                                                                                                                                                               |  |  |

□ 3.3 volts ±10%

VR Series, VR4310, and VR4300 are either registered trademarks or trademarks of NEC Corporation in the United States and/or other countries. Windows and Windows CE are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries. MIPS is a registered trademark of the MIPS group, a division of Silicon Graphics, Inc.

For literature, call **1-800-366-9782** 7 a.m. to 6 p.m. Pacific time or FAX your request to **1-800-729-9288** or visit our web site at **www.nec.com**

## **NEC Electronics Inc.**

CORPORATE HEADQUARTERS 2880 Scott Boulevard Santa Clara, CA 95050-2554 TEL 408-588-6000 In North America: No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. All devices sold by NECEL are covered by the provisions appearing in NECEL Terms and Conditions of Sales only. Including the limitation of liability, warranty, and patent provisions. NECEL makes no warranty, express, statutory, implied or by description, regarding information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. "Standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliability requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or