# 9-LINE 3 TO 5 VOLT SCSI ACTIVE TERMINATOR, REVERSE DISCONNECT

#### **FEATURES**

- Complies with SCSI, SCSI-2 and SPI-2 Standards

- 2.7-V to 5.25-V Operation

- 1.8-pF Channel Capacitance during Disconnect

- 0.5-μA Supply Current in Disconnect Mode

- 110-Ω/2.5-kΩ Programmable Termination

- Completely Meets SCSI Hot Plugging

- -400-mA Sourcing Current for Termination

- +400-mA Sinking Current for Active Negation Drivers

- Trimmed Termination Current to 4%

- Trimmed Impedance to 7%

- Current Limit and Thermal Shutdown Protection

#### **DESCRIPTION**

The UCC5606 provides 9 lines of active termination for a small computer systems interface (SCSI) parallel bus. The SCSI standard recommends active termination at both ends of the cable segment.

The UCC5606 is ideal for high performance 3.3-V SCSI systems. The key features contributing to such low operating voltage are the 0.1-V drop out regulator and the 2.7-V reference. During disconnect the supply current is typically only 0.5  $\mu$ A, which makes the device attractive for battery powered systems.

The UCC5606 is designed with an ultra-low channel capacitance of 1.8 pF, which eliminates effects on signal integrity from disconnected terminators at interim points on the bus.

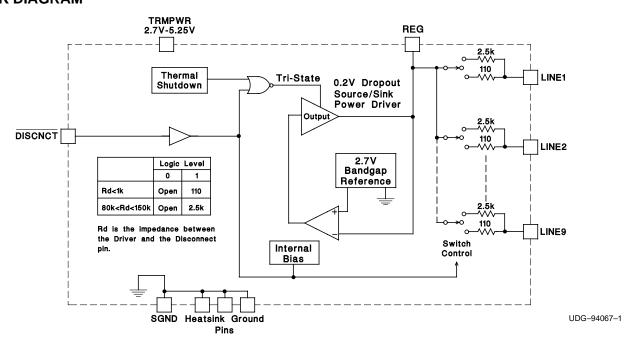

#### **BLOCK DIAGRAM**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION (CONTINUED)**

The UCC5606 can be programmed for either a 110- $\Omega$  or 2.5-k $\Omega$  termination. The 110- $\Omega$  termination is used for standard SCSI bus lengths and the 2.5-k $\Omega$  termination is typically used in short bus applications. When driving the TTL compatible  $\overline{\text{DISCNCT}}$  pin directly, the 110- $\Omega$  termination is connected when the  $\overline{\text{DISCNCT}}$  pin is driven high, and disconnected when low. When the  $\overline{\text{DISCNCT}}$  pin is driven through an impedance between 80 k $\Omega$  and 150 k $\Omega$ , the 2.5-k $\Omega$  termination is connected when the  $\overline{\text{DISCNCT}}$  pin is driven high, and disconnected when driven low.

The power amplifier output stage allows the UCC5606 to source full termination current and sink active negation current when all termination lines are actively negated.

The UCC5606 is pin-for-pin compatible with Unitrode's other 9-line single-ended SCSI terminators, except that  $\overline{\text{DISCNCT}}$  is now active low, allowing lower capacitance and lower voltage upgrades to existing systems. The UCC5606 is completely hot pluggable and appears as high impedance at the terminating channels with  $V_{\text{TRMPWR}} = 0 \text{ V}$  or open.

Internal circuit trimming is utilized, first to trim the 110- $\Omega$  termination impedance to a 7% tolerance, and then most importantly, to trim the output current to a 4% tolerance, as close to the maximum SCSI specification as possible, which maximizes noise margin in fast SCSI operation.

Other features include thermal shutdown and current limit.

This device is offered in low thermal resistance versions of the industry standard 16-pin narrow body SOIC, 16-pin N and 24-pin TSSOP.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted†‡

|                                                           | UCC5606    | UNIT |  |

|-----------------------------------------------------------|------------|------|--|

| TRMPWR voltage                                            | 7          | .,   |  |

| Signal line voltage                                       | 0 to 7     |      |  |

| Regulator output current                                  | 0.6        | А    |  |

| Storage temperature, T <sub>Stg</sub>                     | -65 to 150 |      |  |

| Operating junction temperature, T <sub>J</sub> -55 to 150 |            | °C   |  |

| Lead temperature (soldering, 10 sec.)                     | 300        |      |  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into and negative out of, the specified terminal.

#### RECOMMENDED OPERATING CONDITIONS

|                          | MIN | NOM MAX | UNIT |

|--------------------------|-----|---------|------|

| TRMPWR voltage           | 2.7 | 5.25    | V    |

| Signal line voltage      | 0   | 5       | V    |

| Disconnect input voltage | 0   | TRMPWR  | °C   |

#### ORDERING INFORMATION

|    | _           | DISCONNECT | PACKAGED DEVICE† |                |            |

|----|-------------|------------|------------------|----------------|------------|

| TA | STATUS      | DIL-16 (N) | SOIC-16 (DP)     | TSSOP-24 (PWP) |            |

|    | 0°C to 70°C |            | UCC5606N         | UCC5606DP      | UCC5606PWP |

<sup>†</sup> The LQFP packages are available taped and reeled. Add TR suffix to device type (e.g. UCC5606PWPTR) to order quantities of 2,500 devices per reel.

<sup>‡</sup> Currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages. All voltages are referenced to GND.

#### **CONNECTION DIAGRAM**

#### DIL-16 (Top View) SOIC-16 (Top View) TSSOP-24 (Top View) N Package **DP Package PWP Package** LINE7 1 24 LINE6 LINE7 1 16 LINE6 LINE7 1 16 LINE6 23 LINE5 LINE8 2 LINE8 2 15 LINE5 LINE8 2 15 LINE5 22 REG LINE9 3 21 REG LINE9 3 14 REG 14 REG N/C 4 LINE9 3 20 GND\* SGND\* 5 13 N/C N/C 4 GND\* 4 13 GND\* 19 GND\* GND\* 6 SGND 5 12 N/C GND\* 7 18 GND\* SGND\* 5 12 GND\* DISCNCT 6 11 TRMPWR GND\* 8 17 GND\* DISCNCT 6 11 TRMPWR 16 TRMPWR GND\* 9 LINE1 7 10 LINE4 15 TRMPWR DISCNCT 10 LINE2 8 9 LINE3 LINE1 7 10 LINE4 14 LINE4 LINE1 11 9 LINE3 LINE2 8 13 LINE3 LINE2 12

NOTE: GND\* serves as a heat sink ground which must be tied to a large copper area or the grounding plate.

## **ELECTRICAL CHARACTERISTICS**

$T_A = 0$ °C to 70°C, TRMPWR = 3.3 V,  $\overline{DISCNCT} = 3.3$  V,  $R_{DISCNCT} = 0$   $\Omega$ ,  $T_A = T_J$ , (unless otherwise noted)

| PARAMETER                                     | TEST CONDITIONS                                                    | MIN   | TYP   | MAX   | UNITS |  |

|-----------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|-------|--|

| Supply Current Section                        | ·                                                                  |       |       |       |       |  |

|                                               | All termination lines = open                                       |       | 1     | 2     |       |  |

| Termpwr supply current                        | All termination lines = 0.2 V                                      |       | 210   | 218   | mA    |  |

| Power down mode                               | DISCNCT = 0 V                                                      |       | 0.5   | 5.0   | μΑ    |  |

| Output Section (110 ohms – Terminate          | or Lines)                                                          |       |       |       |       |  |

| Terminator impedance                          |                                                                    | 102.3 | 110.0 | 117.7 | Ohms  |  |

| Output high voltage                           | TRMPWR = 3 V (1)                                                   | 2.5   | 2.7   | 3.0   | V     |  |

| Max output current                            | $V_{LINE} = 0.2 \text{ V}, \qquad T_{J} = 25^{\circ}\text{C}$      | -22.1 | -23.0 | -24.0 |       |  |

|                                               | V <sub>LINE</sub> = 0.2 V                                          | -21   | -23   | -24   |       |  |

|                                               | V <sub>LINE</sub> = 0.2 V, TRMPWR = 3 V, T <sub>J</sub> = 25°C (1) | -20.2 | -23.0 | -24.0 | mA    |  |

|                                               | $V_{LINE} = 0.2 \text{ V}, \qquad TRMPWR = 3 \text{ V} (1)$        | -19   | -23   | -24   |       |  |

|                                               | V <sub>LINE</sub> = 0.5 V                                          |       |       | -22.4 |       |  |

| Output leakage                                | DISCNCT = 0 V, TRMPWR = 0 V to 5.25 V                              |       | 10    | 400   | nA    |  |

| Output capacitance                            | DISCNCT = 0 V, DP package (2)                                      |       | 1.8   | 2.5   | pF    |  |

| Output Section (2.5 k $\Omega$ – Terminator L | ines) (RDISCNCT = 80 kΩ)                                           |       |       |       |       |  |

| Terminator impedance                          |                                                                    | 2.0   | 2.5   | 3.0   | kΩ    |  |

| Output high voltage                           | TRMPWR = 3 V (1)                                                   | 2.5   | 2.7   | 3.0   | V     |  |

| Max output current                            | V <sub>LINE</sub> = 0.2 V                                          | -0.7  | -1.0  | -1.4  | mA    |  |

|                                               | $V_{LINE} = 0.2 \text{ V}, \qquad TRMPWR = 3 \text{ V} (1)$        | -0.6  | -1.0  | -1.5  |       |  |

| Output leakage                                | DISCNCT = 0 V, TRMPWR = 0 to 5.25 V                                |       | 10    | 400   | nA    |  |

| Output capacitance                            | DISCNCT = 0 V, DP package (2)                                      |       | 1.8   | 2.5   | pF    |  |

| PARAMETER                   | TEST CONDITIONS                                               | MIN  | TYP  | MAX  | UNITS |  |

|-----------------------------|---------------------------------------------------------------|------|------|------|-------|--|

| Regulator Section           | Regulator Section                                             |      |      |      |       |  |

| Regulator output voltage    | 5.25 V > TRMPWR > 3 V                                         | 2.5  | 2.7  | 3.0  | V     |  |

| Drop-out voltage            | All termination lines = 0.2 V                                 |      | 0.1  | 0.2  |       |  |

| Short circuit current       | V <sub>REG</sub> = 0 V                                        | -200 | -400 | -800 | mA    |  |

| Sinking current capability  | V <sub>REG</sub> = 3 V                                        | 200  | 400  | 800  |       |  |

| Thermal shutdown            | (2)                                                           |      | 170  |      | °C    |  |

| Thermal shutdown hysteresis | (2)                                                           |      | 10   |      |       |  |

| Disconnect Section          |                                                               |      |      |      |       |  |

| Disconnect threshold        | RDISCNCT = $0 \text{ k}\Omega \text{ to } 80 \text{ k}\Omega$ | 0.8  | 1.5  | 2.0  | V     |  |

| Input current               | DISCNCT = 3.3 V                                               |      | 30   | 50   | μΑ    |  |

NOTES: 1. Measuring each termination line while other eight are low (0.2 V).

2. Ensured by design. Not production tested.

## **TERMINAL FUNCTIONS**

| TERM              | ERMINAL |     | DECORPTION                                                                                                                                                                                                                                                                                   |  |  |

|-------------------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME              | NO.     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                  |  |  |

| DISCNCT           | 7       | I   | Taking this pin low causes the 9 channels to become high impedance and the chip to go into low power mode. In short laptop buses an $80$ -k $\Omega$ to $150$ -k $\Omega$ resister to TERPWR terminates the bus at 2.5 k $\Omega$ . Less than 110 $\Omega$ to TERPWR enables the terminator. |  |  |

| GND               | 9       |     | Ground reference for the device                                                                                                                                                                                                                                                              |  |  |

| LINE1 TO<br>LINE9 | 4       | I   | 110- $\Omega$ termination channels                                                                                                                                                                                                                                                           |  |  |

| REG               | 9       | I   | Output of the internal 2.7-V regulator                                                                                                                                                                                                                                                       |  |  |

| TRMPWR            | 4       |     | Power for the device                                                                                                                                                                                                                                                                         |  |  |

| GND*              |         |     | Heat sink ground, must be tied to a large copper area or the grounding plate.                                                                                                                                                                                                                |  |  |

## **APPLICATION INFORMATION**

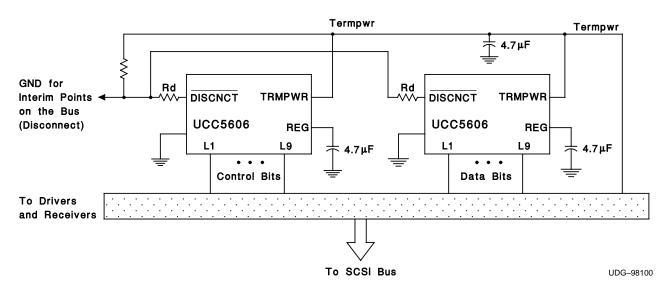

Figure 1. Typical SCSI Bus Configurations Utilizing two UCC5606 Devices

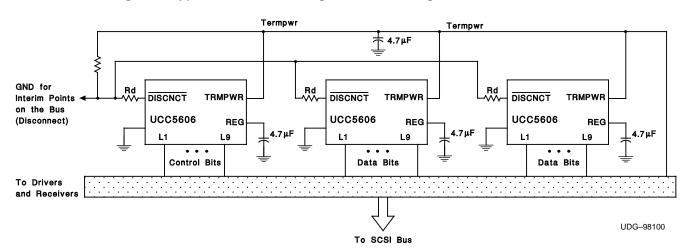

Figure 2. Typical Wide SCSI Bus Configurations Utilizing three UCC5606 Devices

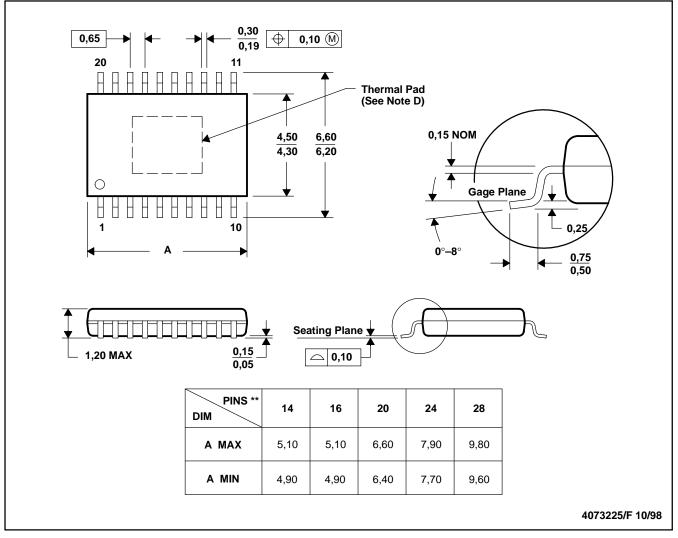

## **MECHANICAL DATA**

## PWP (R-PDSO-G\*\*)

## **PowerPAD™ PLASTIC SMALL-OUTLINE**

#### **20 PINS SHOWN**

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusions.

D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

E. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated