# CMOS-8LCX 3-VOLT, 0.50-MICRON CMOS GATE ARRAYS CROSSCHECK TEST SUPPORT

October 1993

#### Description

NEC's 3-volt CMOS-8LCX family consists of ultra-high performance, sub-micron gate arrays, targeted for applications requiring extensive integration and high speeds. The device processing includes a true 3-volt, 0.5-micron (drawn) silicon-gate CMOS technology and three-layer metalization. This technology features channelless (sea-of-gates) architecture with an internal gate delay of 131 ps (F/O = 1; L = 0 mm).

The  $\mu$ PD658xx series of 3-volt CrossCheck<sup>®</sup>-supported devices consists of 10 masters, offered in densities of 10K gates to 486K gates. Usable gates range from 32K gates to 389K gates. These gate arrays are ideal for use in engineering workstations, high-end PCs, mainframes and LAN products, where extensive integration and high speed are primary design goals. CMOS-8LCX gate arrays are also well-suited for all battery-operated applications where high performance and low power consumption are critical; and feasible only with a truly optimized 3-volt CMOS process.

#### Features

- □ Supports CrossCheck on-chip testability circuitry

- □ Internal gate delays of 131 ps (F/O = 1; L = 0 mm)

- □ Channelless, 0.50 µm CMOS architecture

- □ Power (typ.) = 1.24 (3.3V) = 0.80 (3.0V)

- Process technology designed for 3V operation

- □ I/Os interface directly to 5V logic

- □ 48mA GTL I/O buffers are in development

- Phase Locked Loop (PLL) for chip-to-chip clock synchronization in development

- □ Automated generation of clock network for skew minimization

- □ High pad to gate ratio optimizes silicon usage

- Fully configurable high-speed RAM compiler

- □ Advanced package options include TAB/QFP, TQFP, PQFP, PGA and TAB

- □ Libraries characterized at 3V±10% and 3.3V±0.3V

- □ Variable output drive: 3, 6, 9, 12, 18, 24 or 48 mA

- Slew-rate controlled output buffers

- Supports scan test methodology

- Single/Dual-Port RAM and ROM memory blocks

Figure 1. Various CMOS-8LCX Packages

#### Table 1 Gate Array Sizes

| Device<br>µPD658xx | Metal<br>Layers | Available<br>Gates | Usable<br>Gates | Total<br>Pads |

|--------------------|-----------------|--------------------|-----------------|---------------|

| 23                 | 3               | 39,856             | 31,884          | 284           |

| 25                 | 3               | 50,880             | 40,704          | 316           |

| 26                 | 3               | 60,320             | 48,256          | 340           |

| 28                 | 3               | 80,400             | 64,320          | 388           |

| 30                 | 3               | 103,360            | 82,688          | 436           |

| 31                 | 3               | 153,264            | 122,611         | 524           |

| 32                 | 3               | 200,128            | 160,102         | 596           |

| 33                 | 3               | 255,360            | 204,288         | 688           |

| 35                 | 3               | 347,200            | 277,760         | 772           |

| 38                 | 3               | 486,048            | 388,838         | 908           |

|                    |                 |                    |                 |               |

Actual gate utilitization may vary depending on circuit implementation. Utilization is 70% for three-layer metal.

Depending on package and circuit specification, some pads are used for  $V_{_{\rm DD}}$  and GND and are not available as signal pads.

CMOS-8LCX products are fully supported by NEC's advanced ASIC design technology. NEC's OpenCAD<sup>®</sup> integration system lets the designer choose the most powerful design tools and services available.

CMOS-8LCX gate arrays support automatic test generation through CrossCheck Technology's testability structures. This results in high fault coverage ATPT of synchronous and asynchronous designs with no netlist modifications and without designer involvement.

® OpenCAD is a registered trademark of NEC Electronics Inc.

® CrossCheck is a registered trademark of CrossCheck Technology, Inc.

#### **Circuit Architecture**

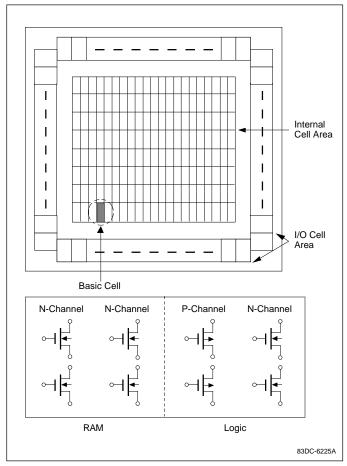

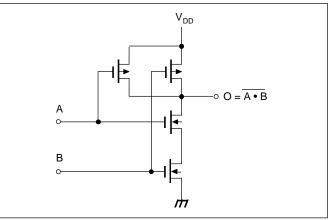

CMOS-8LCX products are built with NEC's 0.50-micron (drawn) channelless gate array architecture. As shown in figure 2, CMOS gate array chips are divided into I/O and internal cell areas. The I/O cell area contains input and output buffers that isolate the internal cells from high-energy external signals. The internal cell area is an array of basic cells, each composed of two p-channel MOS transistors and two n-channel MOS transistors, as well as four additional n-channel MOS transistors for compact RAM design. A cell configured as a two-input NAND gate is shown in figure 3. These p-channel and n-channel transistors are sized to offer a superb ratio of speed to silicon area.

#### **Output Slew-Rate Selection**

Fast rise and fall times of CMOS output buffers can cause system noise and signal overshoot. When an unterminated line is being driven by a buffer, the maximum line length is determined by the rise and fall time of the output buffers and the round-trip signal delay of the line.

Figure 2. Chip Layout and Internal Cell Configuration

As a general rule, the round-trip delay of the line should not exceed the rise or fall time of the driving signal. Transmission lines that are longer than those determined by this rule can degrade system performance due to reflections and ringing. One benefit of slew-rate output buffers is that longer interconnections on a PC board and routing flexibility are possible.

ASIC designers, therefore, can slow down the output edge-rate by using a slew-rate output buffer and thus accommodate longer transmission lines on PC boards.

Slew-rate buffers also inject less noise into the internal power and ground busses of the device, than their nonslew-rate counterparts. As a consequence, slew-rate buffers require fewer power/ground pairs for simultaneous switching outputs.

#### **Publications**

This data sheet contains preliminary specifications, package information, and operational data for the CMOS-8LCX gate array families. Additional design information will be available in NEC's CMOS-8LCX Block Library and CMOS-8LCX Design Manual. Contact your local NEC Design Center or the NEC Literature Center for further ASIC design information; see the back of this data sheet for locations and phone numbers.

### **Absolute Maximum Ratings**

| -0.5 to +4.6 V<br>V <sub>DD</sub> + 0.5 V |

|-------------------------------------------|

| V <sub>DD</sub> + 0.5 V                   |

|                                           |

| V <sub>DD</sub> + 3.0 V                   |

| >1 A (typ)                                |

| –40 to +85°C                              |

| 65 to +150°C                              |

|                                           |

**Caution:** Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.

#### Input/Output Capacitance

$V_{DD} = V_{I} = 0 V; f = 1 MHz$

| Terminal | Symbol           | Тур | Max | Unit |

|----------|------------------|-----|-----|------|

| Input    | C <sub>IN</sub>  | 10  | 20  | pF   |

| Output   | C <sub>OUT</sub> | 10  | 20  | pF   |

| I/O      | C <sub>I/O</sub> | 10  | 20  | pF   |

Note: (1) Values include package pin capacitance.

### Power Consumption at $V_{DD} = 3.3V \pm 0.3V$

| Description        | Limits | Unit   |

|--------------------|--------|--------|

| Internal cell      | 1.24   | µW/MHz |

| Input block (FI01) | 10.0   | µW/MHz |

| Output block       | 0.181  | mW/MHz |

# Recommended Operating Conditions at $V_{DD} = 3.3V \pm 0.3V$

| Parameter                        | Symbol                          | Min                 | Max                 | Unit |

|----------------------------------|---------------------------------|---------------------|---------------------|------|

| Power supply voltage             | V <sub>DD</sub>                 | 2.7                 | 3.6                 | V    |

| Ambient temperature              | T <sub>A</sub>                  | -40                 | +85                 | °C   |

| Low-level input voltage, 3V      | V <sub>IL</sub>                 | 0                   | 0.3 V <sub>DD</sub> | V    |

| High-level input voltage, 3V     | V <sub>IH</sub>                 | 0.7 V <sub>DD</sub> | V <sub>DD</sub>     | V    |

| Low-level input voltage, 5V      | V <sub>IL</sub>                 | 0                   | 0.8                 | V    |

| High-level input voltage, 5V     | V <sub>IH</sub>                 | 2.2                 | V <sub>PP</sub>     | V    |

| Input rise or fall time          | t <sub>R</sub> , t <sub>F</sub> | 0                   | 200                 | ns   |

| Input rise or fall time, Schmitt | t <sub>R</sub> , t <sub>F</sub> | 0                   | 10                  | ms   |

| Positive Schmitt-trigger voltage | V <sub>P</sub>                  | TBD                 | TBD                 | V    |

| Negative Schmitt-trigger voltage | V <sub>N</sub>                  | TBD                 | TBD                 | V    |

| Hysteresis voltage               | V <sub>H</sub>                  | TBD                 | TBD                 | V    |

# AC Characteristics at $V_{DD} = 3.3V \pm 0.3V$ ; $T_j = -40^{\circ}C$ to +125°C

| Parameter                     | Symbol           | Min | Тур | Мах | Unit | Conditions                                      |

|-------------------------------|------------------|-----|-----|-----|------|-------------------------------------------------|

| Toggle frequency              | f <sub>TOG</sub> | 175 |     |     | MHz  | D-F/F; F/O = 2                                  |

| Delay time, 2-input NAND gate |                  |     |     |     |      |                                                 |

| Standard gate (F302)          | t <sub>PD</sub>  | _   | 131 |     | ps   | F/O = 1; L = 0 mm                               |

|                               |                  | _   | 243 |     | ps   | F/O = 2; L = 1 mm                               |

| Low power gate (L302)         | t <sub>PD</sub>  | _   | 149 |     | ps   | F/O = 1; L = 0 mm                               |

|                               |                  |     | 371 |     | ps   | F/O = 2; L = 1 mm                               |

| Delay time, buffer            |                  |     |     |     |      |                                                 |

| Input (FI01)                  | t <sub>PD</sub>  |     | 1.1 |     | ns   | F/O = 1; L = 0 mm @ V <sub>DD</sub> = 3.3 V     |

| Output (FO06)                 | t <sub>PD</sub>  |     | 2.0 |     | ns   | C <sub>L</sub> = 15 pF @ V <sub>DD</sub> = 3.3V |

| Output rise time (FO06)       | t <sub>R</sub>   |     | 1.1 |     | ns   | C <sub>L</sub> = 15 pF @ V <sub>DD</sub> = 3.3V |

| Output fall time (FO06)       | t <sub>F</sub>   |     | 1.1 |     | ns   | C <sub>L</sub> = 15 pF @ V <sub>DD</sub> = 3.3V |

# DC Characteristics at V<sub>DD</sub> = $3.3V \pm 0.3V$ V<sub>DD</sub> = $3.3V \pm 0.3V$ or $3V \pm 10\%$ ; T<sub>j</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C

| Parameter                             | Symbol          | Min                   | Тур              | Max | Unit | Conditions                |

|---------------------------------------|-----------------|-----------------------|------------------|-----|------|---------------------------|

| Quiescent current (Note 1)            | Ι <sub>L</sub>  |                       | TBD              | TBD | μA   | $V_1 = V_{DD}$ or GND     |

| Input leakage current                 |                 |                       |                  |     |      |                           |

| Regular                               | l <sub>i</sub>  |                       | 10 <sup>-5</sup> | 10  | μA   | $V_1 = V_{DD}$ or GND     |

| 50 kΩ pull-up                         | l,              | TBD                   | TBD              | TBD | μA   | V <sub>I</sub> = GND      |

| 5 kΩ pull-up                          | l <sub>l</sub>  | TBD                   | TBD              | TBD | mA   | V <sub>I</sub> = GND      |

| 50 kΩ pull-down                       | l,              | TBD                   | TBD              | TBD | μA   | $V_{I} = V_{DD}$          |

| Off-state output leakage current      | I <sub>oz</sub> |                       |                  | TBD | μA   | $V_0 = V_{DD}$ or GND     |

| Input clamp voltage                   | V <sub>IC</sub> | TBD                   |                  |     | V    | I <sub>I</sub> = 18 mA    |

| Output short circuit current (Note 2) | I <sub>OS</sub> | TBD                   |                  |     | mA   | $V_0 = 0 V$               |

| Low-level output current, 3V buffers  |                 |                       |                  |     |      |                           |

| 3 mA                                  | I <sub>OL</sub> | 3                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 6 mA                                  | I <sub>OL</sub> | 6                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 9 mA                                  | I <sub>OL</sub> | 9                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 12 mA                                 | I <sub>OL</sub> | 12                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 18 mA                                 | I <sub>OL</sub> | 18                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 24 mA                                 | I <sub>OL</sub> | 24                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 48 mA                                 | I <sub>OL</sub> | 48                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| Low-level output current, 5V buffers  |                 |                       |                  |     |      |                           |

| 3 mA                                  | I <sub>OL</sub> | 3                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 6 mA                                  | I <sub>OL</sub> | 6                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 9 mA                                  | I <sub>OL</sub> | 9                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 12 mA                                 | I <sub>OL</sub> | 12                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| 18 mA                                 | I <sub>OL</sub> | 18                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V   |

| High-level output current, 3V buffers |                 |                       |                  |     |      | -                         |

| 3 mA                                  | I <sub>OH</sub> | -3                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 6 mA                                  | I <sub>OH</sub> | -6                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 9 mA                                  | I <sub>OH</sub> | -9                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 12 mA                                 | I <sub>OH</sub> | -12                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 18 mA                                 | I <sub>OH</sub> | -18                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 24 mA                                 | I <sub>OH</sub> | -24                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 48 mA                                 | I <sub>OH</sub> | -48                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| High-level output current, 5V buffers |                 |                       |                  |     |      |                           |

| 3 mA                                  | I <sub>OH</sub> | -3                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 6 mA                                  | I <sub>OH</sub> | -3                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 9 mA                                  | I <sub>OH</sub> | -3                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 12 mA                                 | I <sub>OH</sub> | -6                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| 18 mA                                 | I <sub>OH</sub> | -6                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V   |

| Low-level output voltage, 3V and 5V   | V <sub>OL</sub> |                       |                  | 0.1 | V    | $I_{OL} = 0 \text{ mA}$   |

| High-level output voltage, 3V and 5V  | V <sub>OH</sub> | V <sub>DD</sub> - 0.1 |                  |     | V    | I <sub>OH</sub> = -0.2 mA |

The maximum value reflects the use of pull-up/pull-down resistors and oscillator blocks. Contact an NEC ASIC Design Center Notes: (1) for assistance in calculation.

(2) Rating is for only one output operating in this mode for less than 1 second.

### **Absolute Maximum Ratings**

| $\label{eq:supply voltage, V_{DD}} \begin{array}{c} -0.5 \ \text{to } +4.6 \ \text{V} \\ \hline 3 \text{V interface I/O voltage, V}_{I,} \text{V}_{O} & -0.5 \ \text{V to } \text{V}_{DD} + 0.5 \ \text{V} \\ \hline 5 \text{V interface I/O voltage, V}_{I,} \text{V}_{O} & -0.5 \ \text{V to } \text{V}_{DD} + 3.0 \ \text{V} \\ \hline \text{Latch-up current, I}_{LATCH} & >1 \ \text{A (typ)} \\ \hline \text{Operating temperature, T}_{OPT} & -40 \ \text{to } +85^{\circ}\text{C} \\ \hline \text{Storage temperature, T}_{STG} & -65 \ \text{to } +150^{\circ}\text{C} \\ \end{array}$ |                                         |                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|

| 5V interface I/O voltage, $V_{I}, V_{O}$ -0.5 V to $V_{DD}$ + 3.0 VLatch-up current, $I_{LATCH}$ >1 A (typ)Operating temperature, $T_{OPT}$ -40 to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                        | Power supply voltage, $V_{DD}$          | –0.5 to +4.6 V                    |

| Latch-up current, I>1 A (typ)Operating temperature, T-40 to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3V interface I/O voltage, $V_{I, v_O}$  | –0.5 V to V <sub>DD</sub> + 0.5 V |

| Operating temperature, T <sub>OPT</sub> -40 to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5V interface I/O voltage, $V_{I, V_O}$  | -0.5 V to V <sub>DD</sub> + 3.0 V |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Latch-up current, I <sub>LATCH</sub>    | >1 A (typ)                        |

| Storage temperature, T <sub>STG</sub> -65 to +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Operating temperature, T <sub>OPT</sub> | –40 to +85°C                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Storage temperature, T <sub>STG</sub>   | -65 to +150°C                     |

Caution: Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.

# Input/Output Capacitance $V_{DD} = V_I = 0 V$ ; f=1 MHz

| Terminal | Symbol           | Тур | Max | Unit |

|----------|------------------|-----|-----|------|

| Input    | C <sub>IN</sub>  | 10  | 20  | pF   |

| Output   | C <sub>OUT</sub> | 10  | 20  | pF   |

| I/O      | C <sub>I/O</sub> | 10  | 20  | pF   |

### Power Consumption at $V_{DD} = 3.0V \pm 10\%$

| Description        | Limits | Unit        |

|--------------------|--------|-------------|

| Internal cell      | 0.80   | µW/MHz/cell |

| Input block (FI01) | 8.0    | µW/MHz      |

| Output block       | 0.164  | mW/MHz      |

# Recommended Operating Conditions at $V_{\text{DD}}$ = 3.0V ± 10%

| Parameter                        | Symbol                          | Min                 | Max                 | Unit |

|----------------------------------|---------------------------------|---------------------|---------------------|------|

| Power supply voltage             | V <sub>DD</sub>                 | 2.7                 | 3.6                 | V    |

| Ambient temperature              | T <sub>A</sub>                  | -40                 | +85                 | °C   |

| Low-level input voltage, 3V      | V <sub>IL</sub>                 | 0                   | 0.3 V <sub>DD</sub> | V    |

| High-level input voltage, 3V     | V <sub>IH</sub>                 | 0.7 V <sub>DD</sub> | V <sub>DD</sub>     | V    |

| Low-level input voltage, 5V      | V <sub>IL</sub>                 | 0                   | 0.8                 | V    |

| High-level input voltage, 5V     | V <sub>IH</sub>                 | 2.2                 | V <sub>DD</sub>     | V    |

| Input rise or fall time          | t <sub>R</sub> , t <sub>F</sub> | 0                   | 200                 | ns   |

| Input rise or fall time, Schmitt | t <sub>R</sub> , t <sub>F</sub> | 0                   | 10                  | ms   |

| Positive Schmitt-trigger voltage | V <sub>P</sub>                  | TBD                 | TBD                 | V    |

| Negative Schmitt-trigger voltage | V <sub>N</sub>                  | TBD                 | TBD                 | V    |

| Hysteresis voltage               | V <sub>H</sub>                  | TBD                 | TBD                 | V    |

# AC Characteristics at $V_{DD}$ = 3.0V ± 10%; T<sub>j</sub> = -40°C to +125°C

| Parameter                     | Symbol           | Min | Тур  | Max | Unit | Conditions                                      |

|-------------------------------|------------------|-----|------|-----|------|-------------------------------------------------|

| Toggle frequency              | f <sub>TOG</sub> | 175 |      |     | MHz  | D-F/F; F/O = 2                                  |

| Delay time, 2-input NAND gate |                  |     |      |     |      |                                                 |

| Standard gate (F302)          | t <sub>PD</sub>  | _   | 147  |     | ps   | F/O = 1; L = 0 mm                               |

|                               |                  |     | 272  |     | ps   | F/O = 2; L = 1 mm                               |

| Low power gate (L302)         | t <sub>PD</sub>  |     | 167  |     | ps   | F/O = 1; L = 0 mm                               |

|                               |                  |     | 416  |     | ps   | F/O = 2; L = 1 mm                               |

| Delay time, buffer            |                  |     |      |     |      |                                                 |

| Input (FI01)                  | t <sub>PD</sub>  |     | 309  |     | ps   | F/O = 1; L = 0 mm @ V <sub>DD</sub> = 3.0 V     |

| Output (FO06)                 | t <sub>PD</sub>  |     | 1.62 |     | ns   | C <sub>L</sub> = 15 pF @ V <sub>DD</sub> = 3.0V |

| Output rise time (FO06)       | t <sub>R</sub>   |     | TBD  |     | ns   | C <sub>L</sub> = 15 pF @ V <sub>DD</sub> = 3.0V |

| Output fall time (FO06)       | t <sub>F</sub>   |     | TBD  |     | ns   | C <sub>L</sub> = 15 pF @ V <sub>DD</sub> = 3.0V |

# **DC Characteristics at** $V_{DD}$ = 3.0V ± 10% $V_{DD}$ = 3.3V ± 0.3V or 3V ± 10%; $T_j$ = -40°C to +125°C

| Parameter                             | Symbol          | Min                   | Тур              | Max | Unit | Conditions                              |

|---------------------------------------|-----------------|-----------------------|------------------|-----|------|-----------------------------------------|

| Quiescent current (Note 1)            | Ι <sub>L</sub>  |                       | TBD              | TBD | μA   | $V_I = V_{DD}$ or GND                   |

| Input leakage current                 |                 |                       |                  |     |      |                                         |

| Regular                               | l <sub>l</sub>  |                       | 10 <sup>-5</sup> | 10  | μA   | $V_1 = V_{DD}$ or GND                   |

| 50 kΩ pull-up                         | l,              | TBD                   | TBD              | TBD | μA   | V <sub>I</sub> = GND                    |

| 5 kΩ pull-up                          | l,              | TBD                   | TBD              | TBD | mA   | V <sub>I</sub> = GND                    |

| 50 kΩ pull-down                       | l,              | TBD                   | TBD              | TBD | μA   | $V_{I} = V_{DD}$                        |

| Off-state output leakage current      | I <sub>oz</sub> |                       |                  | TBD | μA   | V <sub>O</sub> = V <sub>DD</sub> or GND |

| Input clamp voltage                   | V <sub>IC</sub> | TBD                   |                  |     | V    | l <sub>l</sub> = 18 mA                  |

| Output short circuit current (Note 2) | I <sub>OS</sub> | TBD                   |                  |     | mA   | $V_0 = 0 V$                             |

| Low-level output current, 3V buffers  |                 |                       |                  |     |      |                                         |

| 3 mA                                  | I <sub>OL</sub> | 3                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 6 mA                                  | I <sub>OL</sub> | 6                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 9 mA                                  | I <sub>OL</sub> | 9                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 12 mA                                 | I <sub>OL</sub> | 12                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 18 mA                                 | I <sub>OL</sub> | 18                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 24 mA                                 | I <sub>OL</sub> | 24                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 48 mA                                 | I <sub>OL</sub> | 48                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| Low-level output current, 5V buffers  |                 |                       |                  |     |      |                                         |

| 3 mA                                  | I <sub>OL</sub> | 3                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 6 mA                                  | I <sub>OL</sub> | 6                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 9 mA                                  | I <sub>OL</sub> | 9                     |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 12 mA                                 | I <sub>OL</sub> | 12                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| 18 mA                                 | I <sub>OL</sub> | 18                    |                  |     | mA   | V <sub>OL</sub> = 0.4 V                 |

| High-level output current, 3V buffers |                 |                       |                  |     |      |                                         |

| 3 mA                                  | I <sub>OH</sub> | -3                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V                 |

| 6 mA                                  | I <sub>он</sub> | -6                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V                 |

| 9 mA                                  | I <sub>OH</sub> | -9                    |                  |     | mA   | V <sub>OH</sub> = 2.4 V                 |

| 12 mA                                 | I <sub>OH</sub> | -12                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V                 |

| 18 mA                                 | I <sub>OH</sub> | -18                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V                 |

| 24 mA                                 | I <sub>OH</sub> | -24                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V                 |

| 48 mA                                 | I <sub>OH</sub> | -48                   |                  |     | mA   | V <sub>OH</sub> = 2.4 V                 |

| High-level output current, 5V buffers |                 |                       |                  |     |      |                                         |

| 3 mA                                  | I <sub>OH</sub> | -2                    |                  |     | mA   | V <sub>OH</sub> = 2.2 V                 |

| 6 mA                                  | I <sub>OH</sub> | -2                    |                  |     | mA   | V <sub>OH</sub> = 2.2 V                 |

| 9 mA                                  | I <sub>OH</sub> | -2                    |                  |     | mA   | V <sub>OH</sub> = 2.2 V                 |

| 12 mA                                 | I <sub>OH</sub> | -4                    |                  |     | mA   | V <sub>OH</sub> = 2.2 V                 |

| 18 mA                                 | I <sub>он</sub> | -4                    |                  |     | mA   | V <sub>OH</sub> = 2.2 V                 |

| Low-level output voltage, 3V and 5V   | V <sub>OL</sub> |                       |                  | 0.1 | V    | $I_{OL} = 0 \text{ mA}$                 |

| High-level output voltage, 3V         | V <sub>OH</sub> | V <sub>DD</sub> - 0.1 |                  |     | V    | I <sub>OH</sub> =0 mA                   |

| High-level output voltage, 5V         | V <sub>он</sub> | V <sub>DD</sub> - 0.2 |                  |     | V    | I <sub>OH</sub> = 0 mA                  |

The maximum value reflects the use of pull-up/pull-down resistors and oscillator blocks. Contact an NEC ASIC Design Center for assistance.

Rating is for only one output operating in this mode for less than 1 second. Notes: (1)

#### Table 2 CMOS-8 Package Options

| Maximum           |                | je Dimens |         |      |      |      | Mas  | ter Slic | e µPD6 | 5xxx |      |      |      |

|-------------------|----------------|-----------|---------|------|------|------|------|----------|--------|------|------|------|------|

| I/O Pins          | Body Size      | Pitch     | Height  | -823 | -825 | -826 | -828 | -830     | -831   | -832 | -833 | -835 | -838 |

| Plastic Quad Flat | pack (PQFP)    |           |         |      |      |      |      |          |        |      |      |      |      |

| 120-pin           | 28 mm 🗆        | 0.8 mm    | 3.7 mm  | А    | А    | А    | А    | А        | А      | А    | А    | А    | А    |

| 136-pin           | 28 mm 🗆        | 0.65 mm   | 3.7 mm  | А    | А    | А    | А    | А        | А      | А    | А    | А    | А    |

| 160-pin           | 28 mm 🗆        | 0.65 mm   | 3.7 mm  | D    | D    | А    | А    | А        | А      | А    | А    | А    | А    |

| 160-pin (H/       | 'S) 28 mm □    | 0.65 mm   | 3.2 mm  | -    | D    | D    | D    | D        | D      | D    | D    | D    | -    |

| 184-pin           | 32 mm 🗆        | 0.65 mm   | 3.2 mm  | D    | D    | D    | D    | D        | D      | D    | D    | D    | D    |

| Plastic Quad Flat | pack (PQFP-FP) |           |         |      |      |      |      |          |        |      |      |      |      |

| 100-pin           | 14 mm 🗆        | 0.5 mm    | 1.45 mm | А    | А    | А    | -    | -        | -      | -    | -    | -    | -    |

| 120-pin           | 20 mm □        | 0.5 mm    | 2.7 mm  | А    | А    | А    | А    | А        | А      | А    | А    | -    | -    |

| 144-pin           | 20 mm □        | 0.5 mm    | 2.7 mm  | А    | А    | А    | А    | А        | А      | А    | А    | -    | -    |

| 160-pin           | 24 mm 🗆        | 0.5 mm    | 2.7 mm  | D    | А    | А    | А    | А        | А      | А    | А    | А    | -    |

| 160-pin (H/       | 'S) 24 mm □    | 0.5 mm    | 2.7 mm  | -    | Р    | Р    | Ρ    | Р        | Р      | Р    | Р    | Р    | -    |

| 176-pin           | 24 mm 🗆        | 0.5 mm    | 2.7 mm  | D    | D    | А    | А    | А        | А      | А    | А    | А    | -    |

| 176-pin (H/       | 'S) 24 mm □    | 0.5 mm    | 2.7 mm  | -    | -    | D    | D    | D        | D      | D    | D    | D    | -    |

| 208-pin           | 28 mm 🗆        | 0.5 mm    | 3.2 mm  | D    | D    | D    | D    | А        | А      | А    | А    | А    | А    |

| 208-pin (H/       | 'S) 28 mm □    | 0.5 mm    | 3.2 mm  | -    | -    | -    | -    | D        | D      | D    | D    | D    | D    |

| 240-pin           | 32 mm 🗆        | 0.5 mm    | 3.2 mm  | D    | D    | D    | D    | D        | А      | А    | А    | А    | А    |

| 256-pin           | 28 mm 🗆        | 0.4 mm    | 3.2 mm  | D    | D    | D    | D    | D        | А      | А    | А    | А    | А    |

| 272-pin           | 36 mm □        | 0.5 mm    | 3.2 mm  | D    | D    | D    | D    | D        | А      | А    | А    | А    | А    |

| 304-pin           | 40 mm □        | 0.5 mm    | 3.7 mm  | D    | D    | D    | D    | D        | D      | А    | А    | А    | А    |

| Thin Quad Flatpa  | ck (TQFP) PRE  | LIMINARY  |         |      |      |      |      |          |        |      |      |      |      |

| 80-pin            | 12 mm 🗆        | 0.5 mm    | 1.05 mm | Р    | -    | -    | -    | -        | -      | -    | -    | -    | -    |

| 100-pin           | 14 mm 🗆        | 0.5 mm    | 1.0 mm  | Р    | Р    | Р    | -    | -        | -      | -    | -    | -    | -    |

| 120-pin           | 14 mm 🗆        | 0.4 mm    | 1.0 mm  | Р    | Р    | Р    | Ρ    | Р        | Р      | Р    | Р    | -    | -    |

| 144-pin           | 20 mm 🗆        | 0.5 mm    | 1.4 mm  | Р    | Р    | Р    | Р    | Р        | Р      | Ρ    | Р    | -    | -    |

| 160-pin           | 24 mm 🗆        | 0.5 mm    | 1.4 mm  | Р    | Р    | Р    | Р    | Р        | Р      | Ρ    | Р    | Р    | -    |

| 176-pin           | 24 mm 🗆        | 0.5 mm    | 1.4 mm  | Р    | Р    | Р    | Ρ    | Р        | Р      | Р    | Р    | Р    | -    |

| 208-pin           | 28 mm 🗆        | 0.5 mm    | 1.4 mm  | Р    | Р    | Р    | Р    | Р        | Р      | Р    | Р    | Р    | Р    |

| Ceramic Pin Grid  | Array (CPGA)   |           |         |      |      |      |      |          |        |      |      |      |      |

| 72-pin            | 27.94 mm 🗆     | 100 mils  | 4.57 mm | А    | А    | А    | А    | А        | А      | А    | А    | А    | А    |

| 132-pin           | 35.56 mm □     | 100 mils  | 4.57 mm | А    | А    | А    | А    | А        | А      | А    | А    | А    | А    |

| 176-pin           | 38.10 mm 🗆     | 100 mils  | 4.57 mm | D    | D    | D    | А    | А        | А      | А    | А    | А    | А    |

| 208-pin           | 43.18 mm 🗆     | 100 mils  | 5.08 mm | D    | D    | D    | D    | А        | А      | А    | А    | А    | А    |

| 280-pin           | 48.26 mm 🗆     | 100 mils  | 4.57 mm | D    | D    | D    | D    | D        | D      | А    | А    | А    | А    |

| 364-pin           | 43.18 mm 🗆     | 50 mils   | 3.0 mm  | _    | _    | _    | D    | D        | D      | D    | D    | А    | А    |

| Ceramic Pin Grid  | Array (CPGA) B | utt-Lead  |         |      |      |      |      |          |        |      |      |      |      |

| 288-pin           | 27.94 mm 🗆     | 50 mils   | 5.58 mm | D    | D    | D    | D    | D        | D      | D    | D    | D    | D    |

| 528-pin           | 48.26 mm 🗆     | 50 mils   | 10.6 mm | _    | _    | _    | _    | _        | D      | D    | D    | D    | D    |

Notation: A = Available; P = Planned; D = In Development; "-" = Unavailable; H/S = Heat Spreader.

**Note:** NEC reserves the right to alter the package plan based on the results of qualification. For current package availability, please contact your local NEC Design Center.

#### **NEC's ASIC Design System**

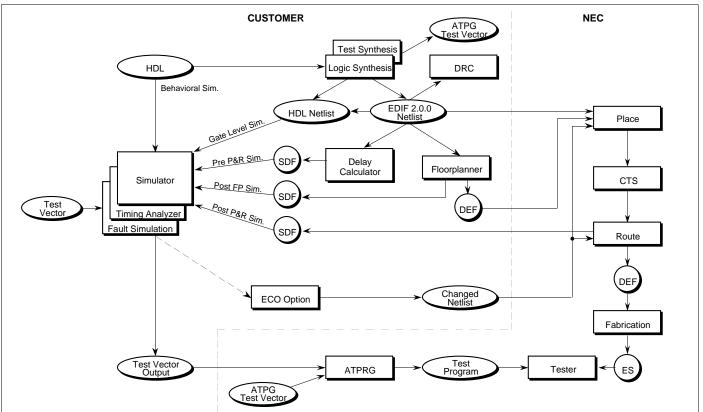

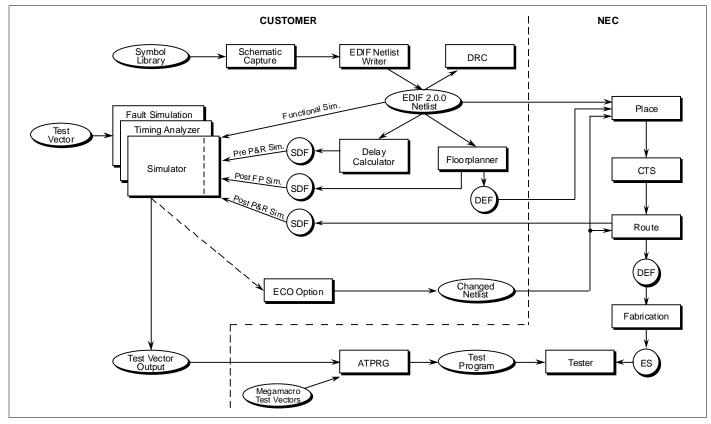

NEC supports its ASIC products with a comprehensive CAD system that significantly reduces the time and expense usually associated with the development of semicustom devices. Designers can choose from today's most popular third-party software tools, shown in the table on the adjacent page. NEC's OpenCAD Design System is a front-end to back-end ASIC design package that merges several advanced CAE/CAD tools into a single structure. Designers can now choose a single CAE platform, or mix and match tools from a variety of third-party vendors. The design flow combines tools for floorplanning, logic synthesis, automatic test generation, accelerated fault-grading, full timing simulation, and advanced place-and-route algorithms. This flexible design environment thereby ensures accurate, on schedule designs.

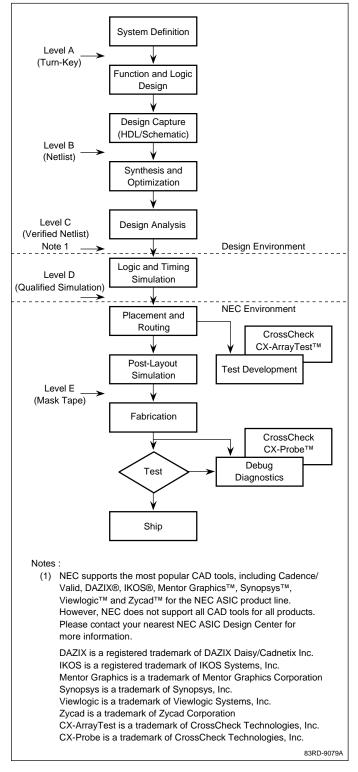

There are two basic methods for design entry, the first is by HDL specification, figure 4; the second is via schematic capture, figure 5. Note that after the initial EDIF netlist is generated, there is little difference in the basic design flow for either method. Figure 6 shows the location of the CrossCheck tools in the high-level design flow.

A top-down modeling methodology is possible using the HDL specification approach. Designers can concentrate

their design effort at a higher level of abstraction, specifying, modeling, and simulating their designs at a systems level. This leaves the details of the gate-level implementation to the synthesis tools. After verification confirms the design's functionality, designers are then free to explore various functional and architectural trade-offs, and can optimize chip performance while minimizing chip area. An engineer can evaluate several architectures and select the best solution before committing the design to silicon.

The more traditional method of design entry, schematic capture, figure 5, is available with a wide variety of thirdparty tools. The supported tools, described in Table 3, provide the designer with a productive way to manage the hierarchical elements of a CMOS-8 design, utilizing the macro symbol library provided by NEC. For those designers who are experienced and already well-versed with graphical design entry, this provides an efficient migration path for ASIC development.

One of the key benefits of NEC's ASIC design flow is that post place-and-route simulation can be accomplished at the customer's site, since NEC offers designers a choice of simulators within the "golden simulator" category. Golden simulator status means that upon receiving post placeand-route simulation results from a customer, NEC can then proceed directly to photomask production, bypassing any additional post-simulation steps. This can save a lot of time.

Figure 4. HDL Specification Design Flow

NEC

The floorplanner tool provides realistic estimates of wire length by grouping hierarchical blocks into specific physical locations on the chip. This minimizes critical path interconnect delays for more accurate simulation. The floorplanner also provides graphical I/O assignment capabilities and generates a delay file for post-floorplanner simulation.

The ECO (Engineering Change Order) option in figures 4 and 5 allows the designer to make minor corrections in the design without requiring an entirely new placement and routing of the device. This tool improves turnaround time by ensuring that relatively small changes, such as connectivity changes, will not greatly impact the current design timing.

NEC also incorporates proprietary tools to facilitate the design process. A single delay calculator is used for all CAE platforms to ensure consistent timing and simulation results. A comprehensive design rule check (DRC) program reports design rule violations as well as chip utilization statistics for the design netlist. The generated report contains such information as net-count calculation, total pin-count and cell-count use, and usage rate calculations. Unused input pins, violations in pin naming conventions and fan-out limits, are examples of the design rule violations reported by this program.

Sample design kits are available at no charge to qualified users. A software license agreement is required. For more information, contact your nearest NEC ASIC Design Center, listed on the back of this data sheet.

| Table 5 Third-1 arty Supported Tools |                    |           |            |                           |              |                    |                     |      |

|--------------------------------------|--------------------|-----------|------------|---------------------------|--------------|--------------------|---------------------|------|

| Tools<br>CAD<br>Company              | Schematic<br>Entry | Synthesis | Simulation | Static Timing<br>Analysis | Floorplanner | Place<br>and Route | Fault<br>Simulation | ATPG |

| Synopsys                             |                    |           |            |                           |              |                    |                     |      |

| Cadence                              | Ι                  |           | *          |                           |              |                    |                     |      |

| Mentor                               |                    |           |            | +                         |              |                    | +                   |      |

| Viewlogic                            | I                  |           |            |                           |              |                    |                     |      |

| Valid (Cadence)                      | -                  |           |            | +                         |              |                    |                     |      |

| IKOS                                 |                    |           |            |                           |              |                    |                     |      |

| Zycad/NECplus                        |                    |           | *          |                           |              |                    |                     |      |

| Intelligen                           |                    |           |            |                           |              |                    |                     |      |

| NEC                                  |                    |           | *          |                           |              |                    |                     |      |

#### Table 3 Third-Party Supported Tools

Key:

- indicates "Golden Simulator" status.

- indicates planned support-check with local Design Center for exact availability.

- + indicates function is available via software library, and software support is through third-party vendor.

#### Figure 5. Schematic-Based Design Flow

#### **CrossCheck Test Design Flow**

The CMOS-8LCX (CrossCheck) ASICs makes use of a unique test structure, called On-Chip Test Engine<sup>™</sup>, that allows testability to be incorporated into a CMOS-8LCX design, using a process that is totally transparent to the designer. This unique approach transfers the burden of test development from the designer to NEC, where the testability is incorporated automatically during the manufacturing phase of the device. A summary of the benefits to CrossCheck Test are described below.

#### **CrossCheck Test Benefits**

- Push-button automatic test pattern generation (ATPG)

- No functional or initialization vectors required

- Negligible performance impact

- Netlist modifications not required

- High fault coverage tests including stuck at, bridging and manufacturing faults

- Tests all design styles, including: Synchronous single clock

Synchronous multiple gated clock

Asynchronous

- □ Enhanced prototype diagnostic capability

#### **Designing with CrossCheck**

In using CrossCheck, the designer's only test consideration is in the selection of a CMOS-8LCX base array. In the design phase, the designer is free to use any preferred CAE tools and methodology supported by NEC.

This design freedom extends to the nature of the design, synchronous or asynchronous, as shown in figure 4, where the CMOS-8LCX gate array design flow with the CrossCheck solution is illustrated. During simulation the designer uses NEC's CrossCheck library. The only input to test development is the netlist that is sent to NEC for manufacturing CMOS-8LCX devices.

When the design is placed and routed, NEC automatically connects the On-Chip Test Engine to the circuit design. The test structure affords massive observability and controllability of the design even though the CMOS-8LCX looks exactly like a conventional ASIC. The connections of the test structures have a negligible performance impact on the design and require no modification to the user's netlist.

NEC uses the CX-ArrayTest<sup>™</sup> software to automatically generate high fault coverage test patterns. The test development process requires only the design netlist and placement information. There is no need for designer-supplied

functional or initialization vectors, a significant benefit. CX-ArrayTest software performs design analysis, ATPG, and fault grading. The CX-Probe<sup>™</sup>, a software program developed by CrossCheck Technology, uses the on-chip test structures to automate prototype debug and diagnostics. With these tools, CMOS-8LCX gate arrays with the embedded test solution resolve three of the key parameters for testing the quality of ASICs: high fault coverage, rapid failure analysis and time-to-market.

#### **Embedded Test Structures**

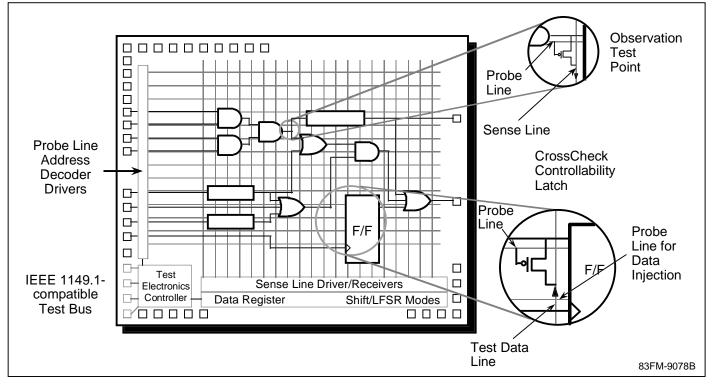

In the CMOS-8LCX, the test structure is embedded directly in the base array, as shown in figure 5. The On-Chip Test Engine consists of a grid of sense transistors, which provide massive observability and which are transparent to the designer. An address matrix of probe and sense lines select and control the node under test. A test controller then manages the address matrix and activates the sense transistors. The small transistor used has a negligible impact on the overall performance of the gate array. There is one observation point for each four transistors or gate.

<sup>™</sup> CX-Probe and CX-ArrayTest are trademarks of CrossCheck Technology, Inc.

Figure 5. CMOS-8LCX CrossCheck On-Chip Test Engine

The key to this on-chip test system is the patented CrossCheck Controllability Latch (CCL), shown in figure 5, which allows fully automated test pattern generation without modification to the user's netlist. The CCL uses two embedded probe lines and a sense line to control the latch data injection. Thus, the CCLs are not connected as a synchronous chain. For this reason CX-ArrayTest software can perform ATPG on asynchronous circuitry. The CCL implementation has negligible impact on performance.

#### **Test Controller**

The on-chip test electronics controller, shown in figure 5, performs four major functions:

- □ Interface to the CrossCheck Test Access Port

- □ Test vector generation

- □ Signature generation

- On-Chip Test Engine self-test

Access to the On-Chip Test Engine is through CrossCheck's Test Access Port. This test bus, compatible with IEEE 1149.1, interfaces with automatic test equipment (ATE). The ATE sends instructions and data to the on-chip controller and in return receives test results from it. The On-Chip Test Engine produces test vectors on the chip acting on instructions and/or data received from the CX-ArrayTest software. This compatibility significantly reduces the ATE test vector memory requirements for high fault coverage testing. To further reduce the amount of ATE vector memory used, the state of the test points on the device are read and compressed into a signature in the data register.

#### **Fault Models**

Because macrocells generally contain multiple test points, defects within cells are detected. Traditional methods test only the inputs and outputs of the macrocells, detecting only the symptoms of a fault rather than the fault itself, and often not detecting the fault at all. The CMOS-8LCX CrossCheck test solution models nine different defect types:

□ Stuck-at-faults:

| Input stuck-at "1" | Output stuck-at "1" |

|--------------------|---------------------|

| Input stuck-at "0" | Output stuck-at "0" |

Comprehensive manufacturing defects:

Shorted FET Shorted intra-macro interconnect Open FET Open intra-macro interconnect Shorted inter-macro networks

# Table 4 Typical Fault Coverage with CX-ArrayTest

| Design Style          | Stuck at Faults | Bridging Faults |

|-----------------------|-----------------|-----------------|

| Synchronous           | > 98%           | >99%            |

| Multiple gated clocks | > 95%           | >99%            |

| Asynchronous          | 90% – 95%       | >98%            |

The fault coverage that can be achieved is dependent upon the design style used. Synchronous designs have a single clock for the complete design. Gated clock designs are generally synchronous but have several clocks and flip-flop clocks that are gated by combinatorial logic.

Asynchronous is all other design styles. Asynchronous is a design style often used in interface circuits, and is generally not testable with approaches such as SCAN. The CMOS-8LCX's ability to test asynchronous design is a significant advantage of this test solution. Examples of typical fault coverage using CMOS-8LCX are shown in Table 4.

NEC uses CrossCheck's CX-Fault<sup>™</sup> tool to analyze the transistor-level descriptions of the macrocells to produce a model library. The library contains the test generation fault models that are used by the ATPG.

#### Automatic Test Pattern Generation

ATPG requires only the user netlist, placement file, and the results of the test strategy developed from the netlist analysis. CX-ArrayTest generates values for the test strategy waveform template and avoids the hazard circuit states. A full timing simulation is performed to determine circuit stability after each vector is generated and applied. Simulating the On-Chip Test Engine allows creation of the signature of the internal circuit node states. Faults are marked as detected only when the circuit is stable and a signature is generated. The ATPG also correctly handles any unavoidable hazard circuit states. The CX-ArrayTest software monitors and reports fault coverage, test time and vector length as it generates new vectors.

The ATPG process continues until one of the user-defined limits is reached, specifically fault coverage, number of test vectors, test time, or elapsed ATPG processing time. At the end of test generation, a set of vectors, including tests of the On-Chip Test Engine, are packaged for translation onto automatic test equipment.

Using the CrossCheck test solution allows automation of the process of failure analysis, reducing diagnostics from days or weeks to just hours.

™ CX-Fault is a trademark of CrossCheck Technology, Inc.

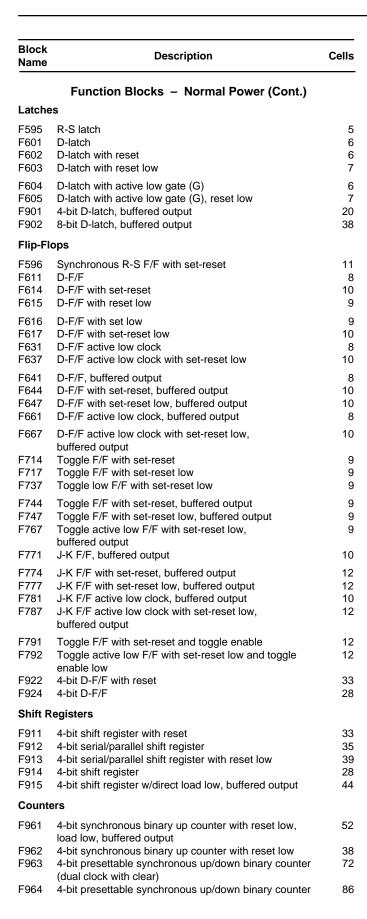

#### **Block Library List**

The CMOS-8L family offers a variety of blocks, including gates, flip-flop circuits, and shift registers. The functions of these blocks are designed to be compatible with those of the CMOS-8, CMOS-7 and CMOS-6 families. In addition, memory blocks such as RAM and ROM will be provided, and low-power gates are available. The low-power blocks are designed for gate count reduction; the number of cells are fewer than that of the standard block, contributing to lower power consumption and higher efficiency. Another feature is the I/Os can directly interface to 5V logic.

#### **Block List**

| Bloc                         | k List                                                                                                                                                                 |                         |                                  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------|

| Block<br>Name                | Description                                                                                                                                                            | l <sub>oL</sub><br>(mA) | Cells                            |

|                              | Interface Blocks                                                                                                                                                       |                         |                                  |

| 3V CM                        | OS Input Buffers                                                                                                                                                       |                         |                                  |

| FI01<br>FID1<br>FIU1<br>FIW1 | 3V CMOS input<br>3V CMOS input, 50 kΩ pull-down<br>3V CMOS in, 50 kΩ pull-up<br>3V CMOS in, 5 kΩ pull-up                                                               |                         | 1 (3)<br>1 (3)<br>1 (3)<br>1 (3) |

| FIS1<br>FDS1<br>FUS1<br>FWS1 | 3V CMOS Schmitt input<br>3V CMOS Schmitt input, 50 k $\Omega$ pull-down<br>3V CMOS Schmitt input, 50 k $\Omega$ pull-up<br>3V CMOS Schmitt input, 5 k $\Omega$ pull-up |                         | 1 (8)<br>1 (8)<br>1 (8)<br>1 (8) |

| FIB1<br>FDB1                 | $3V$ CMOS input, high fanout for clock driver $3V$ CMOS input, high fanout for clock driver, $50 \text{ k}\Omega$ pull-down                                            | -                       | 1 (24)<br>1 (24)                 |

| FUB1<br>FWB1                 | 3V CMOS input, high fanout for clock driver,<br>50 kΩ pull-up<br>3V CMOS input, high fanout for clock driver,<br>5 kΩ pull-up                                          | -                       | 1 (24)<br>1 (24)                 |

| 3V CM                        | OS Input Buffers without Protection Diode up                                                                                                                           | o to V <sub>DD</sub>    |                                  |

| FIA1<br>FDA1<br>FUA1<br>FWA1 | 3V CMOS input<br>3V CMOS input, 50 kΩ pull-down<br>3V CMOS input, 50 kΩ pull-up<br>3V CMOS input, 5 kΩ pull-up                                                         | -                       | 1 (3)<br>1 (3)<br>1 (3)<br>1 (3) |

| FIE1<br>FDE1<br>FUE1<br>FWE1 | 3V CMOS Schmitt input<br>3V CMOS Schmitt input, 50 k $\Omega$ pull-down<br>3V CMOS Schmitt input, 50 k $\Omega$ pull-up<br>3V CMOS Schmitt input, 5 k $\Omega$ pull-up | -<br>-<br>-             | 1 (8)<br>1 (8)<br>1 (8)<br>1 (8) |

| FIH1<br>FDH1                 | 3V CMOS input, high fanout for clock driver<br>3V CMOS input, high fanout for clock driver,<br>50 kΩ pull-down                                                         | -                       | 1 (24)<br>1 (24)                 |

| FUH1                         | 3V CMOS input, high fanout for clock driver,                                                                                                                           | -                       | 1 (24)                           |

| FWH1                         | 50 k $\Omega$ pull-up<br>3V CMOS input, high fanout for clock driver,<br>5 k $\Omega$ pull-up                                                                          | -                       | 1 (24)                           |

| 5V CM                        | OS Input Buffers                                                                                                                                                       |                         |                                  |

| FIV1<br>FDV1<br>FIF1<br>FDF1 | 5V CMOS input<br>5V CMOS input, 50 kΩ pull-down<br>5V CMOS Schmitt input<br>5V CMOS Schmitt input, 50 kΩ pull-down                                                     |                         | 1 (3)<br>1 (3)<br>1 (8)<br>1 (8) |

| FIG1<br>FDG1                 | 5V CMOS input, high fanout for clock driver<br>5V CMOS input, high fanout for clock driver,<br>50 k $\Omega$ pull-down                                                 | -                       | 1 (24)<br>1 (24)                 |

**CMOS-8LCX**

| Block<br>Name | Description                     | l <sub>oL</sub><br>(mA) | Cells |

|---------------|---------------------------------|-------------------------|-------|

|               | Interface Blocks (Cont.)        |                         |       |

| 3V CM         | OS Output Buffers               |                         |       |

| F00A          | 3V CMOS output                  | 1.0                     | 1 (4) |

| F00B          | 3V CMOS output                  | 2.0                     | 1 (4) |

| F009          | 3V CMOS output                  | 3.0                     | 1 (4) |

| F004          | 3V CMOS output                  | 6.0                     | 1 (4) |

| F001          | 3V CMOS output                  | 9.0                     | 1 (4) |

| F002          | 3V CMOS output                  | 12.0                    | 1 (4) |

| F003          | 3V CMOS output                  | 18.0                    | 1 (8) |

| F006          | 3V CMOS output                  | 24.0                    | 1 (8) |

| FO0C          | 3V CMOS output                  | 48.0                    | 2 (8) |

| 3V CM         | OS Slew-Rate Output Buffers     |                         |       |

| FE02          | 3V CMOS output, low noise       | 12.0                    | 1 (3) |

| FE03          | 3V CMOS output, low noise       | 18.0                    | 1 (3) |

| FE06          | 3V CMOS output, low noise       | 24.0                    | 1 (3) |

| FE0C          | 3V CMOS output, low noise       | 48.0                    | 2 (3) |

| 5V CM         | OS Output Buffers               |                         |       |

| FV0A          | 5V CMOS output                  | 1.0                     | 1 (4) |

| FV0B          | 5V CMOS output                  | 2.0                     | 1 (4) |

| FV09          | 5V CMOS output                  | 3.0                     | 1 (4) |

| FV04          | 5V CMOS output                  | 6.0                     | 1 (4) |

| FV01          | 5V CMOS output                  | 9.0                     | 1 (8) |

| FV02          | 5V CMOS output                  | 12.0                    | 2 (8) |

| FV03          | 5V CMOS output                  | 18.0                    | 2 (8) |

| FV06          | 5V CMOS output                  | 24.0                    | 3 (8) |

| 5V CM         | OS Slew-Rate Output Buffers     |                         |       |

| FW02          | 5V CMOS output, Iow noise       | 12.0                    | 2 (3) |

| FW02          | 5V CMOS output, Iow noise       | 18.0                    | 2 (3) |

| FW06          | 5V CMOS output, Iow noise       | 24.0                    | 3 (3) |

|               | OS Three-State Output Buffers   |                         |       |

| B00T          | 3V CMOS output                  | 3.0                     | 1 (6) |

| B0DT          | 3V CMOS output, 50 kΩ pull-down | 3.0                     | 1 (6) |

| B0UT          | 3V CMOS output, 50 kΩ pull-up   | 3.0                     | 1 (6) |

| B0WT          | 3V CMOS output, 5 kΩ pull-up    | 3.0                     | 1 (6) |

| B00E          | 3V CMOS output                  | 6.0                     | 1 (6) |

| B0DE          | 3V CMOS output, 50 kΩ pull-down | 6.0                     | 1 (6) |

| B0UE          | 3V CMOS output, 50 kΩ pull-up   | 6.0                     | 1 (6) |

| B0WE          | 3V CMOS output, 5 kΩ pull-up    | 6.0                     | 1 (6) |

| B008          | 3V CMOS output                  | 9.0                     | 1 (6) |

| B0D8          | 3V CMOS output, 50 kΩ pull-down | 9.0                     | 1 (6) |

| B0U8          | 3V CMOS output, 50 kΩ pull-up   | 9.0                     | 1 (6) |

| B0W8          | 3V CMOS output, 5 kΩ pull-up    | 9.0                     | 1 (6) |

| B007          | 3V CMOS output                  | 12.0                    | 1 (6) |

| B0D7          | 3V CMOS output, 50 kΩ pull-down | 12.0                    | 1 (6) |

| B0U7          | 3V CMOS output, 50 kΩ pull-up   | 12.0                    | 1 (6) |

| B0W7          | 3V CMOS output, 5 kΩ pull-up    | 12.0                    | 1 (6) |

| B009          | 3V CMOS output                  | 18.0                    | 1 (9) |

| B0D9          | 3V CMOS output, 50 kΩ pull-down | 18.0                    | 1 (9) |

| B0U9          | 3V CMOS output, 50 kΩ pull-up   | 18.0                    | 1 (9) |

| B0W9          | 3V CMOS output, 5 kΩ pull-up    | 18.0                    | 1 (9) |

| B00H          | 3V CMOS output                  | 24.0                    | 1 (9) |

| B0DH          | 3V CMOS output, 50 kΩ pull-down | 24.0                    | 1 (9) |

| B0UH          | 3V CMOS output, 50 kΩ pull-up   | 24.0                    | 1 (9) |

| B0WH          | 3V CMOS output, 5 kΩ pull-up    | 24.0                    | 1 (9) |

# CMOS-8LCX

| Block | Description                                                                           |      | Cells  |

|-------|---------------------------------------------------------------------------------------|------|--------|

| Name  | Description                                                                           | (mĂ) | Cells  |

|       | Interface Blocks (Cont.)                                                              |      |        |

| 3V CM | OS Three-State Output Buffers (Cont.)                                                 |      |        |

| B00J  | 3V CMOS output                                                                        | 48.0 | 2 (9)  |

| B0DJ  | 3V CMOS output, 50 k $\Omega$ pull-down                                               | 48.0 | 2 (9)  |

| B0UJ  | 3V CMOS output, 50 k $\Omega$ pull-up                                                 | 48.0 | 2 (9)  |

| B0WJ  | 3V CMOS output, 5 k $\Omega$ pull-up                                                  | 48   | 2 (9)  |

| 3V CM | OS Slew-Rate Three-State Output Buffers                                               |      |        |

| BE07  | 3V CMOS output                                                                        | 12.0 | 1 (5)  |

| BED7  | 3V CMOS output, 50 k $\Omega$ pull-down                                               | 12.0 | 1 (5)  |

| BEU7  | 3V CMOS output, 50 k $\Omega$ pull-up                                                 | 12.0 | 1 (5)  |

| BEW7  | 3V CMOS output, 5 k $\Omega$ pull-up                                                  | 12.0 | 1 (5)  |

| BE09  | 3V CMOS output                                                                        | 18.0 | 1 (5)  |

| BED9  | 3V CMOS output, 50 kΩ pull-down                                                       | 18.0 | 1 (5)  |

| BEU9  | 3V CMOS output, 50 kΩ pull-up                                                         | 18.0 | 1 (5)  |

| BEW9  | 3V CMOS output, 5 kΩ pull-up                                                          | 18.0 | 1 (5)  |

| BE0H  |                                                                                       | 24.0 | 1 (5)  |

| BEDH  |                                                                                       | 24.0 | 1 (5)  |

| BEUH  |                                                                                       | 24.0 | 1 (5)  |

| BEWH  |                                                                                       | 24.0 | 1 (5)  |

| BE0J  | 3V CMOS output                                                                        | 48.0 | 2 (5)  |

| BEDJ  | 3V CMOS output, 50 k $\Omega$ pull-down                                               | 48.0 | 2 (5)  |

| BEUJ  | 3V CMOS output, 50 k $\Omega$ pull-up                                                 | 48.0 | 2 (5)  |

| BEWJ  | 3V CMOS output, 5 k $\Omega$ pull-down                                                | 48.0 | 2 (5)  |

| 5V CM | OS Three-State Output Buffers                                                         |      |        |

| BV0Q  | 5V CMOS output 5V CMOS output, 50 k $\Omega$ pull-down                                | 1.0  | 1 (16) |

| BVDQ  |                                                                                       | 1.0  | 1 (16) |

| BV0M  | 5V CMOS output                                                                        | 2.0  | 1 (16) |

| BVDM  | 5V CMOS output, 50 kΩ pull-down                                                       | 2.0  | 1 (16) |

| BV0T  | 5V CMOS output 5V CMOS output, 50 k $\Omega$ pull-down                                | 3.0  | 1 (16) |

| BVDT  |                                                                                       | 3.0  | 1 (16) |

| BVOE  | 5V CMOS output 5V CMOS output, 50 k $\Omega$ pull-down                                | 6.0  | 1 (16) |

| BVDE  |                                                                                       | 6.0  | 1 (16) |

| BV08  | 5V CMOS output 5V CMOS output, 50 k $\Omega$ pull-down                                | 9.0  | 1 (19) |

| BVD8  |                                                                                       | 9.0  | 1 (19) |

| BV07  | 5V CMOS output 5V CMOS output, 50 k $\Omega$ pull-down                                | 12.0 | 2 (19) |

| BVD7  |                                                                                       | 12.0 | 2 (19) |

| BV09  | 5V CMOS output                                                                        | 18.0 | 2 (19) |

| BVD9  | 5V CMOS output, 50 k $\Omega$ pull-down                                               | 18.0 | 2 (19) |

| BV0H  | 5V CMOS output                                                                        | 24.0 | 3 (19) |

| BVDH  | 5V CMOS output, 50 k $\Omega$ pull-down                                               | 24.0 | 3 (19) |

| 5V CM | OS Slew-Rate Three-State Output Buffers                                               |      |        |

| BY07  | 5V CMOS output                                                                        | 12.0 | 2 (15) |

| BYD7  | 5V CMOS output, 50 k $\Omega$ pull-down                                               | 12.0 | 2 (15) |

| BY09  | 5V CMOS output                                                                        | 18.0 | 2 (15) |

| BYD9  | 5V CMOS output, 50 k $\Omega$ pull-down                                               | 18.0 | 2 (15) |

| BY0H  | 5V CMOS ouputt 5V CMOS output, 50 k $\Omega$ pull-down                                | 24.0 | 3 (15) |

| BYDH  |                                                                                       | 24.0 | 3 (15) |

| 3V CM | OS Open Drain Output Buffers                                                          |      |        |

| EXTH  | 3V N-ch open drain 3V N-ch open drain, 50 kΩ pull-up 3V N-ch open drain, 5 kΩ pull-up | 3.0  | 1 (4)  |

| EXUH  |                                                                                       | 3.0  | 1 (4)  |

| EXWH  |                                                                                       | 3.0  | 1 (4)  |

| EXTJ  | 3V N-ch open drain                                                                    | 6.0  | 1 (4)  |

| EXUJ  | 3V N-ch open drain, 50 kΩ pull-up                                                     | 6.0  | 1 (4)  |

| EXWJ  | 3V N-ch open drain, 5 kΩ pull-up                                                      | 6.0  | 1 (4)  |

| Block<br>Name | Description                                                                                               | l <sub>oL</sub><br>(mA) | Cells |

|---------------|-----------------------------------------------------------------------------------------------------------|-------------------------|-------|

|               | Interface Blocks (C                                                                                       | cont.)                  |       |

| 3V CM         | OS Open Drain Output Buffers (Co                                                                          | ont.)                   |       |

| EXT1          | 3V N-ch open drain                                                                                        | 9.0                     | 1 (4) |

| EXT3          | 3V N-ch open drain, $50$ kΩ pull-up                                                                       | 9.0                     | 1 (4) |

| EXW3          | 3V N-ch open drain, $5$ kΩ pull-up                                                                        | 9.0                     | 1 (4) |

| EXT9          | 3V N-ch open drain                                                                                        | 12.0                    | 1 (4) |

| EXTB          | 3V N-ch open drain, 50 kΩ pull-up                                                                         | 12.0                    | 1 (4) |

| EXWB          | 3V N-ch open drain, 5 kΩ pull-up                                                                          | 12.0                    | 1 (4) |

| EXT5          | $3V$ N-ch open drain $3V$ N-ch open drain, $50$ k $\Omega$ pull-up                                        | 18.0                    | 1 (8) |

| EXT7          |                                                                                                           | 18.0                    | 1 (8) |

| EXW7          |                                                                                                           | 18.0                    | 1 (8) |

| EXTD          | $3V$ N-ch open drain, 50 k $\Omega$ pull-up                                                               | 24.0                    | 1 (8) |

| EXTF          |                                                                                                           | 24.0                    | 1 (8) |

| EXWF          |                                                                                                           | 24.0                    | 1 (8) |

| EXTL          | 1 / 1 1                                                                                                   | 48.0                    | 2 (2) |

| EXUL          |                                                                                                           | 48.0                    | 2 (8) |

| EXWL          |                                                                                                           | 48.0                    | 2 (8) |

| EXTQ          | $3V$ P-ch open drain $3V$ P-ch open drain, $50~\text{k}\Omega$ pull-dow                                   | *3.0                    | 1 (4) |

| EXDQ          |                                                                                                           | m *3.0                  | 1 (4) |

| EXTR          | $3V$ P-ch open drain $3V$ P-ch open drain, $50 \text{ k}\Omega$ pull-dow                                  | *6.0                    | 1 (4) |

| EXDR          |                                                                                                           | n *6.0                  | 1 (4) |

| EXT2          | $3V$ P-ch open drain $3V$ P-ch open drain, $50$ k $\Omega$ pull-dow                                       | *9.0                    | 1 (4) |

| EXT4          |                                                                                                           | n *9.0                  | 1 (4) |

| EXTA          | 3V P-ch open drain                                                                                        | *12.0                   | 1 (4) |

| EXTC          | $3V$ P-ch open drain, $50 \text{ k}\Omega$ pull-dow                                                       | n *12.0                 | 1 (4) |

| EXT6          | 3V P-ch open drain                                                                                        | *18.0                   | 1 (4) |

| EXT8          | $3V$ P-ch open drain, $50 \text{ k}\Omega$ pull-dow                                                       | n *18.0                 | 1 (4) |

| EXTE          | 3V P-ch open drain                                                                                        |                         | 1 (8) |

| EXTG          | $3V$ P-ch open drain, $50 \text{ k}\Omega$ pull-dow                                                       |                         | 1 (8) |

| EXTS          | 3V P-ch open drain                                                                                        | *48.0                   | 2 (8) |

| EXDS          | $3V$ P-ch open drain, $50 \text{ k}\Omega$ pull-dow                                                       | n *48.0                 | 2 (8) |