# **Power Switching Regulator**

#### **FEATURES**

- Output Switch Current in Excess of 3.0A

- Fixed Frequency Oscillator (72kHz) with **On-Chip Timing**

- **Provides 5.05V Output without External Resistor Divider**

- Precision 2% Reference

- 0% to 95% Output Duty Cycle

- **Cycle-by-Cycle Current Limiting**

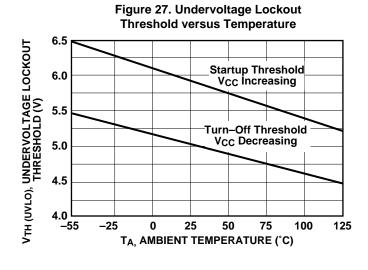

- **Undervoltage Lockout with Hysteresis**

- **■** Internal Thermal Shutdown

- Operation from 7.5V to 40V

- Standby Mode Reduces Power Supply Current to 36µA

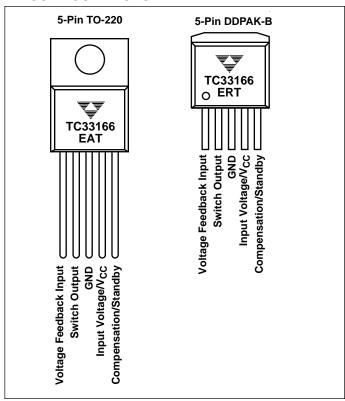

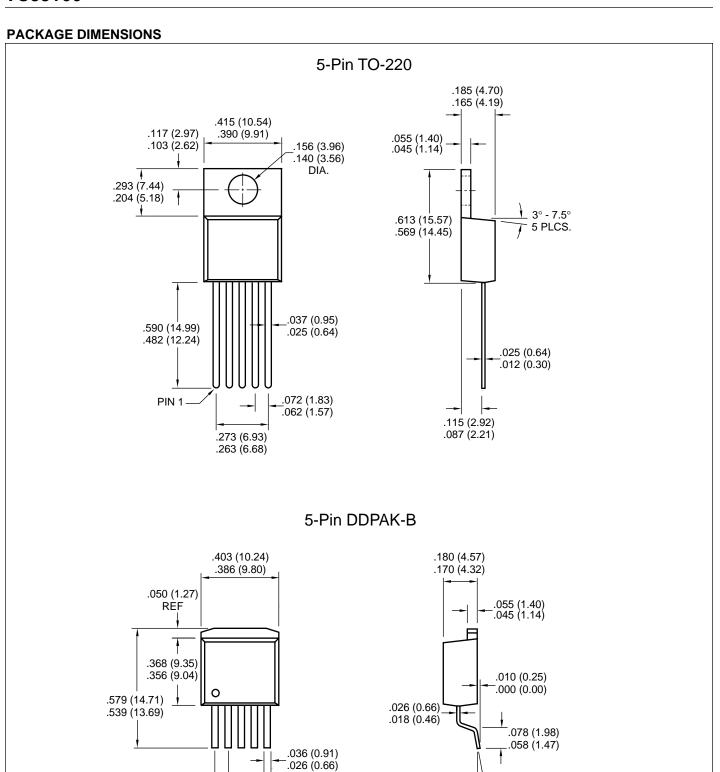

- Available in a Surface Mount 5-Pin DDPAK and 5-Pin TO-220 Packages

#### APPLICATIONS

- **Automotive**

- Computing

- **Industrial Controllers**

- **Consumer Electronics**

#### PIN CONFIGURATIONS

#### GENERAL DESCRIPTION

The TC33166 is a high performance fixed frequency power switching regulator that contains the primary functions required for DC-to-DC converters. This device was specifically designed to be incorporated in step-down and voltage-inverting configurations with a minimum number of external components and can also be used cost effectively in step-up applications.

This device consists of an internal temperature compensated reference, fixed frequency oscillator with on-chip timing components, latching pulse width modulator for single pulse metering, high gain error amplifier, and a high current output switch.

Protective features consist of cycle-by-cycle current limiting, undervoltage lockout, and thermal shutdown, Also included is a low power standby mode that reduces power supply current to 36µA.

#### ORDERING INFORMATION

| Part<br>Number | Package       | Temperature<br>Range |

|----------------|---------------|----------------------|

| TC33166ERT     | 5-Pin DDPAK-B | −40 to + 85°C        |

| TC33166EAT     | 5-Pin TO-220  | -40 to + 85°C        |

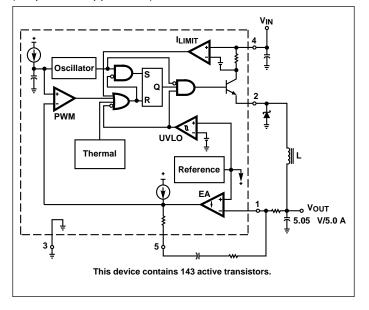

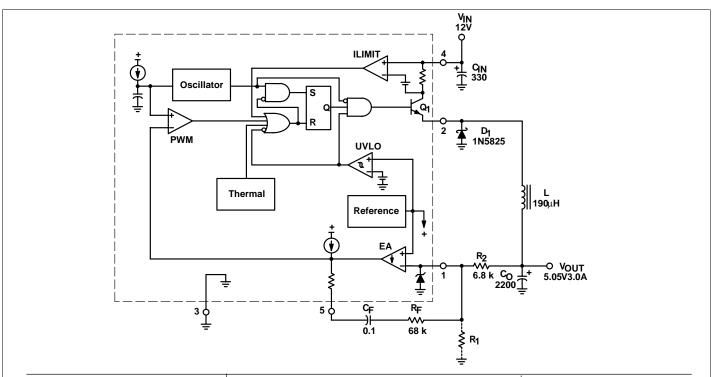

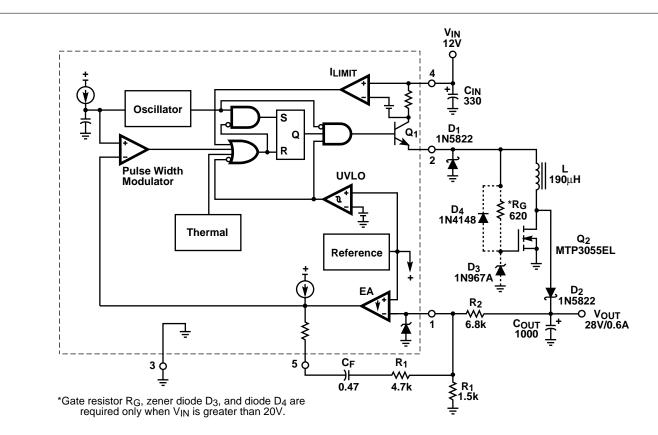

#### SIMPLIFIED BLOCK DIAGRAM

(Step Down Application)

#### **ABSOLUTE MAXIMUM RATINGS\***

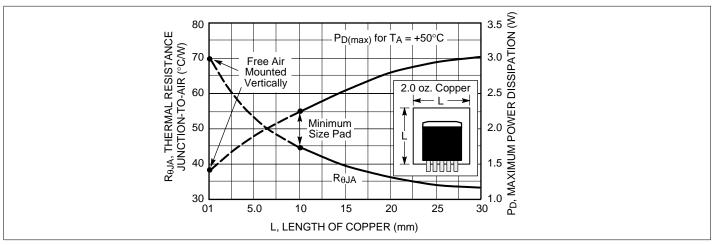

Thermal Resistance(Junction to Case) ......  $\theta_{JC} = 5.0^{\circ}$ C/W

\*This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the operation section of the specifications is not implied. Exposure to absolute maximum ratings conditions for extended periods of time may affect device reliability.

**ELECTRICAL CHARACTERISTICS:**  $V_{CC} = 12V$ , for typical values  $T_A = +25^{\circ}C$ , for min/max  $T_A$  is the operating ambient temperature range that applies [Note 2, 3], unless otherwise specified.

| Symbol               | Parameter                                                        | Test Conditions                                                                                                                        | Min  | Тур                  | Max                  | Units    |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------------|----------|

| Oscillator           |                                                                  |                                                                                                                                        |      | '                    | 1                    | •        |

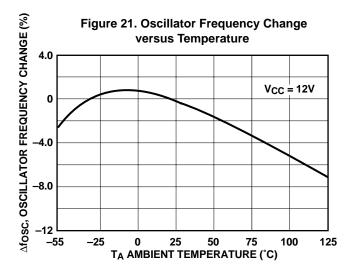

| fosc                 | Frequency (V <sub>CC</sub> 7.5V to 40V),                         | T <sub>A</sub> = +25°C                                                                                                                 | 65   | 72                   | 79                   | kHz      |

|                      |                                                                  | $T_A = T_{LOW}$ to $T_{HIGH}$                                                                                                          | 62   | _                    | 81                   |          |

| Error Ampl           | lifier                                                           |                                                                                                                                        |      |                      |                      |          |

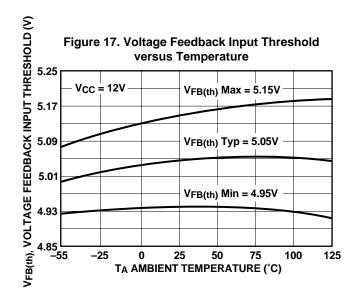

| V <sub>FB(TH)</sub>  | Voltage Feedback Input Threshold                                 | $T_A = +25^{\circ}C$                                                                                                                   | 4.95 | 5.05                 | 5.15                 | V        |

|                      |                                                                  | $T_A = T_{LOW}$ to $T_{HIGH}$                                                                                                          | 4.85 | _                    | 5.20                 |          |

| R <sub>egline</sub>  | Line Regulation                                                  | $V_{CC} = 7.5V \text{ to } 40V, T_A = +25^{\circ}C$                                                                                    | _    | 0.03                 | 0.078                | %V       |

| $I_{IB}$             | Input Bias Current                                               | $V_{FB} = V_{FB(TH)} + 0.15V$                                                                                                          |      | 0.15                 | 1.0                  | μΑ       |

| PSSR                 | Power Supply Rejection Ratio                                     | $V_{CC} = 10V \text{ to } 20V, f = 120Hz$                                                                                              | 60   | 80                   | _                    | dB       |

| V <sub>OH</sub>      | Output Voltage Swing                                             | High State (I <sub>SOURCE</sub> = 75μA,<br>V <sub>FB</sub> = 4.5V                                                                      | 4.2  | 4.9                  | _                    | V        |

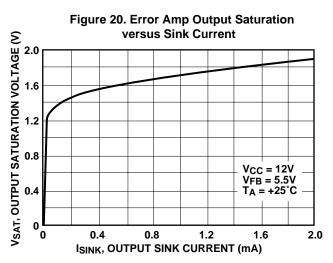

| $V_{OL}$             |                                                                  | Low State $I_{SINK} = 0.4$ mA, $V_{FB} = 5.5$ V                                                                                        | _    | 1.6                  | 1.9                  |          |

| PWM Com              | parator                                                          |                                                                                                                                        |      |                      | •                    | l.       |

| DC <sub>(MAX)</sub>  | Duty Cycle                                                       | Maximum (V <sub>FB</sub> = 0V)                                                                                                         | 92   | 95                   | 100                  | %        |

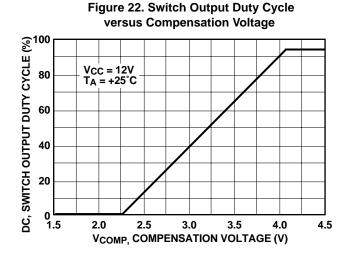

| DC <sub>(MIN)</sub>  |                                                                  | Minimum (V <sub>COMP</sub> = 1.9V)                                                                                                     | 0    | 0                    | 0                    |          |

| Switch Out           | put                                                              |                                                                                                                                        |      | _                    |                      |          |

| V <sub>SAT</sub>     | Output Voltage Source Saturation                                 | V <sub>CC</sub> = 7.5V, I <sub>SOURCE</sub> = 3.0A                                                                                     | _    | V <sub>CC</sub> -1.5 | V <sub>CC</sub> -1.8 | V        |

| I <sub>SW(OFF)</sub> | Off-State Leakage                                                | V <sub>CC</sub> = 40V, Pin 2 = GND                                                                                                     | _    | 0                    | 100                  | μΑ       |

| Ipkswitch            | H Current Limit Threshold                                        |                                                                                                                                        | 3.3  | 4.3                  | 6.0                  | Α        |

|                      | Switching Times (V <sub>CC</sub> = 40 V, I <sub>PK</sub> = 3.0A, |                                                                                                                                        |      |                      |                      | nsec     |

| $t_r$                | $L = 375\mu H, T_A = +25^{\circ}C)$                              | Output Voltage Rise Time                                                                                                               | _    | 100                  | 200                  |          |

| t <sub>r</sub>       |                                                                  | Output Voltage Fall Time                                                                                                               |      | 50                   | 100                  |          |

| Undervolta           | ge Lockout                                                       |                                                                                                                                        |      |                      |                      |          |

| $V_{TH(UVLO)}$       | Startup Threshold                                                | V <sub>CC</sub> Increasing, T <sub>A</sub> = +25°C                                                                                     | 5.5  | 5.9                  | 6.3                  | V        |

| V <sub>H(UVLO)</sub> | Hysteresis                                                       | V <sub>CC</sub> Decreasing, T <sub>A</sub> = +25°C                                                                                     | 0.6  | 0.9                  | 1.2                  | V        |

| Total Device         | e                                                                |                                                                                                                                        |      | •                    |                      |          |

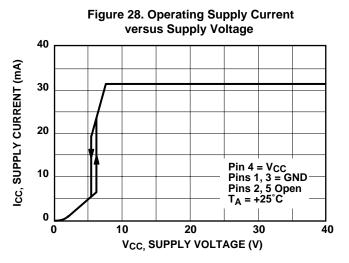

| Icc                  | Power Supply Current ( $T_A = +25^{\circ}C$ )                    |                                                                                                                                        |      |                      |                      |          |

|                      | ,,                                                               | Standby (V <sub>CC</sub> = 12V, V <sub>COMP</sub> < 0.15V)<br>Operating (V <sub>CC</sub> = 40V, Pin 1 = GND<br>for maximum duty cycle) | _    | 36<br>31             | 100<br>55            | μA<br>mA |

NOTES: 1. Maximum package power dissipation limits must be observed to prevent thermal shutdown activation.

TC33166 -1 5/25/00 2

<sup>2.</sup> Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

<sup>3.</sup>  $T_{LOW} = -40^{\circ}C$ ,  $T_{HIGH} = +85^{\circ}C$

## INTRODUCTION

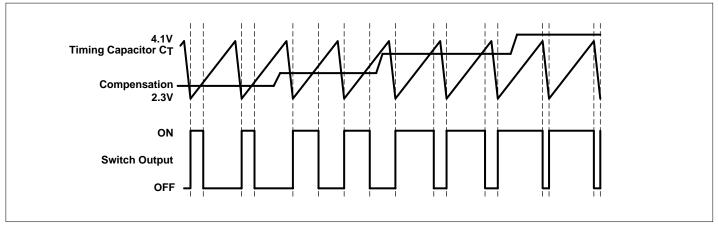

The TC33166 is a monolithic power switching regulator that is optimized for DC-to-DC converter applications. This device operates as a fixed frequency, voltage mode regulator containing all the active functions required to directly implement step—down and voltage—inverting converters with a minimum number of external components. It can also be used cost effectively in step—up converter applications. Potential markets include automotive, computer, industrial, and cost sensitive consumer products. A description of each section of the device is given below with the representative block diagram shown in Figure 1.

#### Oscillator

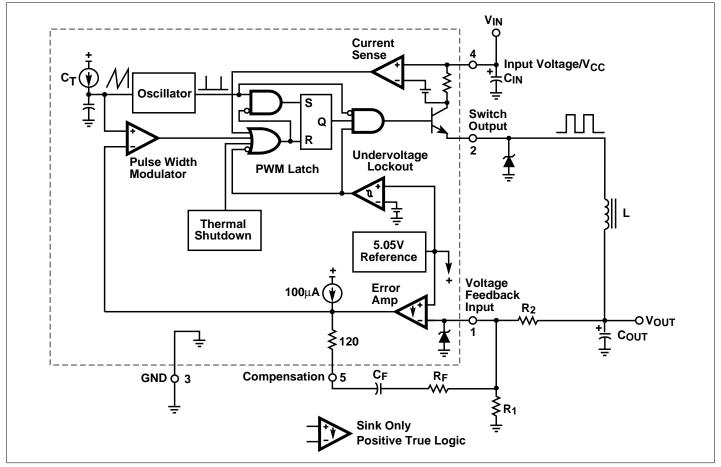

The oscillator frequency is internally programmed to 72 kHz by capacitor  $C_T$  and a trimmed current source. The charge to discharge ratio is controlled to yield a 95% maximum duty cycle at the Switch Output. During the discharge of  $C_T$ , the oscillator generates an internal blanking pulse that holds the inverting input of the AND gate high, disabling the output switch transistor. The nominal oscillator peak and valley thresholds are 4.1V and 2.3V respectively.

#### **Pulse Width Modulator**

The Pulse Width Modulator consists of a comparator with the oscillator ramp voltage applied to the noninverting input, while the error amplifier output is applied into the inverting input. Output switch conduction is initiated when C<sub>T</sub> is discharged to the oscillator valley voltage. As C<sub>T</sub> charges to a voltage that exceeds the error amplifier output, the latch resets, terminating output transistor conduction for the duration of the oscillator ramp-up period. This PWM/ Latch combination prevents multiple output pulses during a given oscillator clock cycle. Figures 2 and 22 illustrate the switch output duty cycle versus the compensation voltage.

#### **Current Sense**

The TC33166 utilizes cycle-by-cycle current limiting as a means of protecting the output switch transistor from overstress. Each on-cycle is treated as a separate situation. Current limiting is implemented by monitoring the output switch transistor current buildup during conduction, and upon sensing an overcurrent condition, immediately turning off the switch for the duration of the oscillator ramp-up period.

The collector current is converted to a voltage by an internal trimmed resistor and compared against a reference by the Current Sense comparator. When the current limit threshold is reached, the comparator resets the PWM latch.

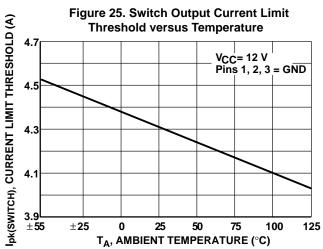

The current limit threshold is typically set at 4.3A. Figure 25 illustrates switch output current limit threshold versus temperature.

## **Error Amplifier and Reference**

A high gain Error Amplifier is provided with access to the inverting input and output. This amplifier features a typical DC voltage gain of 80dB, and a unity gain bandwidth of 600kHz with 70 degrees of phase margin (Figure 19). The noninverting input is biased to the internal 5.05V reference, and is not pinned out. The reference has an accuracy of  $\pm 2.0\%$  at room temperature. To provide 5.0V at the load, the reference is programmed 50mV above 5.0V to compensate for a 1.0% voltage drop in the cable and connector from the converter output. If the converter design requires an output voltage greater than 5.05V, resistor  $R_1$  must be added to form a divider network at the feedback input as shown in Figures 1 and 6. The equation for determining the output voltage with the divider network is:

$$V_{OUT} = 5.05 \left(\frac{R_2}{R_1}\right) + 1$$

External loop compensation is required for converter stability. A simple low-pass filter is formed by connecting a resistor  $(R_2)$  from the regulated output to the inverting input, and a series resistor-capacitor (R<sub>F</sub>, C<sub>F</sub>) between Pins 1 and 5. The compensation network component values shown in each of the applications circuits were selected to provide stability over the tested operating conditions. The stepdown converter (Figure 6) is the easiest to compensate for stability. The step-up (Figure 8) and voltage--inverting (Figure 10) configurations operate as continuous conduction flyback converters, and are more difficult to compensate. The simplest way to optimize the compensation network is to observe the response of the output voltage to a step load change, while adjusting R<sub>F</sub> and C<sub>F</sub> for critical damping. The final circuit should be verified for stability under four boundary conditions. These conditions are minimum and maximum input voltages, with minimum and maximum loads.

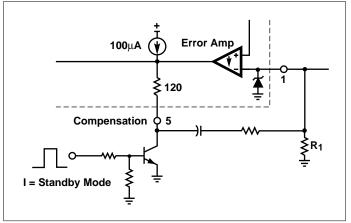

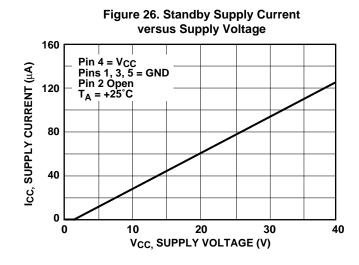

By clamping the voltage on the error amplifier output (Pin 5) to less than 150mV, the internal circuitry will be placed into a low power standby mode, reducing the power supply current to  $36\mu A$  with a 12V supply voltage. Figure 26 illustrates the standby supply current versus supply voltage.

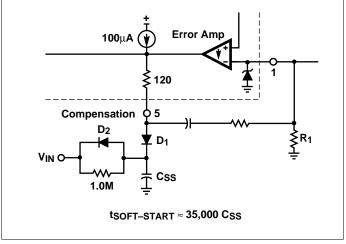

The Error Amplifier output has a  $100\mu A$  current sourcepull-up that can be used to implement soft-start. Figure 5 shows the current source charging capacitor  $C_{SS}$  through a series diode. The diode disconnects  $C_{SS}$  from the feedback loop when the 1.0M resistor charges it above the operating range of Pin 5.

Figure 1. Representative Block Diagram

Figure 2. Timing Diagram

## **Switch Output**

The output transistor is designed to switch a maximum of 40V, with a minimum peak collector current of 3.3 A. When configured for step-down or voltage-inverting applications, as in Figures 6 and 10, the inductor will forward bias the output rectifier when the switch turns off. Rectifiers with a high forward voltage drop or long turn-on delay time should not be used. If the emitter is allowed to go sufficiently negative, collector current will flow, causing additional device heating and reduced conversion efficiency. Figure 24 shows that by clamping the emitter to 0.5 V, the collector current will be in the range of  $100\mu A$  over temperature. A 1N5825 or equivalent Schottky barrier rectifier is recommended to fulfill these requirements.

## **Undervoltage Lockout**

An Undervoltage Lockout comparator has been incorporated to guarantee that the integrated circuit is fully functional before the output stage is enabled. The internal reference voltage is monitored by the comparator which enables the output stage when  $V_{CC}$  exceeds 5.9V. To prevent erratic output switching as the threshold is crossed, 0.9V of hysteresis is provided.

#### **Thermal Protection**

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 170°C the latch is forced into a 'reset' state, disabling the output switch. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heatsinking. The TC33166 is contained in a 5-Pin TO-220 type package. The tab of the package is common with the center pins (Pin 3) and is normally connected to ground.

#### **DESIGN CONSIDERATIONS**

Do not attempt to construct a converter on wirewrap or plug-in prototype boards. Special care should be taken to separate ground paths from signal currents and ground paths from load currents. All high current loops should be kept as short as possible using heavy copper runs to minimize ringing and radiated EMI. For best operation, a tight component layout is recommended. Capacitors  $C_{\text{IN}}$ ,  $C_{\text{OUT}}$ , and all feedback components should be placed as close to the IC as physically possible. It is also imperative that the Schottky diode connected to the Switch Output be located as close to the IC as possible.

Figure 3. Low Power Standby Circuit

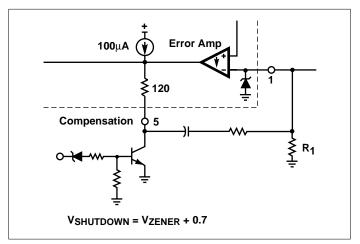

Figure 4. Over Voltage Shutdown Circuit

Figure 5. Soft-Start Circuit

5

| Test                  | Conditions                                      | Results                      |

|-----------------------|-------------------------------------------------|------------------------------|

| Line Regulation       | $V_{IN} = 8.0V \text{ to } 36V, I_{OUT} = 3.0A$ | $5.0 \text{mV} = \pm 0.05\%$ |

| Load Regulation       | $V_{IN} = 12V$ , $I_{OUT} = 0.25A$ to 3.0A      | $2.0$ mV = $\pm 0.02\%$      |

| Output Ripple         | $V_{IN} = 12V, I_{OUT} = 3.0A$                  | 10mVpp                       |

| Short Circuit Current | $V_{IN} = 12V, R_{L} = 0.1\Omega$               | 4.3A                         |

| Efficiency            | $V_{IN} = 12V, I_{OUT} = 3.0A$                  | 82.8%                        |

L = Coilcraft M1496–A or General Magnetics Technology GMT–0223, 42 turns if #16 AWG on Magnetics Inc. 58350–A2 core. Heatsink = AAVID Engineering Inc. 5903B, or 5930B.

The Step–Down Converter application is shown in Figure above. The output switch transistor Q1 interrupts the input voltage, generating squarewave at the  $LC_0$  filter input. The filter averages the squarewaves, producing a DC output voltage that can be set to any level between  $V_{IN}$  and  $V_{REF}$  by controlling the percent conduction time of Q1 to that of the total oscillator cycle time. If the converter design requires an output voltage greater than 5.05V, resistor  $R_1$  must be added to form a divider network at the feedback input.

3.0,

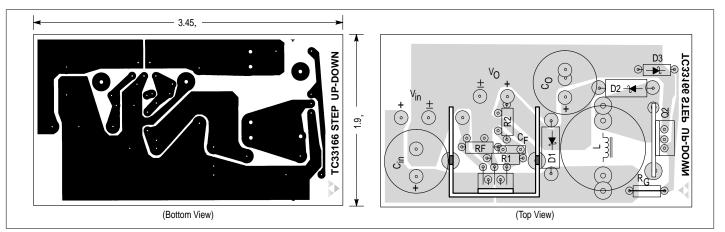

TC33166 STEP±DOWN

TC3316 STEP±DOWN

TC3316 STEP±DOWN

TC3316 STEP±DOWN

Figure 6. Step-Down Converter

Figure 7. Step-Down Converter Printed Circuit Board and Component Layout

6

(Top View)

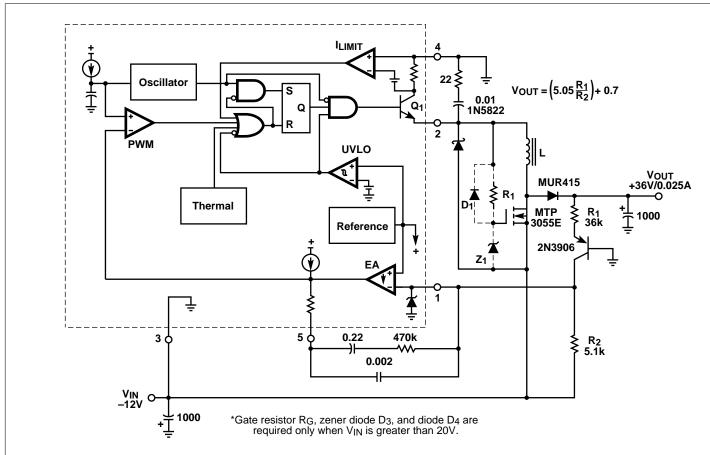

| Test                  | Conditions                                      | Results                       |

|-----------------------|-------------------------------------------------|-------------------------------|

| Line Regulation       | $V_{IN} = 8.0V \text{ to } 24V, I_{OUT} = 0.6A$ | 23mV = ±0.41%                 |

| Load Regulation       | $V_{IN} = 12V$ , $I_{OUT} = 0.1A$ to 0.6A       | $3.0 \text{mV} = \pm 0.005\%$ |

| Output Ripple         | $V_{IN} = 12V, I_{OUT} = 0.6A$                  | 100mVpp                       |

| Short Circuit Current | $V_{IN} = 12V, R_L = 0.1\Omega$                 | 4.0A                          |

| Efficiency            | $V_{IN} = 12V, I_{OUT} = 0.6A$                  | 82.8%                         |

L = Coilcraft M1496–A or General Magnetics Technology GMT–0223, 42 turns if #16 AWG on Magnetics Inc. 58350–A2 core. Heatsink = AAVID Engineering Inc.

TC34166: 5903B, or 5930B MTP3055EL: 5925B

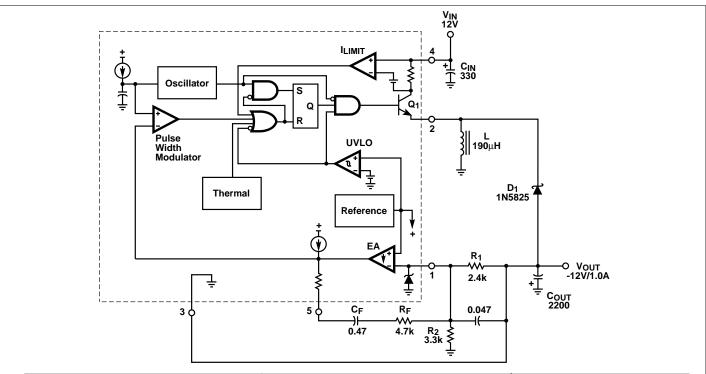

Figure above shows that the TC33166 can be configured as a step–up/down converter with the addition of an external power MOSFET. Energy is stored in the inductor during the ON time of transistors Q1 and Q2 . During the OFF time, the energy is transferred, with respect to ground, to the output filter capacitor and load. This circuit configuration has two significant advantages over the basic step–up converter circuit. The first advantage is that output short -circuit protection is provided by the TC33166, since Q1 is directly in series with  $V_{IN}$  and the load. Second, the output voltage can be programmed to be less than  $V_{IN}$ . Notice that during the OFF time, the inductor forward biases diodes  $D_1$  and  $D_2$ , transferring its energy with respect to ground rather than with respect to  $V_{IN}$ . When operating with  $V_{IN}$  greater than 20V, a gate protection network is required for the MOSFET. The network consists of components  $R_G$ ,  $D_3$ , and  $D_4$ .

Figure 8. Step-Up / Down Converter

7

TC33066 -1 5/25/00

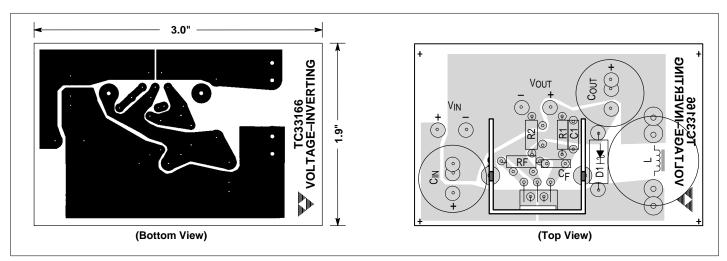

Figure 9. Step-Up/Down Converter Printed Circuit Board and Component Layout

| Test                  | Conditions                                     | Results                  |

|-----------------------|------------------------------------------------|--------------------------|

| Line Regulation       | $V_{IN} = 8V \text{ to } 24V, I_{OUT} = 1.0A$  | 1.5mV = ±0.01%           |

| Load Regulation       | $V_{IN} = 12V$ , $I_{OUT} = 0.1A$ to 1.0A      | $4.0$ mV = $\pm 0.017$ % |

| Output Ripple         | $V_{IN} = 12V, I_{OUT} = 1.7A$                 | 80mVpp                   |

| Short Circuit Current | $V_{IN} = 12V, R_L = 0.1\Omega$                | 3.74A                    |

| Efficiency            | V <sub>IN</sub> = 12V, I <sub>OUT</sub> = 1.0A | 81.2%                    |

L = Coilcraft M1496–A or General Magnetics Technology GMT–0223, 42 turns if #16 AWG on Magnetics Inc. 58350–A2 core. Heatsink = AAVID Engineering Inc. 5903B, or 5930B.

Two potential problems arise when designing the standard voltage—inverting converter with the TC33166. First, the Switch Output emitter is limited to -1.5V with respect to the ground pin and second, the Error Amplifier's noninverting input is internally committed to the reference and is not pinned out. Both of these problems are resolved by connecting the IC ground pin to the converter's negative output as shown in Figure 10. This keeps the emitter of Q1 positive with respect to the ground pin and has the effect of reversing the Error Amplifier inputs. Note that the voltage drop across  $R_1$  is equal to 5.05V when the output is in regulation.

Figure 10. Voltage Inverting Converter

Figure 11. Voltage-Inverting Converter Printed Circuit Board and Component Layout

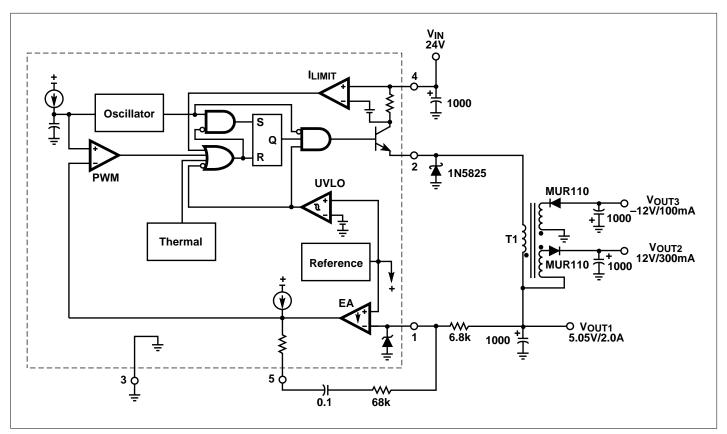

Figure 12. Triple Output Converter

9

## **Power Switching Regulator**

## TC33166

| Tests                 |                     | Conditions                                                                                                                                                                                                                                                          | Results                                                                     |

|-----------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Line Regulation       | 5.0V<br>12V<br>–12V | $V_{IN}$ = 15V to 30V, $I_{OUT1}$ = 2.0A, $I_{OUT2}$ = 300mA, $I_{OUT3}$ = 100mA                                                                                                                                                                                    | $4.0$ mV = $\pm 0.04$ %<br>$450$ mV = $\pm 1.9$ %<br>$350$ mV = $\pm 1.5$ % |

| Load Regulation       | 5.0V<br>12V<br>–12V | $V_{IN} = 24V$ , $I_{OUT1} = 500$ mA to 2.0A, $I_{OUT2} = 300$ mA, $I_{OUT3} = 100$ mA $V_{IN} = 24V$ , $I_{OUT1} = 2.0$ A, $I_{OUT2} = 100$ mA to 250mA, $I_{OUT3} = 200$ mA $V_{IN} = 24V$ , $I_{OUT1} = 2.0$ A, $I_{OUT2} = 300$ mA, $I_{OUT3} = 30$ mA to 100mA | $2.0$ mV = $\pm 0.02$ %<br>$420$ mV = $\pm 1.7$ %<br>$310$ mV = $\pm 1.3$ % |

| Output Ripple         | 5.0V<br>12V<br>–12V | $V_{IN} = 24V$ , $I_{OUT1} = 2.0A$ , $I_{OUT2} = 300mA$ , $I_{OUT3} = 100mA$                                                                                                                                                                                        | 50mV <sub>PP</sub><br>25mV <sub>PP</sub><br>10mV <sub>PP</sub>              |

| Short Circuit Current | 5.0V<br>12V<br>–12V | $V_{IN} = 24V$ , $R_L = 0.1\Omega$                                                                                                                                                                                                                                  | 4.3A<br>1.83A<br>1.47A                                                      |

| Efficiency            | TOTAL               | V <sub>IN</sub> = 24V, I <sub>OUT1</sub> = 2.0A, I <sub>OUT2</sub> = 300mA, I <sub>OUT3</sub> = 100mA                                                                                                                                                               | 83.3%                                                                       |

T1 = Primary: Coilcraft M1496-A or General Magnetics Technology GMT-0223, 42 turns of #16 AWG on Magnetics Inc. 58350-A2 core.

Secondary: V<sub>OUT2</sub> — 65 turns of #26 AWG — 96 turns of #28 AWG

Heatsink = AAVID Engineering Inc. 5903B, or 5930B.

Multiple auxiliary outputs can easily be derived by winding secondaries on the main output inductor to form a transformer. The secondaries must be connected so that the energy is delivered to the auxiliary outputs when the Switch Output turns off. During the OFF time, the voltage across the primary winding is regulated by the feedback loop, yielding a constant Volts/Turn ratio. The number of turns for any given secondary voltage can be calculated by the following equation:

$$\# TURNS_{(SEC)} = \underbrace{\frac{V_{OUT(SEC)} + V_{F(SEC)}}{V_{OUT(PRI)} + V_{F(PRI)}}}_{\# TURNS_{(PRI)}}$$

Note that the 12 V winding is stacked on top of the 5.0V output. This reduces the number of secondary turns and improves lead regulation. For best auxiliary regulation, the auxiliary outputs should be less than 33% of the total output power.

L = Coilcraft M1496–A or General Magnetics Technology GMT–0223, 42 turns if #16 AWG on Magnetics Inc. 58350–A2 core. Heatsink = AAVID Engineering Inc. 5903B, or 5930B.

TC33166 -1 5/25/00 10

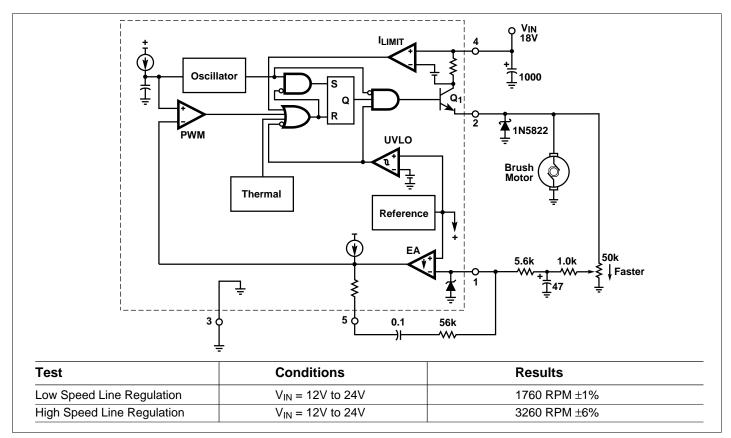

| Test            | Conditions                                        | Results            |

|-----------------|---------------------------------------------------|--------------------|

| Line Regulation | $V_{IN} = -10V \text{ to } -20V, I_{OUT} = 0.25A$ | 250mV = ± 0.35%    |

| Load Regulation | $V_{IN} = -12V$ , $I_{OUT} = 0.025A$ to 0.25A     | 790mV = ±1.19%     |

| Output Ripple   | $V_{IN} = -12V$ , $I_{OUT} = 0.25A$               | 80mV <sub>PP</sub> |

| Efficiency      | $V_{IN} = -12V$ , $I_{OUT} = 0.25A$               | 79.2%              |

L = Coilcraft M1496–A or ELMACO CHK1050, 42 turns of #16 AWG on Magnetics Inc. 58350–A2 core. Heatsink = AAVID Engineering Inc. 5903B or 5930B

Figure 13. Negative Input/Positive Output Regulator

11

TC33066 -1 5/25/00

Figure 14. Variable Motor Speed Control with EMF Feedback Sensing

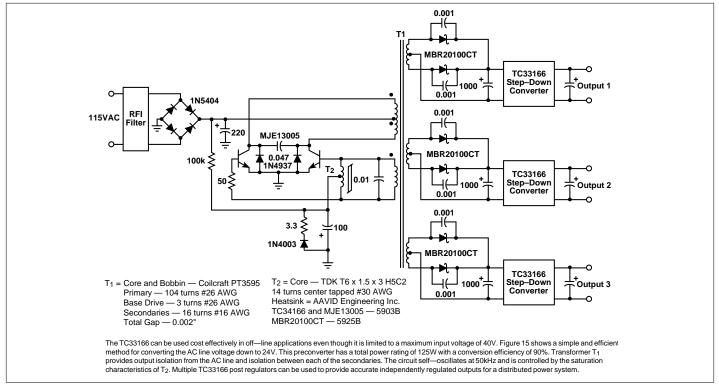

Figure 15. Off-Line Preconverter

Figure 16. DDPAK Thermal Resistance and Maximum Power Dissipation vs. P.C.B. Copper Length

## **Design Equation Table**

| Calculation                  | Step-Down                                                                                              | Step-Up/Down                                                                                               | Voltage-Inverting                                                                          |

|------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| tON_<br>tOFF<br>(Notes 1, 2) | VOUT — VF<br>VIN — VSAT — VOUT                                                                         | VOUT — VF1 + VF2<br>VIN — VSATQ1 — VSATQ2                                                                  | VOUT +VF<br> VIN — VSAT                                                                    |

| <sup>t</sup> ON              | $ \frac{\frac{^{t}ON}{^{t}OFF}}{f_{OSC}\left(\frac{^{t}ON}{^{t}OFF}+1\right)} $                        | $\frac{\frac{{}^{t}ON}{{}^{t}OFF}}{{}^{f}OSC}\left(\frac{{}^{t}ON}{{}^{t}OFF}+1\right)$                    | $\frac{\frac{{}^{t}ON}{{}^{t}OFF}}{{}^{f}OSC}\left(\frac{{}^{t}ON}{{}^{t}OFF}+1\right)$    |

| Duty Cycle<br>(Note 3)       | ton fosc                                                                                               | <sup>t</sup> ON <sup>f</sup> OSC                                                                           | ton fosc                                                                                   |

| l <sub>Lavg</sub>            | I <sub>OUT</sub>                                                                                       | $I_{OUT} \left( t_{OFF}^{tON} + 1 \right)$                                                                 | $I_{OUT} \left( t_{OFF}^{tON} + 1 \right)$                                                 |

| Ipk <sub>(SWITCH)</sub>      | $I_{L \text{ avg }} + \frac{\Delta I_{L}}{2}$                                                          | $I_{L \text{ avg }} + \frac{\Delta I_{L}}{2}$                                                              | $^{\rm I}$ L avg $+\frac{\Delta ^{\rm I}}{2}$                                              |

| L                            | $\left(\frac{V_{\text{IN}}-V_{\text{SAT}}-V_{\text{OU}}T}{\Delta I_{\text{L}}}\right)_{t_{\text{ON}}}$ | $\left(\frac{V_{\text{IN}}-V_{\text{SATQ1}}-V_{\text{SATQ2}}}{\Delta I_{\text{L}}}\right)^{t}_{\text{ON}}$ | $\left(\frac{V_{\text{IN}}-V_{\text{SA}}T}{\Delta I_{\text{L}}}\right)^{t_{\text{ON}}}$    |

| V <sub>RIPPLE</sub> (pp)     | $\Delta I_L \sqrt{\left(\frac{1}{8 \text{fosc C}_0}\right)^2 + (ESR)^2}$                               | $\left(\frac{t_{ON}}{t_{OFF}} + 1\right) \sqrt{\left(\frac{1}{t_{OSC}C_O}\right)^2 + (ESR)^2}$             | $\left(t_{OFF}^{tON} + 1\right)\sqrt{\left(\frac{1}{t_{OSC}C_{O}}\right)^{2} + (ESR)^{2}}$ |

| Vouт                         | $V_{REF}\left(\frac{R_2}{R_1} + 1\right)$                                                              | $V_{REF}\left(\frac{R_2}{R_1} + 1\right)$                                                                  | $V_{REF}\left(\frac{R_2}{R_1} + 1\right)$                                                  |

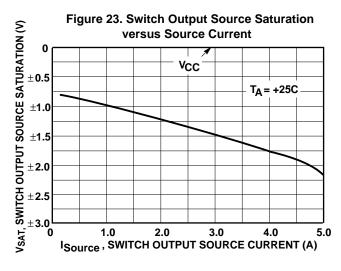

$\textbf{NOTES:} \ 1. \ V_{SAT} - Switch \ Output \ source \ saturation \ voltage, \ refer \ to \ Figure \ 23$

- $2.\ V_F-Output\ rectifier\ forward\ voltage\ drop.\ Typical\ value\ for\ 1N5822\ Schottky\ barrier\ rectifier\ is\ 0.5V.$

- 3. Duty cycle is calculated at the minimum operating input voltage and must not exceed the guaranteed minimum DC (max) specification of 0.92. The following converter characteristics must be chosen:

- V<sub>OUT</sub> Desired output voltage.

- I<sub>OUT</sub> Desired output current.

- $\Delta I_L$  Desired peak-to-peak inductor ripple current. For maximum output current especially when the duty cycle is greater than 0.5, it is suggested that  $\Delta I_L$  be chosen minimum current limit threshold of 3.3A. If the design goal is to use a minimum inductance value, let  $\Delta I_L$  = 2 ( $I_L$ avg). This will proportionally reduce the converter's output current capability.

- VRIPPLE(pp) Desired peak-to-peak output ripple voltage. For best performance, the ripple voltage should be kept to less than 2% of V<sub>OUT</sub>. Capacitor C<sub>O</sub> should be a low equivalent series resistance (ESR) electrolytic designed for switching regulator applications.

TC33066 -1 5/25/00 13

### TYPICAL CHARACTERISTICS

Figure 18. Voltage Feedback Input Bias **Current versus Temperature** 100 IIB, INPUT BIAS CURRENT (nA) **V<sub>CC</sub>** = 12V 80 VFB = VFB(th) 60 40 20 -55 -25 25 50 75 100 125 TA AMBIENT TEMPERATURE (°C)

Figure 19. Error Amp Open Loop Gain and **Phase versus Frequency** 100 Avol, OPEN LOOP VOLTAGE (dB) Vcc = 12V V<sub>COMP</sub> = 3.25V R<sub>L</sub> = 100k **EXCESS PHASE (DEGREES)** 80 30 Gain  $T_A = +25^{\circ}C$ 60 60 40 90 Phase 20 120 150 0 180 10 100 1.0k 10k 100k 1.0M 10M f, FREQUENCY (Hz)

TC33166 -1 5/25/00 14

#### TYPICAL CHARACTERISTICS

Figure 24. Negative Switch Output Voltage versus Temperature VOLTAGE (V) GND 0.2 V<sub>CC</sub> = 12V Pin 5 = 2.0V Pins 1, 3 = GND Pin 2 Driven Negative SWITCH OUTPUT Isw =  $100\mu$ A -0.6 -0.8 Isw = 10mA 1.0 Vsw, -25 --55 0 25 50 75 100 125 TA, AMBIENT TEMPERATURE (°C)

TC33066 -1 5/25/00 15

Dimensions: inches (mm)

5° REF

.067 (1.70) BSC.

# **Power Switching Regulator**

TC33166

### **Sales Offices**

TelCom Semiconductor, Inc. 1300 Terra Bella Avenue P.O. Box 7267 Mountain View, CA 94039-7267 TEL: 650-968-9241 FAX: 650-967-1590

E-Mail: liter@telcom-semi.com

TelCom Semiconductor, GmbH Lochhamer Strasse 13 D-82152 Martinsried Germany TEL: (011) 49 89 895 6500 FAX: (011) 49 89 895 6502 2 **TelCom Semiconductor H.K. Ltd.**10 Sam Chuk Street, Ground Floor San Po Kong, Kowloon

Hong Kong

TEL: (011) 852-2350-7380

FAX: (011) 852-2354-9957