# DATA SHEET

## t8566(7) Multi-window graphic On-Screen-Display

Preliminary specification Video Display Product Series **April** 1999

## trumpion microelectronics

3 " 1 ¤

trumpion microelectronics Preliminary specification

## Multi-window graphic On-Screen-Display

t8566(7)

| CONT                                                                       | TENTS                                                                                                                                                                          | 10.5                               | The Programmable PLL (applicable only for                                                             |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|

| 1                                                                          | FEATURES                                                                                                                                                                       |                                    | t8566(7))                                                                                             |

| 2                                                                          | GENERAL DESCRIPTION                                                                                                                                                            | 10.6<br>10.6.1<br>10.6.2<br>10.6.3 | ROM Code Generation<br>Normal Character Font code<br>Graphic Character Font Code<br>The Standard Code |

| 3                                                                          | ORDERING INFORMATION                                                                                                                                                           |                                    |                                                                                                       |

| 4                                                                          | PIN CONFIGURATION                                                                                                                                                              | 11                                 | PACKAGE OUTLINE                                                                                       |

| 5                                                                          | PIN DISCRIPTION                                                                                                                                                                | 12                                 | SOLDERING                                                                                             |

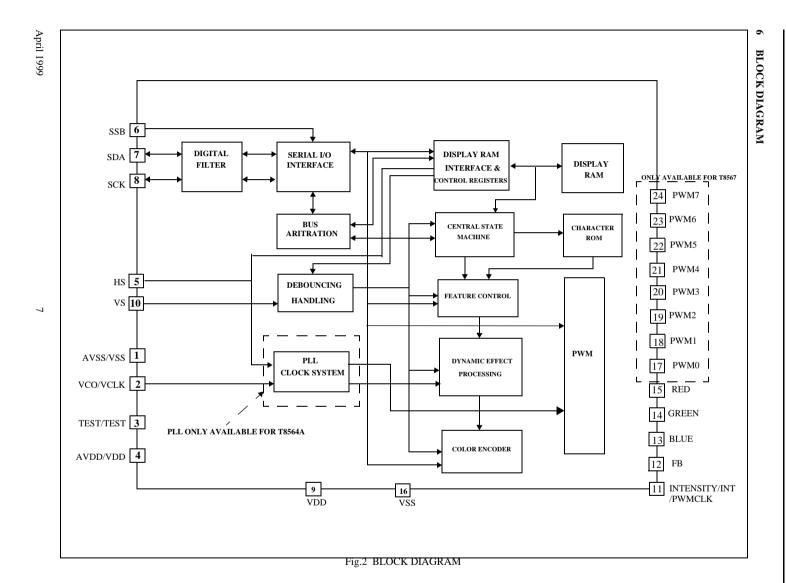

| 6                                                                          | BLOCK DIAGRAM                                                                                                                                                                  |                                    |                                                                                                       |

| 7                                                                          | ABSOLUTE MAXIMUM RATINGS                                                                                                                                                       |                                    |                                                                                                       |

| 8                                                                          | DC CHARACTERISTICS                                                                                                                                                             |                                    |                                                                                                       |

| 9                                                                          | AC CHARACTERISTICS                                                                                                                                                             |                                    |                                                                                                       |

| 10                                                                         | FUNCTIONAL DESCRIPTION                                                                                                                                                         |                                    |                                                                                                       |

| 10.1                                                                       | Display RAM content mapped to Screen management                                                                                                                                |                                    |                                                                                                       |

| 10.2<br>10.2.1<br>10.2.1.1<br>10.2.1.2<br>10.2.1.3<br>10.2.1.4<br>10.2.1.5 | The data structure in Display RAM The ROW Attribute The End of Display The Shadow Mode The Double width and/or Double Height The Programmable Character Height The Row Spacing |                                    |                                                                                                       |

| 10.2.2                                                                     | The SPACE code                                                                                                                                                                 |                                    |                                                                                                       |

| 10.2.3                                                                     | The Character Font Code                                                                                                                                                        |                                    |                                                                                                       |

| 10.3                                                                       | Control Registers                                                                                                                                                              |                                    |                                                                                                       |

| 10.4<br>10.4.1<br>10.4.2                                                   | The Communication Protocol<br>SPI interface<br>I <sup>2</sup> C interface                                                                                                      |                                    |                                                                                                       |

t8566(7)

#### 1 FEATURE

#### Y Screen Attributes:

- Very wide OSD menu moving range for high resolution chassis: maximum up to <u>2048 dots</u>, <u>2048 scan lines</u> for horizontal and vertical position respectively; <u>OSD menu can penetrate</u> the border of the screen

- Programmable horizontal and vertical positioning step: 2 dots (2 scan lines), 4 dots (4 scan lines), 6 dots (6 scan lines), 8 dots(8 scan lines) per step respectively.

- Wipe-In / Wipe-out effect can be optionally enabled with 2 selectable directions (from top left corner to bottom right corner or vice verse)

- Programmable wipeing rate: maximum wiping time: 0.5 sec, or 0.25 sec.

- The <u>built-in SP code</u> associated with boxing background color can produce multiple windows and <u>relieve software load</u> for creating background color underneath foreground character; up to <u>16 background color</u> supported

- Built-in dynamic transparent effect for background color defined by SP code without the external color blending circuit

- Up to **6 deticated hardware windows** with window shadow effect

- Programmable window shadow height and width, individully controllable

- Selectable window shadow color out of 4 colors; each window can select different shadow color

- 16 color selection, including intensity attribute, for each window

- The display outside the windows and be masked: the wipe in/out effect from the center can be achieved through this feature

- Built-in Half Tone effect for each window without the external color blending circuit

- Character basis background color change with 8 color selections; 16 color selections by row basis

- Software flag to clear the screen display

Y Multi-sync application supports:

- Wide Horizontal sync range from 15 KHz to  ${\bf 200~KHz}$

- An internal PLL which generates pixel clock ranged from 6.25 to 96 MHz

- Programmable character height, not only for scaling up (18 to 66 lines) but also **scaling down** (5, 9, 10, 13 lines)

- Double Character Height and Double Character Width, programmable individually by row based control

- Hardware Row to Row spacing by row based control

Y Number of Character fonts

- Total 255 character fonts plus one dedicated Space code

- Flexible memory partitioning to allocate desired number of Normal Character Fonts (NCF) and Graphic Character Fonts (GCF); the number of NCF and GCF can be customized and dependent of the application needs.

Υ Display dimension:

- 16 (rows) by 31 (columns)

- Fixed display format for easy screen arrangement

- On Screen Display can start from any row, which will facilitate the arrangement of preloaded multiple menu segments in different Display RAM area and then displayed by the pointer

- **Scrolling effect** can be emulated through this flexible architecture

- The Display RAM and internal registers are readable through SPI or I2C interface so that huge

t8566(7)

memory resource can be used as buffer and shared for other purposes

#### Y Character attributes:

- 12 X 18 dot matrix

- No clearance between characters; higher resolution character fonts or some special graphic pattern/icon can be designed by combining two, three or more characters

- <u>16 color selection</u>, including intensity attribute, per display <u>character basis</u>

- **16 color selection**, including intensity attribute, for character background, per word basis

- 8 color selection, for individual character background, **16 color selection per row basis**

- Row based character Bordering or Shadowing from 8 programmable directions

- Character based blinking function with **2** different rates

#### Y Proprietary adaptive approach to handle H, V sync collision automatically by internal hardware

Y Industrial standard SPI or I2C interface with default slave address, F4H (SPI, I2C and slave address can be selected by mask option)

Y 8 X 8 bits PWM DAC outputs (applicable only for t8567)

Y 24 pins (for t8567) or 16 pins PDIP package or 16 pins SO package

#### 2 GENERAL DESCRIPTION

The t8566(7) stand alone OSD is designed to interface with microcontroller to display colored patterns, icons or characters onto display devices like TV, CRT monitor or LCD monitor. Since 256 character fonts (including one space code) are provided internally, it can cover the application of Multi-language TV/Monitor. The Graphic Character Fonts can produce the effect of the pixel based graphic display, which allows the impressive display of the customized pattern. symbols or logos. The large display RAM with fixed columns, rows, will relieve CPU from the overhead of screen refreshing.

The internal PLL system associated with the versatile programmable character height is particularly suitable for multi-scan application. Through those features, the desired aspect ratio can be achieved during mode change.

Meanwhile, t8566(7) also provides plentiful features to enhance the appearance of the displayed character fonts. Each character can have its own colors (up to 16 colors) and blinking option. Up to 10 shadowing modes (including bordering, boxing etc.) are provided together with 16 background colors. Multiple overlapping windows, and wipe-in or wipe-out from two directions can create more flexible user interface. The internal built-in half tone function can create the see-through effect without the intervention of the external circuit.

Some handy hardware design tackling some common application issues like the detection and automatic adjustment of Hsync and Vsync collision, the special handling while Hsync or Vsync coming before display finished, can minimizes the efforts of the application supports.

For t8567, 8 X 8 bits PWM DAC are available to provide DC voltage control for other peripherals like R, G, B bias, gain etc.

t8566(7)

PDIP 16

ORDER INFORMATION T8566A PLASTIC PACKAGE

**SO16**

ORDER INFORMATION

T8566B PLASTIC PACKAGE

#### 3 ORDERING INFORMATION

| ТҮРЕ   |      | PACKAG      | <del>S</del> E | темр.               | FREO.      |

|--------|------|-------------|----------------|---------------------|------------|

| NO.    | PINS | PKG<br>TYPE | MATE<br>RIAL   | (T <sub>A</sub> ,C) | (MHZ)      |

| t8566A | 16   | PDIP        | plastic        | 0 to +70            | 6.25 to 96 |

| t8566B | 16   | SOP         | plastic        | 0 to +70            | 6.25 to 96 |

| t8567  | 24   | PDIP        | plastic        | 0 to +70            | 6.25 to 96 |

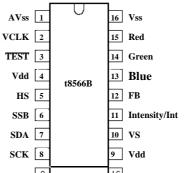

#### 4 PIN CONFIGURATION

Fig.1 PIN Configuration for DIP16, DIP24 and SO16

t8566(7)

#### 5 PIN DESCRIPTION

| 5 FINDESC                 |      |            |         |           |                                                                                                                                                                                            |

|---------------------------|------|------------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL                    | I/O  | PDIP<br>16 | PDIP 24 | SOP<br>16 | DESCRIPTION                                                                                                                                                                                |

| AVss/Vss                  | S    | 1          | 1       | 1         | Analog Vss for t8566A and t8567.                                                                                                                                                           |

|                           |      |            |         |           | Digital Vss for t8566B.                                                                                                                                                                    |

| VCO/VCLK                  | IO/I | 2          | 2       | 2         | Loop Filter connected to the internal Voltage Controlled Oscillator for t8566A and t8567.                                                                                                  |

|                           |      |            |         |           | Driving Clock from the external side for t8566B.                                                                                                                                           |

| TEST/TEST                 | I    | 3          | 3       | 3         | TEST pin; Active High for t8566A and t8567, pulled down internally.                                                                                                                        |

|                           |      |            |         |           | TEST pin; Active Low for t8566B; must be tied to High for normal operation.                                                                                                                |

| AVdd/Vdd                  | S    | 4          | 4       | 4         | Analog 5 Volt DC supply for t8566A and t8567.                                                                                                                                              |

|                           |      |            |         |           | Digital 5 Volt DC supply for t8566B                                                                                                                                                        |

| HS                        | I    | 5          | 5       | 5         | Horizontal Sync input; TTL level with Schmitt leading edge triggered                                                                                                                       |

| SSB                       | I    | 6          | 6       | 6         | SPI interface enable pin; Active low, pulled up internally. For I <sup>2</sup> C interface, just keep it floating or tied to high.                                                         |

| SDA                       | IO   | 7          | 7       | 7         | Serial data input/output pin.                                                                                                                                                              |

| SCK                       | IO   | 8          | 8       | 8         | Serial transfer clock pin.                                                                                                                                                                 |

| Vdd                       | S    | 9          | 9       | 9         | Digital 5 Volt DC supply.                                                                                                                                                                  |

| VS                        | I    | 10         | 10      | 10        | Vertical Sync input; TTL level with Schmitt leading edge triggered.                                                                                                                        |

| Intensity(Int)/<br>PWMCLK | О    | 11         | 11      | 11        | Intensity color output; it can be switched as the interrupt pin for the ending of each displayed row or the leading edge of Vertical Sync. It can selected as the output of the PWM clock. |

| FB                        | О    | 12         | 12      | 12        | Fast Blanking Output.                                                                                                                                                                      |

| Blue                      | О    | 13         | 13      | 13        | Blue color output.                                                                                                                                                                         |

| Green                     | О    | 14         | 14      | 14        | Green color output.                                                                                                                                                                        |

| Red                       | О    | 15         | 15      | 15        | Red color output.                                                                                                                                                                          |

| Vss                       | О    | 16         | 16      | 16        | Digital ground pin.                                                                                                                                                                        |

| PWM0                      | O    | -          | 17      | -         | PWM DAC Output 0                                                                                                                                                                           |

| PWM1                      | О    | -          | 18      | -         | PWM DAC Output 1                                                                                                                                                                           |

| PWM2                      | О    | -          | 19      | -         | PWM DAC Output 2                                                                                                                                                                           |

| PWM3                      | О    | -          | 20      | -         | PWM DAC Output 3                                                                                                                                                                           |

| PWM4                      | О    | -          | 21      | -         | PWM DAC Output 4                                                                                                                                                                           |

| PWM5                      | О    | -          | 22      | -         | PWM DAC Output 5                                                                                                                                                                           |

| PWM6                      | O    | -          | 23      | -         | PWM DAC Output 6                                                                                                                                                                           |

| PWM7                      | О    | <u> -</u>  | 24      | -         | PWM DAC Output 7                                                                                                                                                                           |

Preliminary specification

trumpion microelectronics Preliminary specification

## Multi-window graphic On-Screen-Display

t8566(7)

#### 7 ABSOLUTE MAXIMUM RATINGS

Voltage referenced to Vss

| SYMBOL           | PARAMETER                            | MIN. | MAX.                 | UNIT |

|------------------|--------------------------------------|------|----------------------|------|

| $V_{DD}$         | supply voltage range                 | -0.3 | +7.0                 | V    |

| V <sub>in</sub>  | all input voltages                   | -0.3 | V <sub>DD</sub> +0.3 | V    |

| P <sub>tot</sub> | total power dissipation              | =    | 0.7                  | W    |

| $T_{stg}$        | storage temperature range            | -65  | +150                 | 'C   |

| $T_{amb}$        | operating ambient temperature range: | 0    | +70                  | 'C   |

#### 8 DC CHARACTERISTICS

$V_{DD}$  = 5 V Y10%;  $V_{SS}$  = 0 V;  $AV_{DD}$  = 5 V Y5%;  $AV_{SS}$  = 0 V;  $T_{amb}$  = 0 to +70°C. All voltages with respect to  $V_{SS}$  unless otherwise specified.

| SYMBOL            | PARAMETER                   | CONDITIONS                                          | MIN.                | MAX.                 | UNI<br>T |

|-------------------|-----------------------------|-----------------------------------------------------|---------------------|----------------------|----------|

| Supply            |                             |                                                     | I                   |                      |          |

| $V_{\mathrm{DD}}$ | supply voltage range        |                                                     | 4.5                 | 5.5                  | V        |

| AV <sub>DD</sub>  | Analog supply voltage range | (Applicable only for t8564A)                        | 4.75                | 5.25                 | V        |

| $I_{DD}$          | supply current              | $V_{DD} = 5 \text{ V}; f_{OSDCLK} = 90 \text{ MHz}$ | TBD                 | TBD                  |          |

|                   |                             | note (1)                                            |                     |                      | mA       |

| Inputs            | 1                           |                                                     |                     | <u>'</u>             | ı        |

| $V_{\rm IL1}$     | LOW level input voltage     |                                                     | -0.5                | $0.3V_{\mathrm{DD}}$ | V        |

|                   | (for TEST/TEST pin, SSB,    |                                                     |                     |                      |          |

|                   | SDA, SCK)                   |                                                     |                     |                      |          |

| $V_{\rm IH1}$     | HIGH level input voltage    |                                                     | 0.7 V <sub>DD</sub> | V <sub>DD</sub> +10% | V        |

|                   | (for TEST/TEST pin, SSB,    |                                                     |                     |                      |          |

|                   | SDA, SCK)                   |                                                     |                     |                      |          |

| $V_{IL2}$         | LOW level input voltage     |                                                     | -0.5                | 0.8                  | V        |

|                   | (HS, VS)                    |                                                     |                     |                      |          |

| V <sub>IH2</sub>  | HIGH level input voltage    |                                                     | 2.0                 | V <sub>DD</sub> +10% | V        |

|                   | (HS, VS)                    |                                                     |                     |                      |          |

| $I_{\mathrm{IH}}$ | input current logic 1       | V <sub>I</sub> = 5 V                                | TBD                 | TBD                  | μΑ       |

|                   | (for TEST/TEST pin)         |                                                     |                     |                      |          |

| $I_{IL}$          | input current logic 0       | $V_I = 0 V$                                         | TBD                 | TBD                  | μΑ       |

|                   | (for SSB pin)               |                                                     |                     |                      |          |

| $I_{\rm LI1}$     | input leakage current       | $0.45 < V_{\rm I} < V_{\rm DD}$                     | -10                 | Υ10                  | μΑ       |

|                   | (for SDA, SCK, HS, VS)      |                                                     |                     |                      |          |

t8566(7)

| SYMBOL           | PARAMETER                                                                                               | CONDITIONS               | MIN.                  | MAX.       | UNI<br>T |

|------------------|---------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|------------|----------|

| Outputs          |                                                                                                         |                          |                       |            |          |

| V <sub>OL1</sub> | LOW level output voltage<br>(for Red, Green, Blue, Intensity,<br>FB pins and PWM open drain<br>outputs) | $I_{OL} = 2 \text{ mA};$ | _                     | Vss + 0.4  | V        |

| V <sub>OL2</sub> | LOW level output voltage<br>(for SDA, SCK pins)                                                         | $I_{OL} = 4 \text{ mA}$  | -                     | Vss + 0.4V | V        |

| V <sub>OH</sub>  | HIGH level output voltage<br>(for Red, Green, Blue, Intensity,<br>FB pins)                              | $I_{OH} = 2 \text{ mA};$ | V <sub>DD</sub> - 0.8 | _          | V        |

| $I_{HZ}$         | High-Z current<br>(for Red, Green, Blue, Intensity,<br>FB pins)                                         |                          | TBD                   | TBD        | μΑ       |

#### Note

- 1. The operating supply current is measured with all output pins disconnected;

- a)  $V_{IL} = V_{SS} + 0.5 V$ ;

- b)  $V_{IH} = V_{DD} 0.5 V$ ;

- c)  $TEST/\overline{TEST} = SSB = Not connected;$

- d) SDA = SCK = Vdd (through 4,7 K ohm pullup resistor)

- e) HS = 48.5 KHz

- f) VS = 60 Hz

- g) VCO is connected to loop filter (C1=22 pf, R1 = 40 K ohm, C2 = 0.1 uF)

#### 9 AC CHARACTERISTICS

$V_{DD}$  = 5 V Y10%;  $V_{SS}$  = 0 V;  $AV_{DD}$  = 5 V Y5%;  $AV_{SS}$  = 0 V;  $T_{amb}$  = 0 to +70°C. All voltages with respect to  $V_{SS}$  unless otherwise specified.

| SYMBOL                                                      | PARAMETER                               | MIN.          | TYP. | MAX. | UNIT |  |  |  |

|-------------------------------------------------------------|-----------------------------------------|---------------|------|------|------|--|--|--|

| Red, Green, Blue, FB, Intensity (C <sub>LOAD</sub> = 30 pF) |                                         |               |      |      |      |  |  |  |

| t <sub>R</sub>                                              | Rise TIme (see note (1))                | -             | 4.7  | _    | ns   |  |  |  |

| $t_{\rm F}$                                                 | Fall TIme (see note (1))                | _             | 4.8  | _    | ns   |  |  |  |

| t <sub>SKEW</sub>                                           | Skew between those signals              | -             | 5    | _    | ns   |  |  |  |

| HS                                                          |                                         |               |      |      |      |  |  |  |

| $f_{HS}$                                                    | Horizontal sync input frequency         | 15            | -    | 120  | KHz  |  |  |  |

| t <sub>R</sub>                                              | Rise TIme (see note (1))                | _             | _    | 1    | ns   |  |  |  |

| $t_{\rm F}$                                                 | Fall TIme (see note (1))                | _             | -    | 1    | ns   |  |  |  |

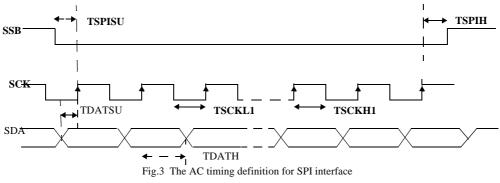

| SPI and I <sup>2</sup>                                      | C interface: SSB, SDA and SCK (refer to | Fig.3 and Fig | g.4) |      |      |  |  |  |

| t <sub>SPISU</sub>                                          | SSB to SCK setup time                   | 200           | -    | -    | ns   |  |  |  |

| t <sub>SPIH</sub>                                           | SSB to SCK hold time                    | 100           | _    | _    | ns   |  |  |  |

t8566(7)

| SYMBOL             | PARAMETER                                               | MIN. | TYP. | MAX.          | UNIT    |

|--------------------|---------------------------------------------------------|------|------|---------------|---------|

| f <sub>SCK1</sub>  | SPI baud rate                                           | _    | _    | 1000          | K bps   |

| t <sub>DATSU</sub> | SDA data setup time                                     | 0    | _    | _             | ns      |

| t <sub>DATH</sub>  | SDA data hold time                                      | 500  | _    | _             | ns      |

| t <sub>SCKL1</sub> | SCK Low period for SPI interface                        | 400  | _    | _             | ns      |

| t <sub>SCKH1</sub> | SCK High period for SPI interface                       | 400  | _    | _             | ns      |

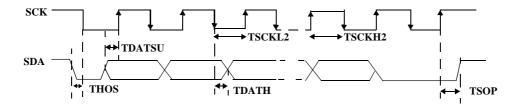

| f <sub>SCK2</sub>  | I <sup>2</sup> C baud rate                              | _    | _    | 400           | K bps   |

| $t_{SUP}$          | Setup time for Stop condition                           | 500  | _    | _             | ns      |

| t <sub>HDS</sub>   | Hold time for Start condition                           | 500  | _    | _             | ns      |

| t <sub>SCKL2</sub> | SCK Low period for I <sup>2</sup> C interface           | 1000 | _    | _             | ns      |

| t <sub>SCKH2</sub> | SCK High period for I <sup>2</sup> C interface          | 1000 | _    | _             | ns      |

| t <sub>R</sub>     | Rise time for SDA and SCK  Depend on the capacitive loa |      |      | ip resistor a | and the |

| $t_{\rm F}$        | Fall time for SDA                                       | _    | _    | 20            | ns      |

#### Note

- 1. Those parameters are guaranteed by internal qualification, including design characterization, process split lots analysis and temperature characterization.

- 2. For the falling edge, the time interval between 90% of  $(V_{DD} V_{SS})$  and 10% of  $(V_{DD} V_{SS})$  is defined as  $t_F$ . For the rising edge, the time interval between 10% of ( $V_{DD}$  -  $V_{SS}$ ) and 90% of ( $V_{DD}$  -  $V_{SS}$ ) is defined as  $t_R$ .

Fig.4 The AC timing definition for I<sup>2</sup>C interface

April 1999 10