- Single-Chip Segmentation and Reassembly Device (SAR) for Full-Duplex ATM-Adaptation-Layer (AAL) Processing

- Integrated 64-Bit Peripheral-Component **Interface for Transferring Data and Control** Information for Packet Segmentation and **Packet Reassembly**

- Provides Complete Encapsulation and **Termination of AAL5 Packets**

- Supports Both Transmit and Receive Buffer Chaining (Buffer Scatter/Gather)

- Provides for Early Segmentation of a Transmit Packet by Beginning the **Segmentation Process Once a Transmit Buffer Is Available Instead of Waiting for** the Entire Packet to Be Buffered

- Provides Full VPI/VCI Support and Allows for the Simultaneous Segmentation of 1023 Packets and the Simultaneous Reassembly of 30720 Packets

- Byte-Wide Cell Interface Is Full Duplex and Compliant to the ATM-Forum UTOPIA Document

- Cell Interface Can Be Programmed to Operate as Either a Physical (PHY)-Layer Interface or as a ATM-Layer Interface

- Provides Reassembly Time-Out for an **Incoming Packet**

- Provides a High-Priority Mechanism for **Transmitting Constant-Bit-Rate Traffic**

- Provides Support for Transparent/Null AAL

#### description

The TNETA1570 is an asynchronous transfer mode (ATM) segmentation and reassembly (SAR) device with a 64-bit peripheral component interconnect (PCI)-bus interface. This device incorporates ATM adaptation-layer (AAL) processing, ATM SAR processing for full-duplex operation up to STS-3c rate of 155.52 Mbit/s, and the controls for the register interface on the PHY layer. The device provides complete encapsulation and termination of AAL5 packets in hardware.

The TNETA1570 supports high-speed networking applications utilizing ATM protocols as either a backbone/backplane or desktop technology. Features include: high level of VPI/VCI support, high-priority segmentation option for constant-bit-rate traffic, early buffer segmentation, buffer scatter/gather capability, and 32-/64-bit PCI-bus support.

The device contains an integrated 32-/64-bit PCI interface for transferring data and control information. The segmentation and reassembly processes use host memory for storing packets that are transmitted or received. No local-packet memory is required. The device is capable of segmenting up to 1023 packets simultaneously and reassembling 30720 packets simultaneously. The device supports the full range of VPI/VCI values for both transmit and receive operations.

The TNETA1570 also supports two methods of transporting a transparent/null AAL used for transferring proprietary information. In addition, the device recognizes ATM-layer OAM cells and provides a mechanism for handling these cells. The device contains a full-duplex, byte-wide cell interface compliant to the ATM-Forum UTOPIA specification. The cell interface can be programmed to operate as either a PHY-layer interface or a ATM-layer interface.

The integrated PCI-host interface operates as either a 32-bit or 64-bit interface for DMA operations. The device operates as a 64-bit interface if the target device can accept 64-bit transfers; otherwise, it operates as a 32-bit interface. The PCI-host interface provides both master and slave capability and operates at a frequency up to 33 MHz. The PCI-host interface is functionally compliant to the PCI-local-bus specification revision 2.0. The TNETA1570 operation is explained in detail in the *Principles of Operation* section.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

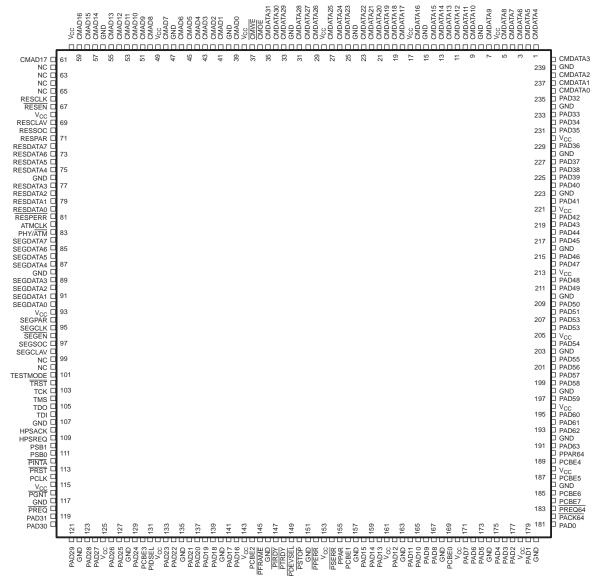

#### MFP PACKAGE (TOP VIEW)

NC - No internal connection

## **Terminal Functions**

## **PCI-bus interface**

| TERMINA      | AL .                                                                                                                                             | .,,              | DE000::-:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.                                                                                                                                              | 1/0              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PACK64       | 182                                                                                                                                              | I/O<br>(3 state) | PCI acknowledge 64-bit transfer. PACK64 is driven by the current target indicating the ability to support a 64-bit access. When acknowledging a 64-bit access, the assertion of PACK64 is coincident with the assertion of PDEVSEL. If PACK64 is not asserted coincident with PDEVSEL, the transaction defaults to 32 bit.                                                                                                                                                                                                                                   |

| PAD31 – PAD0 | 119-121,<br>123-124,<br>126-127,<br>129,<br>133-134,<br>136-139,<br>141-142,<br>158-160,<br>162,<br>164-167,<br>171-173,<br>175-177,<br>179, 181 | I/O<br>(3 state) | PCI address bus and data bus. PAD31–PAD0 are multiplexed on the same PCI terminals. During the first phase of the address phase of a transaction, PAD31–PAD0 contain a 32-bit PHY address. This phase is the clock cycle when PFRAME is asserted.  During the data phase, PAD7–PAD0 contain the least significant byte and PAD31–PAD24 contain the most significant byte. Write data is stable when PIRDY is asserted. Read data is stable when PTRDY is asserted. Data is transferred during those clock cycles when both PIRDY and PTRDY are asserted.     |

| PAD63-PAD32  | 191,<br>193–195,<br>197,<br>199–202,<br>204,<br>206–209,<br>211–212,<br>214–215,<br>217–220,<br>222,<br>224–227,<br>229,<br>231–233,<br>235      | I/O<br>(3 state) | PCI address bus and data bus. PAD63-PAD32 are multiplexed on the same PCI terminals. During the first phase of the address phase of a transaction, PAD63-PAD32 contain a 32-bit PHY address. This phase is the clock cycle when PFRAME is asserted.  During the data phase, PAD39-PAD32 contain the least significant byte and PAD63-PAD56 contain the most significant byte. Write data is stable when PIRDY is asserted. Read data is stable when PTRDY is asserted. Data is transferred during those clock cycles when both PIRDY and PTRDY are asserted. |

| PCBE3-PCBE0  | 130, 144,<br>156, 169                                                                                                                            | I/O<br>(3 state) | PCI-bus command and byte enable. PCBE3-PCBE0 lines are multiplexed on the same PCI terminals. During the address phase of a transaction, PCBE3-PCBE0 lines define the bus command. During the data phase, PCBE3-PCBE0 lines define which bytes are valid.                                                                                                                                                                                                                                                                                                    |

| PCBE7-PCBE4  | 184-185,<br>187,189                                                                                                                              | I/O<br>(3 state) | PCI-bus command and byte enable. PCBE7-PCBE4 lines are multiplexed on the same PCI terminals. During the address phase of a transaction, PCBE7-PCBE4 lines define the bus command. During the data phase, PCBE7-PCBE4 lines define which bytes are valid.                                                                                                                                                                                                                                                                                                    |

| PCLK         | 114                                                                                                                                              | I                | PCI clock. PCLK provides timing for all transactions on the PCI interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PDEVSEL      | 149                                                                                                                                              | I/O<br>(3 state) | PCI device select. When actively driven, PDEVSEL indicates that the address of the driving device is decoded as the target of the current access. As an input, PDEVSEL indicates whether any device on the bus is selected.                                                                                                                                                                                                                                                                                                                                  |

| PFRAME       | 145                                                                                                                                              | I/O<br>(3 state) | PCI frame. PFRAME is driven by the current master to indicate the beginning and duration of an access. PFRAME is asserted at the beginning of the bus transaction and remains asserted during data transfer. When PFRAME is deasserted, the transaction is in the final data phase.                                                                                                                                                                                                                                                                          |

| PGNT         | 116                                                                                                                                              | I                | PCI bus grant. PGNT indicates to the agent that the arbiter has granted access to the bus. PGNT is a point-to-point signal and every master has its own.                                                                                                                                                                                                                                                                                                                                                                                                     |

## **Terminal Functions (Continued)**

## **PCI-bus interface (continued)**

| TERMINAL  |         | 1/0                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----------|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | NO.     | I/O                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| PIDSEL    | 131     | I                      | PCI initialization and device select. PIDSEL is used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                           |  |  |  |

| PINTA     | 112     | O<br>(open<br>drain)   | PCI interrupt. PINTA is an interrupt request from PCI SAR.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PIRDY     | 147     | I/O<br>(3 state)       | PCI initiator ready. PIRDY indicates the initiating agent's (bus master) ability to complete the current data phase of the transaction. During a write, PIRDY indicates valid data on PAD31-PAD0. During a read, PIRDY indicates the master is prepared to accept the data. PIRDY is used with PTRDY when wait cycles are inserted until both are asserted.                                                                                       |  |  |  |

| PPAR      | 155     | I/O<br>(3 state)       | PCI parity. PPAR is even parity across PAD31 – PAD0 and PCBE3 – PCBE0. For data phases, PPAR is valid one clock after either PIRDY is asserted on a write or PTRDY is asserted on a read. Once asserted, PPAR remains valid until one clock after the completion of the current data phase. The master drives the PPAR for address- and write-data phases, and the target drives PPAR for the read-data phase.                                    |  |  |  |

| PPAR64    | 190     | I/O<br>(3 state)       | PCI parity. PPAR64 is even parity across AD63-AD32 and CBE7-CBE4. For data phases, PPAR64 is valid one clock after either PIRDY is asserted on a write or PTRDY is asserted on a read. Once asserted, PPAR64 remains valid until one clock after the completion of the current data phase. The master drives the PPAR 64 for address and write-data phase, and the target drives the PPAR for read-data phases.                                   |  |  |  |

| PPERR     | 152     | I/O<br>(3 state)       | PCI parity error. PPERR reports a data-parity error on all commands except special cycle. An agent cannot report a PPERR until it has claimed the access by PDEVSEL and completed a data phase.                                                                                                                                                                                                                                                   |  |  |  |

| PREQ      | 118     | 0                      | PCI request. PREQ indicates to the arbiter that this agent desires use of the bus. Every master has its own PREQ.                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PREQ64    | 183     | I/O<br>(3 state)       | PCI request 64-bit transfer. PREQ64 is driven by the current master indicating the desire for a 64-bit access. When initiating a 64-bit transaction, the assertion of PREQ64 is coincident with the assertion of PFRAME. If a 64-bit access is not acknowledged by PFRAME, the access defaults to 32 bit. The transfer type (32 or 64 bit) is dynamically negotiated for each transaction and remains constant for the length of the transaction. |  |  |  |

| PRST      | 113     | I                      | PCI reset. PRST forces the PCI sequence of each device to a known state.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| PSB1-PSB0 | 110–111 | 0                      | PCI sideband. PSB1 – PSB0 lines define the size of the transfer when the TNETA1570 is the bus master. The definitions of these signals are as follows:  00: 4-byte transfer 01: 16-byte transfer (except for receive-completion ring) 10: Payload transfer                                                                                                                                                                                        |  |  |  |

|           |         |                        | 11: Transfer to receive-completion ring (16-byte transfer)  PSB1-PSB0 are synchronous to the address phase of the bus-master operations by the TNETA1570. The sideband signals do not change upon a bus retry after disconnect.                                                                                                                                                                                                                   |  |  |  |

| PSERR     | 154     | I/O<br>(open<br>drain) | PCI system error. PSERR reports address-parity errors and data-parity errors on special-cycle commands.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| PSTOP     | 150     | I/O<br>(3 state)       | PCI stop. PSTOP indicates that the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| PTRDY     | 148     | I/O<br>(3 state)       | PCI target ready. PTRDY indicates the target agent's (selected device) ability to complete the current data phase of the transaction. During a read, PTRDY indicates that valid data is present on PAD31–PAD0. During a write, PTRDY indicates that the target is prepared to accept data.                                                                                                                                                        |  |  |  |

## **Terminal Functions (Continued)**

## cell-segmentation interface

| TERMINAL<br>NAME      | NO.             | 1/0         |                     | DESCRIPTION                                                                                                |  |  |

|-----------------------|-----------------|-------------|---------------------|------------------------------------------------------------------------------------------------------------|--|--|

|                       |                 |             | Segmentation        | n cell available                                                                                           |  |  |

| SEGCLAV               | 98              | (CMOS)      | PHY mode            | SEGCLAV (RXEMPTY/RXCLAV) indicates that a complete cell is available.                                      |  |  |

|                       |                 | (CIVIOS)    | ATM mode            | SEGCLAV (TXENB) is active low when SEGDATA contains a valid byte.                                          |  |  |

|                       |                 |             | Segmentation        | on clock                                                                                                   |  |  |

| SEGCLK                | 95              | l<br>(TTL)  | PHY mode            | SEGCLK (RXCLK) is used to synchronize transfers on SEGDATA. SEGCLK is sourced from the UTOPIA interface.   |  |  |

|                       |                 | (112)       | ATM mode            | SEGCLK (TXCLK) is used to synchronize transfers on SEGDATA. SEGCLK is sourced from the ATMCLK.             |  |  |

|                       |                 |             | Segmentation        | Segmentation data                                                                                          |  |  |

| SEGDATA7-<br>SEGDATA0 | 84-87,<br>89-92 | O<br>(CMOS) | PHY mode            | SEGDATA7 – SEGDATA0 (RXDATA) is byte-wide true data that is sourced by the TNETA1570. SEGDATA7 is the MSB. |  |  |

| OLOBATAO              |                 |             | ATM mode            | SEGDATA7 – SEGDATA0 (TXDATA) is byte-wide true data that is sourced by the TNETA1570. SEGDATA7 is the MSB. |  |  |

|                       |                 |             | Segmentation enable |                                                                                                            |  |  |

| SEGEN                 | 96              |             | PHY mode            | SEGEN (RXENB) indicates that a valid byte will be sent during the next clock cycle.                        |  |  |

| OEGEN                 |                 | (TTL)       | ATM mode            | SEGEN (TXFULL/TXCLAV) indicates that at least 1-byte SEGDATA will be accepted.                             |  |  |

|                       |                 |             | Segmentation parity |                                                                                                            |  |  |

| SEGPAR                | 94              | (CMOS)      | PHY mode            | SEGPAR (RXPAR) is the odd-parity bit over SEGDATA7-SEGDATA0.                                               |  |  |

|                       |                 | (0.0.00)    | ATM mode            | SEGPAR (TXPAR) is the odd-parity bit over SEGDATA7 – SEGDATA0.                                             |  |  |

|                       |                 |             | Segmentation        | n start of cell                                                                                            |  |  |

| SEGSOC                | 97              | O<br>(CMOS) | PHY mode            | SEGSOC (RXSOC) is active high when SEGDATA contains the first valid byte of the cell.                      |  |  |

|                       |                 |             | ATM mode            | SEGSOC (TXSOC) is active high when SEGDATA contains the first valid byte of the cell.                      |  |  |

## high-priority segmentation (request and acknowledge)

| TERMINAL |     | 1/0         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|----------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO. | I/O         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| HPSREQ   | 109 | I<br>(TTL)  | High-priority segmentation request. HPSREQ is sampled at each new segmentation opportunity and is synchronous to the PCI-bus clock. When HPSREQ is active, TNETA1570 initiates the procedure for transmitting a cell from TX DMA channel 1. To ensure that the high-priority segmentation request is processed, HPSREQ remains active until HPSACK is set low. HPSREQ is deasserted within two PCI-bus clock cycles of when HPSACK is asserted. |  |  |  |

| HPSACK   | 108 | O<br>(CMOS) | High-priority segmentation acknowledge. HPSACK is asserted for one PCI-bus clock cycle to acknowledge that HPSREQ is detected.                                                                                                                                                                                                                                                                                                                  |  |  |  |

## **Terminal Functions (Continued)**

## cell-reassembly interface

| TERMINAI<br>NAME      | L<br>NO.                 | 1/0         |                           | DESCRIPTION                                                                                          |  |  |

|-----------------------|--------------------------|-------------|---------------------------|------------------------------------------------------------------------------------------------------|--|--|

|                       |                          |             | Reassembly cell available |                                                                                                      |  |  |

| RESCLAV               | 69                       | 0           | PHY mode                  | RESCLAV (TXFULL/TXCLAV) indicates that a transfer of a complete cell can be accepted.                |  |  |

|                       |                          | (CMOS)      | ATM mode                  | RESCLAV (RXENB) indicates that a valid byte RESDATA will be sent during the next clock cycle.        |  |  |

|                       |                          |             | Reassembly                | clock                                                                                                |  |  |

| RESCLK                | 66                       | l<br>(TTL)  | PHY mode                  | RESCLK (TXCLK) is used to synchronize transfers on RESDATA. ATMCLK is used as the source for RESCLK. |  |  |

|                       |                          | (11L)       | ATM mode                  | RESCLK (RXCLK) is used to synchronize transfers on RESDATA. ATMCLK is used as the source for RESCLK. |  |  |

|                       |                          |             | Reassembly data           |                                                                                                      |  |  |

| RESDATA7-<br>RESDATA0 | 72–75,<br>77 <b>–</b> 80 | (TTL)       | PHY mode                  | RESDATA7-RESDATA0 (TXDATA). RESDATA7 is the MSB.                                                     |  |  |

| REODATAO              |                          | (112)       | ATM mode                  | RESDATA7-RESDATA0 (RXDATA). RESDATA7 is the MSB.                                                     |  |  |

|                       | 67                       |             | Reassembly enable         |                                                                                                      |  |  |

| RESEN                 |                          | I<br>(TTL)  | PHY mode                  | RESEN (TXENB) goes active low when RESDATA contains a valid byte.                                    |  |  |

| REGEN                 |                          |             | ATM mode                  | RESEN (RXEMPTY/RXCLAV) indicates that RESDATA will be sent during the next clock cycle.              |  |  |

|                       |                          |             | Reassembly                | parity                                                                                               |  |  |

| RESPAR                | 71                       | (TTL)       | PHY mode                  | RESPAR (TXPAR) is the odd-parity bit over RESDATA7 – RESDATA0.                                       |  |  |

|                       |                          | ('''-)      | ATM mode                  | RESPAR (RXPAR) is the odd-parity bit over RESDATA7 – RESDATA0.                                       |  |  |

|                       |                          |             | Reassembly                | parity error (not required by UTOPIA)                                                                |  |  |

| RESPERR               | 81                       | O<br>(CMOS) | PHY mode                  | RESPERR indicates that parity error is present at the previous rising edge of                        |  |  |

|                       |                          | (CIVICS)    | ATM mode                  | RESCLK.                                                                                              |  |  |

| RESSOC                |                          |             | Reassembly                | start of cell                                                                                        |  |  |

|                       | 70                       | (TTL)       | PHY mode                  | RESSOC (TXSOC) is received when RESDATA contains the first valid byte of the cell.                   |  |  |

|                       |                          |             | ATM mode                  | RESSOC (RXSOC) is received when RESDATA contains the first valid byte of the cell.                   |  |  |

## **Terminal Functions (Continued)**

## control-memory interface

| TERMINAL              |                                                                                       | I/O                       | DESCRIPTION                                                                                                                                 |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                  | NO.                                                                                   | 1/0                       | DESCRIPTION                                                                                                                                 |  |  |  |

| CMAD17-<br>CMAD0      | 61,<br>59-57,<br>55-50,<br>48,<br>46-41,<br>39                                        | O<br>(CMOS)               | Control-memory address. CMAD17–CMAD0 contains an 18-bit physical address to the control memory.                                             |  |  |  |

| CMDATA31 –<br>CMDATA0 | 35-33,<br>31-29,<br>27-25,<br>23-18,<br>16,<br>14-9,<br>7,<br>5-1,<br>240,<br>238-236 | I<br>(TTL)<br>O<br>(CMOS) | Control-memory data. CMDATA31 – CMDATA0 contains 32-bit data to/from the control memory.                                                    |  |  |  |

| СМОЕ                  | 36                                                                                    | O<br>(CMOS)               | Control-memory output enable. When CMOE is active low, the address is valid and data is read into the TNETA1570 on the rising edge of CMOE. |  |  |  |

| CMWE                  | 37                                                                                    | O<br>(CMOS)               | Control-memory write enable. When CMWE is active low, the address and data are valid.                                                       |  |  |  |

## boundary-scan interface

| TERMINAL |     | I/O        | DESCRIPTION                                                                                            |

|----------|-----|------------|--------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0        | DESCRIPTION                                                                                            |

| TCK      | 103 | l<br>(TTL) | Test clock. TCK clocks the test-access-port (TAP) operation.                                           |

| TDI      | 106 | l<br>(TTL) | Test data input. TDI shifts serial-test data and instructions into the device during (TAP) operation.  |

| TDO      | 105 | O<br>(TTL) | Test data output. TDO shifts serial-test data and instructions out of the device during TAP operation. |

| TMS      | 104 | I<br>(TTL) | Test-mode select. TMS controls the state of the TAP controller.                                        |

| TRST     | 102 | I<br>(TTL) | Test reset. TRST asynchronously forces the TAP controller to a known state.                            |

## test signal

| TERMINAL |     | I/O        | DESCRIPTION                                                                    |  |  |

|----------|-----|------------|--------------------------------------------------------------------------------|--|--|

| NAME NO. |     | 1/0        | DESCRIPTION                                                                    |  |  |

| TESTMODE | 101 | l<br>(TTL) | Test mode. TESTMODE is used for device testing. Grounded for normal operation. |  |  |

## **TNETA1570** ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE SDNS033B – JUNE 1995 – REVISED MAY 1996

## miscellaneous signals

| TERMINA | TERMINAL         |             |               | DESCRIPTION                                                                                                                                                                                                               |  |  |  |  |

|---------|------------------|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME    | NO.              | I/O         |               | DESCRIPTION                                                                                                                                                                                                               |  |  |  |  |

| PHY/ATM | 83               | l<br>(TTL)  | PHY/ATM m     | PHY/ATM mode select. PHY/ATM selects ATM mode when low and the PHY mode when high.                                                                                                                                        |  |  |  |  |

|         |                  |             | ATM clock     |                                                                                                                                                                                                                           |  |  |  |  |

|         |                  | O<br>(CMOS) | PHY mode      | In PHY mode, the ATMCLK is driven low. It can be left as a N/C.                                                                                                                                                           |  |  |  |  |

| ATMCLK  | 82               |             | ATM mode      | ATMCLK is used as the clock source to provide for data transfers/synchronization. ATMCLK is connected to SEGCLK and RESCLK in the ATM mode. The clock generated by the interface is 33 MHz (nominal) using the PCI clock. |  |  |  |  |

| NC      | 62-65,<br>99-100 |             | No connection | No connection. Leave open.                                                                                                                                                                                                |  |  |  |  |

## power and ground

|      | TERMINAL                                                                                                                                             |                |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

| NAME | NO.                                                                                                                                                  | DESCRIPTION    |  |  |  |  |

| GND  | 8, 15, 24, 32, 40, 47, 56, 76, 88, 107, 117, 122, 128, 135, 140, 146, 151, 157, 163, 168, 174, 180, 186, 192, 198, 203, 210, 216, 223, 228, 234, 239 | Ground         |  |  |  |  |

| Vcc  | 6, 17, 28, 38, 49, 60, 68, 93, 115, 125, 132, 143, 153, 161, 170, 178, 188, 196, 205, 213, 221, 230                                                  | Supply voltage |  |  |  |  |

## TNETA1570 ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE

SDNS033B - JUNE 1995 - REVISED MAY 1996

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)                                                           | 0.5 V to 6 V                     |

|--------------------------------------------------------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub>                                                                          | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, VO                                                                                     | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, $I_{ K }(V_1 < 0 \text{ or } V_1 > V_{CC})$ (see Note 2)                                | ±20 mA                           |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) (see Note 3) | ±20 mA                           |

| Operating free-air temperature range, T <sub>A</sub>                                                         | 0°C to 70°C                      |

| Storage temperature range, T <sub>stg</sub>                                                                  |                                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to the GND terminals.

- 2. Applies for external input and bidirectional buffers

- 3. Applies for external output and bidirectional buffers

## recommended operating conditions

|                 |                                               |        |                          | MIN   | NOM | MAX  | UNIT |

|-----------------|-----------------------------------------------|--------|--------------------------|-------|-----|------|------|

| Vcc             | V <sub>CC</sub> Supply voltage                |        |                          |       |     |      | V    |

|                 |                                               |        | V <sub>CC</sub> = 4.75 V | 3.325 |     |      |      |

| VIH             | High-level input voltage                      | CMOS   | V <sub>CC</sub> = 5.25 V | 3.675 |     |      | V    |

|                 |                                               | TTL    |                          | 2     |     |      |      |

|                 |                                               | CMOS   | V <sub>CC</sub> = 4.75 V |       |     | 0.95 |      |

| V <sub>IL</sub> | Low-level input voltage                       | CIVIOS | V <sub>CC</sub> = 5.25 V |       |     | 1.05 | V    |

|                 |                                               | TTL    |                          |       |     | 0.8  |      |

| TA              | T <sub>A</sub> Operating free-air temperature |        |                          |       |     | 70   | °C   |

# electrical characteristics over recommended operating conditions, $T_A$ = 25°C (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS                                        | MIN TYP              | MAX | UNIT |

|------------------|-------------------------------------|--------------------------------------------------------|----------------------|-----|------|

| V                | High level output voltage           | I <sub>OH</sub> = 8 mA                                 | V <sub>CC</sub> -0.8 |     | V    |

| VOH              | High-level output voltage           | I <sub>OL</sub> = 4 mA                                 | V <sub>CC</sub> -0.8 |     | l v  |

| VOL              | Law lavel output voltage            | I <sub>OH</sub> = 8 mA                                 |                      | 0.5 | V    |

|                  | Low-level output voltage            | I <sub>OL</sub> = 4 mA                                 |                      | 0.5 | ľ    |

| loz              | High-impedance-state output current | $V_I = V_{CC}$ or GND                                  |                      | ±10 | μΑ   |

| Ι <sub>Ι</sub> L | Low-level input current             | V <sub>I</sub> = GND                                   |                      | -1  | μΑ   |

| lн               | High-level input current            | VI = VCC                                               |                      | 1   | μΑ   |

| ICC              | Supply current, dynamic             | $V_{CC} = 5.25 \text{ V},  f_{clock} = 33 \text{ MHz}$ | 500                  |     | mA   |

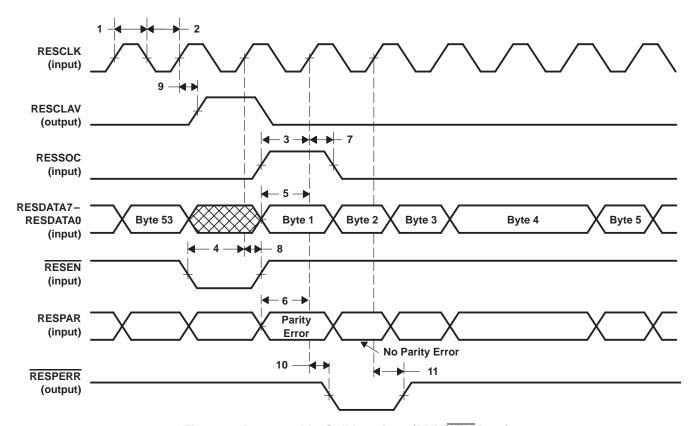

## timing requirements (see Note 4 and Figure 1)

| NO. |                          |                                                    | MIN | MAX | UNIT |

|-----|--------------------------|----------------------------------------------------|-----|-----|------|

| 1   | tw(RESCLKH)              | Pulse duration, RESCLK high                        | 12  |     | ns   |

| 2   | tw(RESCLKL)              | Pulse duration, RESCLK low                         | 12  |     | ns   |

| 3   | tsu(RESSOC)              | Setup time, RESSOC high before RESCLK↑             | 10  |     | ns   |

| 4   | tsu(RESEN)               | Setup time, RESEN low before RESCLK↑               | 10  |     | ns   |

| 5   | <sup>t</sup> su(RESDATA) | Setup time, RESDATA7-RESDATA0 valid before RESCLK↑ | 10  |     | ns   |

| 6   | tsu(RESPAR)              | Setup time, RESPAR valid before RESCLK↑            | 10  |     | ns   |

| 7   | th(RESSOC)               | Hold time, RESSOC high after RESCLK↑               | 1   |     | ns   |

| 8   | th(RESEN)                | Hold time, RESEN low after RESCLK↑                 | 1   |     | ns   |

NOTE 4: All output signals are generated on the rising edge of RESCLK.

## operating characteristics (see Note 4 and Figure 1)

| NO. |                                               | MIN | MAX | UNIT |

|-----|-----------------------------------------------|-----|-----|------|

| 9   | td(RESCLAV) Delay time, RESCLK ↑ to RESCLAV↑  | 1   | 20  | ns   |

| 10  | td(RESPERR)1 Delay time, RESCLK ↑ to RESPERR↓ | 1   | 20  | ns   |

| 11  | td(RESPERR)2 Delay time, RESCLK ↑ to RESPERR↑ | 1   | 20  | ns   |

NOTE 4: All output signals are generated on the rising edge of RESCLK.

Figure 1. Reassembly-Cell Interface (PHY/ATM Low)

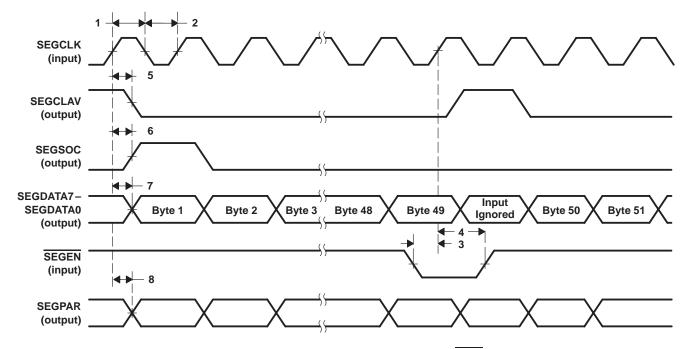

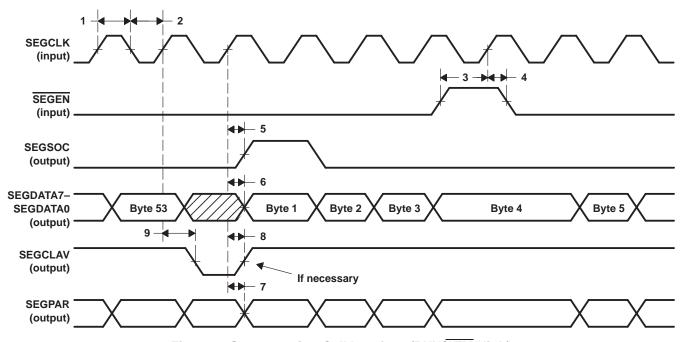

## timing requirements (see Note 5 and Figure 2)

| NO. |                        |                                      | MIN | MAX | UNIT |

|-----|------------------------|--------------------------------------|-----|-----|------|

| 1   | tw(SEGCLKH)            | Pulse duration, SEGCLK high          | 12  |     | ns   |

| 2   | tw(SEGCLKL)            | Pulse duration, SEGCLK low           | 12  |     | ns   |

| 3   | t <sub>su(SEGEN)</sub> | Setup time, SEGEN low before SEGCLK↑ | 10  |     | ns   |

| 4   | th(SEGEN)              | Hold time, SEGEN low after SEGCLK↑   | 1   |     | ns   |

NOTE 5: All output signals are generated on the rising edge of SEGCLK. All inputs are sampled on the rising edge of SEGCLK.

## operating characteristics (see Note 5 and Figure 2)

| NO. |                                                            | MIN | MAX | UNIT |

|-----|------------------------------------------------------------|-----|-----|------|

| 5   | td(SEGCLAV) Delay time, SEGCLK↑ to SEGCLAV↓                | 1   | 20  | ns   |

| 6   | td(SEGSOC) Delay time, SEGCLK↑ to SEGSOC↑                  | 1   | 20  | ns   |

| 7   | td(SEGDATA) Delay time, SEGCLK↑ to SEGDATA7−SEGDATA0 valid | 1   | 20  | ns   |

| 8   | td(SEGPAR) Delay time, SEGCLK↑ to SEGPAR valid             | 1   | 20  | ns   |

NOTE 5: All output signals are generated on the rising edge of SEGCLK. All inputs are sampled on the rising edge of SEGCLK.

Figure 2. Segmentation-Cell Interface (PHY/ATM Low)

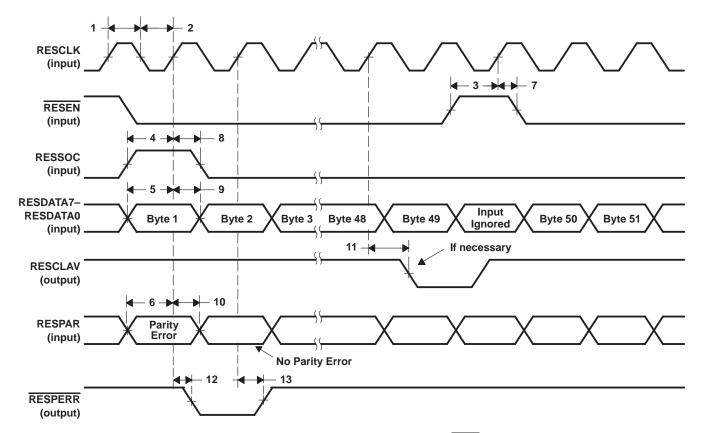

## timing requirements (see Note 6 and Figure 3)

| NO. |                         |                                                      | MIN | MAX | UNIT |

|-----|-------------------------|------------------------------------------------------|-----|-----|------|

| 1   | tw(RESCLKH)             | Pulse duration, RESCLK high                          | 10  |     | ns   |

| 2   | tw(RESCLKL)             | Pulse duration, RESCLK low                           | 10  |     | ns   |

| 3   | tsu(RESEN)              | Setup time, RESEN high before RESCLK↑                | 10  |     | ns   |

| 4   | tsu(RESSOC)             | Setup time, RESSOC high before RESCLK↑               | 10  |     | ns   |

| 5   | tsu(RESDATA)            | Setup time, RESDATA7 – RESDATA0 valid before RESCLK↑ | 10  |     | ns   |

| 6   | tsu(RESPAR)             | Setup time, RESPAR valid before RESCLK↑              | 10  |     | ns   |

| 7   | th(RESEN)               | Hold time, RESEN high after RESCLK↑                  | 1   |     | ns   |

| 8   | th(RESSOC)              | Hold time, RESSOC high after RESCLK↑                 | 1   |     | ns   |

| 9   | <sup>t</sup> h(RESDATA) | Hold time, RESDATA7-RESDATA0 valid after RESCLK↑     | 1   |     | ns   |

| 10  | th(RESPAR)              | Hold time, RESPAR valid after RESCLK↑                | 1   |     | ns   |

NOTE 6: All output signals are generated on the rising edge of RESCLK. All input signals are sampled on the rising edge of RESCLK.

## operating characteristics (see Note 6 and Figure 3)

| NO. |                                              | MIN | MAX | UNIT |

|-----|----------------------------------------------|-----|-----|------|

| 11  | td(RESCLAV) Delay time, RESCLK↑ to RESCLAV↓  | 1   | 20  | ns   |

| 12  | td(RESPERR)1 Delay time, RESCLK↑ to RESPERR↓ | 1   | 20  | ns   |

| 13  | td(RESPERR)2 Delay time, RESCLK↑ to RESPERR↑ | 1   | 20  | ns   |

NOTE 6: All output signals are generated on the rising edge of RESCLK. All input signals are sampled on the rising edge of RESCLK.

Figure 3. Reassembly-Cell Interface (PHY/ATM High)

## timing requirements (see Note 5 and Figure 4)

| NO. |                                                              | MIN | MAX | UNIT |

|-----|--------------------------------------------------------------|-----|-----|------|

| 1   | tw(SEGCLKH) Pulse duration, SEGCLK high                      | 10  |     | ns   |

| 2   | tw(SEGCLKL) Pulse duration, SEGCLK low                       | 10  |     | ns   |

| 3   | t <sub>su(SEGEN)</sub> Setup time, SEGEN high before SEGCLK↑ | 10  |     | ns   |

| 4   | th(SEGEN) Hold time, SEGEN high after SEGCLK↑                | 1   |     | ns   |

NOTE 5: All output signals are generated on the rising edge of SEGCLK. All input signals are sampled on the rising edge of SEGCLK.

#### operating characteristics (see Note 5 and Figure 4)

| NO. |                                                              | MIN | MAX | UNIT |

|-----|--------------------------------------------------------------|-----|-----|------|

| 5   | td(SEGSOC) Delay time, SEGCLK↑ to SEGSOC↑                    | 1   | 20  | ns   |

| 6   | td(SEGDATA) Delay time, SEGCLK↑ to SEGDATA7 – SEGDATA0 valid | 1   | 20  | ns   |

| 7   | td(SEGPAR) Delay time, SEGCLK↑ to SEGPAR↑                    | 1   | 20  | ns   |

| 8   | td(SEGCLAV)1 Delay time, SEGCLK↑ to SEGCLAV↑                 | 1   | 20  | ns   |

| 9   | td(SEGCLAV)2 Delay time, SEGCLK↑ to SEGCLAV↓                 | 1   | 20  | ns   |

NOTE 5: All output signals are generated on the rising edge of SEGCLK. All input signals are sampled on the rising edge of SEGCLK.

Figure 4. Segmentation-Cell Interface (PHY/ATM High)

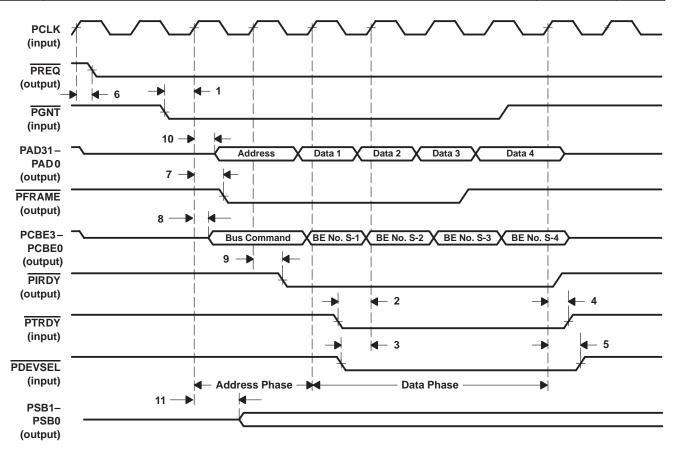

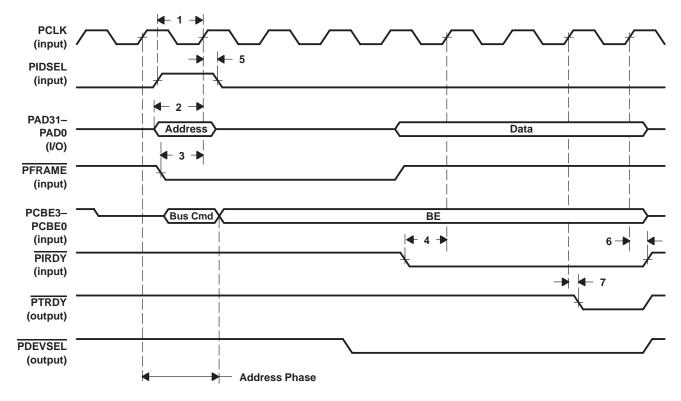

## timing requirements (see Figure 5)

| NO. |                       |                                      | MIN | MAX | UNIT |

|-----|-----------------------|--------------------------------------|-----|-----|------|

| 1   | t <sub>su(PGNT)</sub> | Setup time, PGNT low before PCLK↑    | 10  |     | ns   |

| 2   | tsu(PTRDY)            | Setup time, PTRDY low before PCLK↑   | 7   |     | ns   |

| 3   | tsu(PDEVSEL)          | Setup time, PDEVSEL low before PCLK↑ | 7   |     | ns   |

| 4   | <sup>t</sup> h(PTRDY) | Hold time, PTRDY low after PCLK↑     | 2   |     | ns   |

| 5   | th(PDEVSEL)           | Hold time, PDEVSEL low after PCLK↑   | 2   |     | ns   |

## operating characteristics (see Figure 5)

| NO. |                       |                                         | MIN | MAX | UNIT |

|-----|-----------------------|-----------------------------------------|-----|-----|------|

| 6   | t <sub>d</sub> (PREQ) | Delay time, PCLK↑ to PREQ↓              | 2   | 12  | ns   |

| 7   | td(PFRAME)            | Delay time, PCLK↑ to PFRAME↓            | 2   | 11  | ns   |

| 8   | td(PCBE)              | Delay time, PCLK↑ to PCBE valid         | 2   | 11  | ns   |

| 9   | td(PIRDY)             | Delay time, PCLK↑ to PIRDY↓             | 2   | 11  | ns   |

| 10  | t <sub>d</sub> (PAD)  | Delay time, PCLK↑ to PAD31 – PAD0 valid | 2   | 11  | ns   |

| 11  | t <sub>d</sub> (PSB)  | Delay time, PCLK↑ to PSB1 – PSB0 valid  | 2   | 11  | ns   |

Figure 5. TNETA1570 Write Operation (PCI SAR as Master)

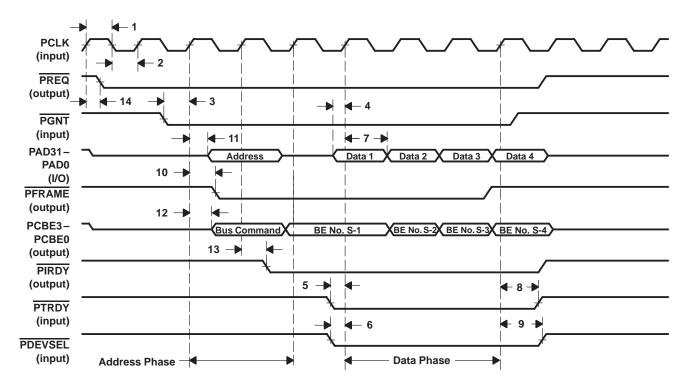

## timing requirements (see Figure 6)

| NO. |                        |                                             | MIN | MAX | UNIT |

|-----|------------------------|---------------------------------------------|-----|-----|------|

| 1   | tw(PCLKH)              | Pulse duration, PCLK high                   | 12  |     | ns   |

| 2   | tw(PCLKL)              | Pulse duration, PCLK low                    | 12  |     | ns   |

| 3   | tsu(PGNT)              | Setup time, PGNT low before PCLK↑           | 10  |     | ns   |

| 4   | <sup>t</sup> su(PAD)   | Setup time, PAD31 – PAD0 valid before PCLK↑ | 7   |     | ns   |

| 5   | t <sub>su(PTRDY)</sub> | Setup time, PTRDY low before PCLK↑          | 7   |     | ns   |

| 6   | tsu(PDEVSEL)           | Setup time, PDEVSEL low before PCLK↑        | 7   |     | ns   |

| 7   | <sup>t</sup> h(PAD)    | Hold time, PAD31 − PAD0 valid after PCLK↑   | 1   |     | ns   |

| 8   | <sup>t</sup> h(PTRDY)  | Hold time, PTRDY low after PCLK↑            | 2   |     | ns   |

| 9   | th(PDEVSEL)            | Hold time, PDEVSEL low after PCLK↑          | 2   |     | ns   |

## operating characteristics (see Figure 6)

| NO.                     |                                                              |                                        | MIN | MAX | UNIT |

|-------------------------|--------------------------------------------------------------|----------------------------------------|-----|-----|------|

| 10                      | t <sub>d(PFRAME)</sub> Delay time, PCLK↑ to PFRAME↓          |                                        | 2   | 11  | ns   |

| 11                      | 11 t <sub>d(PAD)</sub> Delay time, PCLK↑ to PAD31−PAD0 valid |                                        | 2   | 11  | ns   |

| 12 t <sub>d(PCBE)</sub> |                                                              | Delay time, PCLK↑ to PCBE3-PCBE0 valid | 2   | 11  | ns   |

| 13                      | <sup>t</sup> d(PIRDY)                                        | Delay time, PCLK↑ to PIRDY↓            | 2   | 11  | ns   |

| 14                      | t <sub>d</sub> (PREQ)                                        | Delay time, PCLK↑ to PREQ↓             | 2   | 12  | ns   |

Figure 6. TNETA1570 Read Operation (PCI SAR as Master)

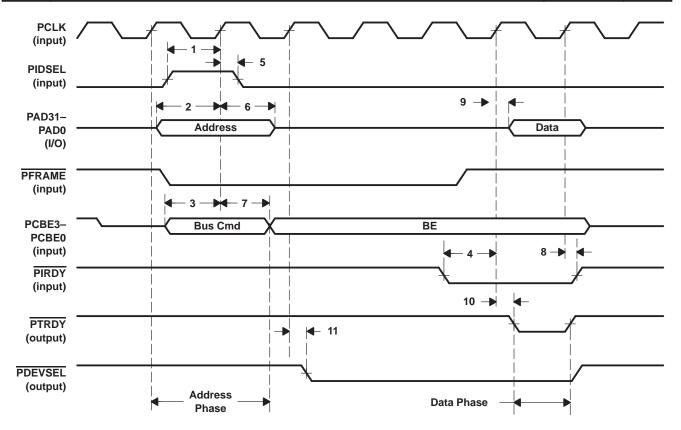

## timing requirements (see Figure 7)

| NO. |                                                                    |                                              | MIN | MAX | UNIT |

|-----|--------------------------------------------------------------------|----------------------------------------------|-----|-----|------|

| 1   | t <sub>su</sub> (PIDSEL)                                           | Setup time, PIDSEL high before PCLK↑         |     |     | ns   |

| 2   | t <sub>SU</sub> (PAD) Setup time, PAD31−PAD0 valid before PCLK↑    |                                              | 7   |     | ns   |

| 3   | 3 t <sub>SU(PCBE)</sub> Setup time, PCBE3−PCBE0 valid before PCLK↑ |                                              | 7   |     | ns   |

| 4   | t <sub>Su(PIRDY)</sub> Setup time, PIRDY low before PCLK↑          |                                              | 7   |     | ns   |

| 5   | <sup>t</sup> h(PIDSEL)                                             | h(PIDSEL) Hold time, PIDSEL high after PCLK↑ |     |     | ns   |

| 6   | 6 th(PAD) Hold time, PAD31−PAD0 valid after PCLK↑                  |                                              | 2   |     | ns   |

| 7   | t <sub>h</sub> (PCBE) Hold time, PCBE3−PCBE0 valid after PCLK↑     |                                              | 1   |     | ns   |

| 8   | th(PIRDY) Hold time, PIRDY low after PCLK↑                         |                                              | 1   |     | ns   |

## operating characteristics (see Figure 7)

| NO. |                                                              | MIN | MAX | UNIT |

|-----|--------------------------------------------------------------|-----|-----|------|

| 9   | t <sub>d</sub> (PAD) Delay time, PCLK↑ to PAD31 – PAD0 valid |     | 11  | ns   |

| 10  | t <sub>d(PTRDY)</sub> Delay time, PCLK↑ to PTRDY↓            |     | 11  | ns   |

| 11  | td(PDEVSEL) Delay time, PCLK↑ to PDEVSEL↓                    | 2   | 11  | ns   |

Figure 7. TNETA1570 Read Operation (PCI SAR as Slave)

## timing requirements (see Figure 8)

| NO.                                             |                                                                  |                                      | MIN | MAX | UNIT |

|-------------------------------------------------|------------------------------------------------------------------|--------------------------------------|-----|-----|------|

| 1                                               | tsu(PIDSEL)                                                      | Setup time, PIDSEL high before PCLK↑ |     |     | ns   |

| 2                                               | 2 t <sub>su(PAD)</sub> Setup time, PAD31−PAD0 valid before PCLK↑ |                                      | 7   |     | ns   |

| 3                                               | t <sub>su(PFRAME)</sub> Setup time, PFRAME low before PCLK↑      |                                      | 7   |     | ns   |

| 4                                               | 4 t <sub>su(PIRDY)</sub> Setup time, PIRDY low before PCLK↑      |                                      | 7   |     | ns   |

| 5 th(PIDSEL) Hold time, PIDSEL high after PCLK↑ |                                                                  | Hold time, PIDSEL high after PCLK↑   | 1   |     | ns   |

| 6                                               | 6 t <sub>h(PIRDY)</sub> Hold time, PIRDY low after PCLK↑         |                                      | 1   |     | ns   |

## operating characteristics (see Figure 8)

|   | NO. |                        |                             | MIN | MAX | UNIT |

|---|-----|------------------------|-----------------------------|-----|-----|------|

| Ī | 7   | t <sub>d</sub> (PTRDY) | Delay time, PCLK↑ to PTRDY↓ | 2   | 11  | ns   |

Figure 8. TNETA1570 Write Operation (PCI SAR as Slave)

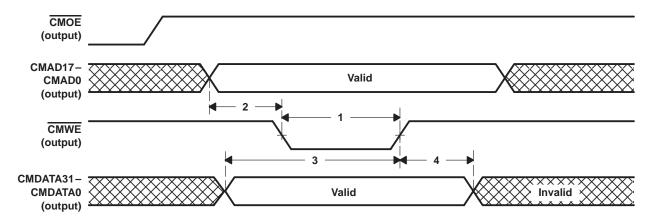

## operating characteristics (see Figure 9)

| NO. |                                                                   |                                                 | MINT | MAX† | UNIT |

|-----|-------------------------------------------------------------------|-------------------------------------------------|------|------|------|

| 1   | tw(CMWEL)                                                         | Pulse duration, CMWE low                        | 28   | 31   | ns   |

| 2   | 2 t <sub>d(CMWE)1</sub> Delay time, CMAD17 – CMAD0 valid to CMWE↓ |                                                 | 12   | 15   | ns   |

| 3   | td(CMWE)2                                                         | Delay time, CMDATA31 – CMDATA0 valid to CMWE↑   | 10   | 14   | ns   |

| 4   | <sup>t</sup> d(CMDATA)                                            | Delay time, CMWE↑ to CMDATA31 – CMDATA0 invalid | 15   | 19   | ns   |

<sup>†</sup> These values are for full-duplex operation at 33 MHz.

Figure 9. Control-Memory-Interface Write Operation

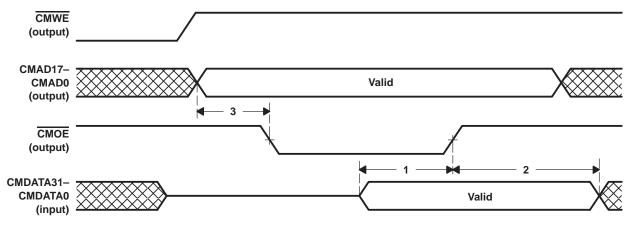

## timing requirements (see Figure 10)

| NO. |                         |                                                 | MIN† | MAX | UNIT |

|-----|-------------------------|-------------------------------------------------|------|-----|------|

| 1   | t <sub>su(CMDATA)</sub> | Setup time, CMDATA31−CMDATA0 valid before CMOE↑ | 10   |     | ns   |

| 2   | <sup>t</sup> h(CMDATA)  | Hold time, CMDATA31 – CMDATA0 valid after CMOE↑ | 0    |     | ns   |

<sup>†</sup> These values are for full-duplex operation at 33 MHz.

## operating characteristics (see Figure 10)

| NO. |                                                               | MIN | MAX | UNIT |

|-----|---------------------------------------------------------------|-----|-----|------|

| 3   | t <sub>d</sub> (CMOE) Delay time, CMAD17−CMAD0 valid to CMOE↓ |     | 3   | ns   |

Figure 10. Control-Memory-Interface Read Operation

#### PRINCIPLES OF OPERATION

| Table of Contents      |                |  |  |  |  |  |

|------------------------|----------------|--|--|--|--|--|

| Segmentation Operation | Host Interface |  |  |  |  |  |

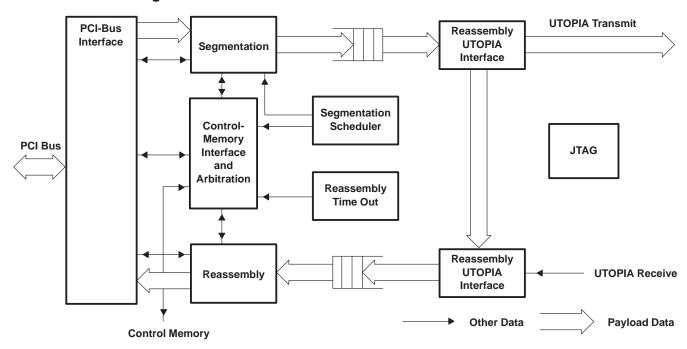

#### functional overview

The function of the TNETA1570 is centered around the entries in the TX DMA state table for segmentation and the RX DMA state table for reassembly. The entries in the tables hold information regarding what type of data to process, where to find it or store it, and the current status of the segmentation/reassembly process for the entry.

For segmentation, the scheduler table is used to select the next entry in the TX DMA state table for processing. For reassembly, the VPI and VCI fields of the incoming ATM cell are decoded using the VPI/VCI DMA pointer table to locate the entry in the RX DMA state table for processing.

The data interface to the host is the 32-bit/64-bit PCI-bus interface. The interface to the ATM layer is the UTOPIA interface.

#### functional block diagram

The TNETA1570 can be configured to transmit and receive either AAL5 or transparent-AAL packets. The segmentation and reassembly of AAL5 packets is performed in accordance with ITU-T specifications I.361 and I.363 (11/93 update). The protocol used to segment and reassemble AAL5 packets is well specified in the ITU-T documents. The protocols for segmenting and reassembling a transparent-AAL packet is not specified by any known standards body; therefore, there is no official sanction for a transparent AAL and no interoperability specification exists. However, a transparent AAL provides a convenient method for transporting proprietary control and data information or data traffic that does not fit well in a currently defined AAL (i.e., voice/video traffic).

NOTE: The terms transmit and segmentation are both used to describe the segmentation operation and the terms receive and reassemble are both used to describe the reassembly operation in this document.

#### PRINCIPLES OF OPERATION

#### segmentation overview

The segmentation operation of the TNETA1570 can operate on three types of packets: AAL5 packets, transparent (undefined)-AAL packets with end-of-packet (EOP) termination in the PTI field of the ATM header, and transparent AAL-packets without special ATM-header processing for the last cell of the packet. Up to 1023 separate virtual circuits (VCs) can be segmented concurrently, and each corresponds to its own host DMA channel maintained by the TNETA1570. Any VC (DMA channel) can be configured to segment any one of the three packet types. Each packet type is stored in host memory in either single buffers or buffer chains. The buffer-chaining mechanism allows segmentation to begin on a packet before all of the packet contents are established in buffers.

For each VC, the host establishes a VPI/VCI connection and assigns it to a transmit packet-segmentation ring that is assigned a free-segmentation DMA channel controlled by the TNETA1570. Memory structures initialized by the host for packet segmentation on a virtual channel include the scheduler table (control memory), the transmit completion-ring pointers (register), and word 3 of the DMA state entry for the DMA channel assigned to the VC (control memory). The ON bit (bit 31) of word 3 in the DMA state entry activates the DMA channel for packet segmentation. The lower 30 bits of word 3 form the packet-segmentation-ring pointer. The TNETA1570 registers that need to be initiated by the host for segmentation are the configuration register, interrupt-mask register, TX completion ring with and without interrupt registers, and TX packet-segmentation ring-size register.

When at least one buffer of a packet in an established DMA channel is prepared for processing, the RDY bit in the buffer header is set to a 1 indicating that the TNETA1570 has control of the buffer and the start-of-packet (SOP) bit is set in the header. The address of the next buffer, if used, must be known at this time and placed in the appropriate buffer-descriptor location. After this, a pointer to the first buffer of the packet is placed in the next entry of the DMA packet-segmentation ring, and the OWN bit of the entry is set to 1 indicating to the TNETA1570 that a packet is ready for processing. The host indicates the readiness of each subsequent buffer to the TNETA1570 upon completion of its contents preparation. The last buffer of a packet must have the EOP bit set in the buffer descriptor.

Upon a buffer-segmentation completion, the TNETA1570 posts an entry in the next position of a transmit-completion ring. The completion ring with and without interrupt selection is initialized by the host in the buffer descriptor. If a completion ring with interrupt entry is posted and the TNETA1570 interrupt-mask register permits, an interrupt is generated on the PCI bus and an interrupt indication is generated in the status register.

The memory structure for scheduling transmit-DMA-channel service is the scheduler table located in the control memory. The TNETA1570 continuously reads through each entry in the scheduler table from the top down. Two transmit-DMA-channel pointers are located in each 32-bit word entry in this table.

Each entry of the scheduler table is an opportunity for packet segmentation. Each entry indexes the transmit-DMA channel used to extract a single cell during packet segmentation. If the DMA channel is on, the segmentation procedure can continue. If the scheduler-table entry contains zero or the DMA channel is off, no packet segmentation is performed and the next scheduler-table entry is examined.

After determining that a transmit-DMA channel is on, packet segmentation for the channel is initiated. If the ACT bit in the TX DMA state table is set, a packet is begun and not ended. Also, if the current data-byte-count field for the entry is greater than zero, a buffer is in use and packet segmentation resumes from the DMA current buffer-address field. A current data-byte-count field of zero causes the TNETA1570 to use the next buffer-address field to acquire a new buffer from host memory before packet segmentation can begin.

When acquiring a new buffer, the RDY bit of the buffer is examined. If the RDY bit is set, the buffer descriptor is loaded into the DMA-state entry. Packet segmentation for the DMA channel is terminated for the cell opportunity if the buffer RDY bit is not set in the buffer.

#### PRINCIPLES OF OPERATION

#### segmentation overview (continued)

The last possibility for an active DMA channel is the start of a new packet. This is detected by the cleared ACT status of the DMA channel. In this case, the packet-segmentation ring-base offset pointer and its index fields of the DMA entry are used to acquire a new buffer address from the packet-segmentation ring for the virtual channel. If the packet-segmentation-ring entry is owned by the TNETA1570, the pointer contained in the entry is used to acquire a new segmentation buffer, the ACT bit of the DMA channel is set, and the packet-segmentation-ring index is incremented. Packet segmentation for the DMA channel is terminated for this cell opportunity if the packet-segmentation-ring entry is owned by the host. It is important that the host sets the RDY bit of the first buffer of a packet before setting the OWN bit of its packet-segmentation-ring entry.

The 32-bit, single and multiple data-phase PCI accesses are used by the TNETA1570 for buffer and DMA initialization information. After establishing a buffer address to acquire cell-payload data, the 4-byte ATM header contained in the DMA entry is loaded into the internal transmit FIFO. The EOP bit in the ATM header is set for the last cell of AAL5 packets and PTI-based transparent packets. If the EOP status in the DMA entry is cleared and the current-data-byte count is greater than or equal to 48, a 48-byte PCI-bus read is used to send the cell-payload contents to the transmit FIFO. If the EOP status in the DMA channel is cleared and the current-data-byte count is less than 48, the remaining bytes are acquired from the data buffer. The next data buffer is obtained using the next buffer-address field in the TX DMA state table. If segmentation is occurring on an EOP buffer, the TNETA1570 performs a PCI-bus read equal to the current-data-byte count acquiring cell payload and providing byte pad as required.

At the end of a segmentation cycle for a single buffer that is not the end of a packet, the TX DMA state table entries for current-data-byte count and current-buffer address are modified to show the number of bytes remaining in the buffer and the starting location for the next ATM-payload fill. The 64-bit, if allowed, or 32-bit multiple data-phase PCI accesses are used by the TNETA1570 for acquiring ATM payload.

When the AAL5 indicator is set in the TX DMA state table entry, the AAL5 PDU pad and trailer are added to the last cell(s) by the TNETA1570. As each 64-bit ATM-payload word is loaded in the transmit FIFO, a 32-bit CRC is calculated with the generator polynomial  $x^32 + x^26 + x^23 + x^22 + x^16 + x^12 + x^11 + x^10 + x^8 + x^7 + x^5 + x^4 + x^2 + x + x^1$ . The AAL5-packet length is also calculated on the number of nonpad bytes in the AAL5 SDU for each ATM-payload fill. At the end of each AAL5-segmentation cycle for a single cell, the partial CRC and current AAL5-packet length are updated in the TX DMA state table entry. In many cases, pad bytes (all 0) must be added after the AAL5 SDU and before the AAL5 trailer to complete cells. The 32-bit CRC is also calculated using the pad bytes and the control and length fields of the trailer.

Upon processing an AAL5 packet where the current-data-byte count of the last cell in an EOP buffer is between 0 and 40 bytes, pad bytes (all 0) are added up to the 40th payload octet. The AAL5-control field, CPCS-UU and CPI octets, stored in the TX DMA state table entry are packed in payload octets 41 and 42, and the AAL5 length-field calculated across the SDU (not including the pad) is placed in octets 43 and 44. The 32-bit CRC for the PDU calculated across the packet data, pad, control, and length fields is inverted and placed in octets 44 through 48. For the last cell in an EOP buffer, which is filled with exactly 40 bytes from the segmentation buffer, no pad is added. After processing the last cell of the packet, the DMA ACT bit is cleared.

When processing a cell in the last buffer of an AAL5 packet with the current-data byte-count field in the TX DMA state table entry between 41 and 48 bytes, the pad is added up to the 48th octet. The segmentation unit creates an empty cell including the 8-byte AAL5 trailer. The current-data-byte count in the TX DMA state table entry is set to zero, but the ACT bit remains set.

Two methods are available for transmitting a transparent-AAL packet. The first method is basically the same as the procedure for transmitting an AAL5 packet, except that no 8-byte trailer (control, length, and 32-bit CRC) is generated and transmitted. The TNETA1570 adds any padding necessary to complete the 48-byte cell payload. The last cell in the transparent-AAL packet has the PTI bits modified to indicate that this is the last cell in the packet, (i.e., the PTI bits is set to  $0 \times 1$ ). Abort processing is disabled for transparent-AAL packets.

#### PRINCIPLES OF OPERATION

#### segmentation overview (continued)

The second method for transmitting a transparent-AAL packet differs from the first method only in that the PTI bits in the last cell of the packet are not modified. The PTI bits are transmitted as they occur in the descriptor entry for all cells in the packet. This method can be used to transmit VC-level OAM cells, which are single cell packets that set the PTI bits to a value of I0x.

After segmenting the contents of a buffer, the current-data-byte count for the DMA entry is set to zero. The OWN bit of the next entry of the completion ring selected for the channel is examined. If the entry is owned by the host, the transmit-freeze bit in the status register is set and an interrupt is generated. Otherwise, a pointer to the start of the buffer is placed in the entry.

The size of the internal transmit FIFO is four cells. The UTOPIA interface for the segmentation unit can operate asynchronous to the PCI bus as cells are read from the transmit buffer in 8-bit bytes. The HEC byte for the ATM header is calculated byte wise and inserted in the fifth-header octet as a cell is read. When the HEC error bit in the configuration register is set, the HEC byte is inverted prior to being inserted into the outgoing byte stream for test purposes. The segmentation UTOPIA bus implements parity generation.

#### reassembly overview

For reassembly operation, the host must allocate memory for the following memory data structures: data buffers with descriptor entries, completion ring with/without interrupt pointers, the receive-free buffer rings/receive-free buffer FIFO, the RX VPI/VCI DMA pointer table, and a DMA state table entry for each VCI. The TNETA1570 registers, which need to be initialized by the host for reassembly, are the configuration register, the interrupt-mask register, the reassembly-global-timer register, the RX DMA-state-table register, the completion ring with/without interrupt-size register, and the FIFO free-buffer-size register.

Free buffers are fetched using either the receive free-buffer ring or the receive free-buffer FIFO. If the free-buffer rings are used, the lower eight bits of word 6 of the DMA state table entry are read to obtain the index for the free-buffer rings. The index points to one of the 256 entries in the free-buffer-ring-pointer table. Each entry contains the base address of each free-buffer ring, as well as the buffer size, the ring size, and the current index. If the free-buffer FIFO is used, a read on the address in word 6 of the DMA state table provides the starting address of a free buffer.

If the receive free-buffer-ring method is used, the host sets the OWN bit of a completion-ring entry to indicate that the buffer is available for use by the TNETA1570. If no free buffers are available, buffer starvation occurs and the reassembly of the packet is terminated.

The completion ring with/without interrupt is initialized by the host in the DMA state table entry. If a completion ring with interrupt entry is posted and the TNETA 1570 interrupt-mask register allows, an interrupt is generated on the PCI bus and an interrupt indication is placed in the status register. A bit in the configuration register can be set so that an interrupt is posted at the completion of the segmentation of either a packet or a buffer.

The VPI of an incoming cell is used as an index into the VPI/VCI DMA pointer-table entry, which resides in control memory. The information in the VPI/VCI DMA pointer table is used to determine if the VPI is enabled to receive packets and if the VCI is within the valid range for the corresponding VPI. The index value in the VPI/VCI pointer table together with the VCI value of the ATM cell are used to form the address of the DMA state-table entry for that particular VCI. If a VCI is found to be out of range, an interrupt is generated.

If the PTI value of the incoming cell is 100, the cell is an OAM F5-segment cell. If the PTI value of the incoming cell is 101, the cell is an OAM F5 end-to-end cell. Both OAM cells are routed to DMA channel 0. If the PTI value is 110 or 111, the cell is routed to DMA channel 1. If the VCI value of the incoming cell is three, the cell is an OAM F4 segment cell. If the VCI value of the incoming cell is four, the cell is an OAM F4 end-to-end cell and both F4 OAM cells are routed to channel 2.

#### PRINCIPLES OF OPERATION

#### reassembly overview (continued)

If the VPI is on, the DMA entry is enabled, the wait on EOP is cleared, the VCI is in range, and the TNETA1570 owns the free buffer, the TNETA1570 begins the reassembly process for the incoming cell.

Word 0 of the free-buffer descriptor is copied to word 2 of the DMA state table entry to get the start-buffer address. If the receive free-buffer rings are used, the lower 16 bits of word 3 in the state table, the current data-byte count, is copied from word 1 of the appropriate receive free-buffer ring-pointer entry. If the receive free-buffer FIFO is used, the lower 16 bits of word 3 in the state table are copied from the FIFO free-buffer-size register. If the cell is a SOP, word 0 of the descriptor entry is copied to word 4 of the state table to keep track of the first buffer in the packet. When this is completed, transfer of the cell to host memory occurs.

The current-data-byte count is decremented by one for each cell transmitted to the host. If the current-data-byte count reaches zero and an EOP has not yet arrived, a new buffer is fetched either from the free-buffer ring or the FIFO.