# Using the Extended Port Awareness Feature of the TNETX4090 ThunderSWITCH

APPLICATION REPORT:

SPWA018A

Enterprise Business Unit Network and Computer Products April 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated

#### TRADEMARKS

$\ensuremath{\mathsf{TI}}$  and  $\ensuremath{\mathsf{ThunderSWITCH}}$  are trademarks of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### **CONTACT INFORMATION**

| PIC Telephone | (972) 644-5580  |

|---------------|-----------------|

| PIC FAX       | (972) 480-7800  |

| Email         | networks@ti.com |

| Abstract                                                | 7  |

|---------------------------------------------------------|----|

| System Overview                                         |    |

| Crossbar Matrix/TNETX4090 Interface                     |    |

| Pre-Tag                                                 |    |

| Transmit Pre-Tag                                        |    |

| Learning Format Receive Pre-Tag                         | 11 |

| Directed Format Receive Pre-Tag                         | 12 |

| TNETX4090 Configuration                                 | 14 |

| System Control Configuration                            |    |

| Port 08 Configuration                                   |    |

| Extended Addresses                                      |    |

| xroutecodes/xportcodes                                  | 23 |

| Appendix A.Crossbar-Matrix Switch Design Considerations | 26 |

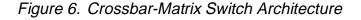

| Crossbar-Matrix Switch                                  |    |

| Crossbar-Matrix Port                                    |    |

| Crossbar-Matrix Design Criteria                         | 28 |

| Appendix B.Product Support                              | 29 |

| Related Documentation                                   |    |

| World Wide Web                                          |    |

| Email Support                                           |    |

# Contents

# Figures

| Figure 1. | High Port Density System            | 8 |

|-----------|-------------------------------------|---|

| Figure 2. | GMII Interface                      | 9 |

| •         | Transmit Pre-Tag Timing Diagram     |   |

|           | Receive Pre-Tag Timing Diagram      |   |

|           | AddPort Register – Multicast Format |   |

| Figure 6. | Crossbar-Matrix Switch Architecture |   |

# Tables

| SysControl Register               | 14                                                                                                                                                                                            |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |                                                                                                                                                                                               |

| Port08Control Register            | 18                                                                                                                                                                                            |

| Port8QTAG Register                | 19                                                                                                                                                                                            |

| AddPort Register – Unicast Format | 19                                                                                                                                                                                            |

| XMultiGroup17 - 63 Registers      | 23                                                                                                                                                                                            |

|                                   |                                                                                                                                                                                               |

|                                   | SysControl Register<br>FlowThreshold Register<br>Port08Control Register<br>Port8QTAG Register<br>AddPort Register – Unicast Format<br>XMultiGroup17 - 63 Registers<br>xroute/xport Code Table |

# Using the Extended Port Awareness Feature of the TNETX4090 ThunderSWITCH

# Abstract

This document describes how the extended port awareness feature of the Texas Instruments (TI<sup>™</sup>) ThunderSWITCH<sup>™</sup> TNETX4090 enables system vendors to design a high port density system.

The TNETX4090 gigabit port (port 08) can be configured to support extended port awareness. This feature allows the TNETX4090 to comprehend a proprietary in-band-pre-tagging scheme, which replaces the preamble and start of frame (SOF) delimiter. The pre-tag contains, among other information, the forwarding decision to an extended port, which could be comprehended by a crossbar matrix switch. By designing a relatively simple and cheap crossbar matrix switch, a nonblocking, high port density system is achievable.

# **System Overview**

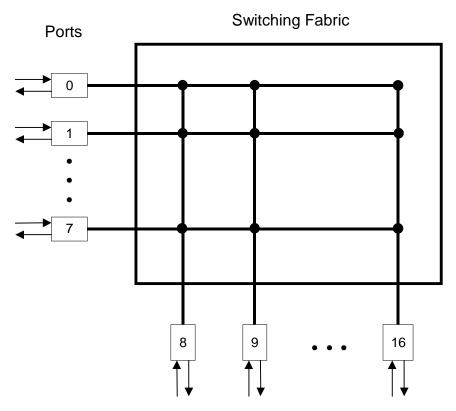

The extended port awareness allows the TNETX4090 to be aware and perform forwarding and filtering decisions of up to 17 ports that would be residing on the crossbar matrix switch (see Figure 1). The proprietary in-band pre-tags contain the forwarding decision that allows the crossbar matrix to be relatively simple and inexpensive.

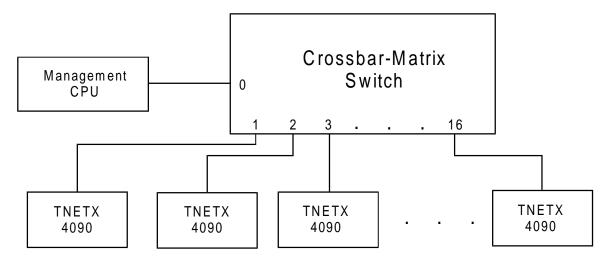

Figure 1 shows a block diagram of a high port density system:

Figure 1. High Port Density System

It is recommended that one port on the crossbar matrix be used as the network management port for the system. The management CPU receives frames forwarded by the TNETX4090 devices. Depending on the higher layer functionality the system supports, the TNETX4090 devices can be configured to forward BPDUs for the spanning tree algorithm, SNMP packets for network management, and IGMP frames for IP multicast to the management CPU. Note that if an external CPU is connected to the crossbar-matrix switch, the CPU must supply the correct CRC for the frames it will source.

#### NOTE:

The TNETX4090 devices must be configured by either a CPU or an EEPROM. It is recommended that the Management CPU be used configure the TNETX4090 devices. To manage the entire system, the Management CPU should be able to perform all operations listed in the *TNETX4090 Programmer's Reference Guide* on each individual device.

#### Crossbar Matrix/TNETX4090 Interface

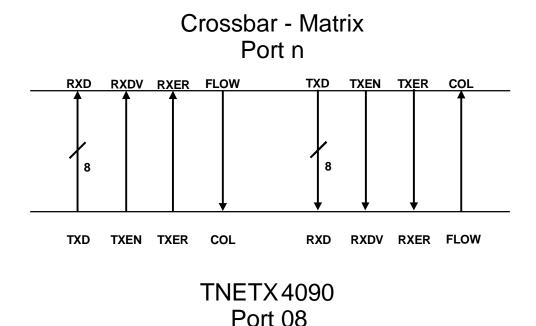

The crossbar matrix switch must interface with the TNETX4090 via the GMII interface (see Figure 2).

Figure 2. GMII Interface

To prevent the loss of data, it is recommended that the crossbar matrix switch support flow control. When the TNETX4090 experiences congestion (that is, the flow control threshold has been crossed), the **FLOW** pin is asserted. When the **FLOW** pin is asserted, the crossbar matrix switch must stop transmitting frames to the congested TNETX4090.

Likewise, when the crossbar matrix switch experiences congestion, it must assert its **FLOW** pin (which must be connected to the TNETX4090 **COL** pin). When the TNETX4090 samples **COL** as asserted, it prevents transmitting frames to the crossbar switch.

#### NOTE:

Refer to the *TNETX4090 Single-Chip 100/1000 Device* data sheet for timing on the GMII interface.

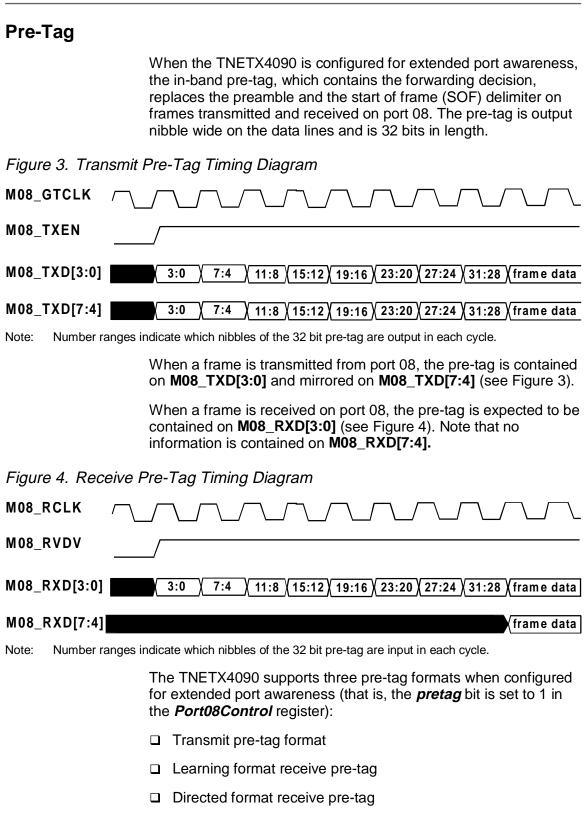

#### **Transmit Pre-Tag**

Transmit pre-tag format is used when the frame is transmitted from the TNETX4090 to the crossbar matrix switch. The pre-tag contains the forwarding decision (that is, *xportvector* indicates the destination portvect), an indication of whether an 802.1Q-like header was inserted (that is, the *rxheader* bit), and which port on the TNETX4090 received the frame (that is, *portcode*).

| Bit   | Name        | Function                                                                                                                                                                                                                                                            |

|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:28 | Reserved    | These bits will always be zero.                                                                                                                                                                                                                                     |

| 27    | rxheader    | This bit indicates whether the receiving MAC added an 802.1Q-like header (i.e. TI header) to the frame. See note below for detail.                                                                                                                                  |

|       |             | <i>rxheader</i> = 1, an 802.1Q-like header was added to the frame                                                                                                                                                                                                   |

|       |             | <i>rxheader</i> = 0, an 802.1Q-like header was not added to the frame                                                                                                                                                                                               |

| 26:25 | Reserved    | These bits will always be zero.                                                                                                                                                                                                                                     |

| 24:20 | portcode    | This bit field indicates which port on the TNETX4090 received the frame. Valid <i>portcodes</i> are 0b00000 – 0b01001, which indicate port 00 through port 09 (port 09 is the network management DIO port). All other codes are reserved and will not be generated. |

| 19:17 | Reserved    | These bits will always be zero.                                                                                                                                                                                                                                     |

| 16:0  | xportvector | A bit position set to 1 indicates that the frame must be forwarded to that port on the crossbar matrix switch. A multicast may have several bit set in the vector. The TNETX4090 never forwards a frame with a <i>xportvector</i> of all 0s.                        |

The *rxheader* bit indicates to the Management CPU whether the port that received the frame added an 802.1Q-like header. The Management CPU must use this information and create a frame with or without the 802.1Q-like header when sending a frame to a TNETX4090 port. (For detailed information on the 802.1Q-like header (TI header), refer to the *TNETX4090 Programmer's Reference Guide*.)

#### Learning Format Receive Pre-Tag

Learning format receive pre-tag is used when the TNETX4090 receives a frame sourced from a data port on the crossbar matrix switch (that is, not sourced from the management CPU port). It is the responsibility of the crossbar matrix switch to alter the transmit pre-tag to a learning format receive pre-tag.

| Bit  | Name      | Function                                                                                                                                                                                                                                  |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31   | type      | Receive frame indicator. When bit 31 equals 0, the receive pre-tag is learning format.                                                                                                                                                    |

| 30:5 | Reserved  | These bits will be ignored                                                                                                                                                                                                                |

| 4:0  | cportcode | Indicates which port on the crossbar matrix switch received the frame.<br>Valid <i>cportcodes</i> are 0b00000 – 0b10000 which indicate crossbar<br>matrix switch ports 0 through 16. All other codes are reserved and will<br>be ignored. |

The source address of a frame received on the TNETX4090 with a learning format receive pre-tag will be learned. The port on which this node resides (according to the TNETX4090) is the *cportcode* of the frames pre-tag. The frame is forwarded according to the frame routing algorithm using the destination address of the frame.

It must be pointed out that the TNETX4090 converts the *cportcode* into a *xportcode*. The *xportcode* is stored in the TNETX4090's address table.

#### NOTE:

The TNETX4090 uses the *xportcode* to create the transmit pre-tag when forwarding a frame to the particular node on an extended port.

#### **Directed Format Receive Pre-Tag**

The directed format receive pre-tag is used when the frame is sourced from the management port on the crossbar matrix switch.

| Bit   | Name       | Function                                                                                                                                                                                                                                               |

|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | type       | Receive frame indicator. When bit 31 equals 1, the receive pre-tag is directed format.                                                                                                                                                                 |

| 30:10 | Reserved   | These bits will be ignored                                                                                                                                                                                                                             |

| 9:0   | portvector | A bit position set to 1 indicates that the frame must be forwarded to that port on the TNETX4090 (bit 9 set to 1 indicates the destination is the NM port). Several bits may be set in the <i>portvector</i> to send the same frame to multiple ports. |

Frames in directed format bypass T-Bird's frame routing algorithm (see the TI *TNETX4090 Programmer's Reference Guide* for information on the frame routing algorithm). It does not matter if the frame is multicast or unicast, the destination address known or unknown; the frame is forwarded only to the ports as specified in the *portvector* of the pre-tag. (If the *portvector* is set to all 0s, the frame will be discarded by theTNETX4090). If port 08 (that is, the source port) is set in the *portvector*, the frame is forwarded back out on port 08.

To support the spanning tree algorithm on the external CPU (the CPU connected to the crossbar-matrix switch), the *TxBlockPorts*, *RxUniBlockPorts*, and *RxMultiBlockPorts* registers have no effect on the reception or transmission of a frame in direct format.

# **TNETX4090** Configuration

This section focuses on the configuration of the TNETX4090 when connected to a crossbar-matrix switch, including:

- □ How to configure the *SysControl* register and port 08 to interface correctly with the crossbar-matrix switch

- □ How nodes on the crossbar-matrix switch ports are addressed

- How the xroute codes work in conjunction with features such as mirroring, unknown destination and VLAN, and unknown source

Please refer to the *TNETX4090 Programmer's Reference Guide* regarding all other aspects of configuring the TNETX4090.

# **System Control Configuration**

The system must prevent data from being lost due to congestion by utilizing flow control. For the system to support flow control, the *flow* bit in the *SysControl* register must be set to 1.

Table 1. SysControl Register

| Bit         | 15          | 14               | 13               | 12                    | 11  | 10     | 9     | 8                               | 7                | 6                     | 5                          | 4                                    | 3           | 2                     | 1                | 0                |                                  |

|-------------|-------------|------------------|------------------|-----------------------|-----|--------|-------|---------------------------------|------------------|-----------------------|----------------------------|--------------------------------------|-------------|-----------------------|------------------|------------------|----------------------------------|

| Field Name  | s<br>t<br>p | l<br>o<br>a<br>d | s<br>t<br>r<br>t | i<br>n<br>I<br>t<br>d | Res | erved[ | 11:9] | с<br>n<br>o<br>t<br>i<br>f<br>v | n<br>a<br>g<br>e | d<br>m<br>I<br>n<br>c | u<br>n<br>V<br>I<br>a<br>n | p<br>o<br>r<br>t<br>c<br>o<br>d<br>e | m<br>I<br>r | n<br>a<br>u<br>t<br>o | n<br>c<br>r<br>c | f<br>I<br>o<br>W | Byte<br>Address<br>Offset<br>0x0 |

| Reset value | 0           | 0                | 0                | 0                     | 0   | 0      | 0     | 0                               | 0                | 0                     | 0                          | 0                                    | 0           | 0                     | 0                | 0                |                                  |

| Reset type  | h           | h                | h                | hs                    | -   | -      | -     | h                               | h                | h                     | h                          | h                                    | h           | h                     | h                | h                |                                  |

| Field type  | rw          | rw               | rwl              | r                     | r   | r      | r     | rwl                             | rwl              | rwl                   | rwl                        | rwl                                  | rwl         | rwl                   | rwl              | rwl              |                                  |

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                 |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | stop | <i>Stop system.</i> When <i>stop</i> = 1, device operation is halted and will remain so until this bit is cleared to zero. All internal state machines, FIFOs, and MACs are reset. Register bits are cleared as per the register definition tables in this section. The HOST registers are not affected. Any data in the device Is lost. |

|     |      | This bit will become set to one if an EEPROM load fails because of a bad<br>CRC word.                                                                                                                                                                                                                                                    |

|     |      | This bit will become set to one if a parity error is detected on the external memory interface.                                                                                                                                                                                                                                          |

| Bit  | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | load     | Load System. Writing a 1 to this bit causes the DIO registers to be auto-<br>loaded from an external EEPROM (if present). Writing a zero to this bit has<br>no effect. Writing a one to this bit also clears the CRC-error indication from<br>the fault-LED. All DIO operations are inhibited ( <b>SRDY</b> will be held inactive<br>high) while <i>load</i> is a one once the EEPROM state machine has finished<br>checking that <b>EDIO</b> is not held at zero, and begins to download data. <i>Load</i><br>will clear to zero once the download is completed.<br>When this bit is written with a one the <b>stop</b> bit should simultaneously be<br>written with a zero.                                              |

| 13   | start    | Start system. Writing a one to this bit causes the device to begin operation following a reset or stop. This bit will be read as a one until buffer and address lookup memory initialization is complete. This will result in any previous frames or address records being erased. While the memory is being initialized all ports are disabled. All DIO writes are inhibited ( <b>SRDY</b> inactive high) while <b>start</b> is a one. Writing a one to this bit also clears the parity-error indication from the fault-LED. Writing a zero to this bit has no effect, as does writing a one when <b>initd</b> – 1. When this bit is written with a one the <b>stop</b> bit should simultaneously be written with a zero. |

| 12   | Initd    | <i>Initialization Done.</i> This bit becomes a one after <i>start</i> has been set, and buffer and address lookup memory initialization is complete (i.e. at the same time <i>start</i> is cleared). Once set, it remains so until a hard reset (pin or DIO), or until <i>stop</i> is set to one. Until this bit becomes a one the ports will ignore any frames they receive.                                                                                                                                                                                                                                                                                                                                              |

| 11:9 | reserved | Reserved. Writes to these bits have no effect. They always read as zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8    | cnotify  | <ul> <li>Change Notification. Determines what action is taken when a known source address is received on a port other than the one currently associated with the address:</li> <li>If cnotify = 0, change notification is disabled.</li> <li>If cnotify = 1, change notification is enabled. The frame is additionally forwarded to the ports specified by UnkSrcPorts ANDed with the appropriate VLANnPorts register, provided that address learning is enabled for the port the address has moved to (appropriate bit in NlearnPorts = 0). This allows the address lookup tables of other switches to be updated in accordance with the change.</li> </ul>                                                               |

| 7    | nage     | <ul> <li>No aging: Allows automatic address-record aging to be disabled independent of learning. (<i>nauto</i> – 1 disables both learning and aging).</li> <li><b>Nage</b> = 1 aging is disabled even if <i>nauto</i>=0.</li> <li><b>Nage</b> = 0 aging is enabled unless <i>nauto</i>=1.</li> <li>If <i>nauto</i>=1 then the value of <i>nage</i> is don't care – aging will be disabled. This bit has no effect on address learning or time-stamp updating.</li> </ul>                                                                                                                                                                                                                                                   |

| 6    | dmainc   | <ul> <li>DMA Address Autoincrement. When accessing the DIO interface with a DMA controller (SDMA pin low), this bit determines whether the address held in <i>dmaadress</i> should be incremented between successive accesses or not:</li> <li>Dmainc = 1, the address will increment between accesses.</li> <li>Dmainc = 0, the address will not increment between accesses.</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | Ishare  | <ul> <li>Load Sharing. If a frame is destined for a port which is part of one of the trunk groups defined by the <i>Trunk0Ports – Trunk3Ports</i> registers, the eight entry lookup table formed by the <i>TrunkMap0 – TrunkMap7</i> registers is used to determine which member of the trunk group the frame will be transmitted on. This bit determines how to index into the lookup table:</li> <li><i>Lshare</i> = 1, if the destination address is unknown, the index is computed using the source address only by exclusive-ORing bits 47:32, 31:16 and 15.0 that address. If the destination address is known, the frame will be routed according to the port associated with the address.</li> <li><i>Lshare</i> = 0, the index is computed using both the source and destination</li> </ul> |

|     |         | addresses, by bitwise exclusive-ORing bits 3:1 of the destination address with bits 3:1 of the source address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4   | unkvlan | Unknown VLAN Forwarding. This bit enables forwarding of multicast frames that have an unknown IEEE802.1Q VLAN Identifier (i.e. one that matches none of the VLAN Ids registered in <b>VLANOQID</b> – <b>VLAN63QID</b> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | <ul> <li>Unkvlan = 1, all multicast frames belonging to unknown VLANs will be forwarded to the port indicated in UnkVLANPort.</li> <li>Unkvlan = 0, all multicast frames belonging to unknown VLANs will be discarded.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | mirr    | Port Mirroring. This bit enables port mirroring.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | Mirr = 1, all frames received on or sent to the port specified in MirrorPort will be copied to the port specified in UplinkPort.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | □ <i>Mirr</i> = 0, no mirroring is performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2   | nauto   | <i>NOT Automatically Add Address Mode.</i> This bit selects the manner in which addresses will be added to the address records:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |         | Nauto = 1, addresses can only be added to the records using DIO adds.<br>The aging state machine will be disabled; it is management's responsibility<br>to manage the address records.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |         | Nauto = 0, new addresses will be learned from the wire and added to the address tables automatically. (They can also be added using DIO adds). If however nage=1 and the address tables become full then further addresses will not be added unless space is first created using DIO deletes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | ncrc    | <i>No CRC Check.</i> This bit determines whether addresses are learned if the frame containing them contains an invalid CRC:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | Ncrc = 1, new addresses are added to the lookup table without regard for<br>the validity of the CRC. Unknown addresses will be added to the lookup<br>table automatically.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |         | Ncrc = 0, new addresses can only be added to the lookup table if the frame containing the address has a valid CRC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | flow    | <ul> <li>Flow Control Enable. This bit enables flow control:</li> <li>Flow = 1, the device will implement flow control. Ports configured for IEEE 802.3X will use pause frames. Ports thatare not will use collisions.</li> <li>Flow = 0, no flow control will be implemented.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

When the TNETX4090's buffer threshold has been broken (that is, the TNETX4090 is considered to be congested) the **FLOW** pin will be asserted. The **FLOW** pin holds off the crossbar-matrix switch from transmitting frames to the TNETX4090. (See Appendix A for details.)

The TNETX4090's buffer threshold is configurable via the *FlowThreshold* register. When the external RAM contains fewer free buffers then the threshold value then the TNETX4090 is considered congested.

| Bit               | 15  | 14  | 13  | 12  | 11       | 10  | 9    | 8      | 7                   | 6     | 5      | 4             | 3      | 2        | 1      | 0             |                    |

|-------------------|-----|-----|-----|-----|----------|-----|------|--------|---------------------|-------|--------|---------------|--------|----------|--------|---------------|--------------------|

| Field Name        |     |     |     |     |          |     | Flov | vthres | hold[1              | 15:0] |        |               |        |          |        |               | Byte               |

| Reset value       | 0   | 0   | 0   | 0   | 0        | 0   | 0    | 0      | 0                   | 0     | 1      | 0             | 1      | 0        | 0      | 0             | Address<br>Offset0 |

| Reset type        | h   | h   | h   | h   | h        | h   | h    | h      | h                   | h     | h      | h             | h      | h        | h      | h             | 0x0                |

| Field type        | rwl | rwl | rwl | rwl | rwl      | rwl | rwl  | rwl    | rwl                 | rwl   | rwl    | rwl           | rwl    | rwl      | rwl    | rwl           |                    |

|                   |     |     |     |     |          |     |      |        |                     |       |        |               |        |          |        |               |                    |

| Bit               | 2   | 3   | 2   | 2   | 2        | :1  | 2    | 0      | 1                   | 9     | 1      | 8             | 1      | 7        | 1      | 6             |                    |

| Bit<br>Field Name | 2   | 3   | 2   | 2   | 2        | :1  |      | -      | <b>1</b><br>d[23:10 | -     | 1      | 8             | 1      | 7        | 1      | 6             | Byte               |

|                   | 2   | -   | 2   |     | <b>2</b> | 0   |      | -      |                     | -     | 1<br>1 | <b>8</b><br>0 | 1<br>1 | <b>7</b> | 0<br>1 | <b>6</b><br>0 | Address            |

| Field Name        |     | -   | I – |     | I –      |     | re   | eserve | d[23:1              | 6]    | 1<br>1 | -             | 1<br>1 |          |        |               | ,                  |

Table 2. FlowThreshold Register

| Bit   | Name          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23:16 | reserved      | Reserved. Writes to these bits have no effect. They always read a 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15:0  | flowthreshold | <i>Flow-control threshold value.</i> When the number of free buffers in external memory that are available for frame reception drops below this value then flow control is initiated (providing <i>flow</i> is set to one in <i>SysControl</i> ). Flow-control ceases when the free-buffer count equals or exceeds the value. Note that depending on the amount of memory in the system it may be possible to program this value to be greater than the total number of buffers in the system, thereby permanently inducing flow control. |

# **Port 08 Configuration**

For the TNETX4090 to interface correctly to the crossbar-matrix switch, the Gigabit port (port 08) must be configured correctly. This is accomplished by configuring both the *Port08Control* and *Port8QTag* registers.

#### Table 3. Port08Control Register

| Bit         | 15 | 14                              | 13 | 12                         | 11               | 10               | 9                     | 8           | 7                          | 6                          | 5                          | 4                          | 3                     | 2                     | 1                          | 0                     |                                    |

|-------------|----|---------------------------------|----|----------------------------|------------------|------------------|-----------------------|-------------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------|-----------------------|----------------------------|-----------------------|------------------------------------|

| Field Name  |    | r<br>e<br>s<br>r<br>v<br>e<br>d |    | m<br>a<br>x<br>I<br>e<br>n | t<br>x<br>c<br>c | r<br>x<br>c<br>c | p<br>r<br>e<br>t<br>g | n<br>e<br>g | d<br>I<br>s<br>b<br>I<br>e | r<br>e<br>n<br>t<br>x<br>p | l<br>c<br>k<br>r<br>e<br>f | r<br>e<br>n<br>r<br>x<br>p | r<br>e<br>p<br>m<br>a | r<br>e<br>1<br>0<br>0 | t<br>x<br>p<br>a<br>c<br>e | r<br>e<br>q<br>h<br>d | DIO<br>Address<br>0x0000<br>+0x2★x |

| Reset value | 0  | 0                               | 0  | 0                          | 1                | 1                | 0                     | 1           | 0                          | 0                          | 0                          | 0                          | 0                     | 0                     | 0                          | 0                     |                                    |

| Reset type  |    |                                 |    | h                          | h                | h                | h                     | h           | h                          | Н                          | h                          | h                          | h                     | h                     | h                          | h                     |                                    |

| Field type  | r  | r                               | r  | rwl                        | rwl              | rwl              | rwl                   | rwl         | rwl                        | rwl                        | rwl                        | rwl                        | rwl                   | rwl                   | rwl                        | rwl                   |                                    |

The maxlen bit is the only bit of the Port8Control register that is up to the user to configure. All other bits in this register must be set to the values listed in the following table to support the extended port awareness feature.

| Bit | Name    | Value  | Explanation                                                                                                                          |

|-----|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| 12  | maxlen  | 0 or 1 | User configurable to support 1518-byte or 1535-byte frames.                                                                          |

| 11  | txacc   | 0      | Prevent the Gigabit MAC from stripping the VLAN tag.                                                                                 |

| 10  | rxacc   | 0      | Prevent the Gigabit MAC from adding a VLAN tag.                                                                                      |

| 9   | pretag  | 1      | Configures the Gigabit port to comprehend extended port pretags.                                                                     |

| 8   | neg     | 0      | Prevents the Gigabit MAC from advertising its capability.                                                                            |

| 7   | disable | 0      | Port 08 must be enabled.                                                                                                             |

| 6   | reqntxp | 1      | Prevents the Gigabit MAC from generating 802.3X pause frames.<br>Flow control is accomplished via the <b>FLOW</b> pin.               |

| 5   | lckref  | 0      | Lock to reference feature is not used when port 08 is connected to a crossbar-matrix switch.                                         |

| 4   | reqnrxp | 1      | Prevents the Gigabit MAC from comprehending 802.3X pause frames. Flow control is accomplished via the <b>FLOW</b> pin.               |

| 3   | reqpma  | 0      | The Gigabit port must interface to the crossbar-matrix switch via the GMII. Port 08 must not be configured in PCS mode.              |

| 2   | req100  | 0      | Port 08 must be configured for 1000Mbps mode.                                                                                        |

| 1   | txpace  | 0      | Prevents the Gigabit MAC from using <i>txpace</i> (mode can only be used when connecting to other TI devices which supports txpace). |

| 0   | reqhd   | 0      | Port 08 must be configured for full duplex.                                                                                          |

The **Port8QTag** register must be configured to 0x000 because the Gigabit port is used as a backplane for the system. As such, the port must be transparent to the system. This means that the Gigabit port must not add or strip a VLAN tag off a frame. This is accomplished by configuring both the **txacc** and **rxacc** bits in the **Port08Control** register to 0 and the **Port8QTag** register to 0x000.

| Bit         | 15 | 14     | 13     | 12 | 11  | 10  | 9   | 8   | 7   | 6      | 5      | 4   | 3   | 2   | 1   | 0   |                   |

|-------------|----|--------|--------|----|-----|-----|-----|-----|-----|--------|--------|-----|-----|-----|-----|-----|-------------------|

| Field Name  | re | eserve | d[15:1 | 2] |     |     |     |     | I   | Vlanqi | d[11:0 | 1   |     |     |     |     | DIO               |

| Reset value | 0  | 0      | 0      | 0  | 0   | 0   | 0   | 0   | 0   | 0      | 0      | 0   | 0   | 0   | 0   | 1   | Address<br>0x0000 |

| Reset type  | -  | -      | -      | -  | h   | h   | h   | h   | h   | h      | h      | h   | h   | h   | h   | h   | +0x2★x            |

| Field type  | r  | r      | r      | r  | rwl | rwl | rwl | rwl | rwl | rwl    | rwl    | rwl | rwl | rwl | rwl | rwl |                   |

#### Table 4. Port8QTAG Register

| Bit   | Name          | Function                                                                                                                                                                                                                                 |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | reserved      | Reserved. Writes to these bits have no effect. They always read a 0.                                                                                                                                                                     |

| 15:0  | flowthreshold | <i>IEEE 802.1Q VLAN Identifier</i> . Identifies the default IEEE 802.1Q VLAN ID associated with each port. How it is used depends on the value of <i>rxacc</i> in <i>PortxControl</i> :                                                  |

|       |               | rxacc = 1, an IEEE 802.1Q tag header is always added to the frame<br>(even if the frame is already tagged). The default source port VLAN ID<br>ccontained in this field is used.                                                         |

|       |               | Rxacc = 0, if a received frame contains no IEEE 802.1Q tag header,<br>one is added using the default source port VLAN ID contained in this<br>field. If the frame has a tag header with an ID of 0x000, it is replaced<br>by this field. |

# **Extended Addresses**

Nodes residing on extended crossbar matrix ports can be learned from the wire (the frame received on port 08 must contain a pretag with learning format) or via the DIO. Multicasts can only be learned via the DIO interface. (For detailed information on how to add and delete address records as well as search the address records table, see the *TNETX4090 Programmer's Reference Guide*.)

| Table 5. | AddPort Register – Unicast Format |  |

|----------|-----------------------------------|--|

|----------|-----------------------------------|--|

| Bit         | 15 | 14 | 13 | 12     | 11     | 10 | 9  | 8  | 7  | 6                                    | 5  | 4  | 3      | 2      | 1  | 0  |                                   |

|-------------|----|----|----|--------|--------|----|----|----|----|--------------------------------------|----|----|--------|--------|----|----|-----------------------------------|

| Field Name  |    |    | r  | eserve | d[15:8 | ;] |    |    |    | r<br>e<br>s<br>e<br>r<br>v<br>e<br>d |    | x  | portco | ode[5: | 0] |    | Byte<br>Address<br>Offset0<br>0x0 |

| Reset value | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 0  | 0                                    | 0  | 0  | 0      | 0      | 0  | 0  |                                   |

| Reset type  | -  | -  | 1  | 1      | -      | 1  | h  | h  | h  | h                                    | h  | h  | h      | h      | h  | h  |                                   |

| Field type  | r  | r  | r  | r      | r      | r  | rw | rw | rw | rw                                   | rw | rw | rw     | rw     | rw | rw |                                   |

| Bit         | 31                    | 30                    | 29                         | 28                         | 27          | 26 | 25 | 24 | 23 | 22   | 21     | 20    | 19 | 18 | 17 | 16 |                                   |

|-------------|-----------------------|-----------------------|----------------------------|----------------------------|-------------|----|----|----|----|------|--------|-------|----|----|----|----|-----------------------------------|

| Field Name  | n<br>b<br>I<br>c<br>k | s<br>c<br>u<br>r<br>e | l<br>o<br>c<br>k<br>e<br>d | c<br>u<br>p<br>I<br>n<br>k | n<br>e<br>W |    |    |    |    | Rese | rved[2 | 6:16] |    |    |    |    | Byte<br>Address<br>Offset0<br>0x2 |

| Reset value | 0                     | 0                     | 0                          | 0                          | 0           | 0  | 0  | 0  | 0  | 0    | 0      | 0     | 0  | 0  | 0  | 0  | 072                               |

| Reset type  | h                     | h                     | h                          | h                          | h           | h  | h  | h  | _  | _    | _      | _     | -  | _  | _  | _  |                                   |

| Field type  | rw                    | rw                    | rw                         | rw                         | rw          | rw | rw | rw | r  | r    | r      | r     | r  | r  | r  | r  |                                   |

| Bit  | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31   | nblck     | Not Blocked Flag. This bit sets the <b>RxUniBlockPorts</b> override function.                                                                                                                                                                                                                                                                                                                |

|      |           | □ <i>Nblck</i> = 1, <i>RxUniBlockPorts</i> will not be used to filter frames.                                                                                                                                                                                                                                                                                                                |

|      |           | <b>Nblck</b> = 0, frames will be forwarded only if the appropriate                                                                                                                                                                                                                                                                                                                           |

|      |           | <b>RxUniBlockPorts</b> bit for the source port is not set. Locked against modification while an Add is in progress – writes have no effect.                                                                                                                                                                                                                                                  |

| 30   | secure    | <i>Secured Address Flag.</i> This bit determines the security level for the address contained in <i>AddNode</i> . Locked against modification while an Add is in progress – writes have no effect.                                                                                                                                                                                           |

| 29   | locked    | <i>Locked Address Flag.</i> This bit determines the lock status for the address contained in <i>AddNode</i> . Any frames received from a locked source will be discarded. Locked against modification while an Add is in progress – writes will have no effect.                                                                                                                              |

| 28   | cuplnk    | <i>Copy Frames to Uplink Flag.</i> This bit determines the Copy Uplink status for the address contained in <i>AddNode</i> . Addresses tagged with this bit will add the port specified in the <i>UplinkPort</i> register to the routing code. Locked against modification wile an Add is in progress – writes have no effect.                                                                |

| 27   | new       | <i>New Address Flag.</i> This bit determines the new status for the address contained in <i>AddNode</i> . Having set <i>new</i> to 1, this address can be easily found by a <i>Find</i> command which has <i>new</i> in <i>FindControl</i> = 1. Locked against modification while an Add is in progress – writes have no effect.                                                             |

| 26:8 | reserved  | Reserved. Writes to these bits have no effect. They always read as zero.                                                                                                                                                                                                                                                                                                                     |

| 7:6  | reserved  | Reserved. Writes to these bits have no effect. They always read as zero.                                                                                                                                                                                                                                                                                                                     |

| 5:0  | xportcode | <i>Current Extended Port for Node.</i> This filed determines the destination port for the unicast address shown in <i>AddNode</i> . If a nonexistent port is specified, no address record will be entered when the add is performed. (The add will complete in the normal manner but no record will exist.) Locked against modification while an Add is in progress – writes have no effect. |

| Bit         | 15                    | 14                                   | 13     | 12      | 11     | 10     | 9   | 8  | 7  | 6  | 5      | 4      | 3       | 2  | 1  | 0  |                                   |

|-------------|-----------------------|--------------------------------------|--------|---------|--------|--------|-----|----|----|----|--------|--------|---------|----|----|----|-----------------------------------|

| Field Name  |                       | re                                   | eserve | d[15:10 | 0]     |        |     |    |    | р  | ortvec | tor[5: | 0]      |    |    |    | Byte                              |

| Reset value | 0                     | 0                                    | 0      | 0       | 0      | 0      | 0   | 0  | 0  | 0  | 0      | 0      | 0       | 0  | 0  | 0  | Address<br>Offset0                |

| Reset type  | I                     | I                                    | I      | I       | -      | -      | h   | h  | h  | h  | h      | h      | h       | h  | h  | h  | 0x0                               |

| Field type  | r                     | r                                    | r      | r       | r      | r      | rw  | rw | rw | rw | rw     | rw     | rw      | rw | rw | rw |                                   |

| Bit         | 31                    | 30                                   | 29     | 28      | 27     | 26     | 25  | 24 | 23 | 22 | 21     | 20     | 19      | 18 | 17 | 16 |                                   |

| Field Name  | n<br>b<br>I<br>c<br>k | r<br>e<br>s<br>e<br>r<br>v<br>e<br>d |        | Xro     | outeco | de[29: | 24] |    |    |    | R      | eserve | ed[23:1 | 6] |    |    | Byte<br>Address<br>Offset0<br>0x2 |

| Reset value | 0                     | 0                                    | 0      | 0       | 0      | 0      | 0   | 0  | 0  | 0  | 0      | 0      | 0       | 0  | 0  | 0  |                                   |

| Reset type  | h                     | h                                    | h      | h       | h      | h      | h   | h  | -  | -  | -      | -      | -       | -  | -  | -  |                                   |

| Field type  | rw                    | rw                                   | rw     | rw      | rw     | rw     | rw  | rw | r  | r  | r      | r      | r       | r  | r  | r  |                                   |

#### Figure 5. AddPort Register – Multicast Format

| Bit   | Name       | Function                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | nblck      | Not Blocked Flag. This bit sets the <b>RxMultiBlockPorts</b> override function.                                                                                                                                                                                                                                                                             |

|       |            | □ <i>Nblck</i> = 1, <i>RxMultiBlockPorts</i> will not be used to filter frames.                                                                                                                                                                                                                                                                             |

|       |            | <b>Nblck</b> = 0, frames will be forwarded only if the appropriate<br><b>RxMultiBlockPorts</b> bit for the source port is not set. Locked against modification while an Add is in progress – writes have no effect.                                                                                                                                         |

| 30    | reserved   | Reserved. Writes to these bits have no effect. They always read as zero.                                                                                                                                                                                                                                                                                    |

| 29:24 | xroutecode | <i>Extended Route Code for Multicast.</i> This field determines the route code used to generate the pre-frame tag added to frames routed to port 08 when <i>pretag</i> in <i>Port8Control</i> = 1. It is ignored if <i>pretag</i> or bit 8 of <i>portvector</i> is 0. Locked against modification while an Add is in progress – writes will have no effect. |

| 23:10 | reserved   | Reserved. Writes to these bits have no effect. They always read as zero.                                                                                                                                                                                                                                                                                    |

| 9:0   | portvector | <i>Port Bit Vector for Multicast.</i> This field determines the port bit vector for the multicast address contained in <i>AddNode</i> . The bit values in this field correspond one to one with the port assignment. Locked against modification while an Add is in progress – writes have no effect.                                                       |

When a frame with a learning format pre-tag is received on port 08, the internal address lookup engine (IALE) will learn/update the address, node, and VLAN if the frame is a unicast. When learning the address, the IALE takes the *xportvector* of the pre-tag and converts it to a *xportcode* (the xportcodes for crossbar matrix switch ports range from 0b100000 to 0b110000, where 0b100000 represents crossbar matrix port 0 and 0b110000 represents crossbar-matrix port 16).

The *xportcode*, along with the source address and the VLAN information, is added to the TNETX4090 address record table. The same information can be learned via the DIO interface.

The *xroutecode* of the *AddPort* register and the *XMultiGroup* registers allows the system to include crossbar-matrix ports in a multicast address. The following conditions must be met for a crossbar-matrix port to be included in the multicast:

- □ The *pretag* bit in the Port08Control register must be set to 1.

- Bit 8 (indicating port 08) of *portvector* in the *AddPort* register must be set to 1.

When the conditions above are met, the multicast frame will be forwarded to all ports on the TNETX4090 as specified by the *portvector* in the *AddPort* register. Furthermore, the multicast frame will also be forwarded to the crossbar-matrix port(s) as specified in the *xroutecode* in the *AddPort* register.

If the value of the *xroutecode* is in the range of 0b000000 to 0b010000 (where 0b000000 indicates crossbar-matrix port 0 and 0b010000 indicates crossbar-matrix port 16), the multicast frame will be forwarded only to the specified crossbar-matrix port. If the value of the xroutecode is in the range of 0b010001 to 0b111111 (where 0b010001 indicates *XMulitGroup17* register and 0b111111 indicates *XMulitGroup63* register), the multicast frame will be forwarded to the crossbar-matrix ports specified in the *XMultiGroup* register the *xroutecode* indexes.

| Bit         | 15               | 14                                                  | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5                                            | 4  | 3  | 2  | 1  | 0  | DIO    |

|-------------|------------------|-----------------------------------------------------|----|----|----|----|----|----|----|----|----------------------------------------------|----|----|----|----|----|--------|

| Field Name  | xportvector15:0] |                                                     |    |    |    |    |    |    |    |    | DIO<br>Address                               |    |    |    |    |    |        |

| Reset value | 1                | 1                                                   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1                                            | 1  | 1  | 1  | 1  | 1  | Offset |

| Reset type  | h                | h                                                   | h  | h  | h  | h  | h  | h  | h  | h  | h                                            | h  | h  | h  | h  | h  | +4★n   |

| Field type  | rw               | rw                                                  | rw | rw | rw | rw | rw | rw | rw | rw | rw                                           | rw | rw | rw | rw | rw |        |

| Bit         | 31               | 30                                                  | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21                                           | 20 | 19 | 18 | 17 | 16 |        |

| Field Name  |                  | x<br>p<br>o<br>r<br>t<br>v<br>e<br>c<br>t<br>o<br>r |    |    |    |    |    |    |    |    | DIO<br>Address<br>Offset<br>0x0500<br>+4 * n |    |    |    |    |    |        |

| Reset value | 0                | 0                                                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                                            | 0  | 0  | 0  | 0  | 1  |        |

| Reset type  | -                | I                                                   | I  | -  | 1  | -  | -  | -  | -  | I  | -                                            | _  | -  | -  | -  | h  |        |

| Field type  | r                | r                                                   | r  | r  | r  | r  | r  | r  | r  | r  | r                                            | r  | r  | r  | r  | rw |        |

#### Table 6. XMultiGroup17 - 63 Registers

| Bit   | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:17 | reserved    | Reserved. Writes to these bits have no effect. They always read a 0.                                                                                                                                                                                                                                                                                                                                                                                    |

| 16:0  | xportvector | <i>Extended Multicast Group Port Vector.</i> This field determines the extended port vector to be inserted into the pre-frame tag added to frames routed to port 08 when <i>pretag</i> in <i>Port8Control</i> =1. <i>XMultiGroupn</i> is associated with <i>xroutecode</i> = $n$ , where $n$ is in the range 17 – 63. If <i>xroutecode</i> is less than 17, it is interrupted as a unicast extended port vector, and only bit $n$ of the vector is set. |

The *xportvector* in the *XMultiGroupn* registers determine which crossbar-matrix ports must forward the multicast frame. The bit position in the *xportvector* indicates the crossbar-matrix port (for example, bit 0 set to one indicates the frame must be forwarded on the crossbar-matrix port 1, bit 1 set to one indicates crossbar-matrix port 1, and so on).

#### xroutecodes/xportcodes

Besides generating *xroutcodes* or *xportcodes* from the IALE performing a lookup on the destination address in the address record table, *xroutecodes* and *xportcodes* can be generated when utilizing the following features (refer to the *TNETX4090 Programmer's Reference Guide* for detailed information on the features listed below):

- Unknown VLAN If a multicast address is received with an unknown VLAN Identifier, the *xportcode* contained in the *UnkVLANPort* register will determine which port the frame is forwarded to. This feature is listed as UnkVLAN in Table 7.

- Unknown Source Address When a frame is received with an unknown source address, the frame will be forwarded to the port according to the *portvector* and *xroutecode* in the *UnkSrcPorts* register. This feature is listed as UnkSrc in Table 7.

- Unknown Unicast Address When a frame is received with an unknown unicast address, the frame will be forwarded to the port according to the *portvector* and *xroutecode* in the *UnkUniPorts* register. This feature is listed as UnkUni in Table 7.

- Unknown Multicast Address When a frame is received with an unknown multicast address, the frame will be forwarded to the port according to the *portvector* and *xroutecode* in the *UnkMultiPorts* register. This feature is listed as UnkMulti in Table 7.

- Destination Address Mirroring If a frame is received and the *cuplnk* bit is set for that destination address, the frame will be mirrored on the port specified in the *xportcode* of the *UplinkPort* register. This feature is listed as Cuplink (cuplink) in Table 7.

- Port Mirroring If the mirr bit is set to one in the SysControl register and a frame is sourced from or destined to the mirror port (that is, the mirror port is configured in the MirrorPort register), the frame will be mirrored on the port specified in the xportcode of the UplinkPort register. This feature is listed as Cuplink (mirror) in Table 7.

The *xroutecode* generated from address record lookup and the *xroutecode*/*xportcode* generated in the features listed above are not mutually exclusive. Table 7 depicts how the TNETX4090 resolves *xroutecode*/*xportcode* when a conflict occurs.

| UnkVLAN      | UnkSrc       | UnkUni       | UnkMulti     | Cuplink<br>(cuplink) | Cuplink<br>(mirror) | Lookup<br>Table | Select   |

|--------------|--------------|--------------|--------------|----------------------|---------------------|-----------------|----------|

| $\checkmark$ |              |              |              |                      | $\checkmark$        |                 | UnkVLAN  |