# System Considerations Using Three TNETE2008 OctalPHY Devices with the TNETX3270 ThunderSWITCH

Worldwide Broadband Access Group LAN Products

## Abstract

The Texas Instruments (TI<sup>™</sup>) TNETX3270 ThunderSWITCH<sup>™</sup> 24/3 is a high-speed Ethernet multiport switching device allowing network system designers to deliver switching products that satisfy corporate desktop environments. The TI TNETE2008 OctaIPHY is a physical-layer (PHY) interface device for up to eight 10BASE-T networks using a multiplexed medium-access controller interface compatible with the TNETX3270 or equivalent.

This application report describes a printed circuit board (PCB) layout using the TNETX3270 device and three TNETE2008 interface devices. The PCB layout reflects the special considerations required to create a stable operating environment and minimize radiated energy.

### Contents

| ntroduction                             | 2 |

|-----------------------------------------|---|

| Ground Plane Layout                     | 2 |

| Power Plane Layout                      |   |

| Signal Plane Layout                     |   |

| Analog Power Connections and Decoupling |   |

| Other Design Suggestions                |   |

### Figures

| Figure 1. | Recommended Ground Plane Layout          | .4 |

|-----------|------------------------------------------|----|

|           | Recommended VDD Plane Layout             |    |

| 0         | First Signal Layer for Four Layer Board  |    |

|           | Ground Layer for Four Layer Board        |    |

| Figure 5. | Power Layer for Four Layer Board         | .8 |

| Figure 6. | Second Signal Layer for Four Layer Board | .9 |

|           | Analog Power Connections1                |    |

| Figure 8. | Analog Power Decoupling1                 | 0  |

### Introduction

A PCB layout using the TNETX3270 device and three TNETE2008 devices requires special considerations to create a stable operating environment and minimal radiated energy.

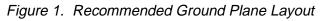

## **Ground Plane Layout**

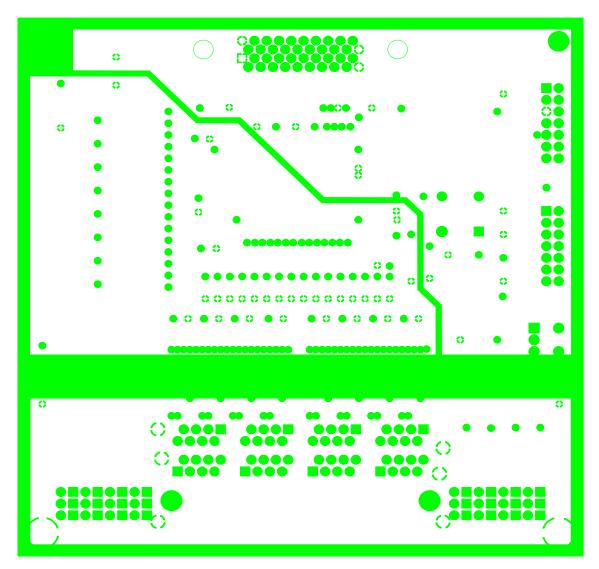

Figure 1 shows a recommended ground plane layout. Use the "20h rule" to isolate the physical layer devices from the circulating currents between the switching fabric and the adjacent physical layer sections. The "20h rule" says that adjacent buses should be separated by at least 20 times the distance from the routing layer to its reference plane. Do **NOT** place any splits or slots in the ground plane, except to separate the system and chassis ground areas.

The gap under the isolation transformers, the chassis ground split, is 0.4 inch. This spacing should be acceptable under most standard four-channel magnetic devices that have a package body width of approximately 0.48 inch. If a thinner device is used, scale the gap so that the body bridges the open space between the ground planes with little overlap to the planes.

### **Power Plane Layout**

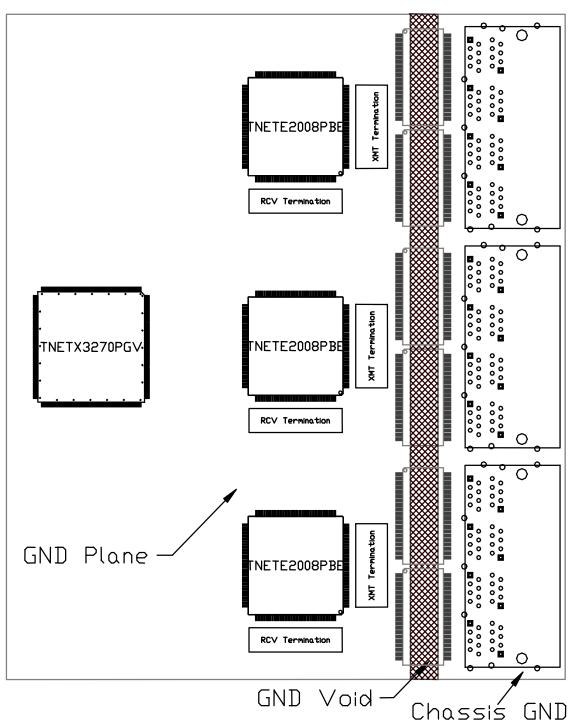

Figure 2 shows a recommended power plane layout that isolates the analog sections of the TNETE2008 devices.

These areas must be kept quiet because the receive and phase locked loop (PLL) circuit sections are referenced to this plane. Noise here can create jitter in the clock and receivers. The transmitters are also referenced here since they must have a clean power to prevent transmit distortion.

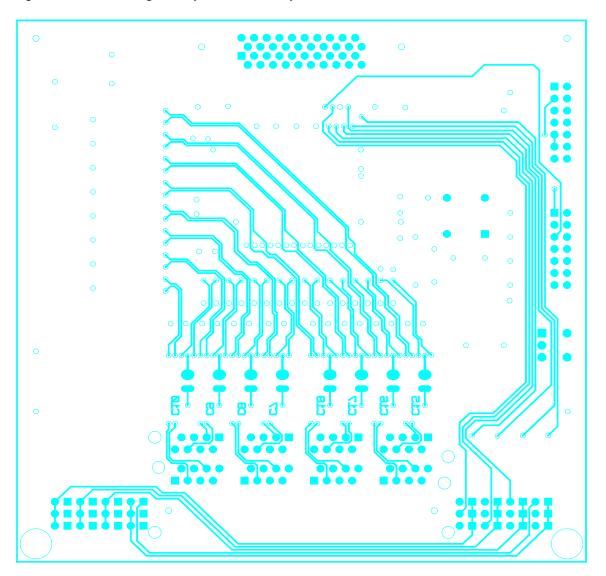

## **Signal Plane Layout**

The RXz+ and RXz- tracks should route from the TNETE2008 to the terminations and then on to the magnetics.

The TXz+ and TXz- track lengths between the TNETE2008 and the magnetics should be as short as possible to minimize radiation. At the same time, the pairs should be spread out to reduce cross talk as much as possible while maintaining the same length.

The layers of a four layer board should be stacked as follows:

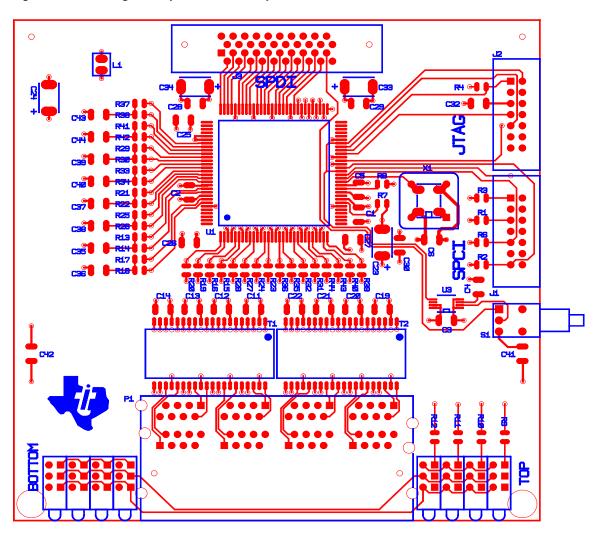

- 1) Signal layer (see Figure 3)

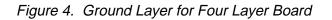

- 2) Ground layer (see Figure 4)

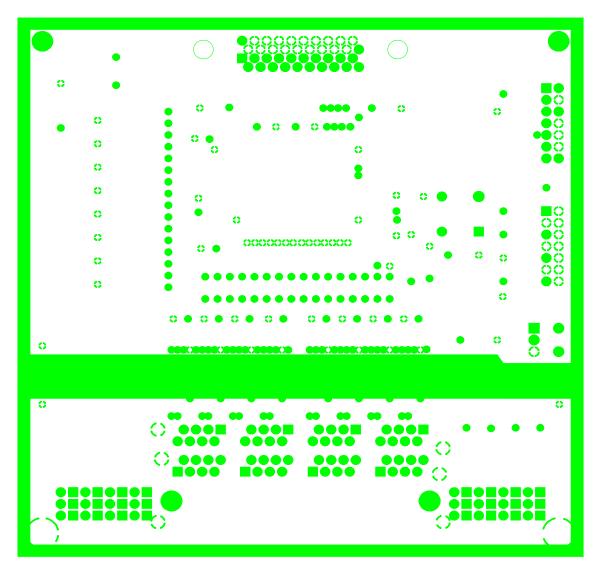

- 3) Power layer (see Figure 5)

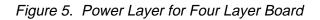

- 4) Signal layer (see Figure 6)

Figure 3 through Figure 6 show a layout developed by Texas Instruments for system compliance testing as well as EMC scans.

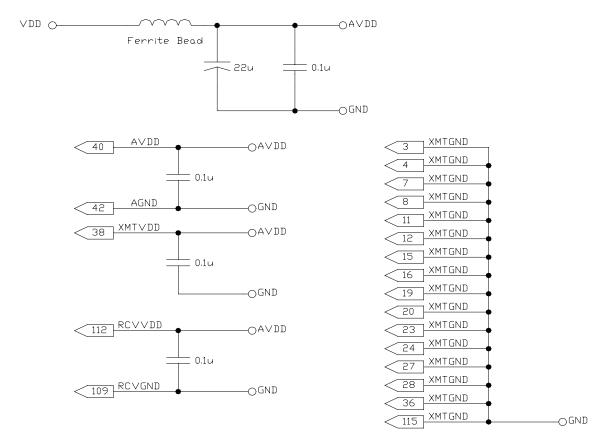

### **Analog Power Connections and Decoupling**

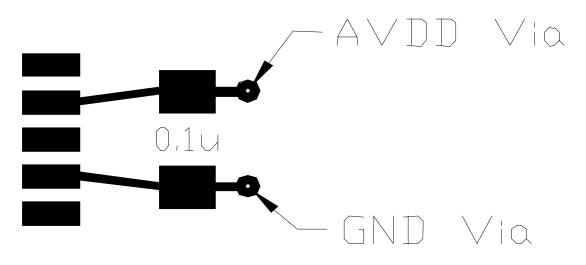

Figure 7 shows the decoupling components and the pins they are mounted near. To improve power supply noise decoupling, all decoupling capacitors should be connected near the related power supply pins and then the capacitors connected to the power planes with a short track.

Figure 8 shows a structure to place the pin decoupling on the individual pins in the analog VDD sections. Notice that the capacitor on XMTVDD, pin 38, is referenced to the GND plane and not to an individual component pin. It should also be noted that all XMTGND pins need an individual GND plane connection and should not have shared vias.

The trace should route from the pin pad to the capacitor and then on to the power plane. This places the capacitor in the path of any noise and will add a small amount of inductance in series with the power source. Both of these effects are desired.

The chassis ground section is included on each power plane and routed to the power input so that the chassis can be capacitively coupled to the system ground return during electromagnetic interference testing. This has been shown on some occasions to provide a path for noise to leave the cable interface without being radiated into the area of measured concern.

### **Other Design Suggestions**

- Use only 3.3V oscillators. Do not use a 5V oscillator with a output level shifter. 5V oscillators tend to radiate during EMC testing more than the lower drive clocks. Also, the level shifter is another source of noise.

- 2) Keep the 83MHz source close to the TNETX3270 with minimal trace lengths.

- 3) Prevent the clocks from changing layers.

- 4) Isolate the clock VDDs from the power plane with a ferrite bead. Include a bulk cap and small decoupler on the oscillator side of the bead.

- 5) Add group bulk decoupling in the SDRAM area of the PCB. This section is noisy and may radiate during EMC testing.

- 6) No signal should cross a gap in either the power or ground plane. A gap forces the return path to form a loop and radiated noise will result.

- 7) JTAG signals should not be routed parallel to any clock signal. The JTAG traces route to the entire PCB and any clock noise coupled onto the JTAG lines will be distributed across the board. If JTAG is not used, tie these lines to their default conditions. (i.e., JRST=0, JTMS=1, JTDI=1, JTCLK=1, JTDO=NC)

İF

Figure 3. First Signal Layer for Four Layer Board

TI OCTAL PHY EVM SILKSCREEN LAYER 1 TOP SIDE , tir

TI OCTAL PHY EVM

LAYER 2 GND PLANE

İĒ

TI OCTAL PHY EVM

LAYER 3 POWER PLANE

*ii*)

Figure 6. Second Signal Layer for Four Layer Board

TI OCTAL PHY EVM

LAYER 4 BACK SIDE

Ĭ

### Figure 7. Analog Power Connections

Figure 8. Analog Power Decoupling

#### INTERNET

#### www.ti.com

Register with TI&ME to build custom information pages and receive new product updates automatically via email.

#### TI Semiconductor Home Page http://www.ti.com/sc

TI Distributors http://www.ti.com/sc/docs/distmenu.htm

PRODUCT INFORMATION CENTERS

*US TMS320* Hotline (281) 274-2320 Fax (281) 274-2324 BBS (281) 274-2323 email dsph@ti.com

Americas Phone +1(972) 644-5580 Fax +1(972) 480-7800 Email sc-infomaster@ti.com

#### Europe, Middle East, and Africa

Phone Phone Deutsch +49-(0) 8161 80 3311 English +44-(0) 1604 66 3399 Francais +33-(0) 1-30 70 11 64 Italiano +33-(0) 1-30 70 11 67 Fax +33-(0) 1-30-70 10 32 Email epic@ti.com

### *Japan* Phone

International +81-3-3457-0972 Domestic +0120-81-0026 Fax

International +81-3-3457-1259 Domestic +0120-81-0036 Email pic-japan@ti.com

### *Asia* Phone

International +886-2-3786800 Domestic Australia 1-800-881-011

#### Asia (continued)

TI Number -800-800-1450 China 10811 China 10811 TI Number -800-800-1450 Hong Kong 800-96-1111 TI Number -800-800-1450 India 000-117 TI Number -800-800-1450 Indonesia 001-801-10 TI Number -800-800-1450 Corpo 0.06 E51 2004 Korea 080-551-2804 Malaysia 1-800-800-011 TI Number -800-800-1450 New Zealand +000-911 TI Number -800-800-1450 Philippines 105-11 TI Number -800-800-1450 Singapore 800-0111-111

TI Number -800-800-1450 Taiwan 080-006800

Thailand 0019-991-1111 TI Number -800-800-1450

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty, or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.