# TLK2201JR 1.0 Gb to 1.6 Gb ETHERNET TRANSCEIVER

SCAS652 - AUGUST 2000

- 1.0 to 1.6 Gigabits Per Second (Gbps) Serializer/Deserializer

- Chip Scale Footprint With 80-Pin 5 mm × 5 mm Land Grid Array (LGA) Package (MicroStarJR™)

- Low Power Consumption < 250 mW at 1.25 Gbps

- PECL Compatible Differential I/O on High-Speed Interface

- Single Monolithic PLL Design

- Support For 10 Bit Interface (TBI) or Reduced Interface 5-Bit Double Data Rate (DDR) Clocking

- Receiver Differential Input Thresholds 200 mV Minimum

- IEEE 802.3 (Gigabit Ethernet) Compliant

- Advanced 0.25 μm CMOS Technology

- Interfaces To Backplane, Copper Cables or Optical Modules

- No External Filter Capacitors Required

- Comprehensive Suite of Built-In Testability

- IEEE 1149.1 JTAG Support

- 2.5-V Supply for Lowest Power Operation

- 3.3-V Tolerant on TTL Inputs

- Hot Plug Protection

- ESD Protection 2 kV HBM

### description

The TLK2201JR is a member of the transceiver family of multigigabit transceivers, intended for use in ultrahigh-speed bidirectional point-to-point data transmission systems. The TLK2201JR gigabit ethernet transceiver is fully compliant with IEEE 802.3 requirements for serializer/deserializer functions at 1.25 Gbps. The TLK2201JR supports a wide range of serial data rates from 1.0 Gbps to 1.6 Gbps.

The primary application of this device is to provide building blocks for point-to-point baseband data transmission over controlled impedance media of 50  $\Omega$  or 75  $\Omega$ . The transmission media can be printed-circuit board traces, copper cables or fiber-optical media. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

|   | Α   | в          | С    | D    | Е          | F          | G   | н           | J          |   |

|---|-----|------------|------|------|------------|------------|-----|-------------|------------|---|

| 9 | RD1 | RD2        | RD3  | RD4  | RD5        | RD6        | RD7 | RD8         | RD9        | 9 |

| 8 | RD0 | VDD        | VDD  | JTMS | JTRST<br>N | JTDI       | VDD | VDD         | SYNC       | 8 |

| 7 | RXN | VDDA       | GNDA | GNDA | GND        | GND        | GND | RBC<br>MODE | RBC0       | 7 |

| 6 | RXP | VDDA       | GNDA | GNDA | GND        | GND        | GND | TEST<br>EN  | RBC1       | 6 |

| 5 | LOS | VDDA       | GNDA | GNDA | GNDA       | GND        | GND | JTCLK       | JTDO       | 5 |

| 4 | TXN | VDDA       | GND  | GND  | GND        | GND        | GND | PRBS<br>EN  | SYNC<br>EN | 4 |

| 3 | ТХР | VDD<br>PLL | Open | GND  | GND        | GND        | GND | MODE<br>SEL | REF<br>CLK | 3 |

| 2 | TD0 | VDD        | VDD  | VDD  | VDD        | EN<br>ABLE | VDD | VDD         | LOOP<br>EN | 2 |

| 1 | TD1 | TD2        | TD3  | TD4  | TD5        | TD6        | TD7 | TD8         | TD9        | 1 |

|   | Α   | В          | С    | D    | E          | F          | G   | Н           | J          |   |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MicroStarJr is a trademark of Texas Instruments.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

SCAS652 - AUGUST 2000

### description (continued)

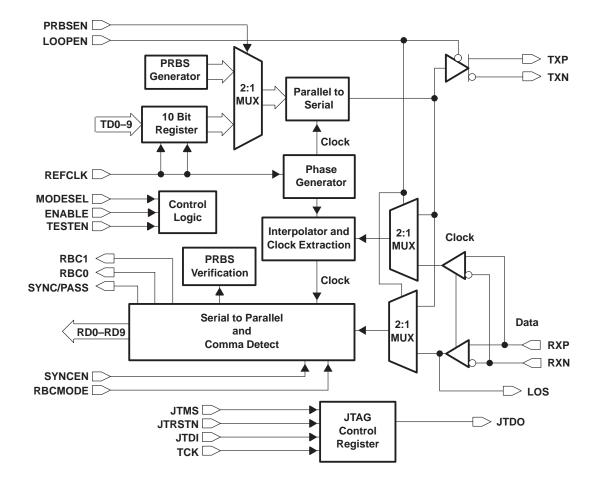

The TLK2201JR performs the data serialization, deserialization, and clock extraction functions for a physical layer interface device. The transceiver operates at 1.25 Gbps (typical), providing up to 1.0 Gbps of data bandwidth over a copper or optical media interface.

The TLK2201JR supports both the defined 10-bit interface (TBI) and a reduced 5-bit interface utilizing double data rate (DDR) clocking. In the TBI mode the serializer/deserializer (SERDES) accepts 10-bit wide 8-bit/10-bit (8b/10b) parallel encoded data bytes. The parallel data bytes are serialized and transmitted differentially at PECL compatible voltage levels. The SERDES extracts clock information from the input serial stream and deserializes the data, outputting a parallel 10-bit data byte.

In the DDR mode the parallel interface accepts 5-bit wide 8-bit/10-bit encoded data aligned to both the rising and falling edge of the reference clock. The data is clocked most significant bit first, (i.e., bits 0 - 4 of the 8-bit/10-bit encoded data) on the rising edge of the clock and the least significant bits (i.e., bits 5 - 9 of the 8-bit/10-bit encoded data) are clocked on the falling edge of the clock.

The transceiver automatically locks onto incoming data without the need to prelock.

The TLK2201JR provides a comprehensive series of built-in tests for self-test purposes including loopback and PRBS generation and verification. An IEEE 1149.1 JTAG port is also supported.

The TLK2201JR is housed in a high performance, thermally enhanced, 80-pin land grid array (LGA) MicroStarJr<sup>™</sup> package. Use of the MicroStarJr<sup>™</sup> package does not require any special considerations. All ac performance specifications in this data sheet are measured with the MicroStarJr<sup>™</sup> soldered to the test board.

The TLK2201JR is characterized for operation from 0°C to 70°C.

The TLK2201JR uses a 2.5 V supply. The I/O section is 3.3 V compatible. With the 2.5 V supply the chipset is very power efficient dissipating less than 250 mW typical power when operating at 1.25 Gbps.

The TLK2201JR is designed to be hot plug capable. A power-on reset holds RCB0 and RCB1 low and goes to high impedance to the parallel side output signal pins during power up as well as goes to TXP and TXN.

## differences between TLK2201JR and TNETE2201

The TLK2201JR is a functional equivalent of the TNETE2201B. There are several differences between the two devices as noted below.

- The V<sub>CC</sub> is 2.5 V for the TLK2201JR versus 3.3 V for TNETE2201.

- The PLL filter capacitors on pins 16, 17, 48, and 49 of the TNETE2201 are no longer required.

- No pulldown resistors are required on the TXP/TXN outputs.

### transceiver family

The TLK2201JR is a member of the transceiver family of CMOS multi-gigabit transceivers, intended for use in high-speed bidirectional point-to-point data transmission systems. Other members of the the transceiver family include:

- **TLK1501** A 0.6-Gbps to 1.5-Gbps transceiver with on chip 8-bit/10-bit ENDEC providing up to 1.28 Gbps of data bandwidth, packaged in a 64-pin VQFP PowerPAD<sup>™</sup> package.

- **TLK2500/TLK2501** A 1.6-Gbps to 2.5-Gbps transceiver with on chip 8-bit/10-bit ENDEC providing up to 2 Gbps of data bandwidth, packaged in a 64-pin VQFP PowerPAD<sup>™</sup> package.

- **TLK2701** A 2.5 Gbps to 2.7 Gbps transceiver with on-chip 8-bit/10-bit ENDEC, providing up to 2.16 Gbps of data bandwidth with k-character control, packaged in a 64-pin VQFP PowerPAD<sup>™</sup> package.

- TLK3101 A 2.5-Gbps to 3.125-Gbps transceiver with on-chip 8-bit/10-bit ENDEC, providing up to 2.5 Gbps of data bandwidth, packaged in a 64-pin VQFP PowerPAD<sup>™</sup> package.

- **TLK3104SC** A 3-Gbps to 3.125-Gbps quad transceiver with on chip 8-bit/10-bit ENDEC, a 16-bit low voltage differential signaling (LVDS) parallel interface, packaged in 289 pin PBGA.

- TLK3104SA A 3-Gbps to 3.125-Gbps quad transceiver with on chip 8-bit/10-bit ENDEC, an IEEE 802.3ae defined XGMII parallel interface with SSTL\_2 I/O, packaged in 289 pin PBGA.

### functional block diagram

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated