# Low voltage Modem Platform based on TMS320LC56

Literature Number: BPRA049 Texas Instruments Europe March 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

#### **Contents**

|                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G/MIPS analysis                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                |

| esign                                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                |

| em Overview                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                |

| ections to the Parallel Port                            | 5                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.1 Memory Interface / Timing verification            | 7                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.2 Host Interface (UART)                             | 11                                                                                                                                                                                                                                                                                                                                                                                               |

| ecting the Analog Interface to the Buffered Serial Port |                                                                                                                                                                                                                                                                                                                                                                                                  |

| ble System Clock                                        | 13                                                                                                                                                                                                                                                                                                                                                                                               |

| mpatibility with TMS320LC541/3/6                        | 14                                                                                                                                                                                                                                                                                                                                                                                               |

| itialization & Test                                     | 15                                                                                                                                                                                                                                                                                                                                                                                               |

| munication between DSP and PC via RS232                 | 15                                                                                                                                                                                                                                                                                                                                                                                               |

| red Serial Port and TLC320AC01                          | 16                                                                                                                                                                                                                                                                                                                                                                                               |

| ng the external SRAM                                    | 17                                                                                                                                                                                                                                                                                                                                                                                               |

| Source Code                                             | 19                                                                                                                                                                                                                                                                                                                                                                                               |

| PAL Programming                                         | 35                                                                                                                                                                                                                                                                                                                                                                                               |

| Schematics                                              | 39                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                         | G/MIPS analysis esign em Overview ections to the Parallel Port. 3.2.1 Memory Interface / Timing verification 3.2.2 Host Interface (UART) ecting the Analog Interface to the Buffered Serial Port ble System Clock mpatibility with TMS320LC541/3/6 itialization & Test munication between DSP and PC via RS232 red Serial Port and TLC320AC01 ng the external SRAM  Source Code  PAL Programming |

## **List of Figures**

| 1 | igure 1: System Overview   | 4 |

|---|----------------------------|---|

| 2 | igure 2: System Memory Map | 6 |

### **List of Tables**

| 1 | Table 1: Status of memory select signals | 5   |

|---|------------------------------------------|-----|

|   | Table 2: Variable frequency for CLKIN.   |     |

| 3 | Table 3: TMS320LC56 clock options.       | .13 |

## Low voltage Modem Platform based on TMS320LC56

#### **ABSTRACT**

This application report presents a modem reference design based on the TMS320LC56 DSP. The advanced peripherals of this device provide the features necessary for integration into complex systems optimizing access times and minimizing external logic. A software analysis at the beginning shows that the computing power of the LC56 is sufficient to support even the highest standards of voice and data transmission. The 3.3V technology of this DSP also makes it possible to integrate this solution in systems such as portable computers where low power consumption is the prime consideration. The combination of 5V with 3.3V devices is also discussed in this report. Onboard line interface, UART, large memory and expansion connectors bring a high degree of flexibility to this design, building a generic evaluation platform.

#### 1. Introduction

This application report discusses a modem reference design based on the TMS320LC56 DSP from Texas Instruments. A software analysis in the beginning will show that the TMS320LC56 has sufficient computing power to support even the highest standards of voice and data transmissions.

The flexible memory and I/O interfaces provide the features necessary to integrate the TMS320LC56 into complex systems with fast access times and minimum external control logic.

The 3.3V technology of the DSP allows power consumption to be minimized, making this solution appropriate for portable computers where power consumption is a prime consideration. Combining 5V and 3.3V devices will also be discussed in this report.

#### 2. DATA/PROG/MIPS analysis

The modem industry is moving away from fixed chip-set designs to a more flexible and future-proof solution based on programmable DSP technology. The benefits of DSP technology are summarized below:

#### Reduced Cost

A single TMS320C5X can replace a 2- or 3-chipset solution, reducing board size, chip count and component interfacing. Easy upgrades can be achieved by loading revised code into an external EPROM without the need to design and replace expensive components.

#### Differentiated Product

The programmability of the DSP enables system designers to blend standard algorithms such as Data pumps with their own in-house algorithms which will differentiate their product from others in the market.

Next, the memory and processing power requirements for a complete V.34+ solution based on the C5X family is presented. An interpolation to the C54X family can be obtained assuming 25% increased efficiency with respect to the C5X figures given in the study.

## MEMORY/MIPS REQUIREMENT FOR COMPLETE V.34 SOLUTION (Based on C5X family)

|       |                           | <b>Program</b> | <u>Data</u>       | <u>Mips</u>                        |                |

|-------|---------------------------|----------------|-------------------|------------------------------------|----------------|

| FAX   |                           |                |                   |                                    |                |

|       | V.21                      | 0.5Kw          | 0.1Kw             | 2.0                                |                |

|       | V.27ter                   | 2.0Kw          | 0.4Kw             | 4.0                                |                |

|       | V.29                      | 2.5Kw          | 0.5Kw             | 4.0                                |                |

|       | V.17                      | 5.0Kw          | 0.8Kw             | 6.0                                |                |

| MODE  | ΞM                        |                |                   |                                    |                |

|       | V.23                      | 0.6Kw          | 0.1Kw             | 4.5                                |                |

|       | V.22/V.22bis              | 2.7Kw          | 0.3Kw             | 4.0                                |                |

|       | V.32/V.32bis              | 8.0Kw          | 6.0Kw             | 14.5                               |                |

|       | V.34                      | 12.0Kw         | 10.0Kw            | 30.0                               |                |

|       | PRESSION/<br>OR DETECTION | 0.014          | 00.014            |                                    |                |

|       | V.42 / V.42bis            | 6.0Kw          | 32.0Kw            | 6.0                                |                |

| AT CO | OMMANDS                   |                |                   |                                    |                |

|       | Basic Comm.<br>+ Parser   | 5.5Kw          | 4.0Kw             | (AT commands a the call set-up, th |                |

|       | Extended AT               | 5.8Kw          | 0.5Kw             | impact on MIPS f                   | igure)         |

| DSVD  |                           |                |                   | ·                                  |                |

|       | G.729A                    | 9.0Kw          | 2.0Kw             | 12.0                               |                |

|       | G.MUX                     | 4.0Kw          | 1.0Kw             | 3.0                                |                |

| TOTA  | L PROG                    | 63.6Kw         | (Store in FLASH   | HEPROM or partial                  | lly masked on  |

|       |                           |                | DSP ROM. Son      | ne extra memory sh                 | nould be added |

|       |                           |                | for Interrupt ser | vice routines, etc.)               |                |

#### **WORST CASE SCENARIO**

|                      | <u>Program</u> | <u>Data</u> | <u>Mips</u> |

|----------------------|----------------|-------------|-------------|

| V.34 + V.42+ V.42bis | 31Kw           | 45Kw        | 51          |

| + DSVD+ GMUX         |                |             |             |

#### 3. Hardware design

#### 3.1 System Overview

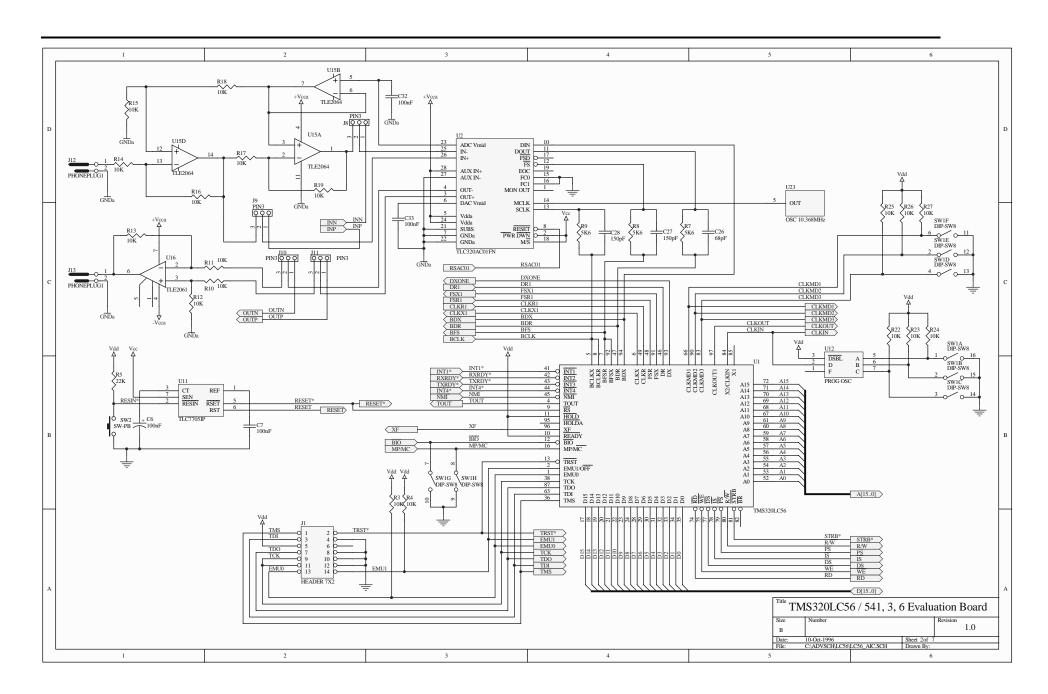

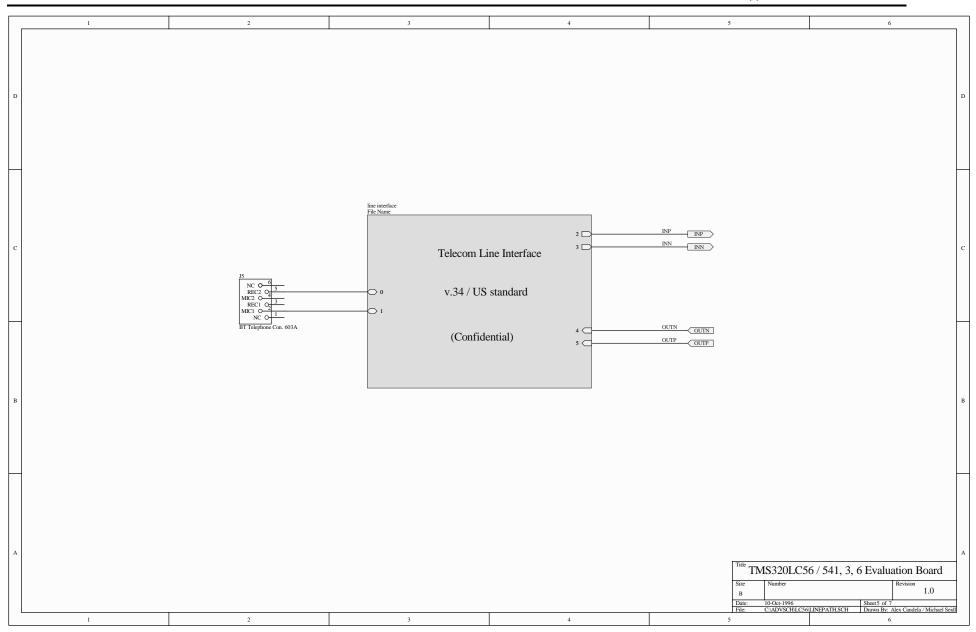

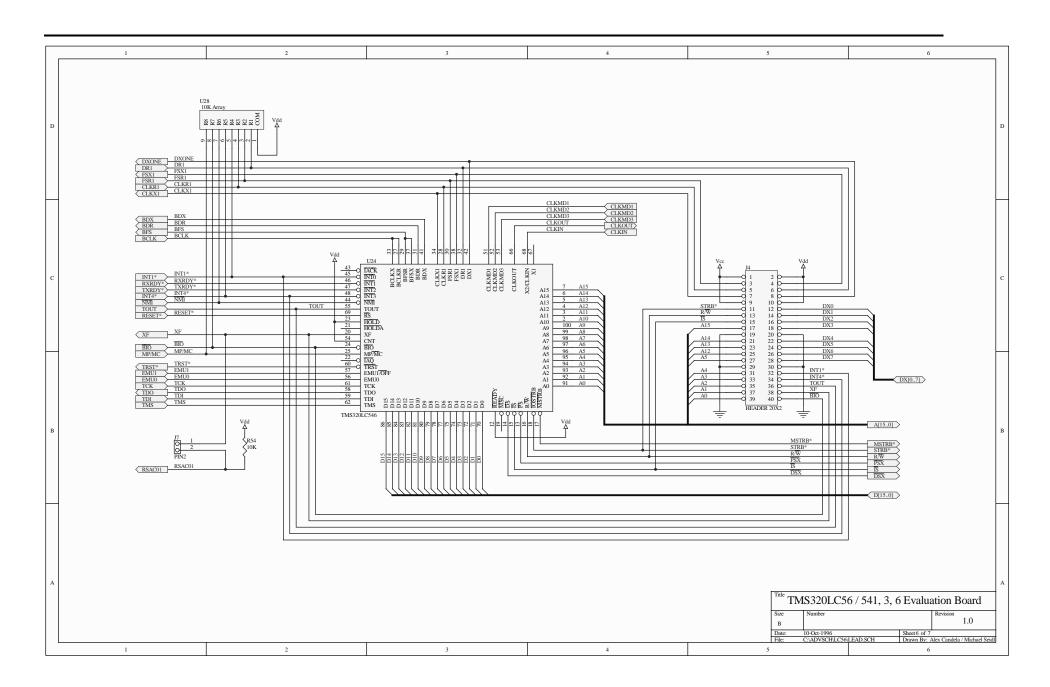

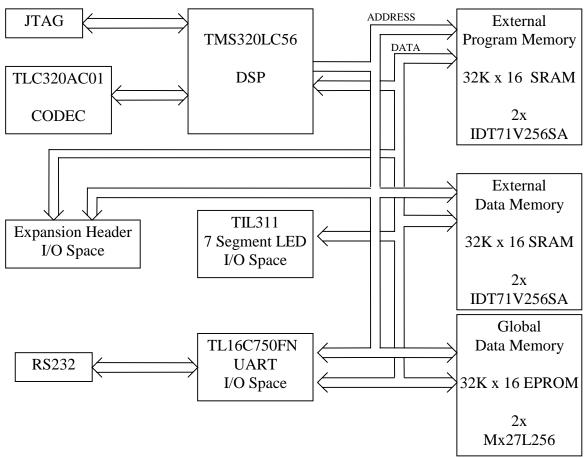

The system contains the components necessary for a modem. Data transfers and signal processing will be handled only by the DSP. The TLC320AC01 provides the A/D and D/A converters for the receive and transmit channels. Its analog input and output are connected to a telephone line interface which fulfills the US standard, enabling tests in a real environment.

The JTAG port provides direct access to the DSP and optimizes test and emulation capabilities of the system. In addition, a seven segment LED display makes it possible to monitor the status of the DSP. It may be used for debug and demonstration purposes.

The UART TL16C750 enables the system to communicate with a host via an RS232 interface.

The large size of external memory provides a very flexible development environment.

An expansion connector gives the opportunity for additional peripherals.

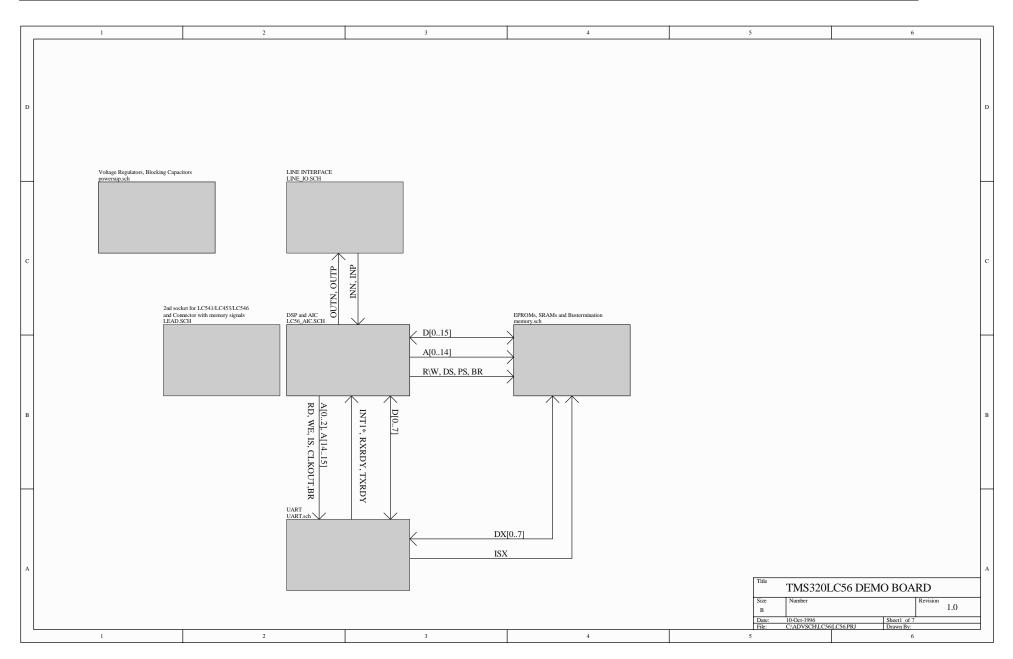

Figure 1 shows the components of the system and the required connections of the bus signals.

Figure 1: System Overview.

#### 3.2 Connections to the Parallel Port

The total space accessible from the DSP by the parallel port is divided into 'Program', 'Data', 'Global Data' and 'I/O'. With each access to external devices, the 'LC56 selects one of these spaces by driving the appropriate memory select strobes (PS\, DS\, IS\ and BR\) low:

| Enabled Space | PS\  | DS\  | IS\  | BR\  |

|---------------|------|------|------|------|

| Program       | Low  | High | High | High |

| Data          | High | Low  | High | High |

| Global Data   | High | Low  | High | Low  |

| I/O           | High | High | Low  | High |

Table 1: Status of memory select signals.

The address and data lines are shared by all external spaces.

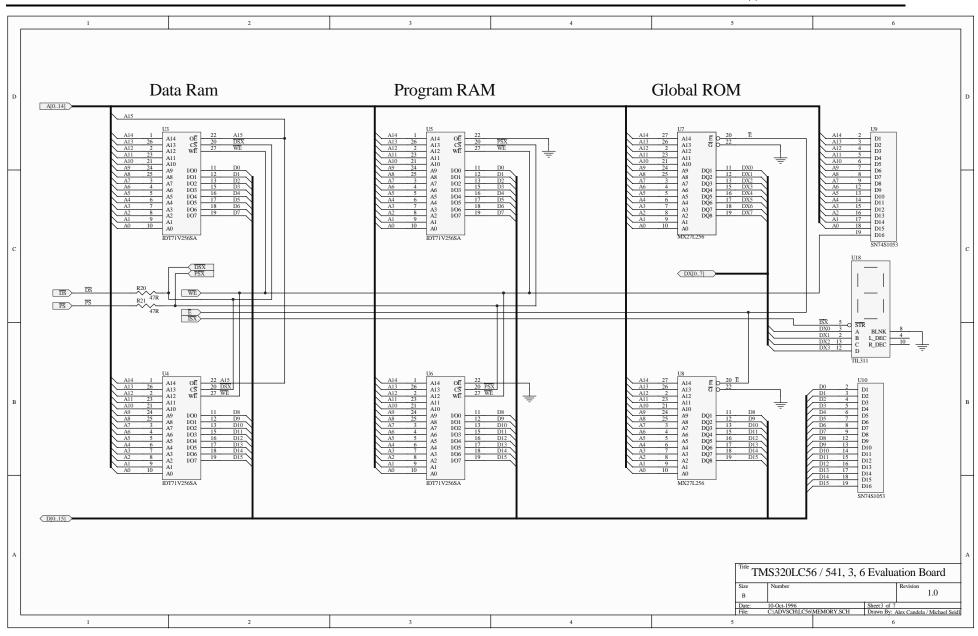

The two SRAM devices U5 and U6 (compare schematics) are the only memory devices in program space. The connection of PS\ to the CS\ inputs of the SRAMs is therefore sufficient to avoid any bus conflicts.

The EPROMs U7 and U8 must be placed in the global data memory for the boot load function stored in the on-chip ROM of the 'LC56. BR\ is connected to the chip enable of the EPROMs.

Because DS\ also goes low during global memory accesses it is not possible to use DS\ alone as chip enable for the SRAMs providing the external Data memory (U3 and U4).Bus conflicts would occur during each access to the EPROM.

One solution for avoiding this would be to generate the chip enable signal for the SRAMs with additional logic from BR\ and DS\. However, the additional delay is not acceptable when accessing the SRAMs with zero wait states in a 40MHz system.

To avoid any logic in the chip enable path it is better to use A15 as output enable of the SRAMs in addition to the connection of DS\ as chip select. Now the SRAM outputs are only enabled during accesses to the lower half (addresses 0x0000 - 0x7FFF) of the data space. EPROM is mapped in the global data space (addresses 0x8000 - 0xFFFF).

[User's Guide TMS320C5x, p. 6-40]

The I/O space will be shared by the 7 segment LED display, U18, and the UART communication element, U20. As both devices are not time critical it is possible to insert external logic to generate the chip enable signals as needed. To lengthen the memory cycles for these slower devices, software wait states have to be implemented for all accesses to the I/O space.

With all devices connected to the data bus, the capacitive loading is too high. The output drivers of the SRAMs are specified for external loads of only 30pF. The implementation of a buffer between the DSP and the slow devices like the UART, LED and the EPROM reduces the loading seen by the SRAMs.

|                                                          | Program                               | Data                                                | Global Data    | I/O            |

|----------------------------------------------------------|---------------------------------------|-----------------------------------------------------|----------------|----------------|

| 0x0000<br>0x005F<br>0x0060<br>0x007F<br>0x0080<br>0x00FF |                                       | Memory- mapped Registers On-Chip DARAM B2 Reserved  |                |                |

| 0x0100                                                   |                                       | On-Chip DARAM<br>B0 (CNF=0)<br>Reserved (CNF=1)     |                |                |

| 0x02FF<br>0x0300<br>0x04FF<br>0x0500                     |                                       | On-Chip DARAM<br>B1<br>Reserved                     |                |                |

| 0x07FF                                                   |                                       | Reserved                                            |                |                |

| 0x0800                                                   | External SRAM<br>U5 and U6<br>MP/MC=1 | On-Chip SARAM Blk0 BSP Block (OVLY=1) External SRAM |                | LED            |

| 0x0FFF                                                   |                                       | U3 and U4                                           |                |                |

| 0x1000                                                   | On Chin DOM                           | (OVLY=0)                                            |                |                |

| OXIOOO                                                   | On-Chip ROM<br>MP/MC=0                | On-Chip SARAM<br>Blk1                               |                |                |

|                                                          |                                       | BSP Block                                           |                |                |

|                                                          |                                       | (OVLY=1)                                            |                |                |

| 01788                                                    |                                       | External SRAM                                       |                |                |

| 0x17FF                                                   |                                       | U3 and U4<br>(OVLY=0)                               |                |                |

| 0x1800                                                   |                                       | On-Chip SARAM                                       |                |                |

|                                                          |                                       | Blk2                                                |                |                |

|                                                          |                                       | BSP Block                                           |                |                |

|                                                          |                                       | (OVLY=1)<br>External SRAM                           |                |                |

| 0x1FFF                                                   |                                       | U3 and U4                                           |                |                |

|                                                          |                                       | (OVLY=0)                                            |                |                |

| 0x2000                                                   |                                       |                                                     |                |                |

| 0x3FFF<br>0x4000                                         |                                       | External SRAM                                       |                | Г              |

| 0x4000<br>0x7FFF                                         |                                       | U3 and U4                                           |                | Free           |

| 0x8000                                                   | On-Chip SARAM                         |                                                     |                |                |

|                                                          | Blk0                                  | Shadow external                                     | External EPROM | UART           |

| 0xBFFF                                                   | (RAM=1)<br>Shadow of external         | Data SRAM<br>U3 and U4                              | U7 and U8      |                |

| 0xC000                                                   | SRAM U5 and U6                        | (Write only)                                        |                |                |

| 0x97FF                                                   | (RAM=0)                               | (write only)                                        |                |                |

| 0x9800                                                   | Shadow of external                    |                                                     |                | External EPROM |

| 0xFDFF                                                   | SRAM U5 and U6                        |                                                     | ļ              | U7 and U8      |

| 0xFE00                                                   | On-Chip DARAM                         |                                                     |                |                |

|                                                          | B0 (CNF=1)<br>Shadow of external      |                                                     |                |                |

| 0                                                        | SRAM U5 and U6                        |                                                     |                |                |

| 0xFFFF                                                   | (CNF=0)                               |                                                     |                |                |

Figure 2: System Memory Map.

#### 3.2.1 Memory Interface / Timing verification

#### a) SRAM

Read Cycle:

The SRAM devices used in this application are specified with an access time  $t_A = 15$ ns from address valid and CS\ low to data valid.

The 'LC56 starts any memory access cycle with the output of the valid addresses. At the same time the appropriate memory select strobe (DS\, PS\, BR\ or IS\) is driven low. After the time  $t_a(RDAV)$  the data must be valid on the bus.

For address and chip select the following equation must be fulfilled:

$$t_A = t_A(RDAV)$$

(1)

In our case, with a 15ns SRAM, a TMS320LC56-80 and Clock frequency of 40MHz we have:

$(\checkmark = equation fulfilled)$

Before the DSP can latch the data with the rising edge of RD\ the bus has to be kept valid for the setup time  $t_{su}(RD-RDH)$ . As RD\ is not connected to the SRAMs the timing is evaluated from the output of the valid address:

$$t_{su}(RD-RDH)$$

$< t_{wmin}(RDH) + t_{wmin}(RDL) - t_{A};$  (2)

7ns  $< H - 2ns + H - 2ns - 15ns;$

7ns  $< 6ns$

In our case, equation (2) is not possible to fulfill. This worst case cannot occur as  $t_{w}(RDH)$  and  $t_{w}(RDL)$  are linked together. This means that when one of them has its minimum value the other one is usually longer for that time. The sum of the two will be much closer to 2H than 2H - 4ns as calculated from equation (2) which ensures the setup time requirement,  $t_{w}(RD-RDH)$ , is met.

After the DSP has latched the data with the rising edge of RD\, the bus will possibly no longer have kept valid  $(t_h(RDH-RD) = 0ns)$ .

Write Cycle:

The falling edge on the WE\ input of the SRAM latches the addresses. The rising edge writes the data to the selected memory location.

The following equations must be fulfilled:

Address and CS\ valid before falling edge of WE\:

$$t_{AS}$$

$t_{SU}(AV-WEL)$  (3)

Ons 8.5ns

Minimum pulse duration WE\ low:

$$t_{WP} \quad t_{w}(WEL)$$

(4)

As OE\ of the SRAM is connected to ground permanently, the pulse duration of WE\ low must include the switching time of the SRAM's output drivers to high Z after the falling edge of WE\ and the setup time for the valid data before WE\ goes high again.

$$t_{WP} \quad t_{WHZ} + t_{DW}; \tag{5}$$

The combination of (4) and (5) gives the following:

$$t_{WHZ} + t_{DW} \quad t_{w}(WEL)$$

(6)

$$9ns + 7ns \quad 21ns \qquad \checkmark$$

Before the rising edge of WE\ the data must be valid for the time t<sub>DW</sub>:

$$t_{DW} \quad t_{su}(WDV-WEH)$$

(7)

7ns 11ns

After the rising edge of WE\ the data has to be kept valid on the bus for the time t<sub>DH</sub>:

$$t_{DH}$$

$t_h$  (WEH-WDV) (8)

Ons 8.5ns

Before the write cycle can be completed with the rising edge of WE\ the addresses and the CE\ input have to be valid for the time  $t_{AW}$ :

$$t_{AW}$$

$t_{su}(AV-WEL) + t_{wmin}(WEL);$  (9)

10ns 8.5ns + 21ns

#### b) EPROM

The EPROM devices used in this application are specified with an access time  $t_A = 150$ ns from address valid and CS\ low to data valid.

The 'LC56 starts any memory access cycle with the output of the valid addresses. At the same time the appropriate memory select strobe (DS\, PS\, BR\ or IS\) is driven low. After the time  $t_a$ (RDAV) the data must be valid on the bus. The enable signal for the buffer (U22), driving the lower 8 bits of the data bus, is generated by a PAL device from IS\, DS\ and A15 using only one macro cell of the programmable device. During boot load 7 s/w wait states are added to each access to the global data memory. It can be assumed the buffer is enabled sufficiently before the EPROM to guarantee the output of valid data. Therefore, it is not necessary to take the buffer enable signal into account for timing verification.

For address and chip select the following equation must be fulfilled:

$$t_A = t_a(RDAV) + 7T - t_{PHXmax}(245);$$

(10)

150ns 15ns + 175ns - 4.1ns

Before the DSP can latch the data with the rising edge of RD\ the bus has to be kept valid for the setup time  $t_{su}(RD-RDH)$ . As RD\ is not connected to the EPROMs, the timing is evaluated from the output of the valid address:

$$t_{su}(RD-RDH)$$

$< t_{wmin}(RDH) + t_{wmin}(RDL) + 7T - t_{A} - t_{PHXmax}(245);$  (11)

7ns  $< H - 2ns + H - 2ns + 175ns - 150ns - 4.1ns$

7ns  $< 41.9ns;$

To make the system compatible with the TMS320LC54x DSP the chip enable for the EPROM is created by a PAL using IS\, A15 and DS\. The additional delay for this gate causes no problems as the timing evaluations (10) and (11) are fulfilled with more than 35ns of tolerance.

#### Note:

The EPROM used in this application has an output disable time of 50ns. This may cause problems if an EPROM read cycle is immediately followed by a zero wait state access to another external device.

The use of the on-chip boot loader guarantees enough cycles between consecutive external accesses.

#### Definitions of names used in the equations above:

t<sub>a</sub>(RDAV) Access time, LC56 reads data from address valid

t<sub>su</sub>(RD-RDH) Setup time, data must be valid before RD high (LC56)

t<sub>h</sub>(RDH-RD) minimum hold time, data must be valid after RD high (LC56)

$t_{wmin}(RDH)$  minimum pulse duration of RD high (LC56)  $t_{wmin}(RDL)$  minimum pulse duration of RD low (LC56)

t<sub>su</sub>(WDV-WEH) setup time, LC56 outputs valid data before WE high

t<sub>su</sub>(AV-WEL) setup time, LC56 outputs valid addresses before WE low

t<sub>wmin</sub>(WEL) minimum pulse duration of WE low (LC56)

t<sub>b</sub>(WEH-WDV) minimum hold time, LC56 keeps data valid after WE high

t<sub>A</sub> Memory access time, data output valid after control signals valid

t<sub>wp</sub> minimum pulse duration WE low required by SRAM

t<sub>whz</sub> SRAM's maximum delay time, output in high Z after WE low

t<sub>DW</sub> SRAM minimum setup time, data valid before WE high SRAM minimum hold time, data valid after WE high

t<sub>AS</sub> SRAM minimum setup time, address and CE valid before WE low SRAM minimum setup time, address and CE valid before WE high

t<sub>PHXmax</sub>(245) Buffer maximum delay time, input to output valid

T System clock cycle time

H Half system clock cycle time T/2

#### 3.2.2 Host Interface (UART)

For the interface of the TL16C750 a compromise has been made. To keep the interface logic compatible with the TMS320LC54x DSPs and to avoid additional buffers in the address bus not all timing requirements of the specification for this device are met. Specifically, the read and write recovery times are not totally fulfilled. Therefore it may be necessary to implement 'NOP' cycles after any accesses to the UART in the software.

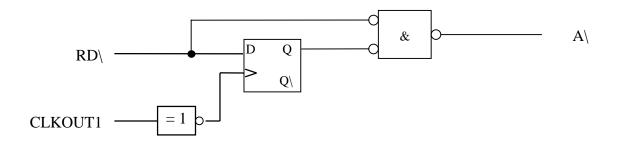

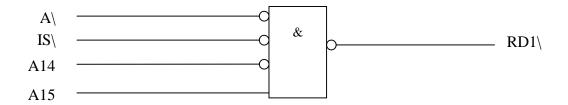

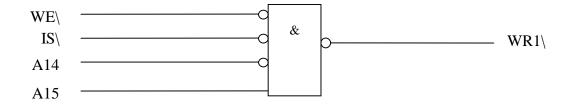

The following logic shifts the falling edge of RD\ for one clock cycle. This will ensure that the setup time for the addresses and CS\ is met. The NAND with RD\ ensures that the strobe goes high early enough to switch the output drivers in high impedance in time. This protects a subsequent access to another device from a bus conflict.

In addition the signal A\ has to be combined with the appropriate memory select signals to ensure that the output drivers are enabled only for accesses to the UART.

The two NAND gates in this logic can be merged and programmed as only one gate in the PAL.

It is not necessary to delay the falling edge of WE\. It is just combined with the memory select signals:

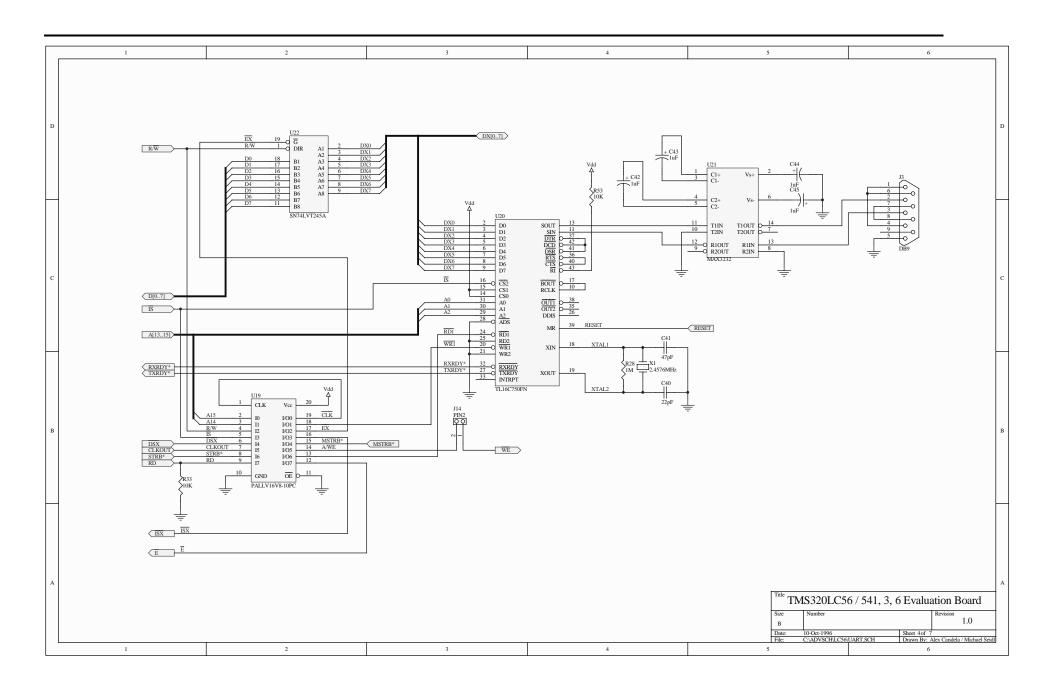

#### 3.3 Connecting the Analog Interface to the Buffered Serial Port

The TLC320AC01 provides the analog-to-digital and digital-to-analog conversion for the DSP. With the help of the headers J8 to J11 it is possible to switch the analog path between the line interface with connector J5 for modem applications and the phone connectors J12 (IN) and J13 (OUT) for other general purpose applications.

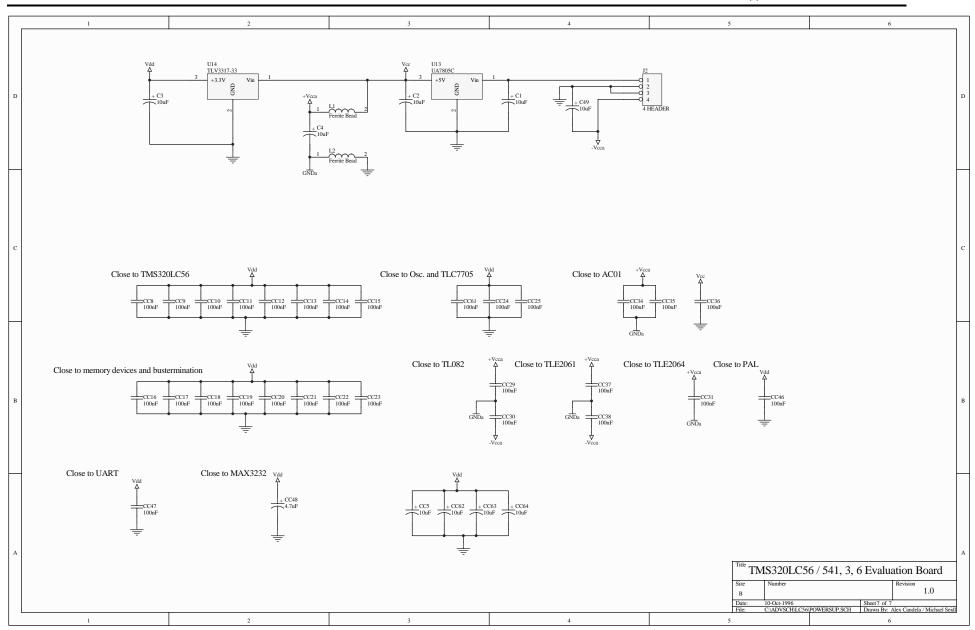

The TLC320AC01 derives the sampling frequency and the bandwidth of its internal low pass filter from the master clock. To enable a sampling rate of exactly 8kHz and the typical filter specification for telecom applications it is necessary to provide 10.368 MHz as MCLK frequency.

The low voltage DSP and the 'AC01 are connected to different power supplies. This may cause problems if one device drives the inputs of the other before it is connected to its power supply.

The connection of the voltage regulators, U13 and U14, in a chain prevents the AC01 from receiving any input signal from the DSP before its power supply voltage is applied.

Therefore it is only necessary to protect the DSP inputs from the 5V output voltage level of the AC01. A 5.6 k $\Omega$  series resistor (R7, R8, R9) limits the current into the DSP input to 1mA. An additional capacitor (C26, C27, C28) in parallel with this resistor maintains the rise and fall times. (for details refer to TLC320AC01 Application report, p.18, SLAAE09)

#### 3.4 Variable System Clock

The clock of the DSP is generated by a programmable oscillator. The inputs A, B and C vary its output frequency on pin #2 as shown in table 2. Pin #1 always outputs the specified frequency of the device.

Table 2: Variable frequency for CLKIN.

| Inputs |     |     |       | Outputs     |        |  |

|--------|-----|-----|-------|-------------|--------|--|

| С      | В   | Α   |       | D           | F      |  |

| SW3    | SW2 | SW1 |       | pin #2      | pin #1 |  |

| L      | L   | L   | F/2   | 10MHz       | 20MHz  |  |

| L      | L   | Η   | F/4   | (5MHz)      | 20MHz  |  |

| L      | Н   |     | F/8   | 2.5MHz      | 20MHz  |  |

| L      | Н   | Ι   | F/16  | (1.25MHz)   | 20MHz  |  |

| Н      | L   | L   | F/32  | 625kHz      | 20MHz  |  |

| Н      | L   | Η   | F/64  | (312.5kHz)  | 20MHz  |  |

| Н      | Н   | L   | F/128 | 156.25kHz   | 20MHz  |  |

| Н      | Н   | Н   | F/256 | (78.125kHz) | 20MHz  |  |

The pins DIV1 and DIV2 of the DSP specify the factor between the frequency on CLKIN and the DSP clock.

Table 3: TMS320LC56 clock options.

| Parameter                                   | CLKMD1<br>SW6 | CLKMD2<br>SW5 | CLKMD3<br>SW4 |

|---------------------------------------------|---------------|---------------|---------------|

| PLL multiply by three                       | L             | L             | L             |

| PLL multiply by five                        | Н             | Ш             | L             |

| PLL multiply by four                        | L             | Н             | L             |

| PLL multiply by nine                        | Н             | Н             | L             |

| External divide-by-two, oscillator disabled | L             | L             | Н             |

| PLL multiply by one                         | Н             | L             | Н             |

| PLL multiply by two                         | L             | Н             | Н             |

| Ext./Int. divide-by-two, oscillator enabled | Н             | Н             | Н             |

#### 4. Enabling compatibility with TMS320LC541/3/6

To be able to use the same design with a member of the TMS320LC54x family a second ZIF socket for a DSP has been added to the PCB. As both devices are connected in parallel to the bus it must be ensured that there is only one DSP inserted at a time.

As the parallel ports of the two processor types are slightly different, a couple of changes to the control logic are necessary.

The TMS320LC56's control outputs WE\ and RD\ of the parallel port do not exist on the TMS320LC54x devices. They have to be created by external logic for the UART and the SRAMs if the 'LC54x is used.

The TMS320LC56's STRB\ signal is split into the MSTRB and the IOSTRB strobes at the 'LC54x. MSTRB is only for accesses to the program and data space activated; IOSTRB only for accesses to the I/O space. The combination of R/W and MSTRB generates the WE\ strobe for writes to the SRAM banks. The RD1\ and WE1\ UART strobes are generated with IOSTRB, R/W\, and A[14:15] performing bank select.

To switch the board from 'LC56 to either 'LC541, 'LC543 or 'LC546 the PAL device, U19, has to be programmed with the file lead.jed instead of lc56.jed.

A jumper on J14 connects the WE\ output of the PAL to the SRAMs. This connection is only allowed if a DSP of the 'LC54x family is used. It must be removed for the 'LC56.

The 'LC56 must be placed into the socket U1, all 'LC54x devices into socket U24.

The boot loader of the LC54x reads the initialization word from the address 0xffff in the I/O space, while the boot load process itself accesses the EPROM in the data memory. Therefore the logic generating the enable signal for the EPROM must be combined in addition to DS\ and A15 with the IS\ strobe.

#### 5. Software: Initialization & Test

The following chapter describes the programs for initialization and test routines written during the development of the board. The source code is contained in the appendix to this report.

#### 5.1 Communication between DSP and PC via RS232

The Windows '*Terminal*' software enables the DSP to use the keyboard and monitor of a PC as input and display interface directly. The board transfers its data to the PC via the RS232 interface driven by the UART communication element, U20.

The data exchange between DSP and the communication element is controlled by the interrupts RXREADY and TXREADY driven by the UART. They are connected to the DSP as INT2 and INT3.

TXREADY signals to the processor that the previous byte has been sent to the PC and it is then possible to write the next byte to its transmit buffer. RXREADY tells the DSP a new byte has been received from the PC and is ready for reading.

To avoid any loss of data, the DSP must read a new byte from the UART receive channel before the PC sends the next byte. Therefore RXREADY is connected to an interrupt with a higher priority than TXREADY.

The software described in the following is based on the communication between PC and DSP via the UART.

The user can choose a routine to run from the menu. By pressing any key, the routine activated will end and the DSP will return to the main program, giving the user a new choice.

#### 5.2 Buffered Serial Port and TLC320AC01

The analog interface TLC320AC01 is connected to the DSP via the buffered serial port. It consists of two independent channels for transmitting and receiving. Each channel has its own memory space or buffer. From the buffer, the transmit channel will read data to be sent. After each read the transmit buffer address pointer AXR will be incremented. The size of the transmit buffer is specified in the register BKX. The port will generate the XINT interrupt each time one half of the buffer has been transmitted.

If AXR has reached the end of the buffer it will be reset to the start address.

The receive channel is similarly organized. ARR contains the actual receive buffer address and BKR the length. The RINT interrupt is generated each time one half of the buffer has been loaded with new data.

The DSP can access the buffers as memory mapped into the On-Chip SARAM Blk0 starting at address 0x0800 in the data space.

The subroutine \_ac01of the program will reset the 'AC01 via the XF pin and initializes the control registers of the analog interface. The DSP will then loop back the incoming samples to the output channel of the AC01.

The AC01 has primary communication for the data exchange from the A/D and D/A converters, and secondary communication to set its control registers. Secondary communication is activated if the two LSBs of a data word written to the DAC during primary communication are set high.

The initialization words used by the software are pre-loaded into the transmit buffer, and are sent interleaved with dummy data to activate secondary communication.

After initialization, it must be ensured that only data words are transmitted to the AC01 with bits 0 and 1 set to zero, unless secondary communication is requested to change the setup of the analog interface. The program then starts to receive samples and store them in the transmit buffer before any samples are sent to the AC01.

After the DSP has detected both interrupts, transmit and receive, it will shift the new data in the receive buffer into the inactive half of the transmit buffer.

It will continue this loop-back process until the user presses a key and an interrupt from the UART signals the process to stop.

#### 5.3 Testing the external SRAM

If this memory test is selected, the DSP will start to write and read data to the memory space defined in the configuration file as 'testmem' and 'testprg'. Each stored value will be checked for errors and any faults will increment the error counter 'ERR'. The program will stay in this mode until the user presses any key - at which point, the memory test will stop and the actual value of ERR will be displayed.

At the start of the routine the contents of the memory locations in the data space specified by 'testmem' will be set to zero. The contents of the data space will then be copied to the program memory specified by 'testprg'.

After that, the DSP reads a location in the program space, checks if the value is correct and stores a new value (0x5555) in this cell. If the value read is different from the value expected, the counter ERR is incremented. The same task is performed in data space. This procedure is repeated for the whole length of the memory defined by 'RANGE' by incrementing the address pointers by 1 after each store instruction.

The same test is repeated with 0xaaaa, 0xffff and 0x0000 as the new values are written to the external memory locations.

The consecutive values are chosen to maximize the number of data bits changed with each access.

The test is executed 16 times for each of the four values. The LED indicates the current number of iterations performed (0 to 16).

The program then starts a different test.

The DSP executes 8 consecutive writes to the external data space. The data written alternates between 0x5555 and 0xaaaa with each cycle. After this, the DSP reads out this data and stores the sum of the eight values in the accumulator to check it. If the result is not correct, ERR is incremented. This procedure is repeated for the following blocks of eight words until the DSP reaches the end of the external memory space, defined by RANGE.

After this, the program executes the same routine with 0x0000 and 0xffff as the values to be written.

Finally the DSP restarts the whole memory test without resetting ERR until the program detects an interrupt from the UART, signaling that a key has been pressed by the user.

#### References

- 1. Designing with the TLC320AC01 Analog Interface for DSPs, John Walliker and Julian Daley, Texas Instruments 1994, SLAAE09

- 2. TLC320AC01 Analog Interface circuit, Texas Instruments 1993, SLAS057A

- 3. TMS320C5x, TMS320LC5x data sheet, Texas Instruments 1995, SPRS030A

- 4. TMS320C5x User's Guide, Texas Instruments 1993, SPRU56C

- 5. Power Supply Circuits, Texas Instruments 1996, SLVD002

- 6. Low-Voltage Logic, Texas Instruments 1994, SCVDE03

- 7. TMS320C54x User's Guide, Texas Instruments 1995, SPRU131A

- 8. TMS320C54x Data Sheet, Texas Instruments 1996, SPRS039

- 9. TMS320C54x Serial Ports User's Guide, Texas Instruments 1995, SPRU156

- 10. Digital Design Workshop, E. Haseloff and P. Forstner, Texas Instruments 1995

#### **Appendix A Source Code**

```

FILE NAME: MAIN.C

PROGRAM UART COMMUNICATION WITH TMS320LC56

#define clean_up receive_data(); break /* cleanup macro

#define maxstring 40

#include "main1.c"

/* flag names, constants

extern void memory();

extern void ac01();

extern int ERR;

/* error counter of memtest */

int DIMR = 6;

void main(void)

#define max 100

char C, COMMAND;

char s[max];

int i,n;

int DONE = 0;

asm(" splk  #1000100010111000b, PMST ");

asm(" splk  #01C0h, PDWSR");  /* reset waitstates, 7 FOR IO

asm(" LMMR IMR, #_DIMR");

asm(" splk #0ffffh,IFR");

/* clear all pending int

asm(" CLRC INTM");

/* disable interrupts

/*load value for line cntrl reg,enable DLAB

port8003 = 135;

||||++---- word length = 8bit

+----- number of stop bits = 2

+----- parity bit = no

+---- even parity select = odd

----- stick parity bit = disabled

----- break control bit = disabled

+---- divisor latch bit = enabled

port8003 = 7; /* disable DLAB bit

C = '\n'; /* load C with a character

port8000 = C;/* send this character to UART to activate a

/* transmit interrupt

C = port8000;/* read received word from the UART to claer it

/* reset cursor

sendinteger(0xa);

sendstring(" *** LC56 test platform ***",27);

sendinteger(0xa); /* reset cursor sendinteger(0xa); /* line feed sendinteger(0xd); /* reset cursor sendinteger(0xd); /* line feed

sendinteger(0xa);

sendinteger(0xd);

/* reset cursor

/* line feed

(m)",21);

sendstring("Memorytest

sendinteger(0xa); /* reset cursor sendinteger(0xd); /* line feed

sendstring("AC01 in Loop Back (a)",21);

/* line feed

(s)",21);

/* reset cursor

/* line feed

sendinteger(0xd);

sendstring("Stop

sendinteger(0xa);

sendinteger(0xd);

```

```

/* stay in following loop while DONE = 0

* /

while(!DONE)

COMMAND = receivechar();

/* load COMMAND with character received f. UART*/

/* write character received on the monitor

* /

sendchar(COMMAND);

sendinteger(0xa);

/* reset cursor

/* line feed

sendinteger(0xd);

* /

switch (COMMAND)

/* execute the command...

{

case 'M': case 'm': memory();

/* run function memory

/* print error counter

printresult(ERR);

sendinteger(0xa);

/* reset cursor

/* line feed

sendinteger(0xd);

sendstring("New choice? (m,a or s)",22);

break;

/* return from 'switch'

case 'a': case 'A': sendstring("ac01 in loop back mode",22);

sendstring("press any key to stop",21);

sendinteger(0xa); /* reset cursor

/* line feed

sendinteger(0xd);

/* run function ac01

ac01();

sendstring("New choice? (m,a or s)",22);

break;

/* return from 'switch'

case 'S': case 's': sendstring("program completed",17);

sendinteger(0xa);

/* reset cursor

/* line feed

/* set DONE to 1

sendinteger(0xd);

DONE = 1;

/* return from 'switch'

break;

```

```

FILE NAME: main1.C

LC56 UART COMMUNICATION FUNCTIONS

clear_messages() receive_data() send_data() send_file_data()

initialize_evm() receive_command() send_command() receive_file_data()

printresult()

/**********************

#include <string.h>

/*#include "evml.h"

/* flag names, constants

#include <ioports.h>

/* indicator for UART receive intrpt

/* indicator for UART transmit intrpt

extern int RXREADY; extern int TXREADY;

unsigned char reply;

/* UART transmit & receive buffer

/* UART Line Control Register

ioport char port8000;

ioport int port8003; ioport int port8100;

/* UART Divisor lower byte

/* UART Divisor upper byte

ioport int port8101;

void sendstring(char s[], int lim)

int c,i;

i = 0;

/* send lim characeters of string s

while(--lim >= 0)

sendchar(s[i++]);

void sendchar(char c)

/* wait for txready interrupt

while(!TXREADY);

port8000 = c;

/* write char to UART's TX register

/* Clear ready to transmit bit

TXREADY = 0;

char receivechar()

RXREADY = 0;

reply = port8000;

/* read char from UART's RX register

/* wait for txready interrupt

while(!RXREADY);

/* read char from UART's RX register

reply = port8000;

RXREADY = 0;

/* Clear ready to receive bit

/* return the received value

return(reply);

void sendinteger(int i)

while(!TXREADY);

/* wait for txready interrupt

/* write char to UART's TX register

port8100 = i;

TXREADY = 0;

/* Clear ready to transmit bit

```

```

void itoa(int n,char s[])

/* transform the integer value n into

/* the ASCII string s

int i, sign;

if ((sign = n) < 0)

n = -n;

i = 0;

do {

\dot{s}[i++] = n % 10 + '0';

while ((n /= 10) > 0);

if (sign < 0)

s[i++] = '-';

s[i] = '\0';

reverse(s);

void reverse(char s[])

/* reverses the string e.g. 'abc' -> 'cba' */

int c, i, j;

for (i = 0, j = strlen(s)-1; i < j; i++, j--)

\dot{c} = s[i];

s[i] = s[j];

s[j] = c;

}

void printresult(int E)

int n, i;

long L;

char s[10];

sendstring("Memorytest identified ",22);

L = E;

n = ltoa(L,s);

/* send this string

for(i=0;i<n;i++)

sendchar(s[i]);

sendstring(" errors",7);

* /

/* line feed

sendinteger(0xa);

```

```

Texas Instruments 1td. 1996

Function test of external memory and buffered seial port

TMS320LC56

TLC320AC01

.title "MEMORY AND AC01 TEST"

.version 50

.mmregs

.def _memory

.def

_ac01

.global

RXREADY

.global

.global _TXREADY

.ref

_c_int0

.set 30h

BDRR

BXDR

.set 31h

.set 32h

BSPC

BSPCE

.set 33h

.set 34h

AXR

BKX

.set 35h

ARR

.set 36h

.set 37h

BKR

RANGE

.set 5fffh

XSIZE

.set 4

; tx buffersize = 4 = rxbuffersize

HSIZE

.set 2

; half buffer size

; This part initializes the LC56 processor and buffered serial port.

; then initializes the ACO1 and starts the main signal

; processing loop. In this example, a data sample \bar{i}s read from

; the adc and written back to the dac unchanged.

XTOP

.sect "txbuff"

; request secondary comms

.word 11b

.word 0000000101000101b

; reg1 36-> 8kHz @10.368MhZ

; 35-> 7.937kHz @10Mhz

.word 11b

; request secondary comms

0000001000010010b

; reg2 = B register

.word

----- data = 18

----- address = 2

----- write =0

++---- phase shif

reg 3 = A' stays as default

reg 4

.word 11b

; request secondary comms

.word 0000010000011001b

---- output 0=sq 1=0dB 2=-6dB 3=-12dB

----- intput 0=sq 1=0dB 2=-6dB 3=-12dB

---- monitor 0=sq 1=0dB 2=-6dB 3=-12dB

---- not used

----- address = 4

----- write = 0

----- phase shift

```

```

reg 5

.word

11b

; request secondary comms

.word 0000010100000101b

----- 0=loopback 1 =norm 2 =aux 3 = both

----- 0=hp on, 1=hp off

+---- 0=echo on , 1=echo off

---- not used

----- address = 5

+---- write = 0

----- phase shift

reg6 = digital configuration

reg7 = frame synch delay

reg8 = frame sync number

.word 9,10,11,12,13,14,15,16

RTOP

.sect "rxbuff"

.word 10h,20h,30h,40h,50h,60h,70h,80h

.word 90h,0a0h,0b0h,0c0h,0d0h,0e0h,0f0h,100h

.data

; Clock Values; Clock Values

CLOCK: .word 0,1,2,3,4

.word 5,6,7,8,9

.word 10,11,12,13,14,15

.usect "test_d", RANGE

testmem

tstprg .usect "test_p",RANGE

gotxflag

.usect "b2",1; used to signal int from serial

; output port

.usect "b2",1; used to signal int from serial % \left( 1\right) =\left( 1\right) \left( 1\right)

gotrflag

; input port

TEMP1

.usect "b2",1; used store buffaddr

TEMP

.usect "b2",1

.usect "b2",1

ADDR

.usect "b2",1

_ERR

_RXREADY

.usect "b2",1

.usect "b2",1

TXREADY

; Macro definitions

; The following macro waits for an interrupt from the serial

; port before it continous with program execution

waitxint

.macro

waitxint?

; load flag into acc

lacc

gotxflag

waitxint?

; wait for int

bz

splk

#0,gotxflag ; reset the flag

.endm

waitrint

.macro

waitrint?

lacc

gotrflag

; load flag into acc

waitrint?

; wait for int

bz

splk

#0,gotrflag ; reset the flag

.endm

.sect "vectors"

_c_int0

rs

int1

b

int.1

int2

b

; UART receive interrupt

rxr

; UART transmit interrupt

int3

b

txr

tint

b

tint

rint

b

rint

xint

b

xint

brint b

getrdata

; bufferred serial port receive interrupt

bxint b

getxdata

; bufferred serial port transmit interrupt

int4

b

int4

rsvd14 b

rsvd14

rsvd16

rsvd16 b

rsvd18

rsvd18 b

rsvd1A b

rsvd1A

```

```

rsvd1C b

rsvd1C

rsvd1E b

rsvd1E

rsvd20

rsvd20 b

trap b

trap

nmi

b

nmi

rsvd26 b

rsvd26

rsvd28 b

rsvd28

.text

.include "ac01.asm"

.include "memory.asm"

; interrupt handlers

getxdata:

splk

#1,gotxflag

; set flag

rete

; return form interrupt restoring

getrdata:

splk

#1,gotrflag

; set flag

; return form interrupt restoring

rete

rxr:

LACC

; set RXREADY if

_RXREADY

SAMM

; int2 occurs

RETE

LACC

txr:

#1

; set TXREADY if

_TXREADY

SAMM

; int3 occurs

RETE

.end

```

```

*************************

TMS320CL56

function memory test

include file of mem.asm

****************************

.text

; start of main program

_ac01:

POPD

*+

; save stack pointer

AR0,*+

SAR

; to be compatible with

AR1,*

; routines written in C

SAR

LARK

AR0,1

LAR

AR0,*0+

ldp

#0

; set dp to first page

setc

INTM

; disable interrupts

setc

SXM

; set sign ext mode

; set Overflow mode

setc

OVM

; The code below does the following: disables visibility of address

; bus, on chip single access ram is mapped into prog space, sets the IPTR

; to point to 8000h and selects MICROPROCESSOR mode

clrc

xf

#1000100010111000b, PMST

splk

; B0 mapped in data space

clrc

; Set the interrupt mask to respond to buffered serial interrupt

splk

#0c6h,IMR

; only respond to buffered serial rx & tx int and

; uart

#08h,BSPC

splk

; reset and configure BSPC

splk

#0b400h,BSPCE

; configure BSPCE, buf for tx/rx enabled

; 16bits ext frame & clk

#XTOP, AXR

#RTOP, ARR

; load startaddress of buffer in AXR

; load startaddress of buffer in ARR

splk

#16, BKX ; load startaddress of buffer in ARR ; load buf size in BKX (only for initialisation) #XSIZE, BKR ; load buf size in BKR #0c0h, IFR

splk

splk

splk

splk

#0c0h, IFR

; clear any pending interupt

setc

хf

; release codec

rpt

#20

nop

; Reset the codec and release it again to make it ignore first garbage

; word generated by serial port

clrc

; reset codec

rpt

#20

; wait for 20 cycles

nop

setc

xf

; release codec

#048h, BSPC

splk

; start SPI transmit part

CLRC

INTM

; enable interrupts

; Serial interface and AC01 are now in stable state

; set up AC01

; wait for xint, ac01 has received initialization

waitxint

XTOP, AXR

; reset tx buffer address

splk

splk

#088h, BSPC

; start SPI receive part

; enable full size of tx buffer

splk

#XSIZE, BKX

waitrint

; wait for rint

after half buffer is full

; reset rx buffer address

RTOP, ARR

splk

AR4, #0

AR3, #HSIZE

; Loop counter for debugging

LAR

LOOP

LAR

; load loop counter with 'half buffersize' - 1

*,AR3

MAR

#RTOP, TEMP1

splk

LACL

TEMP1

; load address of lower half of receive buffer

BSPCE,1

BIT

; check RH flag in BSPCE register

BCND

LRBP, NTC

; branch if RH = 0

ADD

#HSIZE

; add half buffer size if RH = 1

LRBP

SACL

TEMP1

AR5, TEMP1

LAR

; load receive buffer pointer

splk

#XTOP, TEMP1

LACL

TEMP1

; load address of lower half of transmit buffer

BIT

BSPCE, 4

; check XH flag in BSPCE register

BCND

LXBP, NTC

; branch if XH = 0

#HSIZE

ADD

; add half buffer size if RH = 1

LXBP

TEMP1

SACL

```

```

AR2, TEMP1

LAR

; load transmit buffer pointer

MAR

*-,AR5

; substract 1 from loop counter AR3

*+, AR2

*+, AR3

SHIFT,*-,AR5

SHIFT LACL

; activate tx buffer pointer

; store 1st rsample as 1st txsample ; repeat 'half buffer size' times

SACL

{\tt BANZ}

NOP

NOP

#0b400h, BSPCE

; reload SPCE and set BXE again

splk

splk

#0c8h, BSPC

; start SPI rx and tx part

waitxint

; wait for last samples transmited

; wait for new samples received

waitrint

LACC

ARR

LACC

AXR

LACC

LACC

{\tt BKX}

MAR

*, AR4

; increment loop counter for

MAR

*+, AR5

; debugging

LACC

_RXREADY

; check if interrupt from the UART

BCND

LOOP,EQ

; occured. If not stay in the loop

NOP

nop

LARP

AR1

; reload stack pointer

SBRK

2

LAR

AR0,*-

PSHD

RET

```

```

TMS320CL56

function memory test

include file of mem.asm

_memory:

; save stack pointer

; to be compatible with

; routines written in C

POPD

*+

AR0,*+

SAR

AR1,*

SAR

LARK

AR0,1

LAR

AR0,*0+

ldp

#0

spĺk

#0, greg

#1000100010111000b, PMST

splk

splk

#111000000b, PDWSR ; set software wait states

;

CLRC

INTM

; enable intetrrupts

*,AR3

MAR

; activate AR3

CLRC

CNF

; map on-chip RAM into data space

; reset the ; Error counter

LACL

#0

SACL

_ERR

; preload counter values ; in data space locations

AR3, #CLOCK

LAR

SACL

*+

LACL

#1

SACL

*+

#2

LACL

SACL

#3

LACL

SACL

LACL

#4

SACL

*+

LACL

#5

*+

SACL

#6

LACL

*+

SACL

LACL

#7

SACL

LACL

#8

SACL

LACL

#9

SACL

#10

LACL

SACL

*+

LACL

#11

SACL

LACL

#12

SACL

LACL

#13

SACL

LACL

#14

SACL

#15

LACL

SACL

ldp

#0

; set dp to first page

CLRC

SXM

; suppress sign extension

AR6, #testmem ; load start address of

*, AR6 ; data memory to test

START LAR

*, AR6

#RANGE

MAR

; load 0 in all memory

RPTZ

SACL *+

; locations within RANGE

; reset also program space ; while copy data to program

AR6,#testmem

LAR

LACC

#tstprg

RPT

#RANGE

TBLW

```

```

MAR

*,AR3

; ARP points to AR3

AR3, #CLOCK

LAR

; Load AR3 with start value

LAR

AR2,#15

; AR2 is the loop counter

LAR

AR5,#0

LOOPM:

OUT

*+,0001h

; Output value of AR3

LACC

#0h

LAR

AR6, #testmem

; load start address of

MAR

*,AR6

; data memory to test

LAR

AR7, #RANGE

; load counter with the length

; of memory to test

LACC

; store the start address or

#tstprg

SACL

; program memory to test in ADDR

ADDR

OTOA: LACC

ADDR

; read first program memory

TEMP

TBLR

; location

LACC

#0h

XOR

; check if value is correct

TEMP

BCND

ERR_P1,NEQ

; if not correct then ERR_P1

NOP

NOP

P1:

LACC

#0AAAAh

; load new value to store in

SACL

TEMP

; program memory location

LACC

ADDR

; store this value in prog

TBLW

TEMP

ADD

#1

; increment ADDR

SACL

ADDR

LACC

#0h

XOR

; read data memory location

; and check value

BCND

ERR_D1,NEQ

; if not correct ERR_P1

NOP

NOP

D1:

LACC

#0AAAAh

; store new value in

SACL

*+,AR7

; data memory location

BANZ

OTOA, *-, AR6

; stay in loop if loop counter

; AR7 is not 0. Post decrement AR7

NOP

NOP

LACC

#tstprg

; same as OTOA but change values

LAR

AR7, #RANGE

; from A to 5

AR6, #testmem

LAR

SACL

ADDR

ATO5:

LACC

ADDR

TBLR

TEMP

LACC

#0AAAAh

XOR

TEMP

BCND

ERR_P2,NEQ

NOP

NOP

P2:

LACC

#5555h

SACL

TEMP

LACC

ADDR

TBLW

TEMP

ADD

#1

SACL

ADDR

LACC

#0Ah

XOR

BCND

ERR_D2, NEQ

NOP

NOP

D2:

LACC

#5555h

SACL

*+,AR7

BANZ

ATO5,*-,AR6

NOP

NOP

```

```

AR6, #testmem

; same as OTOA but change values

LAR

LACC

#tstprg

; from 5 to F

AR7, #RANGE

LAR

SACL

ADDR

f5TOF: LACC

ADDR

\mathtt{TBLR}

TEMP

LACC

#5555h

XOR

TEMP

BCND

ERR_P3,NEQ

NOP

NOP

P3:

LACC

#0FFFFh

SACL

TEMP

LACC

ADDR

TBLW

TEMP

ADD

#1

SACL

ADDR

LACC

#5555h

XOR

BCND

ERR_D3,NEQ

NOP

NOP

D3:

LACC

#0FFFFh

SACL

*+,AR7

BANZ

f5TOF, *-, AR6

NOP

NOP

LAR

AR6, #testmem

; same as OTOA but change values

#tstprg

LACC

; from F to 0

AR7, #RANGE

LAR

SACL

ADDR

FTOO:

LACC

ADDR

TBLR

TEMP

LACC

#0FFFFh

XOR

TEMP

BCND

ERR_P4,NEQ

NOP

NOP

P4:

LACC

#0h

SACL

TEMP

LACC

ADDR

TBLW

TEMP

ADD

#1

ADDR

SACL

LACC

#0FFFFh

XOR

BCND

ERR_D4, NEQ

NOP

NOP

D4:

LACC

#0h

*+,AR7

SACL

BANZ

FT00, *-, AR6

NOP

NOP

MAR

*,AR2

LOOPM, *-, AR3

BANZ

; Branch to start of loop

;Start this part after 16 times LOOPM

; The following test will generate consecutive writes and reads

; to the external memory

#RANGE, 13

LACC

; load range divided by 8 in AR3

SACH

TEMP

LAR

AR3, TEMP

LAR

AR4, #testmem

; load start address of datamem

MAR

*,AR4

; to test in AR4

CONS1: LACC

#05555h

; load accumulator with

SACL

TEMP

; 5555aaaah

TEMP, 16

LACC

OR

#0aaaah

```

```

SACL

; store aaaah in external data

SACH

; store 5555h in external data

SACL

; store aaaah in external data

SACH

; store 5555h in external data

; store aaaah in external data

SACL

; store 5555h in external data

SACH

SACL

; store aaaah in external data

SACH

*+

; store 5555h in external data

SAR

AR4,ADDR

; reset the address pointer

LACL

ADDR

SUB

#8

SACL

ADDR

LAR

AR4, ADDR

LACC

; read and accumulate the values

ADD

; written before

*+

ADD

ADD

*+

ADD

ADD

ADD

*+

ADD

ADD

; add 4 to the accumulator

#0ffffh

; if all reads and writes are ok

AND

BCND

ERR_CONS1, NEQ

; ACCU = 0. If not ERR_CONS1

C1:

MAR

*, AR3

; stay in loop until AR3 = 0

CONS1, *-, AR4

BANZ

; post increment loop counter AR3

LACC

#RANGE, 13

; same as above

SACH

TEMP

; this time with 0000 and ffffh

; as values to be written to

AR3, TEMP

LAR

LAR

AR4, #testmem

; external memory

*,AR4

MAR

CONS2: LACC

#0ffffh

SACL

TEMP

LACC

TEMP, 16

SACL

*+

SACH

*+

SACL

SACH

*+

SACL

*+

SACH

SACL

*+

*+

SACH

SAR

AR4, ADDR

LACL

ADDR

SUB

#8

SACL

ADDR

AR4, ADDR

LAR

LACC

*+

*+

ADD

ADD

*+

ADD

ADD

ADD

ADD

ADD

#4

ADD

AND

#0ffffh

BCND

ERR_CONS2, NEQ

C2:

*, AR3

MAR

BANZ

CONS2, *-, AR4

LACC

_RXREADY

; check if interrupt occurred

BCND

START, EQ

; from UART. If not start again

NOP

; with memory test

NOP

LARP

AR1

; reload stack pointer

SBRK

LAR

AR0,*-

PSHD

RET

```

```

ERR_D1 LACC _ERR

; add 1 to the

ADD #1

; error counter

SACL _ERR

; and continue

B D1

ERR_D2 LACC _ERR

; program execution

ADD #1

SACL _ERR

B D2

ERR_D3 LACC ERR

ADD #1

SACL _ERR

B D3

ERR_D4 LACC _ERR

ADD #1

SACL _ERR

B D4

ERR_P1 LACC _ERR

ADD #1

SACL _ERR

В

P1

ERR_P2 LACC _ERR

ADD #1

SACL _ERR

B P2

ERR_P3 LACC _ERR

ADD #1

SACL _ERR

B P3

ERR_P4 LACC ERR

ADD #1

SACL _ERR

__...R

P4

В

ERR_CONS1

LACC _ERR

ADD #1

SACL _ERR

C1

В

ERR_CONS2

LACC _ERR

ADD #1

SACL _ERR

В

C2

```

```

/***********************

/* Test Program for EMU5X running on a LC56

/* Configurations of processor:

1) Microprocessor mode (MP/MC=1)

2) B0 DARAM configure on data space (CNF=0)

3) {\tt 6K} Single Access {\tt Ram} configure in Program space

main.obj

mem.obj

-stack 512

-cr

-i c:\dsp\c5x\lib

-l rts50.lib

-m main.map

-o main.out

-v0

MEMORY

PAGE 0:

EXT_PROG : origin = 555h ,length = 7000h

/* 32K ext RAM

/* 6K RAM

PROG_RAM : origin = 8800h ,length = 1000h

PAGE 1 :

REGS : origin = 0000h ,length = 0060h

/* MEM REG

/* Always Data

/* CNF=0

DARAM_B2: origin = 0060h ,length = 0020h

RAM_B0B1: origin = 0100h ,length = 0400h

EXT_DATA: origin = 2000h ,length = 6000h BLK0 : origin = 0800h ,length = 0800h

/* 24K ext RAM

/* OVLY=1

/* SECTIONS ALLOCATION

SECTIONS

} > EXT_PROG PAGE 0

} > PROG_RAM PAGE 0

} > PROG_RAM PAGE 0

} > RAM_B0B1 PAGE 1

test_p :

vectors:

/* CODE

.text :

/* GLOBAL VARS, STACK, HEAP

.bss :

} > RAM_B0B1

} > EXT_DATA

} > DARAM_B2

.data :

PAGE 1

/* Initialized var

test_d :

PAGE 1

PAGE 1

/* DARAM_B2

b2

> DARAM_B2

> PROG_RAM

> RAM_B0B1

> RAM_B0B1

> BLK0

.cinit :

PAGE 0

PAGE 1

.const :

.stack :

PAGE 1

/* Transmit Buffer

txbuff :

PAGE 1

} > BLK0

rxbuff:

PAGE 1

/* Receive Buffer

}

```

## Appendix B PAL Programming

## " EVM used for TMS320LC56

```

MODULE module_name

lc56_2 DEVICE 'p16v8r';

"INPUTS

CLK, A15, A14, RW, IS

PIN 1,2,3,4,5;

DS, CLKOUT, STRB, RD

PIN 6,7,8,9;

ΟE

PIN 11;

"OUTPUTS

PIN 19;

CLK_A

WEX

PIN 18;

ΒE

PIN 17;

ISX

PIN 16;

PIN 14;

Α

RDX

PIN 13;

EX

PIN 12;

X,C,Z=.X.,.C.,.Z.;

EQUATIONS

"UART READ & WRITE ACCESS

!CLK_A = CLKOUT;

!A := !RD;

= !IS & !STRB & RW & !A & !A14 & A15;

!RDX

!WEX

= !IS & !STRB & !RW & !A14 & A15;

"LED STROBE

!ISX

= !A15 & !A14 & !IS & !STRB;

"BUFFER ENABLE

= !IS # !DS & A15;

!BE

"EPROM ENABLE

= !IS & A15 & A14 # !DS & A15;

!EX

```

```

TEST_VECTORS ([CLK,RD,CLKOUT] -> [CLK_A,A])

-> [ 1,

-> [ 0,

[C,

0,

0]

0];

[C,

1,

1]

1];

TEST_VECTORS ([CLK,RD,IS,STRB,RW,A14,A15] -> [A,RDX])

[C,

0,0,

0,

0,

0, 1]

-> [0, 1];

[C,

0,

0,0,

1,

0,1]

-> [0, 0];

0,

[C,

1, 0,

1,

0, 1]

-> [1, 1];

[C,

1,

1,

0,1]

-> [0, 1];

0,0,

1,

0,0,

0,

0,0]

-> [0, 1];

TEST_VECTORS ([CLK, IS, STRB, RW, A14, A15] -> [WEX])

0,

[C,

0,

0,

0,1]

0,

[C,

1,

Ο,

0, 1]

0,

1,

0,

[ 1 ];

[C,

0, 1]

->

0,

-> [ 1 ];

0,

1,

[C,

0, 1]

-> [ 1 ];

[C,

0,

0,

0,

1, 1]

TEST_VECTORS ([CLK,IS,A15,A14,STRB] -> [ISX])

[C,

Ο,

0,

0 ] -> [ 1 ];

1,

0,

[C,

Ο,

0,

0 ] -> [ 0 ];

[C,

0, 1,

Ο,

0 ] -> [ 1 ];

0,

1, 0,

0 ] -> [ 1 ];

[C,

1,

[C,

0, 1,

0 ] -> [ 1 ];

0,

Ο,

0,

1 ] -> [ 1 ];

[C,

TEST_VECTORS ([CLK,IS,A15,DS] -> [BE])

[C,

1,

1,

0] -> [ 0];

[C,

0,

01 -> [ 01;

0,

1,

[C,

Ο,

0] -> [1];

1,

Ο,

1] -> [ 1];

[C,

TEST_VECTORS ([CLK,A15,A14,IS,DS] -> [EX])

1,

[C,

1,

[C,

1,

Ο,

[C,

Ο,

1,

0, 0] -> [

1 ];

0,

0,

1, 0] -> [ 1 ];

[C,

[C,

0,

0,

0, 1] -> [ 1 ];

```

END module\_name

```

" EVM used for TMS320LC541,3,6

MODULE module name

lead_1 DEVICE 'p16v8r';

"INPUTS

CLK, A15, A14, RW, IS

PIN 1,2,3,4,5;

DS,CLKOUT,STRB

PIN 6,7,8;

MSTRB

PIN 15;

OE

PIN 11;

"OUTPUTS

PIN 19;

CLK_A

PIN 18;

WEX

PIN 17;

ΒE

ISX

PIN 16;

WE

PIN 14;

PIN 13;

RDX

PIN 12;

EΧ

X,C,Z=.X.,.C.,.Z.;

EQUATIONS

"UART READ & WRITE ACCESS

!CLK_A = CLKOUT;

!WE

= !MSTRB & !RW;

= !IS & !STRB & RW & !A14 & A15;

!RDX

!WEX

= !IS & !STRB & !RW & !A14 & A15;

"LED STROBE

!ISX

= !A15 & !A14 & !IS & !STRB;

"BUFFER ENABLE

!BE

= !IS # !DS & A15;

"EPROM ENABLE

!EX

= !IS & A15 & A14 # !DS & A15;

```

```

TEST_VECTORS ([CLK,CLKOUT] -> [CLK_A])

[C,

0]

-> [ 1];

[C,

-> [ 0];

1]

TEST_VECTORS ([CLK,MSTRB, RW] -> [WE])

[C,

1] -> [ 1];

[C,

1

1] -> [ 1];

[C,

1

1] -> [ 1];

0

0] -> [ 0];

TEST_VECTORS ([CLK, IS, STRB, RW, A14, A15] -> [RDX])

0,

0,

0,

[C,

0, 1]

Ο,

0,

1,

0, 1]

0, 1,

0,1]

Ο,

-> [ 0 ];

0,

1,

[C,

1,

0, 1]

-> [ 1 ];

0,

0,

[C,

1,

0,0]

-> [ 1 ];

TEST_VECTORS ([CLK, IS, STRB, RW, A14, A15] -> [WEX])

0,

[C,

0,

0,

0, 1]

-> [ 0 ];

[C,

0,

0, 1]

1,

0,

-> [ 1 ];

0, 1,

0,

[C,

0, 1]

-> [ 1 ];

[C,

0, 0,

1, 0, 1]

-> [ 1 ];

0,

[C,

0,

1, 1]

0,

TEST_VECTORS ([CLK,IS,A15,A14,STRB] -> [ISX])

0,

[C,

1,

Ο,

0 ] -> [

[C,

0,

0,

0];

Ο,

0 ] ->

[

0,

0,

[C,

1,

0 | -> |

1 1;

0,

1,

Ο,

[C,

0 ] -> [ 1 ];

1,

0 ] -> [ 1 ];

[C,

Ο,

1,

Ο,

0,

[C,

0,

1 ] -> [ 1 ];

TEST_VECTORS ([CLK,IS,A15,DS] -> [BE])

0] -> [ 0];

1,

0,

0,

0] -> [ 0];

[C,

1,

0,

[C,

0] -> [1];

[C,

1,

0,

1] -> [ 1];

TEST_VECTORS ([CLK,A15,A14,IS,DS] -> [EX])

[C,

1,

1,

0, 1] -> [ 0 ];

0, 0] -> [ 0 ];

[C,

1,

Ο,

0,

0, 0] -> [

[C,

1,

1 ];

0,