#### TLC5502-5M 8-BIT ANALOG-TO-DIGITAL CONVERTER

SGLS067 - MARCH 1992

LinEPIC™ 1-μm CMOS Process J PACKAGE (TOP VIEW) 8-Bit Resolution Differential Linearity Error . . . ±0.2% Max DGTL GND1 24 ANLG GND Maximum Conversion Rate . . . 20 MHz Typ (LSB) D0 23 DGTL V<sub>DD</sub>1 ... 10 MHz Min D1**∏** 3 22 ANLG V<sub>DD</sub> Analog Input Voltage Range ... 0 V to V<sub>DD</sub> D2**∏** 4 21 TREFB D3**∏** 5 20 ANLG INPUT TTL Digital I/O Level D4 □ 6 19 ANLG INPUT Low Power Consumption . . . 150 mW Typ D5**[**] 7 18 REFM 5-V Single-Supply Operation D6**∏** 8 17 | REFT (MSB) D7 16 ANLG V<sub>DD</sub> description CLK 10 15 DGTL V<sub>DD</sub>2 14 ANLG GND The TLC5502-5M is a low-power ultra-high-speed DGTL GND2 11 8-bit analog-to-digital converter that uses the NCL 13 NC

LinEPIC™ CMOS process. It utilizes the full parallel comparison (flash method) for High-speed conversion. Because of such high-speed capability, the TLC5502-5M is suitable for full processing, and video or radar signal processing.

Separate analog and digital supply pins are provided to reduce coupling between the high-speed digital switching sections and the lower-frequency analog signal comparators. This pin partitioning minimizes crosstalk and unwanted spurious signals.

The TLC5502-5M is characterized for operation from -55°C to 125°C.

During storage or handling, the device leads should be shorted together or the device should be placed in conductive foam. In a circuit, unused inputs should always be connected to an appropriated logic voltage level, preferably either V<sub>CC</sub> or ground. Specific guidelines for handling devices of this type are contained in the publication *Guidelines for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices and Assemblies* available from Texas Instruments.

LinEPIC is a trademark of Texas Instruments Incorporated.

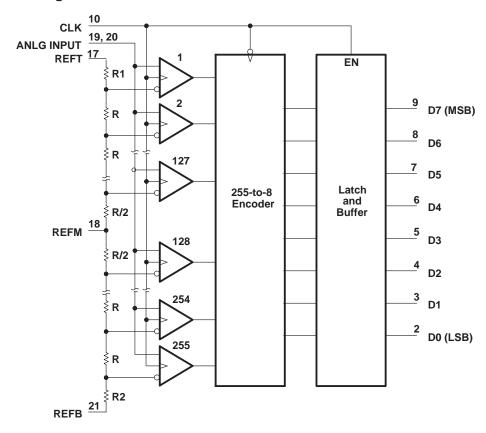

#### functional block diagram

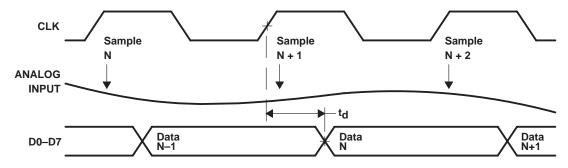

#### operating sequence

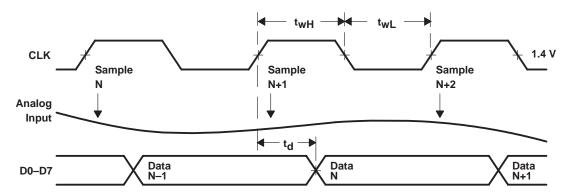

Following the operating sequence above, the rising edge of the clock samples the analog input (sample N) at time  $t_N$  and latches sample N-1 at the output. Sample N is encoded to eight digital lines on the next falling edge of the clock and then the following high clock level latches these eight bits to the outputs (with a delay  $t_d$ ) and acquires sample N + 1. Conversion is completed in one clock cycle and continues the sequence for the next cycle.

SGLS067 - MARCH 1992

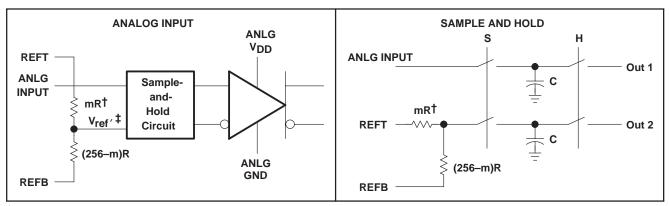

#### equivalents of analog input circuit

$<sup>\</sup>dagger$  m = comparator position along the resistor string

$$^{\ddagger} \ V_{ref}{'} \ = \left[V_{refT} \ - \ V_{refB}\right] \left[1 \ - \ \frac{M}{256}\right] \ + \ V_{refB}$$

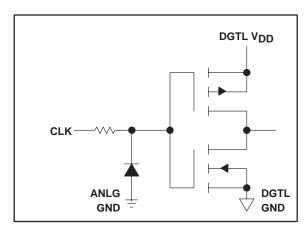

## equivalent of digital input circuit

#### **FUNCTION TABLE**

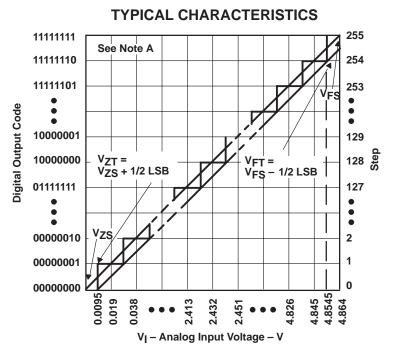

| STEP | ANALOG INPUT<br>VOLTAGE† | DIGITAL OUTPUT<br>CODE |   |   |   |    |   |   |    |

|------|--------------------------|------------------------|---|---|---|----|---|---|----|

| 0    | 0.000 V                  | L                      | L | L | L | L  | L | L | ᄀ  |

| 1    | 0.019 V                  | L                      | L | L | L | L  | L | L | н  |

| :    | :                        |                        |   |   |   |    |   |   |    |

| 127  | 2.413 V                  | L                      | Н | Н | Н | Н  | Н | Н | н  |

| 128  | 2.432 V                  | Н                      | L | L | L | L  | L | L | ᅵᅵ |

| 129  | 2.451 V                  | Н                      | L | L | L | L  | L | L | н  |

| :    | :                        |                        |   |   |   |    |   |   |    |

| 254  | 4.826 V                  | н                      | Н | Н | Н | Н. | Н | Н | 니  |

| 255  | 4.845 V                  | Н                      | Н | Н | Н | Н  | Н | Н | Н  |

<sup>†</sup> These values are based on the assumption that  $V_{refB}$  and  $V_{refT}$  have been adjusted so that the voltage at the transition from digital 0 to 1 ( $V_{ZT}$ ) is 0 V and the transition to full scale ( $V_{FT}$ ) is 4.8545 V. 1 LSB = 19 mV.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, ANLG V <sub>DD</sub> (see Note 1)      | –0.5 V to 7 V                            |

|--------------------------------------------------------------|------------------------------------------|

| Supply voltage range, DGTL V <sub>DD</sub> (see Note 1)      | $-0.5\ V$ to 7 V                         |

| Input voltage range at CLK, V <sub>I</sub>                   | $-0.3$ V to DGTL V <sub>DD</sub> + 0.3 V |

| Input voltage range at analog input, V <sub>I</sub>          | $-0.5$ V to ANLG V <sub>DD</sub> + 0.5 V |

| Analog reference voltage range, V <sub>ref</sub>             | $-0.5$ V to ANLG V <sub>DD</sub> + 0.5 V |

| Operating free-air temperature range, T <sub>A</sub>         | –55°C to 125°C                           |

| Storage temperature range                                    | –55°C to 150°C                           |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                                    |

NOTE 1: Voltages at analog inputs and ANLG V<sub>DD</sub> are with respect to the ANLG GND terminals. Voltages at the digital outputs and DGTL V<sub>DD</sub> are with respect to the DGTL GND terminals.

#### recommended operating conditions

|                                                                       | MIN  | NOM                             | MAX  | UNIT |

|-----------------------------------------------------------------------|------|---------------------------------|------|------|

| Supply voltage, ANLG V <sub>DD</sub>                                  | 4.75 | 5                               | 5.25 | V    |

| Supply voltage, DGTL V <sub>DD</sub>                                  | 4.75 | 5                               | 5.25 | V    |

| High-level input voltage, V <sub>IH</sub> , CLK                       | 2    |                                 |      | V    |

| Low-level input voltage V <sub>IL</sub> , CLK                         |      |                                 | 0.8  | V    |

| Input voltage at analog input, V <sub>I</sub>                         | 0    |                                 | 5    | V    |

| nalog reference voltage (top side), V <sub>refT</sub>                 |      | ANLG<br>V <sub>DD</sub>         |      |      |

| Analog reference voltage (midpoint), V <sub>refM</sub>                |      | $\frac{V_{refT} - V_{refB}}{2}$ |      |      |

| Analog reference voltage (bottom side), V <sub>refB</sub>             |      | 0                               |      |      |

| Differential reference voltage, V <sub>refT</sub> – V <sub>refB</sub> | 5    |                                 | V    |      |

| High-level output current, IOH                                        |      |                                 | -400 | μΑ   |

| Low-level output current, IOL                                         |      |                                 | 4    | mA   |

| Clock pulse duration, high or low, t <sub>WH</sub> or t <sub>WL</sub> | 50   |                                 |      | ns   |

| Operating free-air temperature, T <sub>A</sub>                        | -55  |                                 | 125  | °C   |

SGLS067 - MARCH 1992

# electrical characteristics over operating supply voltage range, $T_A = 25^{\circ}C$

| PARAMETER         |                                   | TEST CONDITIONS                                                      | MIN | TYP  | MAX | UNIT |

|-------------------|-----------------------------------|----------------------------------------------------------------------|-----|------|-----|------|

| Vон               | High-level output voltage         | I <sub>OH</sub> = -400 μA                                            | 2.4 |      |     | V    |

| VOL               | Low-level output voltage          | I <sub>OL</sub> = 4 mA                                               |     |      | 0.4 | V    |

| lį                | Analog input current              | $V_I = 0 \text{ to } 5 \text{ V}, \qquad f_{Clock} = 10 \text{ MHz}$ |     | ±0.5 |     | mA   |

| lН                | Digitial high-level input current | V <sub>I</sub> = 5 V                                                 |     |      | 1   | μΑ   |

| IIL               | Digital low-level input current   | V <sub>I</sub> = 0                                                   |     |      | -1  | μΑ   |

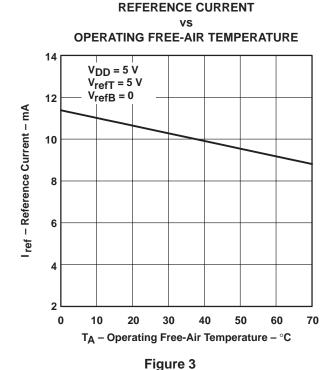

| I <sub>refB</sub> | Reference current                 | V <sub>refB</sub> = 0                                                |     | -10  | -20 | mA   |

| I <sub>refT</sub> | Reference current                 | V <sub>refT</sub> = 5 V                                              |     | 10   | 20  | mA   |

| Ci                | Analog input capacitance          |                                                                      |     | 50   |     | pF   |

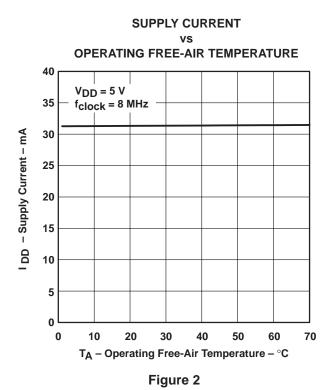

| $I_{DD}$          | Supply current                    | f <sub>clock</sub> = 10 MHz                                          |     | 30   | 60  | mA   |

# operating characteristics over operating supply voltage range, $T_A$ = 25°C

| PARAMETER            |                                     | TEST CONDITIONS                                         | MIN | TYP  | MAX  | UNIT |

|----------------------|-------------------------------------|---------------------------------------------------------|-----|------|------|------|

| f <sub>c</sub> (max) | Maximum conversion rate             |                                                         | 10  | 20   |      | MHz  |

| ED                   | Linearity error, differential       | V <sub>I</sub> = 0 to 5 V                               |     | ±0.1 | ±0.2 | %FSR |

| EL                   | Linearity error, best straight line | V <sub>I</sub> = 0 to 5 V                               |     |      | ±0.4 | %FSR |

| SNR <sup>†</sup>     | Signal to noise ratio               | $f_{Clock} = 9.9 \text{ MHz}, f_{IN} = 97 \text{ kHz},$ |     | -50  |      | dB   |

| THD                  | Total harmonic distortion           | BW = 5 MHz                                              |     | 51   |      | dB   |

| BW                   | Analog input bandwidth (3 dB)       | f <sub>Clock</sub> = 10 MHz                             |     | 5    |      | MHz  |

| t <sub>d</sub>       | Delay time, digital output          | C <sub>L</sub> = 15 pF                                  |     | 10   | 30   | ns   |

<sup>†</sup> SNR is total noise without THD.

### timing diagram

NOTE A: This curve is based on the assumption that  $V_{refB}$  and  $V_{refT}$  have been adjusted so that the voltage at the transition from digital 0 to 1 ( $V_{ZT}$ ) is 0 and the transition to full scale ( $V_{FT}$ ) is 4.8545 V. 1 LSB = 19 mV.

Figure 1. Ideal Conversion Characteristics

TEXAS

INSTRUMENTS

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

#### TYPICAL CHARACTERISTICS

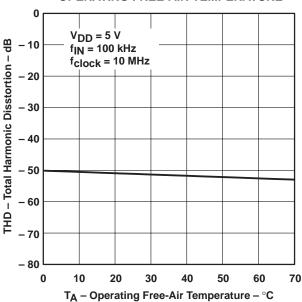

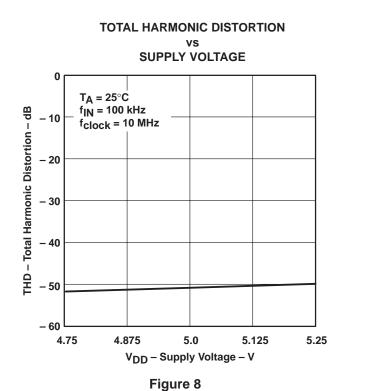

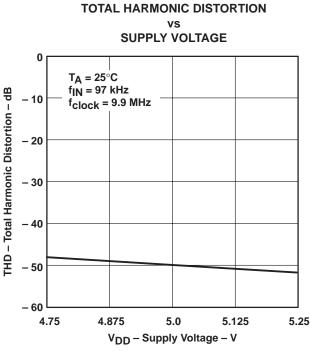

### TOTAL HARMONIC DISTORTION

#### **OPERATING FREE-AIR TEMPERATURE**

Figure 4

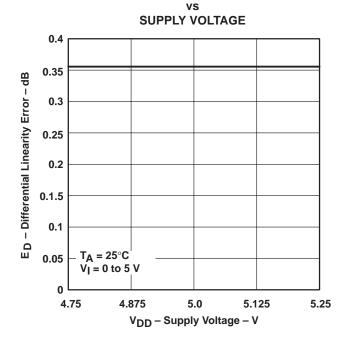

# DIFFERENTIAL LINEARITY ERROR

Figure 6

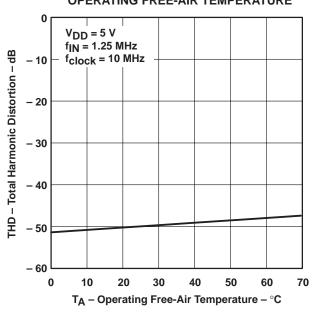

# TOTAL HARMONIC DISTORTION vs OPERATING FREE-AIR TEMPERATURE

Figure 5

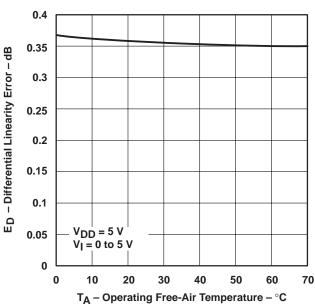

# DIFFERENTIAL LINEARITY ERROR vs

## OPERATING FREE-AIR TEMPERATURE

Figure 7

#### **TYPICAL CHARACTERISTICS**

Figure 9

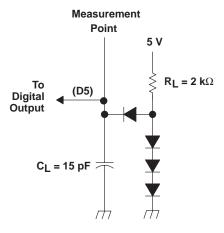

#### PARAMETER MEASUREMENT INFORMATION

Figure 10. Load Circuit

SGLS067 - MARCH 1992

#### **APPLICATION INFORMATION**

The following design recommendations will benefit the TLC5502-5M user:

- 1. External analog and digital circuitry should be physically separated and shielded as much as possible to reduce system noise.

- 2. RF breadboarding or PCB techniques should be used throughout the evaluation and production process. Breadboards should be copper clad for bench evaluation.

- 3. Since the ANLG GND, DGTL GND1, and DGTL GND2 are not connected internally, these pins need to be connected externally. With breadboards, these ground lines should be connected through separate leads with proper supply bypassing. A good method to use is a separate twisted-pair cable for the supply lines to minimize noise pickup. An analog and digital ground plane should be used on PCB layouts.

- 4. Since the ANLG  $V_{DD}$ , DGTL  $V_{DD}$ 1, and DGTL  $V_{DD}$ 2 are not connected internally, these pins also need to be connected externally. To connect ANLG  $V_{DD}$ , DGTL  $V_{DD}$ 1, and DGTL  $V_{DD}$ 2, a 50- $\Omega$  resistor should be placed in series with DGTL  $V_{DD}$ 1 and then a 0.1- $\mu$ F capacitor to ground before being connected to ANLG  $V_{DD}$  and DGTL  $V_{DD}$ 2.

- 5. ANLG  $V_{DD}$  to ANLG GND, DGTL  $V_{DD}$ 1 to DGTL GND1, and DGTL  $V_{DD}$ 2 to DGTL GND2 should be decoupled with 1- $\mu$ F and 0.01- $\mu$ F capacitors, respectively, as close as possible to the appropriate device pins. A ceramic-chip capacitor is recommended for the 0.01- $\mu$ F capacitor. Care should be exercised to assure a solid noise free ground connection for the analog and digital grounds.

- 6. The no connection (NC) pins on the J package should be connected to ground.

- ANLG V<sub>DD</sub>, ANLG GND, and ANLG INPUT should be shielded from the higher-frequency pins, CLK and D0–D7. If possible, ANLG GND traces should be placed on both sides of the ANLG INPUT traces on the PCB.

- 8. In testing or application of the device, the resistance of the driving source connected to the analog input should be 10  $\Omega$  or less within the analog frequency range of interest.

## TLC5502-5M 8-BIT ANALOG-TO-DIGITAL CONVERTER

SGLS067 - MARCH 1992

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated