# TMC2192 10 Bit Encoder

# **Features**

- Multiple input formats

- 20 bit CCIR601

- 10 bit CCIR656

- 10 bit Digital Composite

- · Synchronization modes

- Master

- Slave

- Genlock

- CCIR656

- · Subcarrier modes

- Free-run

- Subcarrier reset

- Genlock

- DRS-lock

- Ancillary Data Control (ANC)

- Pixel rates from 10 MHz to 15 MHz

- Programmable horizontal timing

- Programmable vertical blanking interval (VBI)

- Line-by-line pedestal enable

- Programmable pedestal height from -20 IRE to 20 IRE

- · Programmable burst amplitude and phase

- · Controlled edge rates for

- Sync

- Burst

- Active video

- · Programmable color space matrix

- 8:8:8 video reconstruction

- Three 10 bit D/A's with independent trim

- Individual power down modes for each D/A

- Multiple output formats

- S-video

- Composite

- Digital composite output

- · Pin-driven and data-driven, window keying

- Closed Caption waveform generation (13.5 MHz only)

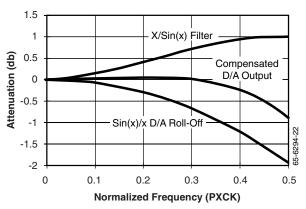

- Sin(X)/X compensation filter

- 5 bit VBI line counter

- 3 bit field counter

- · Internal test pattern generation

- 100% Color Bars

- 75% Color Bars

- Modulated Ramp

# **Applications**

- · Broadcast Television

- Nonlinear Video Processing

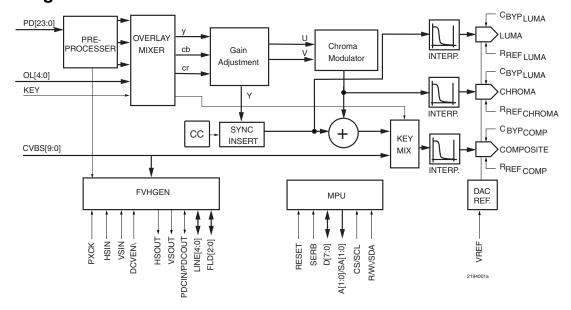

# **Block Diagram**

# **Table of Contents**

| Features                             | Inte   |

|--------------------------------------|--------|

| Applications1                        | x/S    |

| Block Diagram                        | Out    |

| 10 Bit Encoder                       | Dig    |

| List of Figures                      | And    |

| List of Tables                       | Lay    |

| Pin Assignments4                     | ,      |

| Pin Definitions4                     | Har    |

| Functional Description               | Dat    |

| Input Formats7                       | Par    |

| Color Space Matrix 9                 | Ser    |

| Synchronization Modes 10             |        |

| Propagation Delay                    | Contro |

| Blanking Control                     | Contro |

| Pixel Data Control                   | Absol  |

| Edge Shaping                         | Opera  |

| Horizontal Programming12             | Electr |

| Vertical Timing                      |        |

| Chrominance Processor                | Switcl |

| Subcarrier Programming               | Syste  |

| PAL Subcarrier                       | Applic |

| PAL-M Subcarrier                     | Lay    |

| Subcarrier Synchronization           | Out    |

| Burst Envelope 23                    | Mecha  |

| Color-Difference Low-Pass Filters 23 | 100    |

| Sync and Pedestal Insertion          |        |

| Pedestal Enable                      | Order  |

| Sync and Blank Insertion             | Life S |

| Closed Caption Insertion 24          |        |

| Line Selection                       |        |

| Parity Generation                    |        |

| Interpolation Filters 25                                                         |

|----------------------------------------------------------------------------------|

| x/Sin(x) Filter                                                                  |

| Output Data Formats25                                                            |

| Digital Composite Output 26                                                      |

| Ancillary Data26                                                                 |

| Operating Modes 27                                                               |

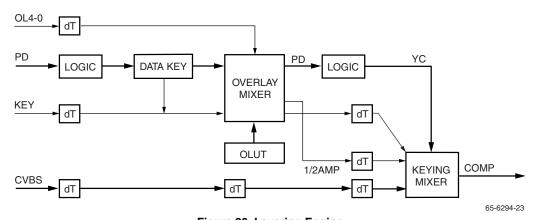

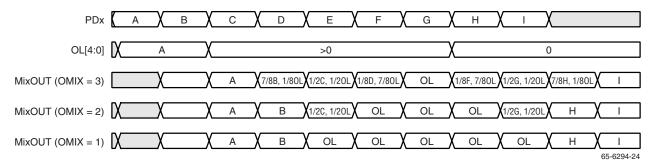

| Layering Engine                                                                  |

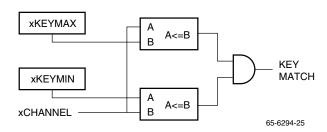

| Hardware Keying 29                                                               |

| Data Keying                                                                      |

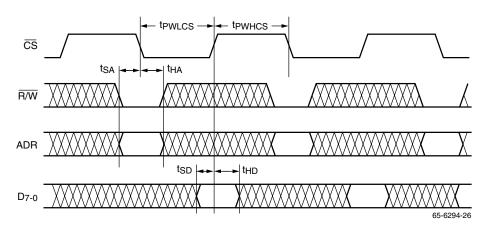

| Parallel Microprocessor Interface 29                                             |

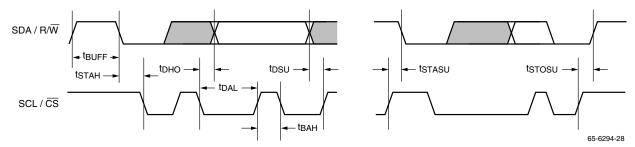

| Serial Control Port (R-Bus)                                                      |

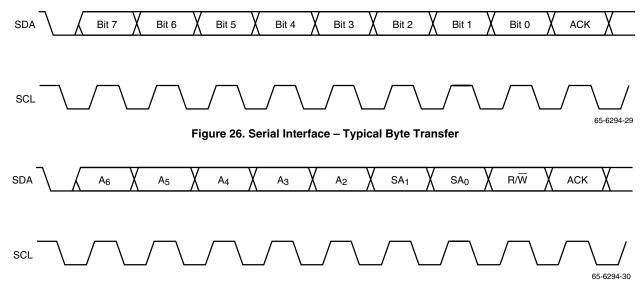

| Data Transfer via Serial Interface 31<br>Serial Interface Read/Write Examples 31 |

| Control Register Map33                                                           |

| Control Register Definitions35                                                   |

| Absolute Maximum Ratings60                                                       |

| Operating Conditions                                                             |

| Electrical Characteristics62                                                     |

| Switching Characteristics62                                                      |

| System Performance Characteristics63                                             |

| Applications Discussion63                                                        |

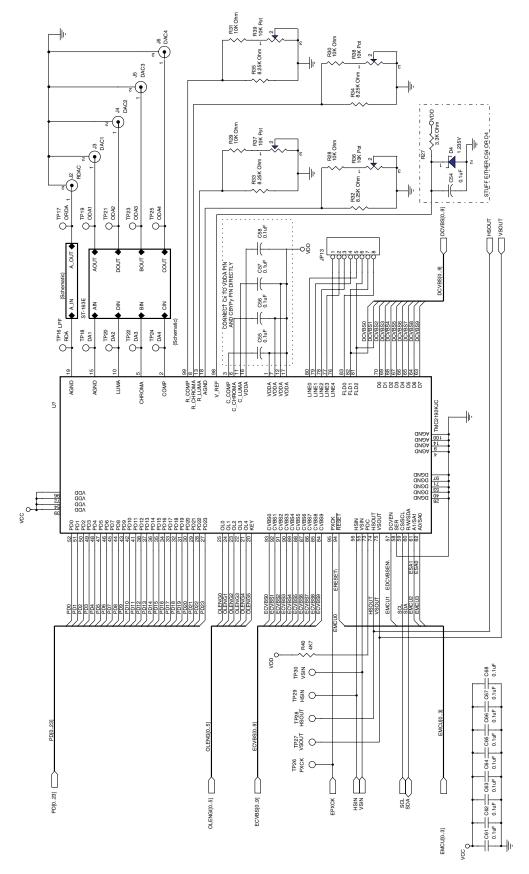

| Layout Considerations 64                                                         |

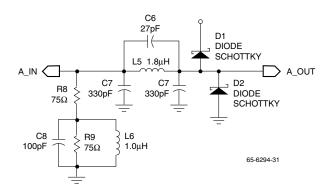

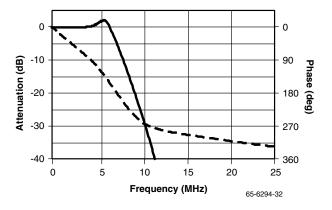

| Output Low-Pass Filters 67                                                       |

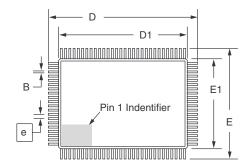

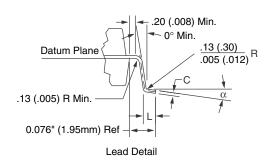

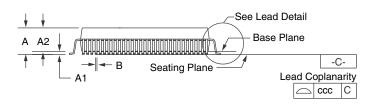

| Mechanical Dimensions                                                            |

| 100-Lead MQFP 71                                                                 |

| Ordering Information                                                             |

| Life Support Policy                                                              |

|                                                                                  |

| List of F  | Figures                                 | List of   | Tables                              |

|------------|-----------------------------------------|-----------|-------------------------------------|

| Figure 1.  | Input Formats                           | Table 1.  | CSM Coefficient Range 9             |

| Figure 2.  | 24 bit Input Format                     | Table 2.  | Expected Output Values for the      |

| Figure 3.  | CCIR656 Input Format                    |           | CSM with YCBCR Inputs 9             |

| Figure 4.  | 10 bit Input Format                     | Table 3.  | PDC Edge Control                    |

| Figure 5.  | 20 bit 4:2:2 Input Format               | Table 4.  | Horizontal Line Equations 12        |

| Figure 6.  | 20 bit 4:4:4 Input Format               | Table 5.  | Horizontal Timing Specifications 13 |

| Figure 7.  | Propagation Delay through the           | Table 6.  | Vertical Interval Timing            |

|            | Encoder                                 |           | Specifications                      |

| Figure 8.  | Horizontal Timing                       | Table 7.  | Default Horizontal Timing           |

| Figure 9.  | Horizontal Timing – Vertical Blanking13 |           | Parameters                          |

| Figure 10. | Horizontal Timing – 1st Half-line14     | Table 8.  | NTSC Field/Line Sequence and        |

| Figure 11. | Horizontal Timing – 2nd Half-line 14    |           | Identification                      |

| Figure 12. | NTSC Vertical Interval                  | Table 9.  | PAL Field/Line Sequence and         |

| Figure 13. | PAL Vertical Interval                   |           | Identification                      |

| Figure 14. | PAL-M Vertical Interval                 | Table 10. | PAL-M Field/Line Sequence and       |

| Figure 15. | Burst Envelope                          |           | Identification 20                   |

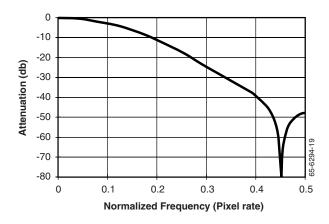

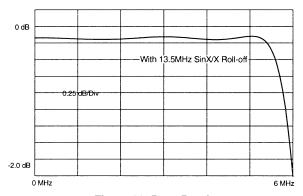

| Figure 16. | Gaussian Filter Response23              | Table 11. | Standard Subcarrier Parameters 22   |

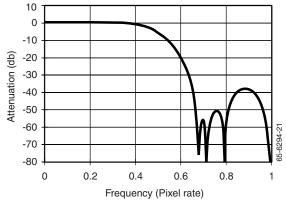

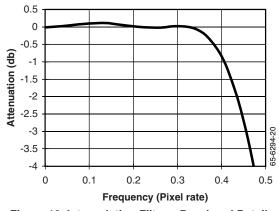

| Figure 17. | Interpolation Filter                    | Table 12. | Line by Line Pedestal Enable 23     |

| Figure 18. | Interpolation Filter – Passband         | Table 13. | Closed Caption Line Selection 24    |

|            | Detail                                  | Table 14. | D/A Outputs                         |

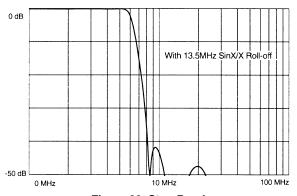

| Figure 19. | X/SIN(X) Filter                         | Table 15. | Ancillary Data Format               |

| Figure 20. | Layering Engine                         | Table 16. | Ancillary Data Control – Phase 27   |

| Figure 21. | Overlay Outputs                         | Table 17. | Ancillary Data Control Frequency 27 |

| Figure 22. | Data Keying                             | Table 18. | Field Identification and Subcarrier |

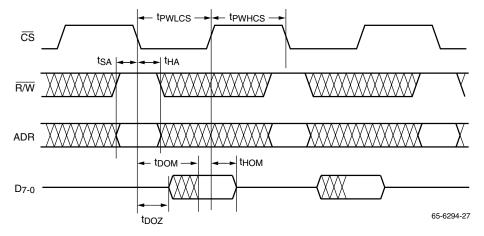

| Figure 23. | Microprocessor Parallel Port –          |           | Reset Modes 27                      |

|            | Write Timing                            | Table 19. | Layering and Keying Modes 28        |

| Figure 24. | Microprocessor Parallel Port –          | Table 20. | Overlay Address Map 29              |

|            | Read Timing                             | Table 21. | Parallel Port Control               |

| Figure 25. | Serial Port Read/Write Timing           | Table 22. | Serial Port Addresses               |

| Figure 26. | Serial Interface – Typical Byte         | Table 23. | Control Register Map                |

|            | Transfer32                              |           |                                     |

| Figure 27. | Serial Interface – Chip Address         |           |                                     |

| Figure 28. | Typical Analog Reconstruction Filter63  |           |                                     |

| Figure 29. | Overall Response                        |           |                                     |

| Figure 30. | Typical Layout                          |           |                                     |

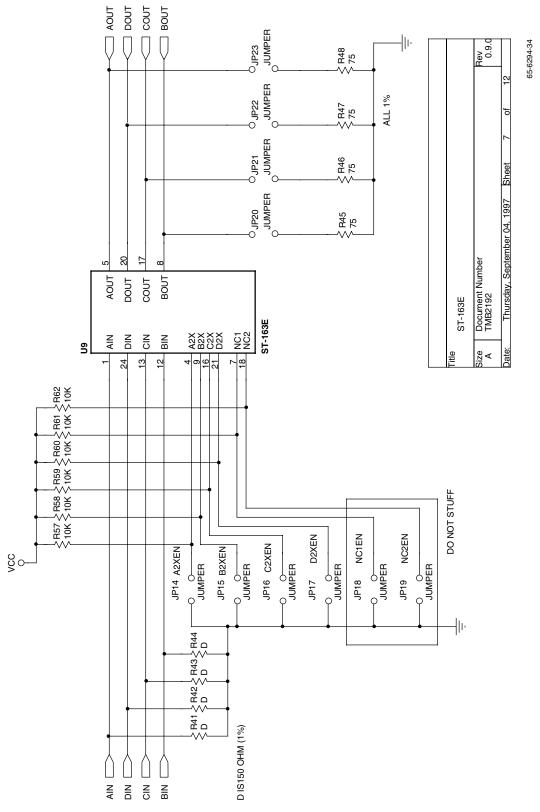

| Figure 31. | ST-163E Layout                          |           |                                     |

| Figure 32. | Pass Band                               |           |                                     |

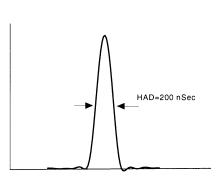

| Figure 33. | Stop Band                               |           |                                     |

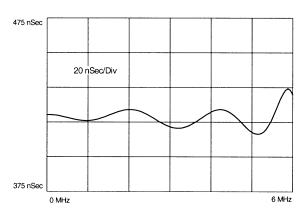

| Figure 34. | 2T Pulse                                |           |                                     |

| Figure 35. | Group Delay                             |           |                                     |

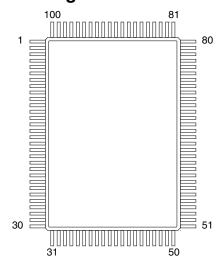

# **Pin Assignments**

65-6294-14

| Pin | Function             | Pin | Function         | Pin | Function         | Pin | Function         |

|-----|----------------------|-----|------------------|-----|------------------|-----|------------------|

| 1   | $V_{DDA}$            | 31  | PD <sub>19</sub> | 51  | PD <sub>1</sub>  | 81  | FLD2             |

| 2   | COMP                 | 32  | PD <sub>18</sub> | 52  | PD <sub>0</sub>  | 82  | FLD1             |

| 3   | C <sub>BYPCOMP</sub> | 33  | PD <sub>17</sub> | 53  | D <sub>GND</sub> | 83  | FLD0             |

| 4   | AGND                 | 34  | PD <sub>16</sub> | 54  | V <sub>DD</sub>  | 84  | CVBS9            |

| 5   | CHROMA               | 35  | PD <sub>15</sub> | 55  | VSIN             | 85  | CVBS8            |

| 6   | CBYPCHROM            | 36  | PD <sub>14</sub> | 56  | HSIN             | 86  | CVBS7            |

| 7   | VDDA                 | 37  | PD <sub>13</sub> | 57  | DCVEN            | 87  | CVBS6            |

| 8   | RREFCHROM            | 38  | PD <sub>12</sub> | 58  | SER              | 88  | CVBS5            |

| 9   | AGND                 | 39  | V <sub>DD</sub>  | 59  | CSVSCL           | 89  | CVBS4            |

| 10  | LUMA                 | 40  | D <sub>GND</sub> | 60  | R/W\/SDA         | 90  | CVBS3            |

| 11  | C <sub>BYPLUMA</sub> | 41  | PD <sub>11</sub> | 61  | A1/SA1           | 91  | CVBS2            |

| 12  | VDDA                 | 42  | PD <sub>10</sub> | 62  | A0/SA0           | 92  | CVBS1            |

| 13  | R <sub>REFLUMA</sub> | 43  | PD <sub>9</sub>  | 63  | D <sub>7</sub>   | 93  | CVBS0            |

| 14  | AGND                 | 44  | PD8              | 64  | D <sub>6</sub>   | 94  | RESET            |

| 15  | AGND                 | 45  | PD <sub>7</sub>  | 65  | D <sub>5</sub>   | 95  | PXCK             |

| 16  | $V_{DDA}$            | 46  | PD <sub>6</sub>  | 66  | D <sub>4</sub>   | 96  | $V_{DD}$         |

| 17  | VDDA                 | 47  | PD <sub>5</sub>  | 67  | D <sub>3</sub>   | 97  | DGND             |

| 18  | AGND                 | 48  | PD <sub>4</sub>  | 68  | D <sub>2</sub>   | 98  | V <sub>REF</sub> |

| 19  | AGND                 | 49  | PD <sub>3</sub>  | 69  | D <sub>1</sub>   | 99  | RREFCOMP         |

| 20  | KEY                  | 50  | PD <sub>2</sub>  | 70  | D <sub>0</sub>   | 100 | AGND             |

| 21  | OL <sub>4</sub>      |     |                  | 71  | D <sub>GND</sub> |     |                  |

| 22  | OL <sub>3</sub>      |     |                  | 72  | V <sub>DD</sub>  |     |                  |

| 23  | 0L <sub>2</sub>      |     |                  | 73  | PDC              |     |                  |

| 24  | 0L <sub>1</sub>      |     |                  | 74  | HSOUT            |     |                  |

| 25  | 0L <sub>0</sub>      |     |                  | 75  | VS0UT            |     |                  |

| 26  | D <sub>GND</sub>     |     |                  | 76  | LINE4            |     |                  |

| 27  | PD <sub>23</sub>     |     |                  | 77  | LINE3            |     |                  |

| 28  | PD <sub>22</sub>     |     |                  | 78  | LINE2            |     |                  |

| 29  | PD <sub>21</sub>     |     |                  | 79  | LINE1            |     |                  |

| 30  | PD <sub>20</sub>     |     |                  | 80  | LINE0            |     |                  |

# **Pin Definitions**

| Pin Name                               | Pin Number | Value | Description                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|----------------------------------------|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| CLOCK, SYNC, & CONTROL INPUTS (6 pins) |            |       |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| DCVEN                                  | 57         | TTL   | Digital CVBS Output Enable. When DCVEN is LOW, the Comp2 output prior to the D/A is routed to D7-0, FLD2-1 providing a digital composite output. When DCVEN is HIGH, D7-0 and FLD2-1 operate in their normal mode.                                                                                                                                                              |  |  |  |  |  |  |  |

| HSIN                                   | 56         | TTL   | Horizontal Sync Input. When operating in slave, Genlock, or DRS-Lock the TMC2192 will start a new horizontal line with each falling edge of HSIN.                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| KEY                                    | 20         | TTL   | Hard Key selection. When the control register bit HKEN is set HIGH and the hardware KEY pin is high, the video data considered to be the foreground. is routed to the COMP2 output. This control signal is data aligned so that the pixel that is present on the PD port when KEY signal is latched is at the midpoint of the key transition. When HKEN is LOW, Key is ignored. |  |  |  |  |  |  |  |

# Pin Definitions (continued)

| Pin Name    | Pin Number      | Value        | Description                                                                                                                                                                                                                                                                                              |

|-------------|-----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PXCK        | 95              | TTL          | Pixel Clock Input. PXCK is a clock signal that period is twice the sample rate of the pixel data. The operating range is 20 to 30 MHz. The clock is internally divided by 2 to generate the internal pixel clock, PCK. PXCK drives the entire TMC2192 except the asynchronous microprocessor interface.  |

| RESET       | 94              | TTL          | Master Chip Reset. When LOW, All outputs are tri-stated and the internal state machines and control registers are reset. At rising edge of RESET, all outputs are active, the preset values will be loaded into the control registers and the internal states machines start to operate.                 |

| VSIN        | 55              | TTL          | Vertical Sync Input. When operating in slave, Genlock, or DRS-Lock the TMC2192 will start a new vertical field with each falling edge of VSIN that is coincident with HSIN.                                                                                                                              |

| SYNC & CONT | ROL OUTPUTS (   | 11 pins)     |                                                                                                                                                                                                                                                                                                          |

| FLD[2:0]    | 81–83           | TTL          | <b>Field Identifier.</b> Field Identifier outputs the current field number. For all video standards the field identifier will cycle through the eight counts.                                                                                                                                            |

| HSOUT       | 74              | TTL          | Horizontal Sync Output. The alignment of HSOUT to the pixel data port or DCVBS port is controlled by control register TSOUT.                                                                                                                                                                             |

| LINE[4:0]   | 76–80           | TTL          | Vertical Blanking Interval Line Identifier. LINE identifies the current line number for the first 31 lines. If the line count is greater than 31 then LINE is 11111b. The first line with a vertical serration is considered to be line 0.                                                               |

| PDC         | 73              | TTL          | Pixel Data Control.                                                                                                                                                                                                                                                                                      |

|             |                 |              | When PDCDIR = LOW: At a rising edge, The next pixel starts a controlled ramp of the PD data. At a falling edge, the pixel prior is the last PD used in the ramp. The rising edge is determined by the PDCCNT control register, the falling edge of PDC is determined by the horizontal timing registers. |

|             |                 |              | When PDCDIR = HIGH: PDCIN is used to override the internal PDC. When HIGH, the internal PDC controls the blank and unblank window. When LOW, the video remains blanked regardless of the internal PDC. All edges have the same ramp control as the internal PDC.                                         |

| VSOUT       | 75              | TTL          | <b>Vertical Sync Output.</b> The alignment of VSOUT to the pixel data port or DCVBS port is controlled by control register TSOUT.                                                                                                                                                                        |

| DATA INPUTS | (39 pins)       |              | •                                                                                                                                                                                                                                                                                                        |

| CVBS[9:0]   | 84–93           | TTL          | Composite Data Input                                                                                                                                                                                                                                                                                     |

| OL[4:0]     | 21–25           | TTL          | Overlay Control                                                                                                                                                                                                                                                                                          |

| PD[23:0]    | 27–38, 41–52    | TTL          | Component Data Input                                                                                                                                                                                                                                                                                     |

| ANALOG INTE | RFACE – Video C | Out (5 pins) |                                                                                                                                                                                                                                                                                                          |

| LUMA        | 10              | 1.35Vp-p     | Luma                                                                                                                                                                                                                                                                                                     |

| CHROMA      | 5               | 1.35Vp-p     | Chroma                                                                                                                                                                                                                                                                                                   |

| COMP        | 2               | 1.35Vp-p     | Composite D/A with optional keying                                                                                                                                                                                                                                                                       |

# Pin Definitions (continued)

| Pin Name                    | Pin Number                   | Value       | Description                                                                                                                                                                                                                             |

|-----------------------------|------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG INTE                 | RFACE – Suppoi               | rt (9 pins) |                                                                                                                                                                                                                                         |

| CBYPLUMA                    | 11                           | 0.1 μF      | <b>Reference Bypass Capacitor for LUMA DAC.</b> Connection point for 0.1 μF Capacitor.                                                                                                                                                  |

| Свурсняюм                   | 6                            | 0.1 μF      | Reference Bypass Capacitor for CHROMA DAC. Connection point for 0.1 $\mu$ F Capacitor.                                                                                                                                                  |

| Свурсомр                    | 3                            | 0.1 μF      | Reference Bypass Capacitor for COMPOSITE DAC. Connection point for 0.1 µF Capacitor.                                                                                                                                                    |

| RREFLUMA                    | 13                           | 1210 Ohm    | Current Setting Resistor. Connection point for external current setting resistor for LUMA DAC. The resistor is connected between RREFLUMA and GND. Output video levels are inversely proportional to the value of RREF2.                |

| RREFCHROM                   | 8                            | 1210 Ohm    | <b>Current Setting Resistor.</b> Connection point for external current setting resistor for CHROMA DAC. The resistor is connected between RREFCHROM and GND. Output video levels are inversely proportional to the value of RREFCHROM.  |

| RREFCOMP                    | 99                           | 1210 Ohm    | <b>Current Setting Resistor.</b> Connection point for external current setting resistor for COMPOSITE DAC. The resistor is connected between RREFCOMP and GND. Output video levels are inversely proportional to the value of RREFCOMP. |

| VREF                        | 98                           | 1.235 V     | Voltage Reference Input. External voltage reference input, internal voltage reference output, nominally 1.235V.                                                                                                                         |

| MPU INTERFA                 | ACE (13 pins)                |             |                                                                                                                                                                                                                                         |

| A[1:0]/S <sub>A</sub> [1:0] | 61, 62                       | TTL         | When SER (HIGH), OLUT/control/pointer address. When SER (LOW), SA[1:0] of serial chip address SA[6:0].                                                                                                                                  |

| CS/SCL                      | 59                           | TTL/R-BUS   | When SER (HIGH), microprocessor port clock. When SER (LOW), serial bus clock.                                                                                                                                                           |

| D[7:0]                      | 63–70                        | TTL         | Bi-directional Data Bus.                                                                                                                                                                                                                |

| RW/SDA                      | 60                           | TTL/R-BUS   | When SER (HIGH), read/write control. When SER (LOW), serial bus bi-directional data.                                                                                                                                                    |

| SER                         | 58                           | TTL         | <b>Microprocessor Select.</b> When LOW, the serial interface is enabled. When HIGH, the parallel interface is enabled.                                                                                                                  |

| POWER & GR                  | OUND (17 pins)               |             |                                                                                                                                                                                                                                         |

| AGND                        | 4, 9, 14, 15, 18,<br>19, 100 | 0.0V        | Analog ground                                                                                                                                                                                                                           |

| DGND                        | 26, 40, 53, 71, 97           | 0.0V        | Digital ground                                                                                                                                                                                                                          |

| V <sub>DD</sub>             | 39, 54, 72, 96               | +5.0V       | Digital positive power supply                                                                                                                                                                                                           |

| VDDA                        | 1, 7, 12, 16, 17             | +5.0V       | Analog positive power supply                                                                                                                                                                                                            |

# **Functional Description**

# **Input Formats**

Control Registers for this section

| Address | Bit(s) | Name   |

|---------|--------|--------|

| 0x05    | 7      | D1OFF  |

| 0x05    | 6-4    | INMODE |

| 0x06    | 0      | TSOUT  |

The TMC2192 supports YCBCR component sources on the pixel data port. YCBCR input sources are supported in 10 bit 4:2:2, 20 bit 4:2:2, 20 bit 4:4:4, and 24 bit 4:4:4. In the 4:2:2 cases the color difference components are linearly interpolated to 4:4:4 internally.

Demuxing of multiplexed data streams depends on which synchronization mode the encoder is operating in. For slave and genlock modes the falling edge of  $\overline{HSIN}$  must be LOW prior to the CB data in order to demux the data correctly. For master mode synchronization the falling edge of  $\overline{HSOUT}$  must be LOW prior to the Y data in order to demux the data correctly. Finally, in 656 mode the demuxing of the data stream is determined by the TRS codes, the first sample after the TRS is considered a CB sample of the CB Y CR YI packet.

The control register D1OFF controls the formatting of the incoming luminance data at the pixel data port. When D1OFF is HIGH a blanking level of 64<sub>10</sub> is subtracted from the luminance and when D1OFF is LOW the incoming the pixel data is passed through. The inversion of the MSB's on the CB and CR components is controlled by the INMODE control register.

| INMODE | 23 |                |                   |   | 16 | 15 |   | PD  |  | 9 | 8 | 7 |   |   | 0 |

|--------|----|----------------|-------------------|---|----|----|---|-----|--|---|---|---|---|---|---|

| 00     | 7  | C <sub>B</sub> |                   |   | 0  | 7  |   | C R |  |   | 0 | 7 | Υ |   | 0 |

| 01     | 9  |                | YC BC             | R |    |    | 0 |     |  |   |   |   |   |   |   |

| 1x     | 9  |                | YC <sub>B</sub> C | R |    |    | 0 |     |  | 1 | 0 | 9 |   | Y | 2 |

Figure 1. Input Formats

2192002A

#### 1. INMODE = 00, PD[7:0] = PD[23:16] = CB, PD[15:8] = CR

Figure 2. 24 Bit Input Format

## 2. INMODE = 01, PD[23:14] = YCBCR running at 27MHz.

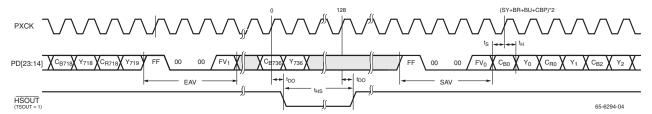

The PD port is clocked at twice the pixel rate, with the data organized as C<sub>B</sub> Y C<sub>R</sub> Y, with the cosited Y's following the C<sub>B</sub>'s. In its CCIR-656 time base mode, the demuxed C<sub>B</sub>, Y, and C<sub>R</sub> data is synchronized to the SAV preamble. The first

data value, after the SAV preamble, is treated as a CB data point in the multiplexed CB, Y, CR Y, D1 data stream.

Note: Figure 3, pixel numbering, reflects the SMPTE-125M pixel numbering.

Figure 3. CCIR656 Input Format

Figure 4. 10 bit Input Format

# 3. INMODE = 11, PD[9:0] = Y, PD[23:14] = $C_B/C_R$

Figure 5. 20 bit 4:2:2 Input Format

# 4. INMODE = 10, PD[9:0] = Y at PCK, PD[23:14] = CB-CR at PXCK

Figure 6. 20 bit 4:4:4 Input Format

# **Color Space Matrix**

Control Registers for this section

| Address | Bit(s) | Name  |

|---------|--------|-------|

| 0x30    | 7-0    | MCF1L |

| 0x33    | 7-0    | MCF2L |

| 0x35    | 7-0    | MCF3L |

| 0x3A    | 7-4    | MCF1M |

| 0x3B    | 2-0    | MCF2M |

| 0x3C    | 2-0    | MCF3M |

# Matrix configuration:

$Y_{composite}$  = MCF1 \* Yin U = MCF2 \* CB V = MCF3 \* CR

The color space matrix consists of 3 multipliers with independently adjustable coefficients, and a resolution of 0.00049 (1/2048). The amount of gain varies among coefficients, Table 1 summarizes the gain for each coefficient.

**Table 1. CSM Coefficient Range**

| Coefficient | Gain Range | Comment             |

|-------------|------------|---------------------|

| MCF1        | 0 to 2     |                     |

| MCF2        | 0 to 1     | 11 bit coefficient. |

| MCF3        | 0 to 1     | 11 bit coefficient. |

To aid in the programming of the color space matrix Table 2 provides a set of default input and output values for 100% color bars. The component values given will be after the pre-

processing block and prior to the sync and pedestal insertion. The blank, pedestal, and sync values are given as a reference. Table 4 gives the default coefficients values for the CSM.

Table 2. Expected Output Values for the CSM with YCBCR Inputs

|          |     | Inputs |      | ;   | 5:2 Output | s    | 7:3 Outputs |      |      |  |

|----------|-----|--------|------|-----|------------|------|-------------|------|------|--|

| Color    | Υ   | Св     | CR   | Υ   | U          | V    | Υ           | U    | V    |  |

| White    | 876 | 0      | 0    | 536 | 0          | 0    | 568         | 0    | 0    |  |

| Yellow   | 776 | -448   | 73   | 475 | -235       | 54   | 503         | -249 | 57   |  |

| Cyan     | 614 | 151    | 448  | 376 | 79         | -332 | 407         | 84   | -351 |  |

| Green    | 514 | -297   | -375 | 315 | -156       | -278 | 340         | -165 | -294 |  |

| Magenta  | 362 | 297    | 375  | 222 | 156        | 278  | 240         | 165  | 294  |  |

| Red      | 262 | -151   | 448  | 160 | -79        | 332  | 173         | -84  | 351  |  |

| Blue     | 100 | 448    | -73  | 61  | 235        | -54  | 66          | 249  | -57  |  |

| Black    | 0   | 0      | 0    | 0   | 0          | 0    | 0           | 0    | 0    |  |

| Blank    | 64  |        |      | 240 |            |      | 256         |      |      |  |

| Pedestal |     |        |      | 44  |            |      | 0           |      |      |  |

| Sync     |     |        |      | 8   |            |      | 12          |      |      |  |

## **Synchronization Modes**

Control Registers for this section

| Address | Bit(s) | Name  |

|---------|--------|-------|

| 0x06    | 5-3    | MODE  |

| 0x06    | 1      | TOUT  |

| 0x06    | 0      | TSOUT |

The TMC2192 offers a variety of synchronization modes; these are master, slave, genlock, 656 mode, and DRS-Lock. In master mode, the TMC2192 generates its own timing and the synchronization is supplied externally by  $\overline{\mbox{HSOUT}}$  and  $\overline{\mbox{VSOUT}}$  signals. In slave and genlock modes the TMC2192 derives its timing from the input pins  $\overline{\mbox{HSIN}}$ ,  $\overline{\mbox{VSIN}}$ . In 656 mode the timing is driven by the synchronization codes embedded into the data stream.

#### Master

The TMC2192 drives the output pins  $\overline{\text{HSOUT}}$  and  $\overline{\text{VSOUT}}$  to synchronize the incoming video. A new color frame starts at the rising edge of  $\overline{\text{RESET}}$ . The encoder always starts at the 1st vertical serration in field 8 and will freerun the field and line sequence. The control register bit  $\overline{\text{SRESET}}$  can be used to synchronize the start of the field and line sequence in master mode by resetting the FVHGEN state machine. Output synchronization signal  $\overline{\text{VSOUT}}$  can operate in a traditional sync mode or in a MPEG style field toggle mode.

#### Slave

The TMC2192 is driven by the input synchronization pins  $\overline{\text{HSIN}}$  and  $\overline{\text{VSIN}}$ . When the falling edge of  $\overline{\text{HSIN}}$  and  $\overline{\text{VSIN}}$  occurs at the same rising edge of PXCK the TMC2192 will start a new field.  $\overline{\text{VSIN}}$  can be either a traditional pulse or the MPEG style field toggle. In both cases the TMC2192 will flywheel through fields 2, 4, 6, and 8 synchronizing only to fields 1, 3, 5, and 7.

#### CCIR656

The TMC2192 derives all synchronization from the embedded TRS (timing reference signals) information. Blanking of selected lines is determined by the v bit of the TRS. However the control registers VBIENx can override and blank the active video portion of VBI lines regardless of the state of the v-bit.

#### Genlock

The TMC2192 is driven by the input synchronization pins  $\overline{\text{HSIN}}$  and  $\overline{\text{VSIN}}$ . When the falling edge of  $\overline{\text{HSIN}}$  and  $\overline{\text{VSIN}}$  occurs at the same rising edge of PXCK the TMC2192 will start a new field.  $\overline{\text{VSIN}}$  can be either a traditional pulse or the MPEG style field toggle. In both cases the TMC2192 will flywheel through fields 2, 4, 6, and 8 synchronizing only to fields 1, 3, 5, and 7. The TMC2192 collects GRS data and resets its subcarrier phase and frequency to the data embedded in the GRS stream. The GRS detection occurs only on the CBVS port.

#### **DRS**

The TMC2192 is driven by the input synchronization pins  $\overline{\text{HSIN}}$  and  $\overline{\text{VSIN}}$ . When the falling edge of  $\overline{\text{HSIN}}$  and  $\overline{\text{VSIN}}$  occurs at the same rising edge of PXCK the TMC2192 will start a new field.  $\overline{\text{VSIN}}$  can be either a traditional pulse or the MPEG style field toggle. In both cases the TMC2192 will flywheel through fields 2, 4, 6, and 8 synchronizing only to fields 1, 3, 5, and 7. Subcarrier phase adjustment is determined by the DRS data. The DRS detection can occur on either the CBVS port or the pixel data port.

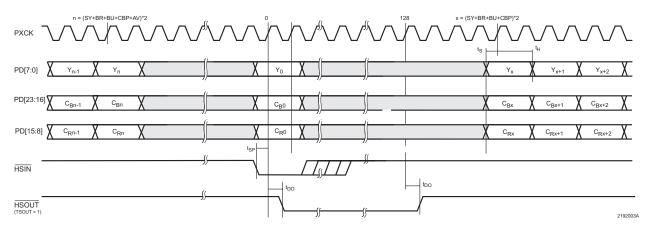

#### **Propagation Delay**

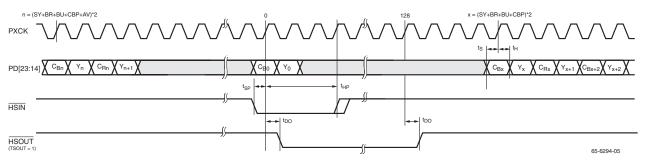

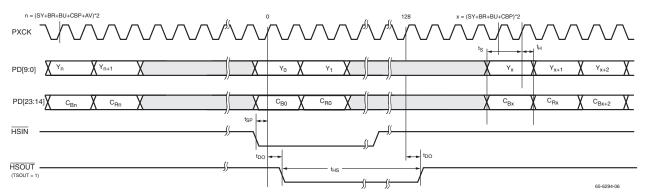

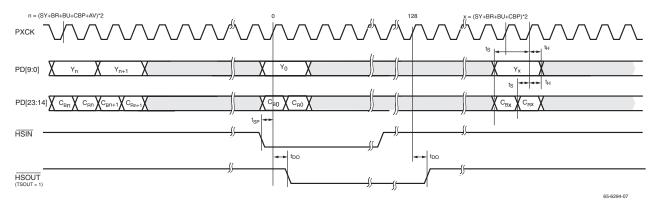

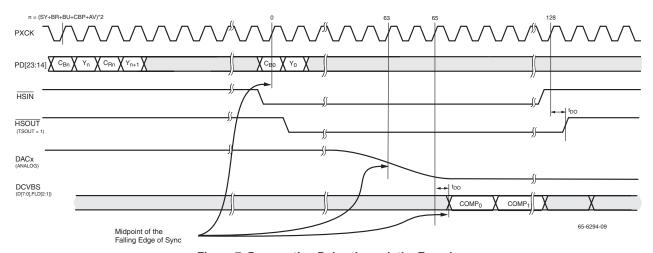

The propagation delay from the pixel data (PD) input to the D/A output is 64 PXCK's. Figure 8 shows the propagation delay for both master and slave synchronization modes. For CCIR656 data streams, pixel 736 (pixel 0 in Figure 8) is the midpoint of sync and is 32 PXCK's (24 PXCK's in PAL) after the EAV TRS.

Figure 7. Propagation Delay through the Encoder

# **Blanking Control**

Control Registers for this section

| Address | Bit(s) | Name    |

|---------|--------|---------|

| 0x04    | 1-0    | PDRM    |

| 0x06    | 2      | PDCDIR  |

| 0x18    | 4-0    | VBIENF1 |

| 0x19    | 4-0    | VBIENF2 |

| 0x1F    | 7-0    | PDCCNT  |

The content of VBIENFx[4:0] selects the first line to contain an active video region in each field, all subsequent lines for the remainder of the field are active. To blank an entire field, the user zeroes the VBIENFx[4:0] control register. In CCIR656 slave mode, the user can selectively blank any enabled line by setting its TRS V bit HIGH. For 525-line systems, NTSC line numbering is employed, with the first vertical serration starting on line 4. PAL line numbering is used with 625-line systems, with each field's line 1 being the start of the first vertical serration.

Any line(s) enabled by the closed caption control are automatically unblanked for the closed caption waveform, irrespective of the corresponding values of VBIENF.

#### **Pixel Data Control**

The pixel data control has two modes of operation, as an input or as an output. The mode of operation is determined by the PDCDIR control register. When PDC is an input the internally generated PDC is ANDed with the PDC pin. This allows the user to blank any active video regions. When PDC is an output, the internally generated PDC is the output for the PDC pin.

The internal PDC control will toggle to a logic HIGH at the pixel specified by PDCNT and toggle to a logic LOW four pixels prior to the end of the active video region. The starting point and ending point of the active video region (VA) are determined by the control registers 10h to 1Fh. When PDC is used as an input, the sloped edge of the active video region will occur on the next four pixels following the toggle point.

# **Edge Shaping**

The TMC2192 has three modes of sloped edges on the active video region and are controlled by PDRM control register.

**Table 3. PDC Edge Control**

| PDRM[1:0] | Slope type at PDC (HIGH)                                                                                                                                   | Slope type at PDC (LOW)                                                                                                                                   |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00        | The following four pixels have the weighting of 1/8, 1/2, 7/8 and 1 for NTSC and 1/8, 3/8, 5/8, and 7/8 for PAL.                                           | The following four pixels have the weighting of 1, 7/8, 1/2, and 1/8 for NTSC and 7/8, 5/8, 3/8, and 1/8 for PAL.                                         |

| 01        | The fifth pixel is sampled and scaled 1/8, 1/2, 7/8 and 1 over the next four pixels for NTSC and 1/8, 3/8, 5/8, and 7/8 over the next four pixels for PAL. | The fifth pixel s sampled and scaled 1, 7/8, 1/2 and 1/8 over the next four pixels for NTSC and 7/8, 5/8, 3/8, and 1/8 over the next four pixels for PAL. |

| 1x        | Slope is off, edge control is dictated by the PD stream from active video start                                                                            | Slope is off, edge control is dictated by the PD stream to active video end                                                                               |

# **Horizontal Programming**

Control registers for this section

| Address | Bit(s) | Name        |  |  |  |  |  |

|---------|--------|-------------|--|--|--|--|--|

| 0x06    | 7-6    | FORMAT      |  |  |  |  |  |

| 0x19    | 7      | SHORT       |  |  |  |  |  |

| 0x19    | 6      | T512        |  |  |  |  |  |

| 0x19    | 5      | HALFEN      |  |  |  |  |  |

| 0x20    | 7-0    | SY          |  |  |  |  |  |

| 0x21    | 7-0    | BR          |  |  |  |  |  |

| 0x22    | 7-0    | BU          |  |  |  |  |  |

| 0x23    | 7-0    | CBP         |  |  |  |  |  |

| 0x24    | 7-0    | XBP         |  |  |  |  |  |

| 0x25    | 7-0    | VA          |  |  |  |  |  |

| 0x26    | 7-0    | VC          |  |  |  |  |  |

| 0x27    | 7-0    | VB          |  |  |  |  |  |

| 0x28    | 7-0    | EL          |  |  |  |  |  |

| 0x29    | 7-0    | EH          |  |  |  |  |  |

| 0x2A    | 7-0    | SL          |  |  |  |  |  |

| 0x2B    | 7-0    | SH          |  |  |  |  |  |

| 0x2C    | 7-0    | FP          |  |  |  |  |  |

| 0x2D    | 7-6    | XBP (MSB's) |  |  |  |  |  |

| 0x2D    | 5-4    | VA (MSB's)  |  |  |  |  |  |

| 0x2D    | 3-2    | VB (MSB's)  |  |  |  |  |  |

| 0x2D    | 1-0    | VC (MSB's)  |  |  |  |  |  |

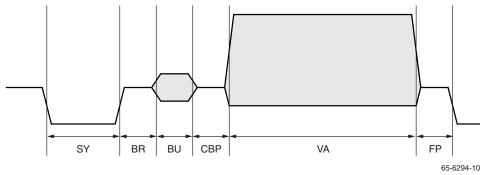

Horizontal interval timing is fully programmable and is established by loading the timing registers with the duration of each horizontal element. The duration is expressed in PCK clock cycles. In this way, any pixel clock rate between 10 MHz and 15 MHz can be accommodated, and any desired standard or non-standard horizontal video timing may be produced.

Horizontal timing parameters can be calculated as follows:

t = N x (PCK period)

= N x (2 x PXCK period)

where N is the value loaded into the appropriate timing register, and PCK is the pixel clock period.

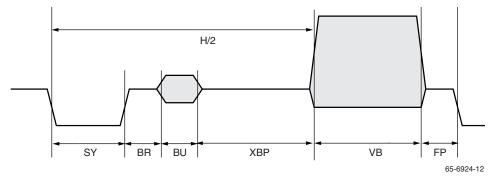

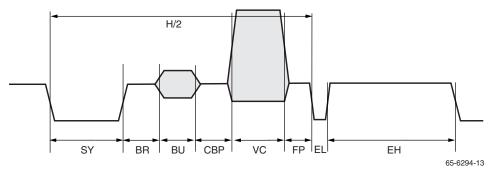

When programming horizontal timing, subtract 5 PCK periods from the calculated values of CBP and add 5 PCK periods to the calculated value for VA. The control register HALFEN enables the 1<sup>st</sup> half line (UBV) on line 283 for NTSC, PAL-M and line 23 for all other PAL standards when it is LOW.

**Table 4. Horizontal Line Equations**

| Line Type | Line ID | Line Length Equals                     |

|-----------|---------|----------------------------------------|

| EE        | 00      | EL + EH + EL + EH                      |

| SE        | 02      | SL + SH + EL + EH                      |

| SS        | 03      | SL + SH + SL + SH                      |

| ES        | 01      | EL + EH + SL + SH                      |

| EB        | 10      | EL + EH + EL + EH                      |

| UBB, -BB  | 0D, 05  | SY + BR + BU + CBP + VA + FP           |

| UVV, -VV  | 0F, 07  | SY + BR + BU + CBP + VA + FP           |

| UVE, -VE  | 0C, 04  | SY + BR + BU + CBP + VC + FP + EL + EH |

| UBV       | 0E      | SY + BR + BU + XBP + VB + FP           |

Figure 8. Horizontal Timing

**Table 5. Horizontal Timing Specifications**

| Parameter | NTSC-M<br>(μs) | PAL-I<br>(μs) | PAL-M<br>(μs) |  |  |

|-----------|----------------|---------------|---------------|--|--|

| FP        | 1.5            | 1.65          | 1.9           |  |  |

| SY        | 4.7            | 4.7           | 4.95          |  |  |

| BR        | 0.6            | 0.9           | 0.9           |  |  |

| BU        | 2.5            | 2.25          | 2.25          |  |  |

| CBP       | 1.6            | 2.55          | 1.8           |  |  |

| VA        | 52.6556        | 51.95         | 51.692        |  |  |

| Н         | 63.5556        | 64.0          | 63.492        |  |  |

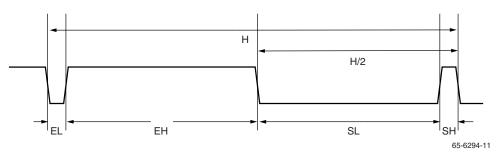

Vertical interval timing is also fully programmable, and is established by loading the timing registers with the duration's of each vertical timing element, the duration expressed in PCK clock cycles. In this way as with horizontal program-

ming, any pixel rate between 10 and 15 Mpps can be accommodated, and any desired standard or non-standard vertical video timing may be produced.

Like horizontal timing parameters, vertical timing parameters are calculated as follows:

where N is the value loaded into the appropriate timing register, and PCK is the pixel clock period.

The vertical interval comprises several different line types based upon H, the Horizontal line time.

$$H = (2 \times SL) + (2 \times SH)$$

[Vertical sync pulses]

=  $(2 \times EL) + (2 \times EH)$  [Equalization pulses]

Figure 9. Horizontal Timing - Vertical Blanking

The VB and VC control registers are added to produce the half-lines needed in the vertical interval at the beginning and end of some fields. These must properly mate with components of the normal lines.

Figure 10. Horizontal Timing – 1st Half-line

Figure 11. Horizontal Timing – 2nd Half-line

**Table 6. Vertical Interval Timing Specifications**

| Parameter | NTSC-M<br>(μs) | PAL-I<br>(μs) | PAL-M<br>(μs) |  |  |

|-----------|----------------|---------------|---------------|--|--|

| Н         | 63.5556        | 64            | 63.492        |  |  |

| EH        | 29.4778        | 29.65         | 29.45         |  |  |

| EL        | 2.3            | 2.35          | 2.3           |  |  |

| SH        | 4.7            | 4.7           | 4.65          |  |  |

| SL        | 27.1           | 27.3          | 27.1          |  |  |

**Table 7. Default Horizontal Timing Parameters**

|                 |               |                  |               |               |    |    |    |     |     | Т  | iming | Regist | er (he | x)              |                 |    |    |      |     |

|-----------------|---------------|------------------|---------------|---------------|----|----|----|-----|-----|----|-------|--------|--------|-----------------|-----------------|----|----|------|-----|

|                 | Field<br>Rate | Horizontal Freg. | Pixel<br>Rate | PXCK<br>Freq. | SY | BR | BU | СВР | XBP | VA | vc    | VB     | EL     | EH <sup>2</sup> | SL <sup>2</sup> | SH | FP | Note | CBL |

| Standard        | (Hz)          | (KHz)            | (Mpps)        | (MHz)         | 20 | 21 | 22 | 23  | 24  | 25 | 26    | 27     | 28     | 29              | 2A              | 2B | 2C | 2D   | 2F  |

| NTSC sqr. pixel | 59.94         | 15.734266        | 12.27         | 24.54         | ЗА | 07 | 1F | 0F  | 23  | 8B | 05    | 77     | 1C     | 6A              | 4C              | ЗА | 12 | 65   | 52  |

| NTSC CCIR-601   | 59.94         | 15.734266        | 13.50         | 27.00         | 40 | 08 | 22 | 11  | 44  | СВ | 1E    | 98     | 1F     | 8E              | 6D              | 40 | 14 | 65   | 59  |

| NTSC 4x FSC     | 59.94         | 15.734266        | 14.32         | 28.64         | 43 | 09 | 24 | 12  | 54  | F7 | 30    | B5     | 21     | A6              | 84              | 43 | 15 | 65   | 5F  |

| PAL sqr. pixel  | 50.00         | 15.625000        | 14.75         | 29.50         | 45 | 0D | 21 | 21  | 6D  | 03 | 2B    | B7     | 23     | B5              | 93              | 45 | 19 | 75   | 61  |

| PAL CCIR-601    | 50.00         | 15.625000        | 13.50         | 27.00         | 40 | 0C | 1E | 22  | 4D  | BE | 0E    | 93     | 20     | 90              | 70              | 40 | 16 | 65   | 59  |

| PAL 15 Mpps     | 50.00         | 15.625000        | 15.00         | 30.00         | 46 | 0D | 22 | 21  | 73  | 11 | 31    | BF     | 23     | BD              | 9A              | 47 | 19 | 75   | 62  |

| PAL-M sqr.pixel | 60.00         | 15.750000        | 12.50         | 25.01         | 3E | 0B | 1C | 13  | 26  | 86 | FE    | 8B     | 1D     | 70              | 53              | ЗА | 18 | 61   | 52  |

| PAL-M CCIR-601  | 60.00         | 15,750000        | 13.50         | 27.00         | 44 | 0C | 1E | 13  | 26  | Bf | 12    | 99     | 1F     | 8E              | 6E              | 3F | 1A | 65   | 57  |

| PAL-M 4x FSC    | 60.00         | 15,750000        | 14.30         | 28.60         | 47 | 0D | 20 | 15  | 4C  | E8 | 22    | AC     | 21     | A5              | 84              | 42 | 1B | 65   | 5D  |

#### Notes:

- 1. XBP, VA, VC, and VB are 10 bit values. The 2 MSBs for these four variables are in Timing Register 2D.

- 2. EH and SL are 9 bit values. A most significant "1" is forced by the TMC2192 since EH and SL must range from 256 to 511. EH and SL may be extended to 767. Only the eight LSBs are stored in Timing Registers 29 and 2A.

- 3. Every calculated timing parameter has a minimum value of 5 except EH and SL which have minimum values of 256.

# **Vertical Timing**

The vertical timing is controlled by the FORMAT control register, which dictates the field and line sequence.

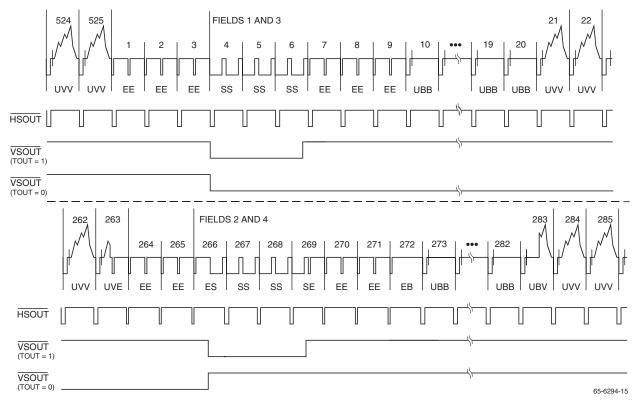

Figure 12. NTSC Vertical Interval

Table 8. NTSC Field/Line Sequence and Identification

| FIE  | Field 1<br>LD ID = 2 | x00   | FIE  | Field 2<br>FIELD ID = x01 |       |      | Field 3<br>LD ID = 3 | x10   | Field 4<br>FIELD ID = x11 |     |       |

|------|----------------------|-------|------|---------------------------|-------|------|----------------------|-------|---------------------------|-----|-------|

| Line | ID                   | LTYPE | Line | ID                        | LTYPE | Line | ID                   | LTYPE | Line                      | ID  | LTYPE |

| 4    | SS                   | 03    | 266  | ES                        | 01    | 4    | SS                   | 03    | 266                       | ES  | 01    |

| 5    | SS                   | 03    | 267  | SS                        | 03    | 5    | SS                   | 03    | 267                       | SS  | 03    |

| 6    | SS                   | 03    | 268  | SS                        | 03    | 6    | SS                   | 03    | 268                       | SS  | 03    |

| 7    | EE                   | 00    | 269  | SE                        | 02    | 7    | EE                   | 00    | 269                       | SE  | 02    |

| 8    | EE                   | 00    | 270  | EE                        | 00    | 8    | EE                   | 00    | 270                       | EE  | 00    |

| 9    | EE                   | 00    | 271  | EE                        | 00    | 9    | EE                   | 00    | 271                       | EE  | 00    |

| 10   | UBB                  | 0D    | 272  | EB                        | 10    | 10   | UBB                  | 0D    | 272                       | EB  | 10    |

|      | UBB                  | 0D    | 273  | UBB                       | 0D    |      | UBB                  | 0D    | 273                       | UBB | 0D    |

| 19   | UBB                  | 0D    |      | UBB                       | 0D    | 19   | UBB                  | 0D    |                           | UBB | 0D    |

| 20   | UBB                  | 0D    | 282  | UBB                       | 0D    | 20   | UBB                  | 0D    | 282                       | UBB | 0D    |

| 21   | UVV                  | 0F    | 283  | UBV                       | 0E    | 21   | UVV                  | 0F    | 283                       | UBV | 0E    |

| 22   | UVV                  | 0F    | 284  | UVV                       | 0F    | 22   | UVV                  | 0F    | 284                       | UVV | 0F    |

|      | UVV                  | 0F    |      | UVV                       | 0F    |      | UVV                  | 0F    |                           | UVV | 0F    |

| 262  | UVV                  | 0F    | 524  | UVV                       | 0F    | 262  | UVV                  | 0F    | 524                       | UVV | 0F.   |

| 263  | UVE                  | 0C    | 525  | UVV                       | 0F    | 263  | UVE                  | 0C    | 525                       | UVV | 0F    |

| 264  | EE                   | 00    | 1    | EE                        | 00    | 264  | EE                   | 00    | 1                         | EE  | 00    |

| 265  | EE                   | 00    | 2    | EE                        | 00    | 265  | EE                   | 00    | 2                         | EE  | 00    |

|      |                      |       | 3    | EE                        | 00    |      |                      |       | 3                         | EE  | 00    |

EE Equalization pulse

SE Half-line vertical sync pulse, half-line equalization pulse

SS Vertical sync pulse

ES Half-line equalization pulse, half-line vertical sync pulse

EB Equalization broad pulse

UBB Black burst UVV Active video

UVE Half-line video, half-line equalization pulse

UBV half-line black, half-line video

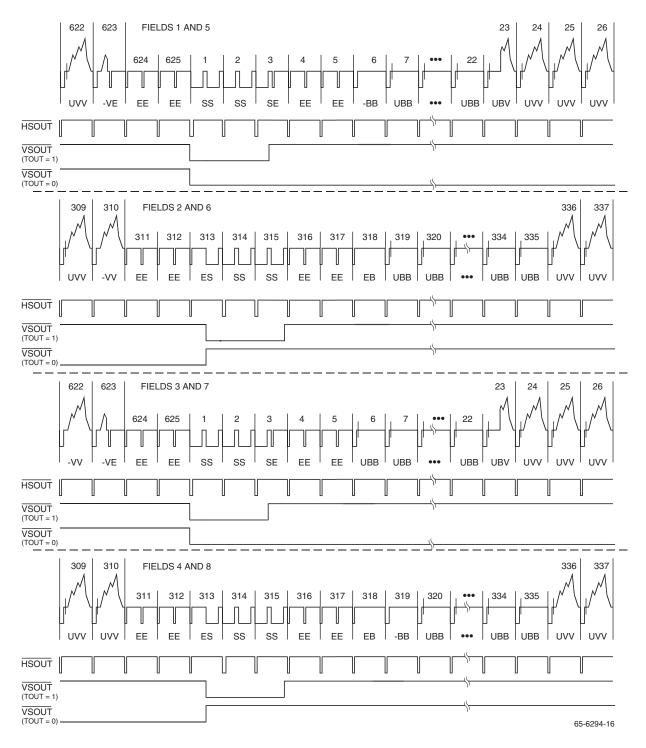

Figure 13. PAL Vertical Interval

Table 9. PAL Field/Line Sequence and Identification

|      | Field 1 & 9<br>D ID = 000 |       |      |     |       | Field 3 & 7<br>FIELD ID = 010, 110 |     |       | Field 4 & 8<br>FIELD ID = 011, 111 |     |       |

|------|---------------------------|-------|------|-----|-------|------------------------------------|-----|-------|------------------------------------|-----|-------|

| Line | ID                        | LTYPE | Line | ID  | LTYPE | Line                               | ID  | LTYPE | Line                               | ID  | LTYPE |

| 1    | SS                        | 03    | 313  | ES  | 01    | 1                                  | SS  | 03    | 313                                | ES  | 01    |

| 2    | SS                        | 03    | 314  | SS  | 03    | 2                                  | SS  | 03    | 314                                | SS  | 03    |

| 3    | SE                        | 02    | 315  | SS  | 03    | 3                                  | SE  | 02    | 315                                | SS  | 03    |

| 4    | EE                        | 00    | 316  | EE  | 00    | 4                                  | EE  | 00    | 316                                | EE  | 00    |

| 5    | EE                        | 00    | 317  | EE  | 00    | 5                                  | EE  | 00    | 317                                | EE  | 00    |

| 6    | -BB                       | 05    | 318  | EB  | 10    | 6                                  | UBB | 0D    | 318                                | EB  | 10    |

| 7    | UBB                       | 0D    | 319  | UBB | 0D    | 7                                  | UBB | 0D    | 319                                | -BB | 05    |

|      | UBB                       | 0D    | 320  | UBB | 0D    |                                    | UBB | 0D    | 320                                | UBB | 0D    |

| 22   | UBB                       | 0D    |      | UBB | 0D    | 22                                 | UBB | 0D    |                                    | UBB | 0D    |

| 23   | UBV                       | 0E    | 334  | UBB | 0D    | 23                                 | UBV | 0E    | 334                                | UBB | 0D    |

| 24   | UVV                       | 0F    | 335  | UBB | 0D    | 24                                 | UVV | 0F    | 335                                | UVV | 0F.   |

| 25   | UVV                       | 0F    | 336  | UVV | 0F    | 25                                 | UVV | 0F    | 336                                | UVV | 0F    |

| 26   | UVV                       | 0F    | 337  | UVV | 0F    | 26                                 | UVV | 0F    | 337                                | UVV | 0F    |

|      | UVV                       | 0F    |      | UVV | 0F    |                                    | UVV | 0F    |                                    | UVV | 0F    |

| 309  | UVV                       | 0F    | 622  | -VV | 07    | 309                                | UVV | 0F    | 622                                | UVV | 0F    |

| 310  | -VV                       | 07    | 623  | -VE | 04    | 310                                | UVV | 0F    | 623                                | -VE | 04    |

| 311  | EE                        | 00    | 624  | EE  | 00    | 311                                | EE  | 00    | 624                                | EE  | 00    |

| 312  | EE                        | 00    | 625  | EE  | 00    | 312                                | EE  | 00    | 625                                | EE  | 00    |

EE Equalization pulse

SE Half-line vertical sync pulse, half-line equalization pulse

SS Vertical sync pulse

ES Half-line equalization pulse, half-line vertical sync pulse

EB Equalization broad pulse

UBB Black burst

-BB Black burst with color burst suppressed

UVV Active video

-VV Active video with color burst suppressed UVE Half-line video, half-line equalization pulse

-VE Half-line video, half-line equalization pulse, color burst suppressed.

UBV half-line black, half-line video

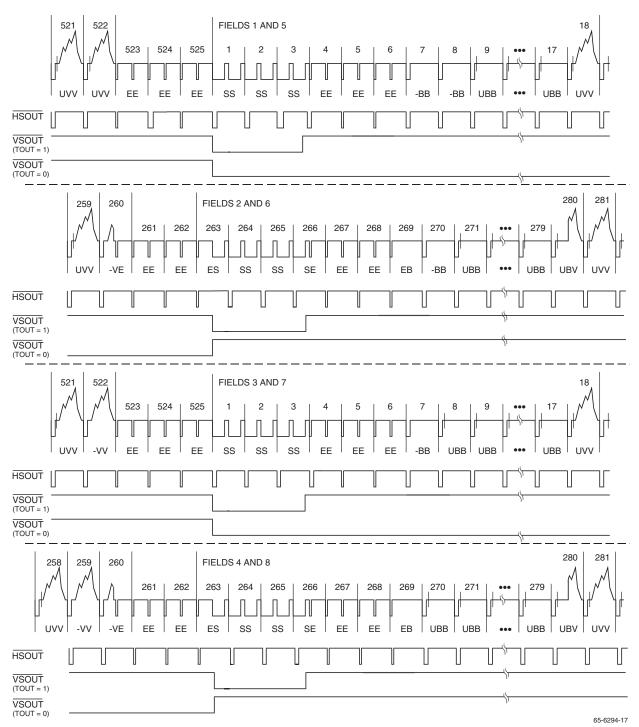

Figure 14. PAL-M Vertical Interval

Table 10. PAL-M Field/Line Sequence and Identification

|      | ield 1 & :<br>D ID = 000 |       | Field 2 & 6<br>FIELD ID = 001, 111 |     |       |      | ield 3 &<br>D ID = 01 |       | Field 4 & 8<br>FIELD ID = 011, 111 |     |       |

|------|--------------------------|-------|------------------------------------|-----|-------|------|-----------------------|-------|------------------------------------|-----|-------|

| Line | ID                       | LTYPE | Line                               | ID  | LTYPE | Line | ID                    | LTYPE | Line                               | ID  | LTYPE |

| 1    | SS                       | 03    | 263                                | ES  | 01    | 1    | SS                    | 03    | 263                                | ES  | 01    |

| 2    | SS                       | 03    | 264                                | SS  | 03    | 2    | SS                    | 03    | 264                                | SS  | 03    |

| 3    | SS                       | 03    | 265                                | SS  | 03    | 3    | SS                    | 03    | 265                                | SS  | 03    |

| 4    | EE                       | 00    | 266                                | SE  | 02    | 4    | EE                    | 00    | 266                                | SE  | 02    |

| 5    | EE                       | 00    | 267                                | EE  | 00    | 5    | EE                    | 00    | 267                                | EE  | 00    |

| 6    | EE                       | 00    | 268                                | EE  | 00    | 6    | EE                    | 00    | 268                                | EE  | 00    |

| 7    | -BB                      | 05    | 269                                | EB  | 10    | 7    | -BB                   | 05    | 269                                | EB  | 10    |

| 8    | -BB                      | 05    | 270                                | -BB | 05    | 8    | UBB                   | 05    | 270                                | UBB | 05    |

| 9    | UBB                      | 0D    | 271                                | UBB | 1D    | 9    | UBB                   | 0D    | 271                                | UBB | 1D    |

|      |                          |       |                                    |     |       |      |                       |       |                                    |     |       |

| 17   | UBB                      | 0D    | 279                                | UBB | 0D    | 17   | UBB                   | 0D    | 279                                | UBB | 0D    |

| 18   | UVV                      | 0F    | 280                                | UBV | 0E.   | 18   | UVV                   | 0F    | 280                                | UBV | 0E.   |

|      |                          |       | 281                                | UVV | 0F    |      | UVV                   | 0F    | 281                                | UVV | 0F    |

| 259  | UVV                      | 0F    |                                    |     |       | 258  | UVV                   | 0F    |                                    |     |       |

| 260  | -VE                      | 04    | 521                                | UVV | 0F    | 259  | -VV                   | 07    | 521                                | UVV | 0F    |

| 261  | EE                       | 00    | 522                                | -VV | 07    | 260  | -VE                   | 04    | 522                                | UVV | 0F    |

| 262  | EE                       | 00    | 523                                | EE  | 00.   | 261  | EE                    | 00    | 523                                | EE  | 00    |

|      |                          |       | 524                                | EE  | 00    | 262  | EE                    | 00    | 524                                | EE  | 00    |

|      |                          |       | 525                                | EE  | 00    |      |                       |       | 525                                | EE  | 00    |

EE Equalization pulse

SE Half-line vertical sync pulse, half-line equalization pulse

SS Vertical sync pulse

ES Half-line equalization pulse, half-line vertical sync pulse

EB Equalization broad pulse

UBB Black burst

-BB Black burst with color burst suppressed

UVV Active video

-VV Active video with color burst suppressed UVE Half-line video, half-line equalization pulse

-VE Half-line video, half-line equalization pulse, color burst suppressed.

UBV half-line black, half-line video

#### **Chrominance Processor**

Control registers for this section:

| Address | Bit(s) | Name      |

|---------|--------|-----------|

| 0x06    | 7-6    | FORMAT    |

| 0x06    | 5-3    | MODE      |

| 0x07    | 5      | DDSRST    |

| 0x11    | 7      | DRSSEL    |

| 0x18    | 6      | GLKCTL1   |

| 0x18    | 5      | GLKCTL0   |

| 0x3F    | 3      | GAUSS_BYP |

| 0x40    | 7-0    | FREQL     |

| 0x41    | 7-0    | FREQ3     |

| 0x42    | 7-0    | FREQ2     |

| 0x43    | 7-0    | FREQM     |

| 0x44    | 7-4    | SYSPHL    |

| 0x45    | 3-0    | SYSPHM    |

| 0x46    | 7-4    | BURPHL    |

| 0x47    | 3-0    | BURPHM    |

| 0x48    | 7-4    | BRSTFULL  |

| 0x49    | 3-0    | BRST1     |

| 0x4A    | 7-4    | BRST2     |

#### **Subcarrier Programming**

The color subcarrier is produced by an internal 32 bit digital frequency synthesizer which is completely programmable in frequency and phase. Separate registers, FREQx, SYSPHx, BSTPHx, are provided for phase adjustment of the color burst and of the active video, permitting external delay compensation, color adjustment, etc. FREQx is the subcarrier phase step per pixel and SYSPHx is phase offset at field 1, line 1 (line 4 for NTSC), pixel 1.

#### **NTSC Subcarrier**

For NTSC encoding, the subcarrier synthesizer frequency has a simple relationship to the pixel clock period, repeating over 2 lines: The decimal value for the subcarrier phase step is:

$$FREQx = \frac{455/2}{pixels/line} \times 2^{32}$$

Where the number of pixels/line is:

$$pixels/line = \frac{PXCK Frequency}{H Period}$$

This value must be converted to binary and split into four 8 bit registers, FREOM, FREO2, FREO3, and FREOL.

#### **PAL Subcarrier**

The PAL relationship is more complex, repeating only once in 8 fields (the well-known 25 Hz offset):

FREQx =

$$\frac{(1135/4) + (1/625)}{\text{pixels/line}} \times 2^{32}$$

This value must be converted to binary and split as described previously for NTSC. The number of pixels/line is found as in NTSC.

#### **PAL-M Subcarrier**

$$FREQ = \frac{909/4}{pixels/line} \times 2^{32}$$

SYSPHx establishes the appropriate phase relationship between the internal synthesizer and the chroma modulator. The nominal value for SYSPHx is zero.

Other values for SYSPHx must be converted to binary and split into two 8 bit registers, SYSPHM and SYSPHL.

Burst Phase (BURPHx) sets up the correct relative NTSC modulation angle. The value for BURPH is:

BURPHx = SYSPHx

This value must be converted to binary and split into two 8 bit registers, BURPHM and BURPHL.

Table 11. Standard Subcarrier Parameters

|                 |               |                     |               |               |                     | Subcarrier Register (hex) |        |        |        |       |       |       |       |

|-----------------|---------------|---------------------|---------------|---------------|---------------------|---------------------------|--------|--------|--------|-------|-------|-------|-------|

|                 | Field<br>Rate | Horizontal<br>Freq. | Pixel<br>Rate | PXCK<br>Freq. | Subcarrier<br>Freq. | BURPHM                    | BURPHL | SYSPHM | SYSPHL | FREQM | FREQ2 | FREQ3 | FREQL |

| Standard        | (Hz)          | (kHz)               | (Mpps)        | (MHz)         | (MHz)               | 47                        | 46     | 45     | 44     | 43    | 42    | 41    | 40    |

| NTSC sqr. pixel | 59.94         | 15.734266           | 12.27         | 24.54         | 3.57954500          | 00                        | 00     | 00     | 00     | 4A    | AA    | AA    | AB    |

| NTSC CCIR-601   | 59.94         | 15.734266           | 13.50         | 27.00         | 3.57954500          | 00                        | 00     | 00     | 00     | 43    | E0    | F8    | 3E    |

| NTSC 4x FSC     | 59.94         | 15.734266           | 14.32         | 28.64         | 3.57954500          | 00                        | 00     | 00     | 00     | 40    | 00    | 00    | 00    |

| PAL sqr. pixel  | 50.00         | 15.625000           | 14.75         | 29.50         | 4.43361875          | 00                        | 00     | 00     | 00     | 4C    | F3    | 18    | 19    |

| PAL CCIR-601    | 50.00         | 15.625000           | 13.50         | 27.00         | 4.43361875          | 00                        | 00     | 00     | 00     | 54    | 13    | 15    | 96    |

| PAL 15 Mpps     | 50.00         | 15.625000           | 15.00         | 30.00         | 4.43361875          | 00                        | 00     | 00     | 00     | 4B    | AA    | C6    | A1    |

| PAL-M sqr.pixel | 60.00         | 15.750000           | 12.50         | 25.01         | 3.57561149          | 00                        | 00     | 00     | 00     | 49    | 45    | 00    | 51    |

| PAL-M CCIR-601  | 60.00         | 15,750000           | 13.50         | 27.00         | 3.57561149          | 00                        | 00     | 00     | 00     | 43    | DF    | 3F    | D7    |

| PAL-M 4x FSC    | 60.00         | 15,750000           | 14.30         | 28.60         | 3.57561149          | 00                        | 00     | 00     | 00     | 40    | 10    | 66    | F5    |

#### **Subcarrier Synchronization**

There are 5 modes of subcarrier synchronization in the TMC2192, freerun, subcarrier reset, Genlock, DRS-lock and Ancillary Data Control (ANC).

#### Freerun

At the rising edge of  $\overline{RESET}$  the DDS starts to generate the subcarrier reference and will continue to freerun the subcarrier. When setting the control register DDSRST is HIGH, the TMC2192 will reset the DDS to the SYSPH value on the next field 1, line 1 (line 4 for NTSC), pixel 1 occurrence and will reset this bit to be LOW. This allows the encoder to start with the correct SCH relationship. The phase of the subcarrier reference will drift over time since a 32 bit accumulator has a error of  $\pm 0.5$  Hz when generating the subcarrier reference for NTSC 13.5 MHz.

#### Subcarrier Reset

At the rising edge of RESET the DDS starts to generate the subcarrier reference and will reset the DDS to the SYSPH value every field 1, line 1 (line 4 for NTSC), pixel 1 occurrence. This enables the encoder to maintain the proper SCH relationship.

#### Genlock

The Genlock mode allows the TMC2192 to lock to a composite reference when used in conjunction with the TMC22071A Genlocking Video Digitizer. The TMC22071A produces a genlock reference signal (GRS) which contains field identification, PALODD status, relative phase and relative frequency of the composite reference. The GRS is sampled on the CVBS bus 60 PXCK's after the falling edge of  $\overline{\rm HSIN}$ . The phase and frequency values are used to update the DDS on a line to line basis, thus synchronizing the subcarrier to an external composite reference.

#### DRS-Lock

The DRS-Lock mode allows the TMC2192 to lock its composite output to the decoded composite or S-video input of

the TMC22x5y. The TMC22x5y produces a decoder reference signal (DRS) which contains field identification, PAL-ODD status, relative phase and relative frequency of the composite or S-video input. The DRS is sampled on either the CVBS bus or the PD port, depending on DRSSEL, 60 PXCK's after the falling edge of HSIN. The phase and frequency values are used to update the DDS on a line to line basis, thus synchronizing the subcarrier to an external composite reference.

#### • Ancillary Data Control (ANC)

Subcarrier synchronization in ANC mode is covered in the Ancillary Data Control section of this data sheet.

#### **SCH Phase Error Correction**

SCH refers to the timing relationship between the 50% point of the leading edge of horizontal sync and the positive or negative zero-crossing of the color burst subcarrier reference. SCH error is usually expressed in degrees of subcarrier phase. In PAL, SCH is defined for line 1 of field 1, but since there is no color burst on line 1, SCH is usually measured at line 7 of field 1. The need to specify SCH relative to a particular line in PAL is due to the 25 Hz offset of PAL subcarrier frequency. Since NTSC has no such 25 Hz offset, SCH applies to all lines.

The SCH relationship is important in the TMC2192 when two video sources are being combined or if the composite video output is externally combined with another video source. In these cases, improper SCH phasing will result in a noticeable horizontal jump of one image with respect to another and/or a change in hue proportional to the SCH error between the two sources.

SCH phasing can be adjusted by modifying BURPH and SYSPH values by equal amounts. SCH is advanced/delayed by one degree by increasing/decreasing the value of BURPH and SYSPH by approximately B6h. An SCH error of 15° is corrected with SYSPH and BURPH offsets of AAAh.

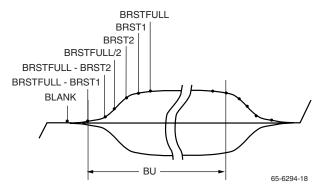

#### **Burst Envelope**

The TMC2192 includes the ability to adjust the burst amplitude and the shape of the burst. The Control Registers BRSTFULL, BRST1 and BRST2 hold the magnitude of the burst vector. BRSTFULL is the maximum amplitude of the burst vector. BRST1 and BRST2 determine the intermediate values of the burst vector for the burst envelope shaping. A 5 pixel burst envelope shaping occurs at the rising and falling edges of burst. At the rising edge of burst the next 5 pixels have the following weighting; BRSTFULL – BRST1, BRSTFULL – BRST2, BRSTFULL/2, BRST2, and BRST1. At the falling edge of burst the next 5 pixels have the following weighting; BRST1, BRST2, BRSTFULL/2, BRSTFULL – BRST2, and BRSTFULL – BRST1. With this flexibility the user determine the shape, amplitude and width of the burst signal.

Figure 15. Burst Envelope

#### Color-Difference Low-Pass Filters

The chrominance portion of a composite video signal must be sufficiently bandlimited to avoid cross-color and crossluminance distortion, and to preclude exceeding the allowable bandwidth of a video channel.

The color-difference low-pass filters on the TMC2192 establish chrominance bandwidths which meet the specifications outlined in CCIR Report 624-3, Table II, Item 2.6, for system I over a range of pixel rates from 12.27 Mpps to 14.75 Mpps. Equal bandwidth is established for both color-difference channels.

Figure 16. Gaussian Filter Response

# **Sync and Pedestal Insertion**

Control Registers for this section

| Address | Bit(s) | Name     |  |  |

|---------|--------|----------|--|--|

| 0x06    | 7-6    | MODE     |  |  |

| 0x11    | 5      | COMP2DB  |  |  |

| 0x14    | 7-0    | VBIPEDEM |  |  |

| 0x15    | 7-0    | VBIPEDEL |  |  |

| 0x16    | 7-0    | VBIPEDOM |  |  |

| 0x17    | 7-0    | VBIPENOL |  |  |

| 0x1A    | 6-0    | PEDHGT1  |  |  |

| 0x3F    | 3      | C2DB_OFF |  |  |

#### **Pedestal Enable**

The TMC2192 has the ability to independently select lines for pedestal insertion during the vertical blanking interval (VBI). For 525-line systems and using the NTSC line numbering convention, in which the first vertical serration is on line 4 for field 1 and line 266 for field 2, the vertical interval lines map to the control registers VBIPEDxy as shown in Table 15.

Table 12. Line by Line Pedestal Enable

| Bit      | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------|------|-----|-----|-----|-----|-----|-----|-----|

| VBIPEDEL | 17   | 16  | 15  | 14  | 13  | 12  | 11  | 10  |

| VBIPEDEM | 25*  | 24  | 23  | 22  | 21  | 20  | 19  | 18  |

| VBIPEDOL | 279  | 278 | 277 | 276 | 275 | 274 | 273 |     |

| VBIPEDOM | 287* | 286 | 285 | 284 | 283 | 282 | 281 | 280 |

Enabling the pedestal on line 25 enables it for the remainder of field 1, to line 262. Likewise, enabling the pedestal on line 288 enables it for the remainder of field 2.

#### **Pedestal Height**

PEDHGT1 determines the height of the pedestal for the luminance channel on the composite path. The range of the pedestal height is from -22.1 to 21.74 IRE in .345 IRE increments.

# Sync and Blank Insertion

The composite paths blank and sync D/A codes are determined by the FORMAT control register. For NTSC and PAL-M formats the blank D/A code is 240 (295 mV) and the sync D/A code is 8 (9 mV). For all other PAL formats the blank D/A code is 256 (314 mV) and the sync D/A code is 12 (14 mV).

In all cases the sync edges are sloped to insure the proper rise and fall times in all video standards.

## **Closed Caption Insertion**

Control Registers for this section

| Address | Bit(s) | Name   |

|---------|--------|--------|

| 0x1C    | 7-6    | CCD1   |

| 0x1D    | 1-0    | CCD2   |