SLVS036J - SEPTEMBER 1981 - REVISED MAY 2003

- Output Adjustable From 1.25 V to 125 V When Used With an External Resistor Divider

- 700-mA Output Current

- Full Short-Circuit, Safe-Operating-Area, and Thermal-Shutdown Protection

- 0.001%/V Typical Input Voltage Regulation

- 0.15% Typical Output Voltage Regulation

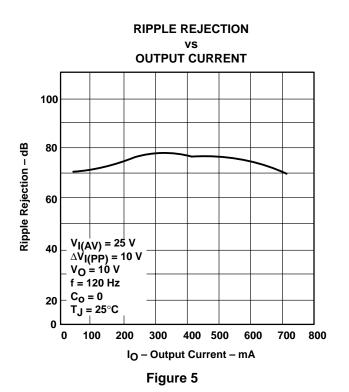

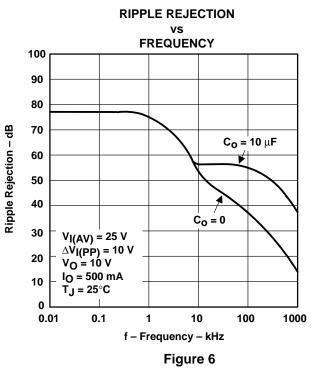

- 76-dB Typical Ripple Rejection

## description/ordering information

The TL783 is an adjustable three-terminal high-voltage regulator with an output range of 1.25 V to 125 V and a DMOS output transistor capable of sourcing more than 700 mA. It is designed for use in high-voltage applications where standard bipolar regulators cannot be used. Excellent performance specifications, superior to those of most bipolar regulators, are achieved through circuit design and advanced layout techniques.

# KC (TO-220) PACKAGE (TOP VIEW)

#### KTT (TO-263) PACKAGE (TOP VIEW)

As a state-of-the-art regulator, the TL783 combines standard bipolar circuitry with high-voltage double-diffused MOS transistors on one chip, to yield a device capable of withstanding voltages far higher than standard bipolar integrated circuits. Because of its lack of secondary-breakdown and thermal-runaway characteristics usually associated with bipolar outputs, the TL783 maintains full overload protection while operating at up to 125 V from input to output. Other features of the device include current limiting, safe-operating-area (SOA) protection, and thermal shutdown. Even if ADJ is disconnected inadvertently, the protection circuitry remains functional.

Only two external resistors are required to program the output voltage. An input bypass capacitor is necessary only when the regulator is situated far from the input filter. An output capacitor, although not required, improves transient response and protection from instantaneous output short circuits. Excellent ripple rejection can be achieved without a bypass capacitor at the adjustment terminal.

#### **ORDERING INFORMATION**

| TJ           | PACKAGE <sup>†</sup> |              | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|--------------|----------------------|--------------|--------------------------|---------------------|

| 0°C to 125°C | Power Flex (KTE)     | Reel of 2000 | TL783CKTER               | TL783               |

|              | TO-263 (KTT)         | Tube of 50   | TL783CKTT                | LE DDEVIEW          |

|              |                      | Reel of 1000 | TL783CKTTR               | AE PREVIEW          |

|              | TO-220 (KC)          | Tube of 50   | TL783CKC                 | TL783C              |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

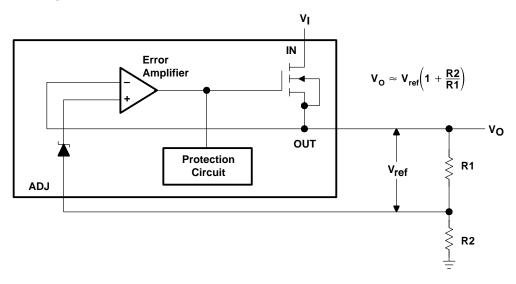

### functional block diagram

## absolute maximum ratings over operating temperature range (unless otherwise noted)

| Input-to-output differential voltage, V <sub>I</sub> – V <sub>O</sub> | 125 V |

|-----------------------------------------------------------------------|-------|

| Operating virtual junction temperature, Tj                            | 150°C |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds          | 260°C |

| Storage temperature range, T <sub>stg</sub> –65°C to                  | 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# package thermal data (see Note 1)

| PACKAGE          | BOARD             | θЈС   | $\theta$ JA |

|------------------|-------------------|-------|-------------|

| Power Flex (KTE) | High K, JESD 51-5 | 3°C/W | 23°C/W      |

| TO-263 (KTT)     | High K, JESD 51-5 | TBD   | TBD         |

| TO-220 (KC)      | High K, JESD 51-5 | 3°C/W | 19°C/W      |

$NOTE~1:~~Maximum~power~dissipation~is~a~function~of~T_{J}(max),~\theta_{JA},~and~T_{A}.~The~maximum~allowable~power~dissipation~at~any~allowable~ambient$ temperature is  $P_D = (T_J(max) - T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of 150°C can affect reliability. Due to variations in individual device electrical characteristics and thermal resistance, the built-in thermal overload protection may be activated at power levels slightly above or below the rated dissipation.

### recommended operating conditions

|                   |                                        |        | MIN | MAX | UNIT |

|-------------------|----------------------------------------|--------|-----|-----|------|

| $V_I - V_O$       | Input-to-output voltage differential   |        |     | 125 | V    |

| IO Output current |                                        | 15     | 700 | mA  |      |

| TJ                | Operating virtual junction temperature | TL783C | 0   | 125 | °C   |

SLVS036J - SEPTEMBER 1981 - REVISED MAY 2003

# electrical characteristics at $V_I - V_O = 25$ V, $I_O = 0.5$ A, $T_J = 0$ °C to 125°C (unless otherwise noted)

| DADAMETED                                     | TEST CONDITIONS†                                            |                                           |                               | TL783C |       |      |      |  |

|-----------------------------------------------|-------------------------------------------------------------|-------------------------------------------|-------------------------------|--------|-------|------|------|--|

| PARAMETER                                     |                                                             |                                           |                               | MIN    | TYP   | MAX  | UNIT |  |

| Input voltage regulation‡                     | $V_I - V_O = 20 \text{ V to } 125 \text{ V},$               | P ≤ rated dissipation                     | T <sub>J</sub> = 25°C         |        | 0.001 | 0.01 | %/V  |  |

|                                               |                                                             |                                           | T <sub>J</sub> = 0°C to 125°C |        | 0.004 | 0.02 |      |  |

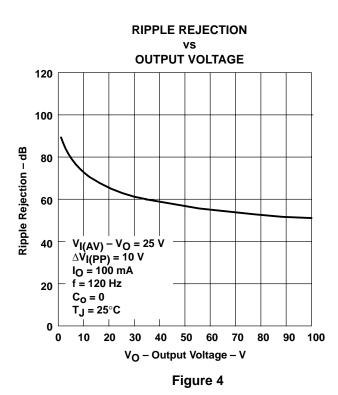

| Ripple rejection                              | $\Delta V_{I(PP)} = 10 \text{ V},$                          | V <sub>O</sub> = 10 V,                    | f = 120 Hz                    | 66     | 76    |      | dB   |  |

|                                               | I <sub>O</sub> = 15 mA to 700 mA,                           | T <sub>J</sub> = 25°C                     | $V_0 \le 5 V$                 |        | 7.5   | 25   | mV   |  |

| Output voltage                                |                                                             |                                           | $V_O \ge 5 V$                 |        | 0.15  | 0.5  | %    |  |

| regulation                                    | L- 45 A to 700 A                                            | P ≤ rated dissipation                     | $V_O \le 5 V$                 |        | 20    | 70   | mV   |  |

|                                               | $I_O = 15 \text{ mA to } 700 \text{ mA},$                   | r stated dissipation                      | $V_O \ge 5 V$                 |        | 0.3   | 1.5  | %    |  |

| Output voltage change with temperature        |                                                             |                                           |                               |        | 0.4   |      | %    |  |

| Output voltage long-term drift                | 1000 hours at T <sub>J</sub> = 125°C,                       | V <sub>I</sub> – V <sub>O</sub> = 125 V   |                               |        | 0.2   |      | %    |  |

| Output noise voltage                          | f = 10 Hz to 10 kHz,                                        | T <sub>J</sub> = 25°C                     |                               |        | 0.003 |      | %    |  |

| Minimum output current to maintain regulation | V <sub>I</sub> – V <sub>O</sub> = 125 V                     |                                           |                               |        |       | 15   | mA   |  |

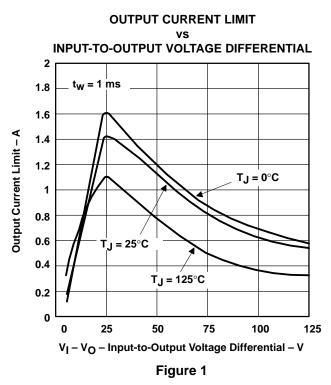

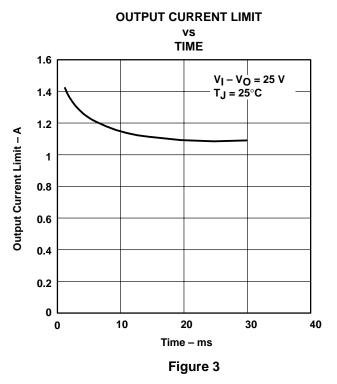

|                                               | $V_I - V_O = 25 V$ ,                                        | t = 1 ms                                  |                               |        | 1100  |      | A    |  |

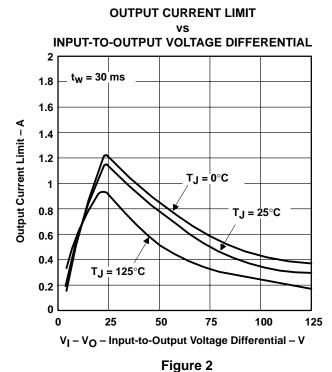

| Book output ourront                           | $V_I - V_O = 15 V$ ,                                        | t = 30 ms                                 |                               |        | 715   |      |      |  |

| Peak output current                           | $V_I - V_O = 25 V$ ,                                        | t = 30 ms                                 |                               | 700    | 900   |      | mA   |  |

|                                               | $V_I - V_O = 125 V$ ,                                       | t = 30 ms                                 |                               | 100    | 250   |      |      |  |

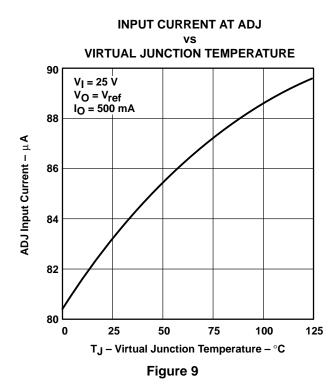

| ADJ input current                             |                                                             |                                           |                               |        | 83    | 110  | μΑ   |  |

| Change in ADJ input current                   | $V_I - V_O = 15 \text{ V to } 125 \text{ V},$               | I <sub>O</sub> = 15 mA to 700 mA,         | P ≤ rated dissipation         |        | 0.5   | 5    | μΑ   |  |

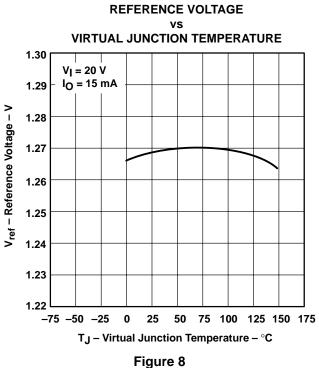

| Reference voltage<br>(OUT to ADJ)             | $V_I - V_O = 10 \text{ V to } 125 \text{ V},$<br>See Note 2 | $I_O = 15 \text{ mA to } 700 \text{ mA},$ | P ≤ rated dissipation,        | 1.2    | 1.27  | 1.3  | ٧    |  |

<sup>†</sup> Pulse-testing techniques maintain the junction temperature as close to the ambient temperature as possible. Thermal effects must be taken into account separately.

<sup>‡</sup> Input voltage regulation is expressed here as the percentage change in output voltage per 1-V change at the input.

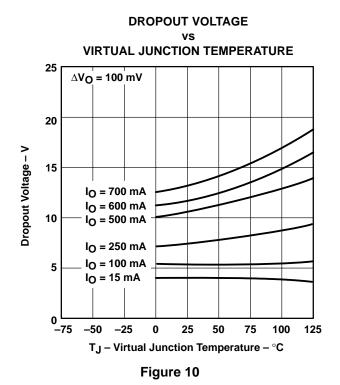

NOTE 2: Due to the dropout voltage and output current-limiting characteristics of this device, output current is limited to less than 700 mA at input-to-output voltage differentials of less than 25 V.

#### TYPICAL CHARACTERISTICS

TEXAS INSTRUMENTS

#### TYPICAL CHARACTERISTICS<sup>†</sup>

† Data at high and low temperatures are applicable only within the recommended operating free-air temperature ranges of the various devices.

#### TYPICAL CHARACTERISTICS

# **OUTPUT VOLTAGE DEVIATION VIRTUAL JUNCTION TEMPERATURE** $V_{I} = 25 V$ V<sub>O</sub> = 5 V ∆V<sub>O</sub> – Output Voltage Deviation – % $I_0 = 15 \text{ mA to } 700 \text{ mA}$ -0.1 -0.2 -0.3-0.4-0.5 0 25 50 75 100 125 150 T<sub>J</sub> - Virtual Junction Temperature - °C

<sup>†</sup> This is the minimum current required to maintain voltage regulation.

Figure 11 Figure 12

#### TYPICAL CHARACTERISTICS

#### **DESIGN CONSIDERATIONS**

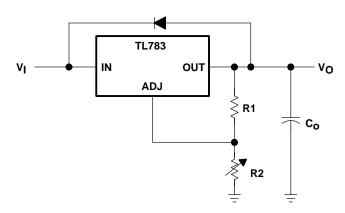

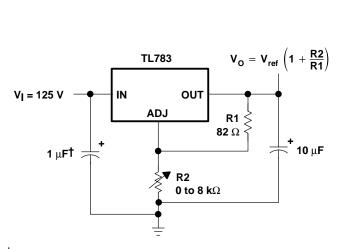

The internal reference (see functional block diagram) generates 1.25 V nominal (V<sub>ref</sub>) between OUT and ADJ. This voltage is developed across R1 and causes a constant current to flow through R1 and the programming resistor R2, giving an output voltage of:

$$V_{O} = V_{ref} (1 + R2/R1) + I_{I(ADJ)} (R2)$$

or

$$V_O \approx V_{ref} (1 + R2/R1)$$

The TL783 was designed to minimize the input current at ADJ and maintain consistency over line and load variations, thereby minimizing the associated (R2) error term.

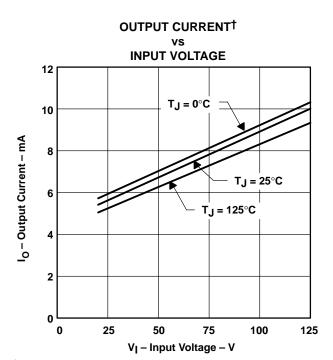

To maintain  $I_{I(ADJ)}$  at a low level, all quiescent operating current is returned to the output terminal. This quiescent current must be sunk by the external load and is the minimum load current necessary to prevent the output from rising. The recommended R1 value of 82  $\Omega$  provides a minimum load current of 15 mA. Larger values can be used when the input-to-output differential voltage is less than 125 V (see the output-current curve in Figure 14) or when the load sinks some portion of the minimum current.

#### **DESIGN CONSIDERATIONS**

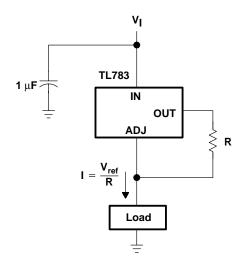

# bypass capacitors

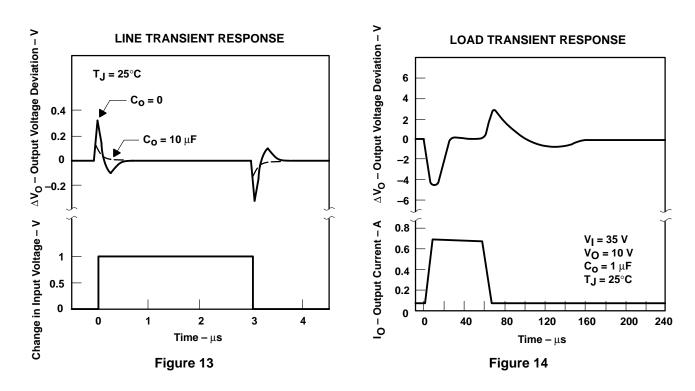

The TL783 regulator is stable without bypass capacitors; however, any regulator becomes unstable with certain values of output capacitance if an input capacitor is not used. Therefore, the use of input bypassing is recommended whenever the regulator is located more than four inches from the power-supply filter capacitor. A 1-µF tantalum or aluminum electrolytic capacitor usually is sufficient.

Adjustment-terminal capacitors are not recommended for use on the TL783 because they can seriously degrade load transient response, as well as create a need for extra protection circuitry. Excellent ripple rejection presently is achieved without this added capacitor.

Due to the relatively low gain of the MOS output stage, output voltage dropout may occur under large-load transient conditions. The addition of an output bypass capacitor greatly enhances load transient response and prevents dropout. For most applications, it is recommended that an output bypass capacitor be used, with a minimum value of:

$$C_0 (\mu F) = 15/V_0$$

Larger values provide proportionally better transient-response characteristics.

### protection circuitry

The TL783 regulator includes built-in protection circuits capable of guarding the device against most overload conditions encountered in normal operation. These protective features are current limiting, safe-operating-area protection, and thermal shutdown. These circuits protect the device under occasional fault conditions only. Continuous operation in the current limit or thermal shutdown mode is not recommended.

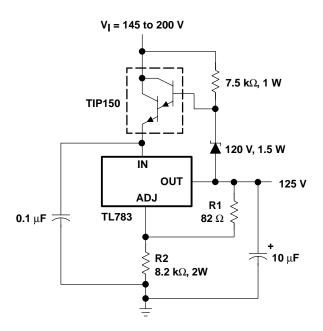

The internal protection circuits of the TL783 protect the device up to maximum-rated  $V_I$  as long as certain precautions are taken. If  $V_I$  is switched on instantaneously, transients exceeding maximum input ratings may occur, which can destroy the regulator. Usually, these are caused by lead inductance and bypass capacitors causing a ringing voltage on the input. In addition, when rise times in excess of 10 V/ns are applied to the input, a parasitic npn transistor in parallel with the DMOS output can be turned on, causing the device to fail. If the device is operated over 50 V and the input is switched on, rather than ramped on, a low-Q capacitor, such as tantalum or aluminum electrolytic, should be used, rather than ceramic, paper, or plastic bypass capacitors. A Q factor of 0.015, or greater, usually provides adequate damping to suppress ringing. Normally, no problems occur if the input voltage is allowed to ramp upward through the action of an ac line rectifier and filter network.

Similarly, when an instantaneous short circuit is applied to the output, both ringing and excessive fall times can result. A tantalum or aluminum electrolytic bypass capacitor is recommended to eliminate this problem. However, if a large output capacitor is used, and the input is shorted, addition of a protection diode may be necessary to prevent capacitor discharge through the regulator. The amount of discharge current delivered is dependent on output voltage, size of capacitor, and fall time of V<sub>I</sub>. A protective diode (see Figure 17) is required only for capacitance values greater than:

$$C_0 (\mu F) = 3 \times 10^4 / (V_0)^2$$

Care always should be taken to prevent insertion of regulators into a socket with power on. Power should be turned off before removing or inserting regulators.

### **DESIGN CONSIDERATIONS**

Figure 15. Regulator With Protective Diode

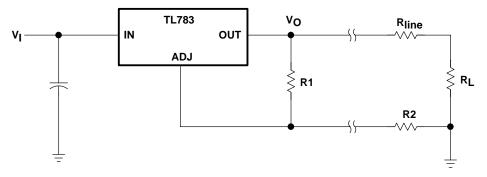

# load regulation

The current-set resistor (R1) should be located close to the regulator output terminal, rather than near the load. This eliminates long line drops from being amplified, through the action of R1 and R2, to degrade load regulation. To provide remote ground sensing, R2 should be near the load ground.

Figure 16. Regulator With Current-Set Resistor

#### **APPLICATION INFORMATION**

† Needed if device is more than 4 inches from filter capacitor

Figure 17. 1.25-V to 115-V Adjustable Regulator

Figure 18. 125-V Short-Circuit-Protected Off-Line Regulator

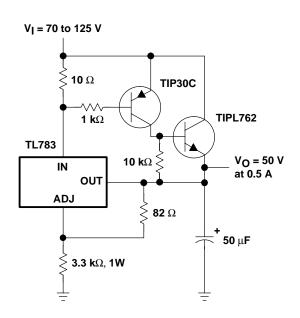

Figure 19. 50-V Regulator With Current Boost

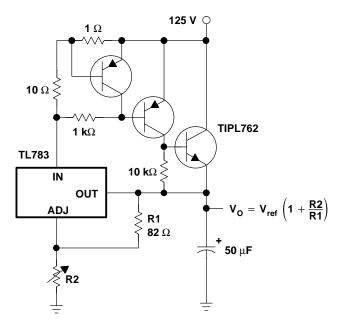

Figure 20. Adjustable Regulator With Current Boost and Current Limit

#### **APPLICATION INFORMATION**

Figure 21. Current-Sinking Regulator

Figure 22. Current-Sourcing Regulator

Figure 23. High-Voltage Unity-Gain Offset Amplifier

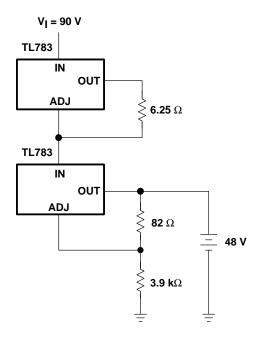

Figure 24. 48-V, 200-mA Float Charger

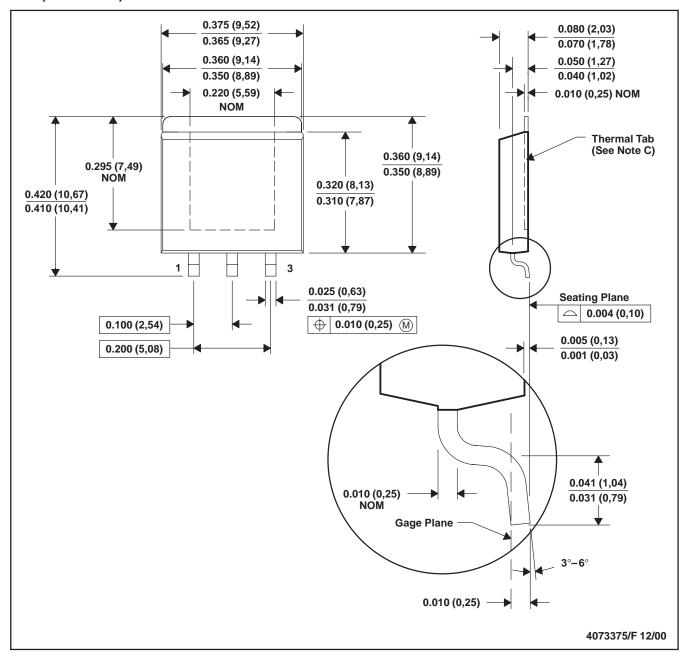

## KTE (R-PSFM-G3)

#### PowerFLEX™ PLASTIC FLANGE-MOUNT

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. The center lead is in electrical contact with the thermal tab.

- D. Dimensions do not include mold protrusions, not to exceed 0.006 (0,15).

- E. Falls within JEDEC MO-169

PowerFLEX is a trademark of Texas Instruments.

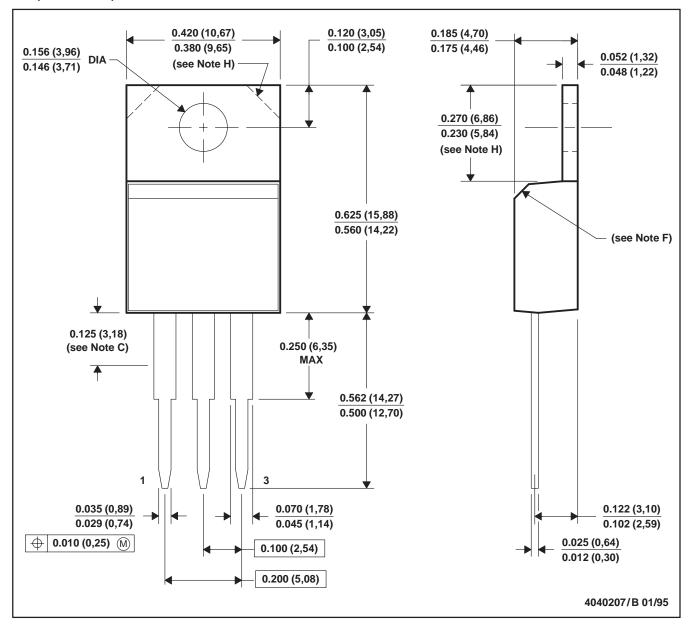

#### KC (R-PSFM-T3)

#### PLASTIC FLANGE-MOUNT PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Lead dimensions are not controlled within this area.

- D. All lead dimensions apply before solder dip.

- E. The center lead is in electrical contact with the mounting tab.

- F. The chamfer is optional.

- G. Falls within JEDEC TO-220AB

- H. Tab contour optional within these dimensions

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated